### THREE INTEGRATED, FIXED OUTPUT LINEAR VOLTAGE REGULATORS PRELIMINARY DATA SHEET

### FEATURES

- Stable with Ceramic Capacitor

- Fixed 8V, 3.3V and 2.6V

- Fast Transient Response

- Output Current Limiting for each outputs

- Built-In Thermal Shutdown

# **APPLICATIONS**

- Hard Disk Drive

- Multi-Outputs Applications

- High Efficiency Linear Regulator

# DESCRIPTION

The IRU1237SC voltage regulator solution contains three integrated, fixed, linear voltage regulators in one 7-pin surface mount package. The first is a 2.6V regulator to power the read channel and integrated controller/ $\mu$ P. The second is a 3.3V regulator to power the controller I/O and memory chips requiring 3.3V. The last is an 8V regulator to power the preamp chip. The bandgap reference, the 8V ground, and the substrate are all tied to a common ground pin, while the 2.6V and 3.3V ground is tied to a separate ground pin. This grounding scheme allows for improved noise isolation between the 8V regulator and the 2.6V and 3.3V regulator.

The 2.6V and 3.3V regulators shall each be capable of 1.2A continuous for a 5.25V input. The 8V regulator shall be capable of 0.2A continuous for a 13.2V input.

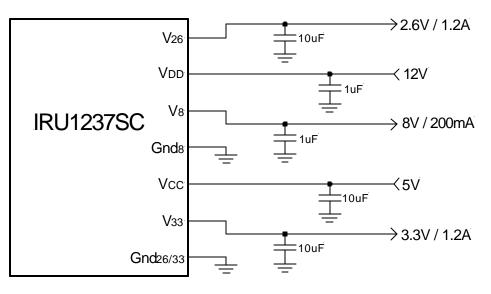

# TYPICAL APPLICATION

Figure 1 - Typical application of IRU1237SC.

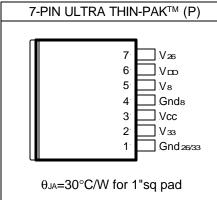

## PACKAGE ORDER INFORMATION

| TJ (°C)  | 7-PIN PLASTIC<br>Ultra Thin-Pak™ (P) | PACKAGE<br>MARKING |  |  |

|----------|--------------------------------------|--------------------|--|--|

| 0 To 150 | IRU1237SCCP                          | US1237SCCP         |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

| Input Voltage (Vcc)                  | 18V             |

|--------------------------------------|-----------------|

| Input Voltage (VDD)                  | 18V             |

| Operating Junction Temperature Range | 0°C To 150°C    |

| Operating Ambient Temperature Range  | 0°C To 70°C     |

| Storage Temperature Range            | -65°C To +150°C |

| ESD Capability (Human Body Model)    | 2000V           |

# PACKAGE INFORMATION

# **ELECTRICAL SPECIFICATIONS**

Unless otherwise specified, these specifications apply over Vcc=5V, Vbb=12V, GN=Cout=0.1 $\mu$ F(X7R), TJ=0 to 125°C. Typical values refer to TJ=25°C. IFL1=1.2A, IFL2 =1.2A and IFL3 =0.2A.

| PARAMETER                    | SYM              | TEST CONDITION                                                                                  | MIN   | TYP  | MAX   | UNITS |

|------------------------------|------------------|-------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Output Voltage #1            | Vo1              | Over all operating conditions                                                                   | 2.522 | 2.60 | 2.678 | V     |

| Output Voltage #1            | V <sub>01</sub>  | 0V <vpd<10.8v, lo1="0.5A&lt;/td"><td>2.20</td><td>2.60</td><td>2.65</td><td>V</td></vpd<10.8v,> | 2.20  | 2.60 | 2.65  | V     |

| Output Voltage #2            | V <sub>O2</sub>  | Over all operating conditions                                                                   | 3.20  | 3.30 | 3.40  | V     |

| Output Voltage #2            | V <sub>O2</sub>  | 0V <vpd<10.8v, lo1="0.5A&lt;/td"><td>2.90</td><td>3.30</td><td>3.40</td><td>V</td></vpd<10.8v,> | 2.90  | 3.30 | 3.40  | V     |

| Output Voltage #3            | V <sub>O3</sub>  | Over all operating conditions                                                                   | 7.76  | 8.00 | 8.24  | V     |

| Line Regulation              | RegLINE          | $lo=10mA$ , $Vcc \pm 5\%$ , $V_{DD} \pm 10\%$                                                   |       | 0.2  |       | %Vo   |

| Load Regulation              | Regload          | Note 1, 10mA < l₀ < l⊧∟                                                                         |       | 0.4  |       | %Vo   |

| Dropout Voltage (Output #1)  | V <sub>DO1</sub> | Note 2, lo1=IFL1                                                                                |       | 1.3  | 1.7   | V     |

| Dropout Voltage (Output #2)  | Vdo2             | Note 2, lo2=IFL2                                                                                |       | 1.1  | 1.3   | V     |

| Dropout Voltage (Output #3)  | V <sub>DO3</sub> | Note 3, Io3=IFL3                                                                                |       | 2.0  | 2.2   | V     |

| Transient Response           | t <sub>TR</sub>  | Note 3 and 7                                                                                    |       | 1.0  |       | μS    |

| Current Limit (Output #1)    | IOL1             | $\Delta V_{01}=125 mV$                                                                          | 1.50  | 1.65 | 2.50  | А     |

| Current Limit (Output #2)    | l0L2             | $\Delta V_{02}=165 mV$                                                                          | 1.50  | 1.65 | 2.50  | Α     |

| Current Limit (Output #3)    | lol3             | $\Delta V_{03}=400 \text{mV}$                                                                   | 0.25  | 0.30 | 0.50  | Α     |

| Min Load Current (Output #1) | LO1(MIN)         | Note 4 and 7                                                                                    |       |      | 0     | mA    |

| Min Load Current (Output #2) | LO2(MAX)         | Note 4 and 7                                                                                    |       |      | 0     | mA    |

| Min Load Current (Output #3) | LO3(MAX)         | Note 4 and 7                                                                                    |       |      | 0     | mA    |

| Output Capacitor             | Co               | Note 5 and 7                                                                                    | 0.1   |      | 33    | μF    |

| Input Capacitor              | CIN              | Note 7                                                                                          | 0.1   |      |       | μF    |

| Thermal Regulation           | Regtherm         | Note 7, 30ms pulse, lo=IFL                                                                      |       | 0.1  | 0.3   | %/W   |

| PARAMETER             | SYM               | TEST CONDITION                                                                                      | MIN | TYP   | MAX | UNITS |

|-----------------------|-------------------|-----------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| Ripple Rejection      | <b>PSRR</b> ₁     | Note 7, 100Hz <f<100khz, lo="I⊧∟1/10&lt;/td"><td>30</td><td>40</td><td></td><td>dB</td></f<100khz,> | 30  | 40    |     | dB    |

| (Vcc to Output #1)    |                   |                                                                                                     |     |       |     |       |

| Ripple Rejection      | PSRR <sub>2</sub> | Note 7, 100Hz <f<100khz, lo="IFL2/10&lt;/td"><td>30</td><td>40</td><td></td><td>dB</td></f<100khz,> | 30  | 40    |     | dB    |

| (Vcc to Output #2)    |                   |                                                                                                     |     |       |     |       |

| Ripple Rejection      | <b>PSRR</b> ₃     | Note 7, 100Hz <f<100khz, lo="IFL3/10&lt;/td"><td>40</td><td>50</td><td></td><td>dB</td></f<100khz,> | 40  | 50    |     | dB    |

| (VDD to Output #3)    |                   |                                                                                                     |     |       |     |       |

| TJ Thermal Shutdown   | TTHERM            | Note 7                                                                                              |     | 150   |     | °C    |

| Temperature Stability | Stabtemp          | Note 6 and 7, lo=10mA                                                                               |     | 0.5   |     | %Vo   |

| Long Term Stability   | StabLONG          | Note 7, TJ=125°C, 1000Hrs                                                                           |     | 0.3   |     | %Vo   |

| RMS Output Noise      | VN                | Note 7, 10Hz <f<10khz< td=""><td></td><td>0.003</td><td></td><td>%Vo</td></f<10khz<>                |     | 0.003 |     | %Vo   |

| Vcc Quiescent current | lq1               | lo1=lo2=lo3=0                                                                                       |     | 4     | 8   | mA    |

| VDD Quiescent current | Q2                | lo1=lo2=lo3=0                                                                                       |     | 12    | 20  | mA    |

**Note 1:** Low duty cycle pulse testing with Kelvin connections is required in order to maintain accurate data.

**Note 2:** Dropout voltage is defined as the minimum differential voltage between  $V_{IN}$  and  $V_{OUT}$  required to maintain regulation at  $V_{OUT}$ . It is measured when the output voltage drops 1% below its nominal value.

**Note 3:** Transient response is defined with a step change in load from 10mA to  $I_{FL}/2$ , as the time from the load step until the output voltage reaches its minimum value.

**Note 4:** Minimum load current is defined as the minimum current required at the output in order for the output voltage to maintain regulation.

**Note 5:** The regulator shall withstand 100,000 reverse bias discharges of the maximum output capacitance, with no degradation, when the input voltage is switched to ground in  $1\mu$ s.

**Note 6:** Temperature stability is the change in output from nominal over the operating temperature range.

**Note 7:** Guaranteed by design, but not tested in production.

| PIN#                                                        | PIN SYMBOL      | PIN DESCRIPTION                                                                                                                                                                                                                                    |  |  |  |  |  |

|-------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1,4                                                         | Gnd26/33, Gnd8  | These pins are connected to ground. It is also the tab of the device.                                                                                                                                                                              |  |  |  |  |  |

| 2 V <sub>33</sub> Output #1. Fixed regulator output (3.3V). |                 |                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 3                                                           | Vcc             | Positive unregulated supply input for the regulator. This pin must always be higher than both $V_{OUT}$ pins by the amount of the dropout voltage in order for the device to regulate properly. Bypass to ground with low ESR and ESL capacitance. |  |  |  |  |  |

| 5                                                           | V8              | Output #3. Fixed regulator output (8V).                                                                                                                                                                                                            |  |  |  |  |  |

| 6                                                           | Vdd             | Input voltage to supply the base current for the pass transistor for both regulators.                                                                                                                                                              |  |  |  |  |  |

| 7                                                           | V <sub>26</sub> | Output #2. Fixed regulator output (2.6V).                                                                                                                                                                                                          |  |  |  |  |  |

|                                                             |                 |                                                                                                                                                                                                                                                    |  |  |  |  |  |

## PIN DESCRIPTIONS

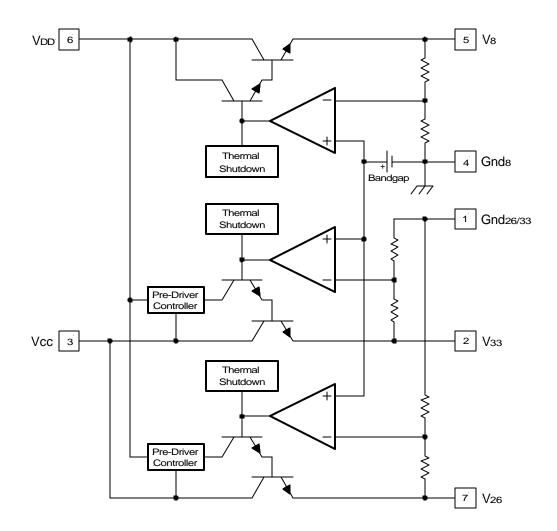

# **BLOCK DIAGRAM**

Figure 2 - Simplified block diagram of the IRU1237SC.

### **APPLICATION INFORMATION**

### Introduction

The IRU1237SC regulator is 7-pin terminal device and contains three integrated, fixed, linear regulators. The dual inputs provide a low dropout voltage for  $V_{33}$  and  $V_{26}$  by biasing the base current to power NPN transistors. The IRU1237SC is designed to meet the fast current transient needs as well as an accurate initial voltage, thus reducing the overall system cost with the need for fewer number of output capacitors.

### **Thermal Protection**

The IRU1237SC provides thermal protection for all three outputs. All outputs will be disabled for any over-temperature condition. When one of the outputs exceeds the thermal limit (typically 150°C), the IRU1237SC shuts down all three outputs simultaneously. The outputs will be re-enabled when the temperature drops below the thermal limit.

### **Current Limit Protection**

The IRU1237SC provides over current protection when one the outputs' current exceeds the current limit level.

### Stability

The IRU1237SC doesn't require input and output capacitors for stability, however to improve the transient response and guarantee stability, it is recommended that a  $0.1\mu F$  (minimum) ceramic for input and output capacitors be used.

#### **Transient Response and PSRR**

The input and output capacitors are critical in order to ensure good transient response and PSSR. The most important aspects of this are capacitor selection, placement, and trace routing. Place each capacitor as close as physically possible to it's corresponding regulator pin. Use wide traces for low inductance path. Couple directly to the ground and power planes as possible. The use of low ESR capacitors is crucial to achieving good results. An input capacitance of at least  $0.1\mu$ F is recommended. An output capacitance of at least  $0.1\mu$ F with low ESR is recommended for good PSSR at high frequencies. Ceramic capacitors are a good choice for low ESR. Larger capacitance and lower ESR will improve both PSSR and transient response.

### **Thermal Design**

The IRU1237SC incorporates an internal thermal shutdown that protects the device when the junction temperature exceeds the allowable maximum junction temperature. Although this device can operate with junction temperatures in the range of 150°C, it is recommended that the selected heat sink be chosen such that during maximum continuous load operation the junction temperature is kept below this number.

The following thermal design illustrates the method used to calculate the maximum junction temperature of the regulator.

| Vin1=5.25V | Vout1=2.6V | lout1=0.5A |

|------------|------------|------------|

| V1N2=12V   | Vout2=3.3V | lout2=0.5A |

|            | Vout3=8V   | louтз=0.1A |

Calculating the maximum power dissipation:

```

\begin{array}{l} \mathsf{P}_{\mathsf{D}} = \ (\mathsf{V}_{\mathsf{IN1}} - \mathsf{V}_{\mathsf{OUT1}}) \times \ \mathsf{I}_{\mathsf{OUT1}} + (\mathsf{V}_{\mathsf{IN1}} - \mathsf{V}_{\mathsf{OUT2}}) \times \ \mathsf{I}_{\mathsf{OUT2}} + (\mathsf{V}_{\mathsf{IN2}} - \mathsf{V}_{\mathsf{OUT3}}) \times \ \mathsf{I}_{\mathsf{OUT3}} \\ \mathsf{P}_{\mathsf{D}} = \ (5.25 - 2.6) \times 0.5 + (5.25 - 3.3) \times 0.5 + (12 - 8) \times 0.1 \\ \mathsf{P}_{\mathsf{D}} = \ 2.7 \mathsf{W} \end{array}

```

For Ultra Thin-Pak<sup>™</sup> we have:

$\begin{array}{l} \mathsf{R}_{\mathsf{TH}(\mathsf{JA})}{=}30\mathsf{W}/^{\circ}\mathsf{C}\\ \mathsf{T}_{\mathsf{A}}{=}50^{\circ}\mathsf{C}\\ \Delta\mathsf{T}{=}\mathsf{P}_{\mathsf{D}}{\times}\mathsf{R}_{\mathsf{TH}(\mathsf{JA})}{=}2.7\mathsf{W}{\times}30{=}81^{\circ}\mathsf{C}\\ \mathsf{T}_{\mathsf{J}}{=}\mathsf{T}_{\mathsf{A}}{+}\Delta\mathsf{T}{=}131^{\circ}\mathsf{C} \end{array}$

### Layout Consideration

The IRU1237SC, like many other high-speed regulators, requires that the output capacitors be close to the device for stability. For power consideration, a ground plane pad of approximately one-inch square on the component side must be dedicated to device where all ground pins are connected to dissipate the power. The copper area under the package shall have vias to the internal ground plane. The thermal ground plane shall extend out from the regulator to open areas of the PCB. All open areas shall be filled with copper to help radiate heat from the PCB.

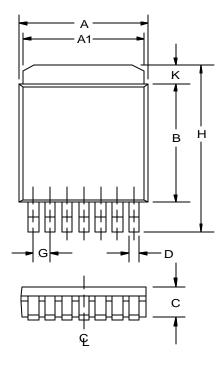

# IRU1237SC

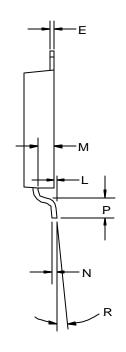

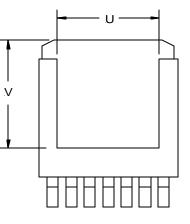

| SYMBOL | MIN        | MAX   |  |

|--------|------------|-------|--|

| Α      | 9.27       | 9.52  |  |

| A1     | 8.89       | 9.14  |  |

| В      | 7.87       | 8.13  |  |

| С      | 1.78       | 2.03  |  |

| D      | 0.63       | 0.79  |  |

| Е      | 0.25 NOM   |       |  |

| G      | 1.27       |       |  |

| Н      | 10.41      | 10.67 |  |

| K      | 0.76       | 1.27  |  |

| L      | 0.03       | 0.13  |  |

| М      | 0.89       | 1.14  |  |

| N      | 0.2        | 25    |  |

| Р      | 0.79       | 1.04  |  |

| R      | 3°         | 6°    |  |

| U      | 5.59 NOM   |       |  |

| V      | V 7.49 NOM |       |  |

NOTE: ALL MEASUREMENTS ARE IN MILLIMETERS.

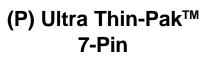

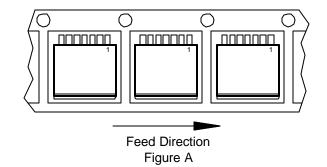

## **PACKAGE SHIPMENT METHOD**

|   | PKG   | PACKAGE         | PIN PARTS      |    | PARTS    | T & R       |  |

|---|-------|-----------------|----------------|----|----------|-------------|--|

|   | DESIG | DESCRIPTION     | COUNT PER TUBE |    | PER REEL | Orientation |  |

| ſ | Р     | Ultra Thin-Pak™ | 7              | 75 | 2500     | Fig A       |  |

International IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information Data and specifications subject to change without notice. 02/01

. 02/0