## TPS62000, TPS62001, TPS62002, TPS62003 TPS62004, TPS62005, TPS62006, TPS62007, TPS62008 HIGH-EFFICIENCY STEP-DOWN LOW POWER DC-DC CONVERTER SLVS294B – SEPTEMBER 2000 – REVISED JUNE 2002

## features

- High-Efficiency Synchronous Step-Down Converter With Greater Than 95% Efficiency

- 2 V to 5.5 V Operating Input Voltage Range

- Adjustable Output Voltage Range From 0.8 V to V<sub>I</sub>

- Fixed Output Voltage Options Available in 0.9 V, 1 V, 1.2 V, 1.5 V, 1.8 V, 1.9 V, 2.5 V, and 3.3 V

- Synchronizable to External Clock Signal up to 1 MHz

- Up to 600 mA Output Current

- Pin-Programmable Current Limit

- High Efficiency Over a Wide Load Current Range in Power Save Mode

- 100% Maximum Duty Cycle for Lowest Dropout

- Low-Noise Operation Antiringing Switch and PFM/PWM Operation Mode

- Internal Softstart

- **50-**µA Quiescent Current (TYP)

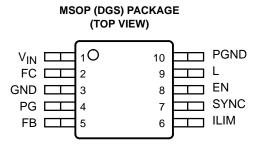

- Available in the 10-Pin Microsmall Outline Package (MSOP)

- Evaluation Module Available

#### applications

- Low-Power CPUs and DSPs

- Cellular Phones

- Organizers, PDAs, and Handheld PCs

- MP-3 Portable Audio Players

- Digital Cameras

- USB-Based DSL Modems and Other Network Interface Cards

## description

The TPS6200x devices are a family of low-noise synchronous step-down dc-dc converters that are ideally suited for systems powered from a 1-cell Li-ion battery or from a 2- to 3-cell NiCd, NiMH, or alkaline battery. The TPS6200x operates typically down to an input voltage of 1.8 V, with a specified minimum input voltage of 2 V.

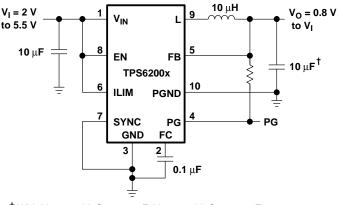

<sup>†</sup> With  $V_{O} \ge 1.8$  V;  $C_{O} = 10 \mu$ F,  $V_{O} < 1.8$  V;  $C_{O} = 47 \mu$ F

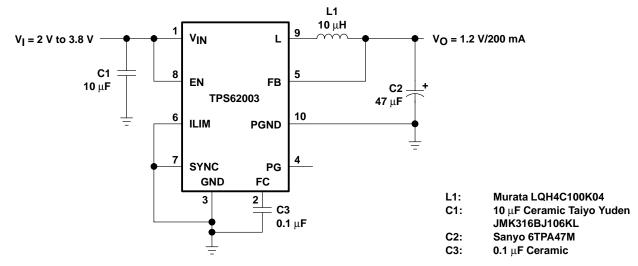

#### Figure 2. Typical Application Circuit for Fixed Output Voltage Option

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2002, Texas Instruments Incorporated

SLVS294B – SEPTEMBER 2000 – REVISED JUNE 2002

## description (continued)

The TPS6200x is a synchronous current-mode PWM converter with integrated N- and P-channel power MOSFET switches. Synchronous rectification is used to increase efficiency and to reduce external component count. To achieve the highest efficiency over a wide load current range, the converter enters a power-saving pulse-frequency modulation (PFM) mode at light load currents. Operating frequency is typically 750 kHz, allowing the use of small inductor and capacitor values. The device can be synchronized to an external clock signal in the range of 500 kHz to 1 MHz. For low-noise operation, the converter can be operated in the PWM mode and the internal antiringing switch reduces noise and EMI. In the shutdown mode, the current consumption is reduced to less than 1  $\mu$ A. The TPS6200x is available in the 10-pin (DGS) microsmall outline package (MSOP) and operates over a free-air temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C.

| Т             | VOLTAGE OPTIONS | PACKAGE                               |             |  |  |

|---------------|-----------------|---------------------------------------|-------------|--|--|

| TA            | VOLIAGE OF HONS | MICROSMALL OUTLINE (DGS) <sup>†</sup> | MARKING DGS |  |  |

|               | Adjustable      | TPS62000DGS                           | AIH         |  |  |

|               | 0.9 V           | TPS62001DGS                           | All         |  |  |

|               | 1 V             | TPS62002DGS                           | AIJ         |  |  |

|               | 1.2 V           | TPS62003DGS                           | AIK         |  |  |

| -40°C to 85°C | 1.5 V           | TPS62004DGS                           | AIL         |  |  |

|               | 1.8 V           | TPS62005DGS                           | AIM         |  |  |

|               | 1.9 V           | TPS62008DGS                           | AJI         |  |  |

|               | 2.5 V           | TPS62006DGS                           | AIN         |  |  |

|               | 3.3 V           | TPS62007DGS                           | AIO         |  |  |

#### **AVAILABLE OPTIONS**

<sup>†</sup> The DGS package is available taped and reeled. Add R suffix to device type (e.g. TPS62000DGSR) to order quantities of 2500 devices per reel.

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

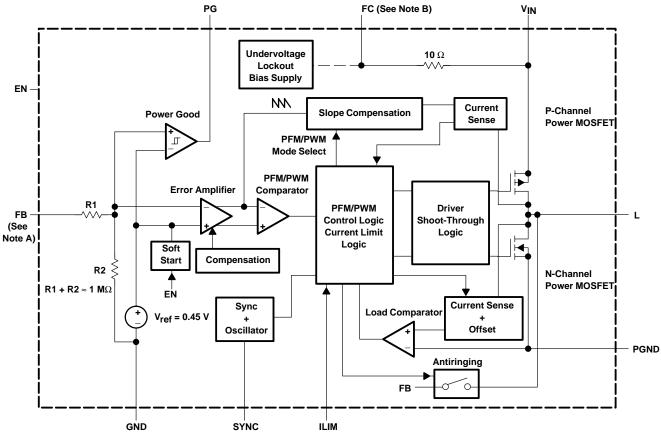

## functional block diagram

NOTES: A. The adjustable output voltage version does not use the internal feedback resistor divider. The FB pin is directly connected to the error amplifier.

B. Do not connect the FC pin to an external power source

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# **Terminal Functions**

| TERM         | INAL | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                         |

|--------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                         |

| EN           | 8    | I   | Enable. A logic high enables the converter, logic low forces the device into shutdown mode reducing the supply current to less than 1 $\mu$ A.                                                                                                                                                      |

| FB           | 5    | I   | Feedback pin for the fixed output voltage option. For the adjustable version an external resistive divider is connected to this pin. The internal voltage divider is disabled for the adjustable version.                                                                                           |

|              |      |     | Supply bypass pin. A 0.1 $\mu$ F coupling capacitor should be connected as close as possible to this pin for good high frequency input voltage supply filtering.                                                                                                                                    |

| GND 3 Ground |      |     | Ground                                                                                                                                                                                                                                                                                              |

| ILIM         | 6    | I   | Switch current limit. Connect ILIM to GND to set the switch current limit to typically 600 mA, or connect this pin to $V_{IN}$ to set the current limit to typically 1200 mA.                                                                                                                       |

| L            | 9    | I/O | Connect the inductor to this pin. This pin is the switch pin connected to the drain of the internal power MOSFETS.                                                                                                                                                                                  |

| PG           | 4    | 0   | Power good comparator output. This is an open-drain output. A pullup resistor should be connected between PG and $V_O$ . The output goes active high when the output voltage is greater than 94.5% of the nominal value.                                                                            |

| PGND         | 10   |     | Power ground. Connect all power grounds to this pin.                                                                                                                                                                                                                                                |

| SYNC         | 7    | I   | Input for synchronization to external clock signal. Synchronizes the converter switching frequency to an external clock signal with CMOS level:<br>SYNC = HIGH: Low-noise mode enabled, fixed frequency PWM operation is forced<br>SYNC = LOW (GND): Power save mode enabled, PFM/PWM mode enabled. |

| VIN          | 1    | I   | Supply voltage input                                                                                                                                                                                                                                                                                |

## detailed description

#### operation

The TPS6200x is a step down converter operating in a current mode PFM/PWM scheme with a typical switching frequency of 750 kHz.

At moderate to heavy loads, the converter operates in the pulse width modulation (PWM) and at light loads the converter enters a power save mode (pulse frequency modulation) to keep the efficiency high.

In the PWM mode operation, the part operates at a fixed frequency of 750 kHz. At the beginning of each clock cycle, the high side P-channel MOSFET is turned on. The current in the inductor ramps up and is sensed via an internal circuit. The high side switch is turned off when the sensed current causes the PFM/PWM comparator to trip when the output voltage is in regulation or when the inductor current reaches the current limit (set by ILIM). After a minimum dead time preventing shoot through current, the low side N-channel MOSFET is turned on and the current ramps down again. As the clock cycle is completed, the low side switch is turned off and the next clock cycle starts.

In discontinuous conduction mode (DCM), the inductor current ramps to zero before the end of each clock cycle. In order to increase the efficiency the load comparator turns off the low side MOSFET before the inductor current becomes negative. This prevents reverse current flowing from the output capacitor through the inductor and low side MOSFET to ground that would cause additional losses.

As the load current decreases and the peak inductor current does not reach the power save mode threshold of typically 120 mA for more than 15 clock cycles, the converter enters a pulse frequency modulation (PFM) mode.

In the PFM mode, the converter operates with:

- Variable frequency

- Constant peak current that reduces switching losses

- Quiescent current at a minimum

# TPS62000, TPS62001, TPS62002, TPS62003 TPS62004, TPS62005, TPS62006, TPS62007, TPS62008 HIGH-EFFICIENCY STEP-DOWN LOW POWER DC-DC CONVERTER SLVS294B – SEPTEMBER 2000 – REVISED JUNE 2002

#### operation (continued)

Thus maintaining the highest efficiency at light load currents. In this mode, the output voltage is monitored with the error amplifier. As soon as the output voltage falls below the nominal value, the high side switch is turned on and the inductor current ramps up. When the inductor current reaches the peak current of typical: 150 mA + 50 mA/V x ( $V_I - V_O$ ), the high side switch turns off and the low side switch turns on. As the inductor current ramps down, the low side switch is turned off before the inductor current becomes negative which completes the cycle. When the output voltage falls below the nominal voltage again, the next cycle is started.

The converter enters the PWM mode again as soon as the output voltage can not be maintained with the typical peak inductor current in the PFM mode.

The control loop is internally compensated reducing the amount of external components.

The switch current is internally sensed and the maximum current limit can be set to typical 600 mA by connecting ILIM to ground or to typically 1.2 A connecting ILIM to  $V_{IN}$ .

#### 100% duty cycle operation

As the input voltage approaches the output voltage and the duty cycle exceeds typical 95%, the converter turns the P-channel high side switch continuously on. In this mode, the output voltage is equal to the input voltage minus the voltage drop across the P-channel MOSFET.

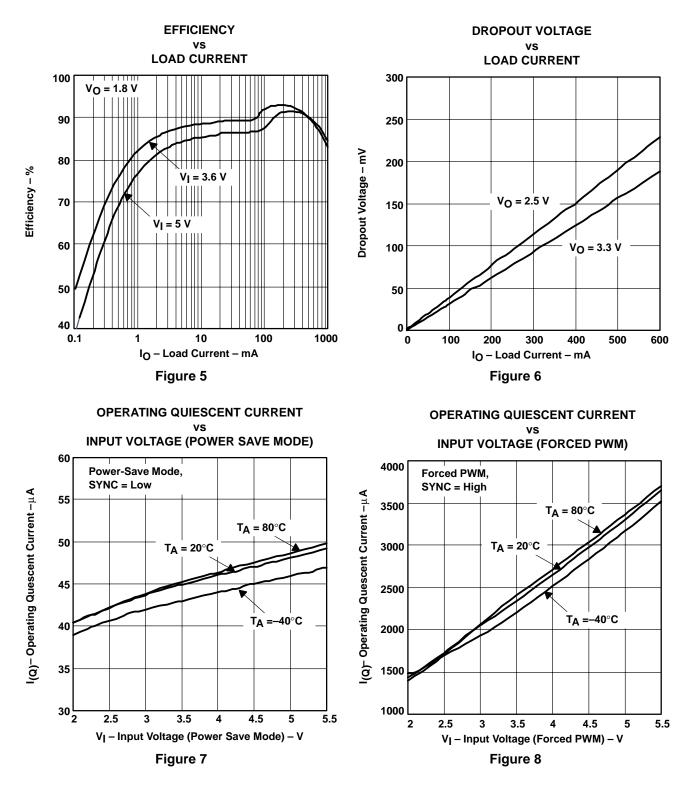

#### synchronization, power save mode and forced PWM mode

If no clock signal is applied, the converter operates with a typical switching frequency of 750 kHz. It is possible to synchronize the converter to an external clock within a frequency range from 500 kHz to 1000 kHz. The device automatically detects the rising edge of the first clock and is synchronizes immediately to the external clock. If the clock signal is stopped, the converter automatically switches back to the internal clock and continues operation without interruption. The switch over is initiated if no rising edge on the SYNC pin is detected for a duration of four clock cycles. Therefore, the maximum delay time can be 8 µs in case the internal clock has a minimum frequency of 500 kHz.

In case the device is synchronized to an external clock, the power save mode is disabled and the device stays in forced PWM mode.

Connecting the SYNC pin to the GND pin enables the power save mode. The converter operates in the PWM mode at moderate to heavy loads and in the PFM mode during light loads maintaining high efficiency over a wide load current range.

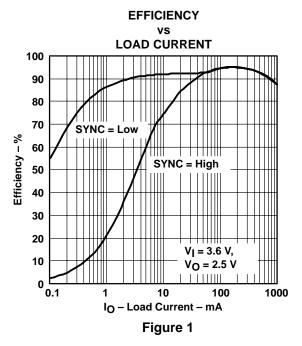

Connecting the SYNC pin to the  $V_{IN}$  pin forces the converter to operate permanently in the PWM mode even at light or no load currents. The advantage is the converter operates with a fixed switching frequency that allows simple filtering of the switching frequency for noise sensitive applications. In this mode, the efficiency is lower compared to the power save mode during light loads (see Figure 1).

It is possible to switch from forced PWM mode to the power save mode during operation.

The flexible configuration of the SYNC pin during operation of the device allows efficient power management by adjusting the operation of the TPS6200x to the specific system requirements.

#### low noise antiringing switch

An *antiringing* switch is implemented in order to reduce the EMI radiated from the converter during discontinuous conduction mode (DCM). In DCM, the inductor current ramps to zero before the end of each switching period. The internal load comparator turns off the low side switch at that instant thus preventing the current flowing backward through the inductance which increases the efficiency. An antiringing switch across the inductor prevents parasitic oscillation caused by the residual energy stored in the inductance (see Figure 12).

NOTE:

The *antiringing* switch is only activated in the fixed output voltage versions. It is not enabled for the adjustable output voltage version TPS62000.

## TPS62000, TPS62001, TPS62002, TPS62003 TPS62004, TPS62005, TPS62006, TPS62007, TPS62008 HIGH-EFFICIENCY STEP-DOWN LOW POWER DC-DC CONVERTER SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

### detailed description (continued)

#### soft start

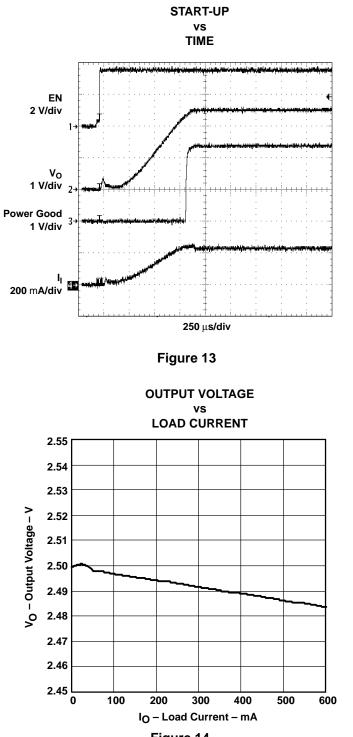

As the enable pin (EN) goes high, the soft-start function generates an internal voltage ramp. This causes the start-up current to slowly rise preventing output voltage overshoot and high inrush currents. The soft-start duration is typical 1 ms (see Figure 13). When the soft-start function is completed, the error amplifier is connected directly to the internal voltage reference.

#### enable

Logic low on EN forces the TPS6200x into shutdown. In shutdown, the power switch, drivers, voltage reference, oscillator, and all other functions are turned off. The supply current is reduced to less than 1 µA in the shutdown mode.

#### undervoltage lockout

An undervoltage lockout circuit provides the save operation of the device. It prevents the converter from turning on when the voltage on VIN is less than typically 1.6 V

#### power good comparator

The power good (PG) comparator has an open drain output capable of sinking typically 10  $\mu$ A. The PG is only active when the device is enabled (EN = high). When the device is disabled (EN = low), the PG pin is high impedance.

The PG output is only valid after a 100 µs delay after the device is enabled and the supply voltage is greater than 1.2 V. This is only important in cases where the pullup resistor of the PG pin is connected to an external voltage source which might cause an initial spike (false high signal) within the first 100 µs after the input voltage exceeds 1.2 V. This initial spike can be filtered with a small R-C filter to avoid false power good signals during start-up.

If the PG pin is connected to the output of the TPS62000 with a pullup resistor, no initial spike (false high signal) occurs and no precautions have to be taken during start-up.

The PG pin becomes active high when the output voltage exceeds typically 94.5% of its nominal value. Leave the PG pin unconnected when not used.

### no load operation

In case the converter operates in the forced PWM mode and there is no load connected to the output, the converter will regulate the output voltage by allowing the inductor current to reverse for a short period of time.

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Supply voltages on pin V <sub>IN</sub> and FC (see Note 1)                          |                                   |

|-------------------------------------------------------------------------------------|-----------------------------------|

| Voltages on pins EN, ILIM, SYNC, PG, FB, L (see Note 1)                             | –0.3 V to V <sub>IN</sub> + 0.3 V |

| Peak switch current                                                                 | 1.6 A                             |

| Continuous power dissipation                                                        | See Dissipation Rating Table      |

| Operating junction temperature range, T <sub>J</sub>                                |                                   |

| Storage temperature range, T <sub>stg</sub><br>Lead temperature (soldering, 10 sec) |                                   |

| Lead temperature (soldering, 10 sec)                                                | 260°C                             |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to network ground terminal.

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

| DISSIPATION RATING TABLE                                                            |                       |                                                |                                       |                                       |  |  |

|-------------------------------------------------------------------------------------|-----------------------|------------------------------------------------|---------------------------------------|---------------------------------------|--|--|

| $\begin{array}{c} T_{A} \leq 25^{\circ}\text{C} \\ \text{POWER RATING} \end{array}$ |                       | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |  |  |

| 10 pin MSOP                                                                         | 555 mW                | 5.56 mW/°C                                     | 305 mW                                | 221 mW                                |  |  |

| NOTE: Tho the                                                                       | rmal resistance junct | ion to ambient of the 10 n                     |                                       | The dovice does no                    |  |  |

NOTE: The thermal resistance junction to ambient of the 10-pin MSOP is 180°C/W. The device does not run into thermal limitations provided it is operated within the specified range.

# recommended operating conditions

|                                                                                                             | MIN | TYP | MAX | UNIT |

|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Supply voltage, VI                                                                                          | 2   |     | 5.5 | V    |

| Output voltage range for adjustable output voltage version, $V_{\mbox{O}}$                                  | 0.8 |     | Vj  | V    |

| Output current for 3-cell operation, IO (VI $\geq$ 2.5 V; L = 10 $\mu H,$ f = 750 kHz)                      |     |     | 600 | mA   |

| Output current for 2-cell operation, I <sub>O</sub> (V <sub>I</sub> $\ge$ 2 V; L = 10 $\mu$ H, f = 750 kHz) |     |     | 200 | mA   |

| Inductor, L (see Note 2)                                                                                    |     | 10  |     | μH   |

| Input capacitor, C <sub>i</sub> (see Note 2)                                                                | 10  |     |     | μF   |

| Output capacitor, $C_0$ (see Note 2) $V_0 \ge 1.8 V$ )                                                      | 10  |     |     | μF   |

| Output capacitor, $C_0$ (see Note 2) $V_0 < 1.8 V$ )                                                        | 47  |     |     | μF   |

| Operating ambient temperature, T <sub>A</sub>                                                               | -40 |     | 85  | °C   |

| Operating junction temperature, TJ                                                                          | -40 |     | 125 | °C   |

NOTE 2: Refer to application section for further information.

# electrical characteristics over recommended operating free-air temperature range, $V_I = 3.6 V_r$ , $V_0 = 2.5 \text{ V}, I_0 = 300 \text{ mA}, \text{EN} = V_{IN}, \text{ILIM} = V_{IN}, T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ (unless otherwise noted)}$

#### supply current

|                   | PARAMETER                   | TEST CONDITIONS                                      | MIN | TYP | MAX | UNIT |

|-------------------|-----------------------------|------------------------------------------------------|-----|-----|-----|------|

| VI                | Input voltage range         | I <sub>O</sub> = 0 mA to 600 mA                      | 2.5 |     | 5.5 | V    |

|                   |                             | I <sub>O</sub> = 0 mA to 200 mA                      | 2   |     | 5.5 |      |

| I <sub>(Q)</sub>  | Operating quiescent current | I <sub>O</sub> = 0 mA, SYNC = GND (PFM-mode enabled) |     | 50  | 75  | μA   |

| I <sub>(SD)</sub> | Shutdown current            | EN = GND                                             |     | 0.1 | 1   | μΑ   |

#### enable

|                  | PARAMETER                      | TEST CONDITIONS               | MIN | TYP  | MAX  | UNIT |

|------------------|--------------------------------|-------------------------------|-----|------|------|------|

| VIH              | EN high-level input voltage    |                               | 1.3 |      |      | V    |

| VIL              | EN low level input voltage     |                               |     |      | 0.4  | V    |

| l <sub>lkg</sub> | EN input leakage current       | $EN = GND \text{ or } V_{IN}$ |     | 0.01 | 0.1  | μA   |

| V(UVLO)          | Undervoltage lockout threshold |                               | 1.2 | 1.6  | 1.95 | V    |

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# electrical characteristics over recommended operating free-air temperature range, $V_I = 3.6 V$ , $V_O = 2.5 V$ , $I_O = 300 mA$ , $EN = V_{IN}$ , $ILIM = V_{IN}$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$ (unless otherwise noted) (continued)

#### power switch and current limit

|                                  | PARAMETER                      | TEST CONDITIONS                                                                            | MIN | TYP  | MAX  | UNIT  |

|----------------------------------|--------------------------------|--------------------------------------------------------------------------------------------|-----|------|------|-------|

|                                  | P-channel MOSFET on-resistance | $V_{I} = V_{GS} = 3.6 \text{ V},  I = 200 \text{ mA}$                                      | 200 | 280  | 410  | mΩ    |

| <sup>r</sup> DS(on)              | r-channel MOSFET on-resistance | $V_{I} = V_{GS} = 2 V$ , $I = 200 mA$                                                      |     | 480  |      | 11152 |

|                                  | P-channel leakage current      | V <sub>DS</sub> = 5.5 V                                                                    |     |      | 1    | μΑ    |

|                                  | N-channel MOSFET on-resistance | $V_{I} = V_{GS} = 3.6 \text{ V},  I_{O} = 200 \text{ mA}$                                  | 200 | 280  | 410  | mΩ    |

|                                  | N-channel MOSFET On-resistance | $V_I = V_{GS} = 2 V$ , $I_O = 200 \text{ mA}$                                              |     | 500  |      | 11152 |

|                                  | N-channel leakage current      | V <sub>DS</sub> = 5.5 V                                                                    |     |      | 1    | μΑ    |

| 14.00                            | P-channel current limit        | $2.5 \text{ V} \leq \text{V}_{I} \leq 5.5 \text{ V},  \text{ILIM} = \text{V}_{IN}$         | 800 | 1200 | 1600 | mA    |

| <sup>I</sup> (LIM)<br>VIH<br>VIL | P-channel current limit        | $2 \text{ V} \leq \text{V}_{\text{I}} \leq 5.5 \text{ V}, \qquad \text{ILIM} = \text{GND}$ | 390 | 600  | 900  | IIIA  |

| VIH                              | ILIM high-level input voltage  |                                                                                            | 1.3 |      |      | V     |

| VIL                              | ILIM low-level input voltage   |                                                                                            |     |      | 0.4  | V     |

| l <sub>lkg</sub>                 | ILIM input leakage current     | $ILIM = GND \text{ or } V_{IN}$                                                            |     | 0.01 | 0.1  | μA    |

### power good output (see Note 3)

|                   | PARAMETER                                    | TEST CONDITIONS                                                  | MIN       | TYP       | MAX       | UNIT |

|-------------------|----------------------------------------------|------------------------------------------------------------------|-----------|-----------|-----------|------|

| V <sub>(PG)</sub> | Power good threshold                         | Feedback voltage falling                                         | 88%<br>VO | 92%<br>VO | 94%<br>VO | V    |

|                   | Power good hysteresis                        |                                                                  | 2         | .5% VO    |           | V    |

| VOL               | PG output low voltage                        | $V_{(FB)} = 0.8 \times V_{O}$ nominal, $I_{(sink)} = 10 \ \mu A$ |           |           | 0.3       | V    |

| l <sub>lkg</sub>  | PG output leakage current                    | V <sub>(FB)</sub> = V <sub>O</sub> nominal                       |           | 0.01      | 1         | μΑ   |

| Minimur           | n supply voltage for valid power good signal |                                                                  | 1.2       |           |           | V    |

NOTE 3: Power good is not valid for the first 100 µs after EN goes high. Please refer to the application section for more information.

#### oscillator

|                  | PARAMETER                     | TEST CONDITIONS                     | MIN | TYP  | MAX  | UNIT |

|------------------|-------------------------------|-------------------------------------|-----|------|------|------|

| f <sub>S</sub>   | Oscillator frequency          |                                     | 500 | 750  | 1000 | kHz  |

| f(SYNC)          | Synchronization range         | CMOS-logic clock signal on SYNC pin | 500 |      | 1000 | kHz  |

| VIH              | SYNC high level input voltage |                                     | 1.3 |      |      | V    |

| VIL              | SYNC low level input voltage  |                                     |     |      | 0.4  | V    |

| l <sub>lkg</sub> | SYNC input leakage current    | SYNC = GND or $V_{IN}$              |     | 0.01 | 0.1  | μA   |

| Duty cycle       | e of external clock signal    |                                     | 20% |      | 60%  |      |

# TPS62000, TPS62001, TPS62002, TPS62003 TPS62004, TPS62005, TPS62006, TPS62007, TPS62008 HIGH-EFFICIENCY STÉP-DOWN LOW POWER DC-DC CONVERTER SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# electrical characteristics over recommended operating free-air temperature range, $V_I = 3.6 V$ , $V_O = 2.5 V$ , $I_O = 300 mA$ , $EN = V_{IN}$ , $ILIM = V_{IN}$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$ (unless otherwise noted) (continued)

| output |

|--------|

|--------|

|                                    | PARAMETER                         |                                                                | TEST CONDITIONS                                                        | MIN  | TYP  | MAX | UNIT |

|------------------------------------|-----------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|------|------|-----|------|

| Vo                                 | Adjustable output voltage range   | TPS62000                                                       |                                                                        | 0.8  |      | 5.5 | V    |

| V <sub>ref</sub>                   | Reference voltage                 | TPS6200x                                                       |                                                                        |      | 0.45 |     | V    |

| -                                  |                                   | TPS62000                                                       | VI = 2.5 V to 5.5 V; 0 mA $\leq$ IO $\leq$ 600 mA                      | -3%  |      | 4%  |      |

|                                    |                                   | adjustable                                                     | $10 \text{ mA} < I_{O} \le 600 \text{ mA}$                             | -3%  |      | 3%  |      |

|                                    |                                   | TPS62001                                                       | $V_I$ = 2.5 V to 5.5 V; 0 mA $\leq$ $I_O$ $\leq$ 600 mA                | -3%  |      | 4%  |      |

| V <sub>ref</sub><br>V <sub>O</sub> |                                   | 0.9 V                                                          | $10 \text{ mA} < I_{O} \le 600 \text{ mA}$                             | -3%  |      | 3%  |      |

|                                    |                                   | TPS62002                                                       | $V_I$ = 2.5 V to 5.5 V; 0 mA $\leq$ $I_O$ $\leq$ 600 mA                | -3%  |      | 4%  |      |

|                                    |                                   | 1 V                                                            | $10 \text{ mA} < I_{O} \le 600 \text{ mA}$                             | -3%  |      | 3%  |      |

|                                    |                                   | TPS62003                                                       | $V_I$ = 2.5 V to 5.5 V; 0 mA $\leq$ $I_O$ $\leq$ 600 mA                | -3%  |      | 4%  |      |

|                                    |                                   | 1.2 V                                                          | $10 \text{ mA} < I_{O} \le 600 \text{ mA}$                             | -3%  |      | 3%  |      |

|                                    | Fixed output voltage (see Note 4) | TPS62004<br>1.5 V                                              | $V_I$ = 2.5 V to 5.5 V; 0 mA $\leq$ $I_O$ $\leq$ 600 mA                | -3%  |      | 4%  | v    |

| ۷V                                 |                                   |                                                                | $10 \text{ mA} < I_{O} \leq 600 \text{ mA}$                            | -3%  |      | 3%  |      |

|                                    |                                   | TPS62005<br>1.8 V                                              | $V_I$ = 2.5 V to 5.5 V; 0 mA $\leq$ $I_O$ $\leq$ 600 mA                | -3%  |      | 4%  |      |

|                                    |                                   |                                                                | $10 \text{ mA} < I_{O} \le 600 \text{ mA}$                             | -3%  |      | 3%  |      |

|                                    |                                   | TPS62008<br>1.9 V                                              | $V_I$ = 2.5 V to 5.5 V; 0 mA $\leq$ $I_O$ $\leq$ 600 mA                | -3%  |      | 4%  |      |

|                                    |                                   |                                                                | $10 \text{ mA} < I_{O} \le 600 \text{ mA}$                             | -3%  |      | 3%  |      |

|                                    |                                   | TPS62006<br>2.5 V                                              | $V_I$ = 2.7 V to 5.5 V; 0 mA $\leq$ $I_O$ $\leq$ 600 mA                | -3%  |      | 4%  |      |

|                                    |                                   |                                                                | $10 \text{ mA} < I_{O} \le 600 \text{ mA}$                             | -3%  |      | 3%  |      |

|                                    |                                   | TPS62007                                                       | $V_I$ = 3.6 V to 5.5 V; 0 mA $\leq$ $I_O$ $\leq$ 600 mA                | -3%  |      | 4%  |      |

|                                    |                                   | 3.3 V                                                          | $10 \text{ mA} < I_{O} \le 600 \text{ mA}$                             | -3%  |      | 3%  |      |

| Line regulation                    |                                   | $V_{I}$ = $V_{O}$ + 0.5 V (min. 2 V) to 5.5 V, $I_{O}$ = 10 mA |                                                                        | 0.05 |      | %/V |      |

| Load re                            | egulation                         |                                                                | $V_{I} = 5.5 \text{ V}; I_{O} = 10 \text{ mA to } 600 \text{ mA}$      |      | 0.6% |     |      |

|                                    | Efficiency                        |                                                                | $V_{I} = 5 V; V_{O} = 3.3 V; I_{O} = 300 \text{ mA}$                   |      | 05%  |     |      |

| η                                  | Efficiency                        |                                                                | $V_{I} = 3.6 \text{ V}; V_{O} = 2.5 \text{ V}; I_{O} = 200 \text{ mA}$ |      | 95%  |     |      |

| Start-u                            | p time                            |                                                                | $I_{O} = 0$ mA, time from active EN to $V_{O}$                         | 0.4  |      | 2   | ms   |

NOTE 4: The output voltage accuracy includes line and load regulation over the full temperature range,  $T_A = -40^{\circ}C$  to 85°C.

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

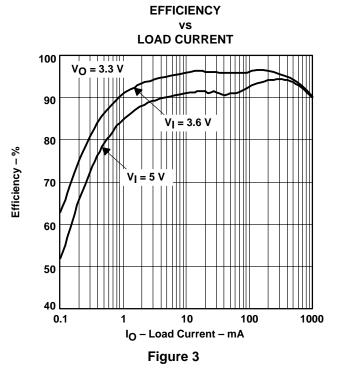

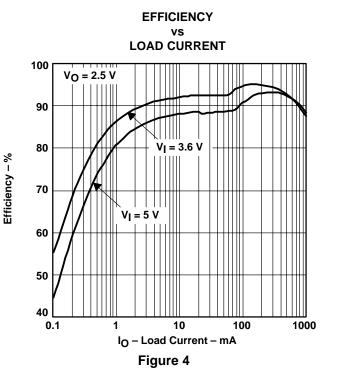

# **TYPICAL CHARACTERISTICS**

# **Table of Graphs**

|                     |                             |                                    | FIGURE  |

|---------------------|-----------------------------|------------------------------------|---------|

| η                   | Efficiency                  | vs Load current                    | 3, 4, 5 |

| V <sub>(drop)</sub> | Dropout voltage             | vs Load current                    | 6       |

| IQ                  | Operating quiescent current | vs Input voltage (power save mode) | 7       |

|                     | Operating quiescent cuffent | vs Input voltage (forced PWM)      | 8       |

| f <sub>osc</sub>    | Oscillator frequency        | vs Free-air temperature            | 9       |

|                     | Load transient response     |                                    | 10      |

|                     | Line transient response     |                                    | 11      |

|                     | Power save mode operation   |                                    | 12      |

|                     | Start-up                    | vs Time                            | 13      |

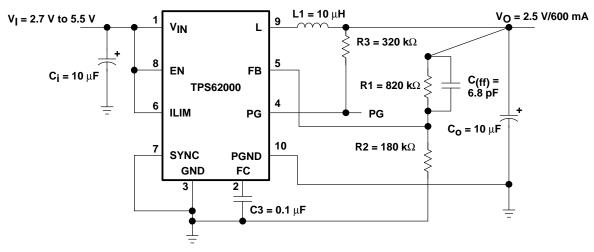

| VO                  | Output voltage              | vs Load current                    | 14      |

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# **TYPICAL CHARACTERISTICS**

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# **TYPICAL CHARACTERISTICS**

# TPS62000, TPS62001, TPS62002, TPS62003 TPS62004, TPS62005, TPS62006, TPS62007, TPS62008 HIGH-EFFICIENCY STEP-DOWN LOW POWER DC-DC CONVERTER SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# **TYPICAL CHARACTERISTICS**

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# **APPLICATION INFORMATION**

## adjustable output voltage version

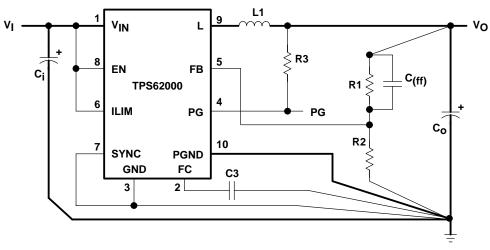

When the adjustable output voltage version (TPS62000DGS) is used, the output voltage is set by the external resistor divider (see Figure 15).

The output voltage is calculated as:

$$V_{O} = 0.45 V \times \left(1 + \frac{R1}{R2}\right)$$

With R1 + R2  $\leq$  1  $M\Omega$

R1 + R2 should not be greater than 1 M $\Omega$  because of stability reasons.

For stability reasons, a small bypass capacitor ( $C_{ff}$ ) is required in parallel to the upper feedback resistor, refer to Figure 15. The bypass capacitor value can be calculated as:

$$C_{\text{(ff)}} = \frac{1}{2\pi \text{ x } 30000 \text{ x } \text{R1}} \text{ for } C_{\text{o}} < 47 \text{ } \mu\text{F}$$

$$C_{\text{(ff)}} = \frac{1}{2\pi \text{ x } 5000 \text{ x } \text{R1}} \text{ for } C_{\text{o}} \ge 47 \text{ } \mu\text{F}$$

R1 is the upper resistor of the voltage divider. For  $C_{(ff)}$ , choose a value which comes closest to the computed result.

Figure 15. Typical Application Circuit for Adjustable Output Voltage Option

## inductor selection

A 10  $\mu$ H minimum output inductor is used with the TPS6200x. Values larger than 22  $\mu$ H or smaller than 10  $\mu$ H may cause stability problems because of the internal compensation of the regulator.

For output voltages greater than 1.8 V, a 22  $\mu$ H inductance might be used in order to improve the efficiency of the converter.

After choosing the inductor value of typically 10  $\mu$ H, two additional inductor parameters should be considered: first the current rating of the inductor and second the dc resistance.

The dc resistance of the inductance influences directly the efficiency of the converter. Therefore, an inductor with lowest dc resistance should be selected for highest efficiency.

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# **APPLICATION INFORMATION**

## inductor selection (continued)

In order to avoid saturation of the inductor, the inductor should be rated at least for the maximum output current plus the inductor ripple current which is calculated as:

$$\Delta I_{L} = V_{O} \times \frac{1 - \frac{V_{O}}{V_{I}}}{L \times f} \qquad \qquad I_{L(max)} = I_{O(max)} + \frac{\Delta I_{L}}{2}$$

Where:

f = Switching frequency (750 kHz typical)

L = Inductor value

$\Delta I_{I}$  = Peak-to-peak inductor ripple current

I<sub>L(max)</sub> = Maximum inductor current

The highest inductor current occurs at maximum V<sub>I</sub>.

A more conservative approach is to select the inductor current rating just for the maximum switch current of the TPS6200x which is 1.6 A with ILIM = V<sub>IN</sub> and 900 mA with ILIM = GND. See table 1 for recommended inductors.

| OUTPUT CURRENT | INDUCTOR VALUE | COMPONENT SUPPLIER                                                                         | COMMENTS          |

|----------------|----------------|--------------------------------------------------------------------------------------------|-------------------|

| 0 mA to 600 mA | 10 μH          | Coilcraft DO3316P-103<br>Coilcraft DT3316P-103<br>Sumida CDR63B-100<br>Sumida CDRH5D28-100 | High efficiency   |

|                |                | Coilcraft DO1608C-100<br>Sumida CDRH4D28-100                                               | Smallest solution |

| 0 mA to 300 mA | 10 µH          | Coilcraft DS1608C-103                                                                      | High efficiency   |

|                |                | muRata LQH4C100K04                                                                         | Smallest solution |

Table 1. Recommended Inductors

#### output capacitor selection

For best performance, a low ESR output capacitor is needed. At output voltages greater than 1.8 V, ceramic output capacitors can be used to show the best performance. Output voltages below 1.8 V require a larger output capacitor and ESR value to improve the performance and stability of the converter.

## **Capacitor Selection**

| OUTPUT VOLTAGE RANGE                               | OUTPUT CAPACITOR     | OUTPUT CAPACITOR ESR                  |

|----------------------------------------------------|----------------------|---------------------------------------|

| $1.8 \text{ V} \leq \text{V}_I \leq 5.5 \text{ V}$ | $C_0 \ge 10 \ \mu F$ | $\text{ESR} \leq 120 \text{ m}\Omega$ |

| $0.8 \text{ V} \le \text{V}_{I} < 1.8 \text{ V}$   | $C_0 \ge 47 \ \mu F$ | ESR > 50 mΩ                           |

See Table 2 for recommended capacitors.

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# APPLICATION INFORMATION

### output capacitor selection (continued)

If an output capacitor is selected with an ESR value  $\leq$  120 m $\Omega$ , its RMS ripple current rating always meets the application requirements. Just for completeness, the RMS ripple current is calculated as:

$$I_{\text{RMS}(C_0)} = V_0 \times \frac{1 - \frac{V_0}{V_1}}{L \times f} \times \frac{1}{2 \times \sqrt{3}}$$

The overall output ripple voltage is the sum of the voltage spike caused by the output capacitor ESR plus the voltage ripple caused by charge and discharging the output capacitor:

$$\Delta V_{O} = V_{O} \times \frac{1 - \frac{V_{O}}{V_{I}}}{L \times f} \times \left(\frac{1}{8 \times C_{O} \times f} + ESR\right)$$

Where the highest output voltage ripple occurs at the highest input voltage VI.

| CAPACITOR VALUE | $\mathbf{ESR/m}\Omega$ | COMPONENT SUPPLIER           | COMMENTS |

|-----------------|------------------------|------------------------------|----------|

| 10 μF           | 50                     | Taiyo Yuden<br>JMK316BJ106KL | Ceramic  |

| 47 μF           | 100                    | Sanyo 6TPA47M                | POSCAP   |

| 68 μF           | 100                    | Spraque<br>594D686X0010C2T   | Tantalum |

**Table 2. Recommended Capacitors**

#### input capacitor selection

Because of the nature of the buck converter having a pulsating input current, a low ESR input capacitor is required for best input voltage filtering and minimizing the interference with other circuits caused by high input voltage spikes.

The input capacitor should have a minimum value of  $10 \,\mu$ F and can be increased without any limit for better input voltage filtering.

The input capacitor should be rated for the maximum input ripple current calculated as:

$$I_{RMS} = I_{O(max)} \times \sqrt{\frac{V_{O}}{V_{I}} \times \left(1 - \frac{V_{O}}{V_{I}}\right)}$$

The worst case RMS ripple current occurs at D = 0.5 and is calculated as:  $I_{RMS} = \frac{I_O}{2}$ .

Ceramic capacitor show a good performance because of their low ESR value, and they are less sensitive against voltage transients compared to tantalum capacitors.

Place the input capacitor as close as possible to the input pin of the IC for best performance.

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# **APPLICATION INFORMATION**

## layout considerations

As for all switching power supplies, the layout is an important step in the design especially at high peak currents and switching frequencies. If the layout is not carefully done, the regulator might show stability problems as well as EMI problems.

Therefore, use wide and short traces for the main current paths as indicted in bold in Figure 16. The input capacitor should be placed as close as possible to the IC pins as well as the inductor and output capacitor. Place the bypass capacitor, C3, as close as possible to the FC pin. The analog ground, GND, and the power ground, PGND, need to be separated. Use a common ground node as shown in Figure 16 to minimize the effects of ground noise.

Figure 16. Layout Diagram

typical application

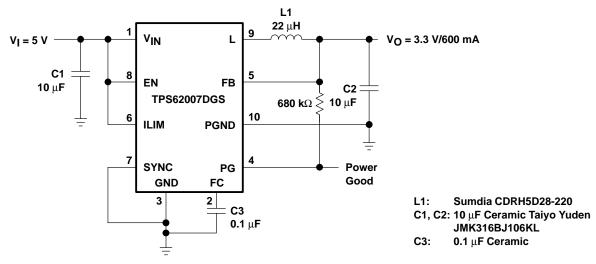

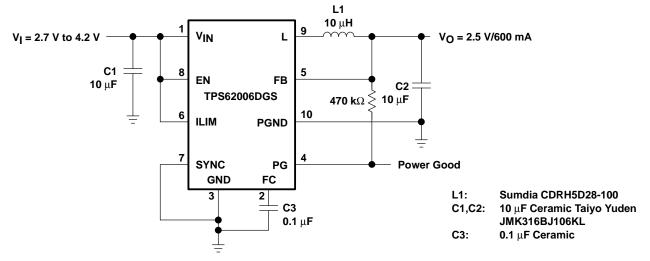

Figure 17. Standard 5 V to 3.3 V/600 mA Conversion; High Efficiency

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

## **APPLICATION INFORMATION**

## typical application (continued)

NOTE: For low noise operation connect SYNC to VIN

SLVS294B - SEPTEMBER 2000 - REVISED JUNE 2002

# **APPLICATION INFORMATION**

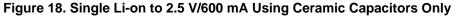

### typical application (continued)

Figure 20. Dual Cell NiMH or NiCd to 1.2 V/200 mA; Smallest Solution Size

<sup>‡</sup>A large value is used for C<sub>(ff)</sub> to compensate for the parasitic capacitance introduced into the regulation loop by Q1.

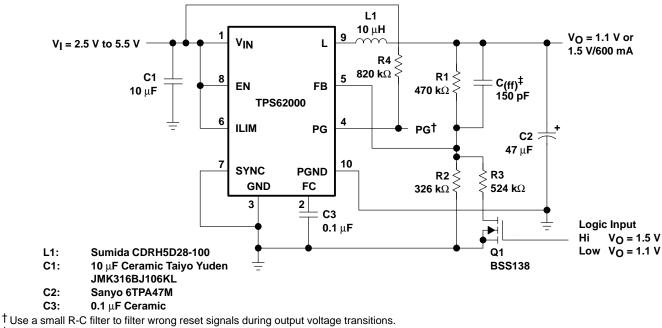

#### Figure 21. Dynamic Output Voltage Programming As Used in Low Power DSP Applications

SLVS294B – SEPTEMBER 2000 – REVISED JUNE 2002

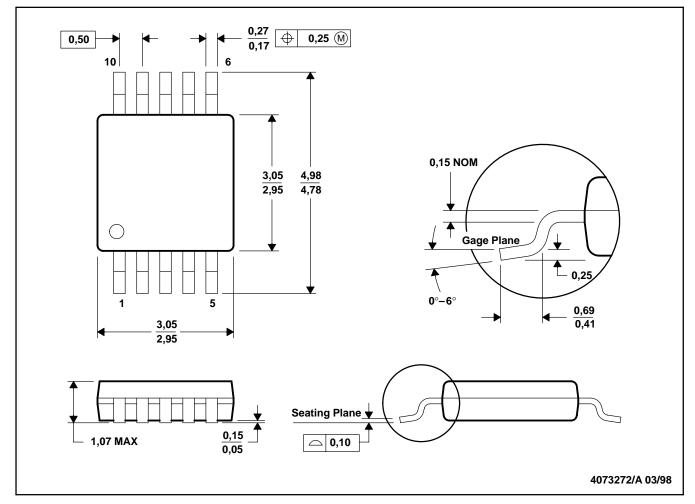

MECHANICAL DATA

### DGS (S-PDSO-G10)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated