Data sheet acquired from Harris Semiconductor

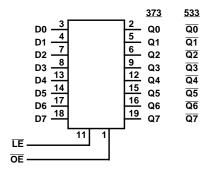

CD54/74FCT373, CD54/74FCT373AT, CD54/74FCT533

FCT Interface Logic Octal Transparent Latch, Three-State

February 1996

## **Features**

- CD54/74FCT373, CD54/74FCT373AT Non-Inverting

- CD54/74FCT533 Inverting

- Buffered inputs

- Typical Propagation Delay: 3.9ns at VCC = 5V, TA = +25°C, CL = 50pF (FCT373AT)

- SCR-Latchup-Resistant BiCMOS Process and Circuit Design

- FCTXXX Types Speed of Bipolar FAST®/AS/S;

FCTXXXAT Types 30% Faster than FAST/AS/S with Significantly Reduced Power Consumption

- 48mA to 32mA Output Sink Current (Commercial/ Extended Industrial)

- Output Voltage Swing Limited to 3.7V at VCC = 5V

- · Controlled Output-Edge Rates

- Input/Output Isolation to VCC

- BiCMOS Technology with Low Quiescent Power

## Description

The CD54/74FCT373, 373AT, and 533 octal transparent latches use a small-geometry BiCMOS technology. The output stage is a combination of bipolar and CMOS transistors that limits the output-HIGH level to two diode drops below VCC. This resultant lowering of output swing (0V to 3.7V) reduces power bus ringing (a source of EMI) and minimizes VCC bounce and ground bounce and their effects during simultaneous output switching. The output configuration also enhances switching speed and is capable of sinking 32mA to 48mA.

The CD54/74FCT373, 373AT, and 533 outputs are transparent to the inputs when the Latch Enable ( $\overline{\text{LE}}$ ) is HIGH. When the Latch Enable ( $\overline{\text{DE}}$ ) goes LOW, the data is latched. The Output Enable ( $\overline{\text{OE}}$ ) controls the three-state outputs. When the Output Enable ( $\overline{\text{OE}}$ ) is HIGH, the outputs are in the high-impedance state. The latch operation is independent of the state of the Output Enable.

## **Ordering Information**

| PART NUMBER      | TEMP. RANGE (°C)    | PACKAGE    |

|------------------|---------------------|------------|

| CD54/74FCT373E   | -55 to 125, 0 to 70 | 20 Ld PDIP |

| CD54/74FCT373ATE | -55 to 125, 0 to 70 | 20 Ld PDIP |

| CD54/74FCT533E   | -55 to 125, 0 to 70 | 20 Ld PDIP |

| CD54/74FCT373M   | -55 to 125, 0 to 70 | 20 Ld SOIC |

| CD54/74FCT373ATM | -55 to 125, 0 to 70 | 20 Ld SOIC |

| CD54/74FCT533M   | -55 to 125, 0 to 70 | 20 Ld SOIC |

| CD54/74FCT373SM  | -55 to 125, 0 to 70 | 20 Ld SSOP |

| CD54/74FCT533SM  | -55 to 125, 0 to 70 | 20 Ld SSOP |

| CD54FCT373H      | -55 to 125          |            |

| CD54FCT533H      | -55 to 125          |            |

# **Functional Diagram**

### **TRUTH TABLE**

| OUTPUT<br>ENABLE | LATCH<br>ENABLE | DATA | 373,373AT<br>OUTPUT | 533<br>OUTPUT |

|------------------|-----------------|------|---------------------|---------------|

| L                | Н               | Н    | Н                   | L             |

| L                | Н               | L    | L                   | Н             |

| L                | L               | 1    | L                   | Н             |

| L                | L               | h    | Н                   | L             |

| Н                | Х               | Х    | Z                   | Z             |

H = HIGH voltage level.

L = LOW voltage level.

X = Irrelevant.Z = HIGH Impedance.

I = LOW voltage level one setup time prior to the high-to-low latch enable transition.

transition

h = HIGH voltage level one setup time prior to the high-to-low latch enable transition.

FAST® is a registered trademark of Fairchild Semiconductor Corporation.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated