# SONY®

# **CXA1203M/N**

# 8mm VCR PAL JOG

#### Description

The CXA1203 compensates the color alignment in variable speed mode for PAL-system 8 mm VCRs. This IC is also available for the SECAM system with the built-in SECAM detector and BELL and C-BELL filters.

#### **Features**

- Color alignment compensation which does not require 1H delay line

- No AFC (fH) adjustment necessary

- · Built-in SECAM detector

- Built-in BELL and C-BELL filters

- · Available for the PAL-M system

V-Invert circuit, TH/DL APC, 2 fsc PLL, SQ DET, EX burst circuit, AFC (fH), Timing generator, SECAM detector, BELL filter, C-BELL filter.

#### Structure

Silicon monolithic IC

#### Absolute Maximum Ratings (Ta = 25°C)

Supply voltage

Operating temperature

Storage temperature

Topr - 20 to +75 °C

Tstg - 55 to +150 °C

Allowable power

dissipation Pb CXA1203M 567 mW CXA1203N 536 mW

### **Recommended Operating Conditions**

• Supply voltage 4.50 to 5.50 V (5.0 V Typ.)

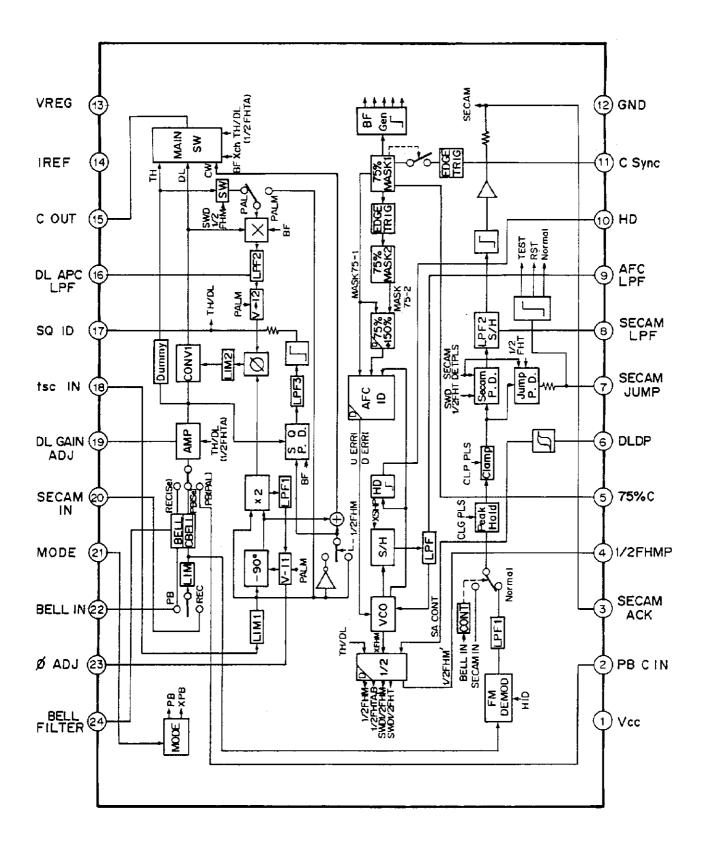

## Block Diagram and Pin Configuration

# Pin Description

| No.   | Symbol       |                          | age                             | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                        |

|-------|--------------|--------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| , 10. |              | DC                       | AC                              | equitation and an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 000/10/10/1                                                                                                                                                                                        |

| 1     | Vcc          | 5.0 V<br>(typical)       | _                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Supply voltage pin                                                                                                                                                                                 |

| 2     | PB C<br>IN   |                          | 350mVp-p<br>150mVp-p<br>(burst) | 2 → PR 47k → 60k → 60k → 15.2p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input pin of PAL playback chrominance signal. The chroma ACK operates to cut off the output at pin 15 when the DC bias voltage at pin 2 is 0.7 V or less.                                          |

| 3     | SECAM<br>ACK | 3.8V<br>(H)<br>OV<br>(L) | _                               | 3 # # # # # # # # # # # # # # # # # # #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SECAM detector output pin.  H → SECAM  L → PAL  The SECAM or PAL mode is fixed by applying an external DC voltage.  SECAM: 3.0 to 5.0 V  PAL: 0 to 1.0 V                                           |

| 4     | 1/2FHMP      |                          | 3.2V<br>1.7V                    | Vcc (x2)   (x2) | Output pin of the pulse obtained by dividing down the AFC (fH-PLL) output by 2.                                                                                                                    |

| 5     | 75% C        |                          | 3.5V<br>1.0V                    | Vcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Connecting pin of the charging and discharging capacity to produce the triangular wave chronized with the C sync signal.  All timing pulses used in the IC are produced from this triangular wave. |

| No. | Symbol        |                            | tage           | Equivalent circuit                      | Description                                                                                                                                                                                         |

|-----|---------------|----------------------------|----------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | DLDP          | 2.8V<br>(H)<br>1.4V<br>(L) | 1.4Vp-p        | 6 PR Bk                                 | Input pin to switch the polarity of the 1/2 FHT pulse for the SECAM detector.  Ouptut pin of the AFC ID signal in TEST mode*1                                                                       |

| 7   | SECAM<br>JUMP | 2.8V<br>(H)<br>1.4V<br>(L) | 1.4Vp-p        | 7 PR 20k \$ 20k 10k 10k 10k             | Output pin to switch the polarity of the 1/2 FHT pulse.  Mode selection*1 is possible by applying an external DC voltage.  PAL-M: 0 to 0.5 V  Normal: OPEN  RESET: 3.6 to 4.1 V  TEST: 4.3 to 5.0 V |

| 8   | SECAM<br>LPF  | 2.5V                       | _              | Vcc                                     | Connecting pin of the time constant of the LPF for the SECAM detector.                                                                                                                              |

| 9   | AFC<br>LPF    | 2.0V                       | _              | 9  Vcc  Vcc  W  Sub  Sub  (X2)  W  (X2) | Connecting pin of the time constant of the LPF for the AFC (fH-PLL).                                                                                                                                |

| 10  | HD            | _                          | 4.0 V<br>0.4 V | Vcc (x2)                                | Output pin of the HD pulse produced in the AFC (fH-PLL).                                                                                                                                            |

| No. | Symbol       | Volt | age                                               | Equivalent circuit                          | Description                                                                                                                                   |

|-----|--------------|------|---------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | C Sync       | DC   | AC                                                | Equivalent circuit                          | Input pin of the composite sync signal.  The internal threshold voltage is 2.0 V and the polarity is active HIGH.                             |

| 12  | GND          | _    |                                                   |                                             | GND pin                                                                                                                                       |

| 13  | VREG         | 4.2V | _                                                 | 13 (x32)  Connected to about 30 elements    | Output pin of the regulated voltage source in the IC (4.2 V).                                                                                 |

| 14  | IREF         | 2.1V |                                                   | Sk ¥ 40k  Vcc  (Sub)  REF  44k  M  M  M     | Connecting pin of the standard resistance to produce the reference current source in the IC.                                                  |

| 15  | с очт        | 2.1V | In PAL<br>mode<br>350mVp-p<br>150mVp-p<br>(burst) | Vcc (x4) (x4) (x4) (x4) (x4) (x4) (x4) (x4) | Output pin of the playback PAL signal (TH, DL and EX burst)* <sup>2</sup> , SECAM signal and PAL-M signal.                                    |

| 16  | DLAPC<br>LPF | 2.4V |                                                   | VCC<br>IS PR                                | Connecting pin of the time constant of the LPF for the TH/DL APC loop. The TH/DL lock phase can be varied by applying an external DC current. |

|     | 0 1 1          | Volt                     | age                 | Equivalent airquit                  | 6                                                                                                                                                                                          |

|-----|----------------|--------------------------|---------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Symbol         | DC                       | AC                  | Equivalent circuit                  | Description                                                                                                                                                                                |

| 17  | SQ ID          | 4.0V<br>(H)<br>0V<br>(L) |                     | Vcc   Sub)                          | Output pin of the SQ detector The TH or DL output signal at pin 15 can be selected by applying an external DC voltage. DL: 0 to 2.0 V TH: 3.0 to 5.0 V                                     |

| 18  | fsc IN         | _                        | 350mVp-p            | PR 10.4P    18                      | Input pin of the fsc.<br>(chrominance subcarrier)                                                                                                                                          |

| 19  | DL GAIN<br>ADJ | 5.0V<br>(Typ.)           |                     | 9 PR 13.4k \$13.4k                  | Control pin of the DL signal gain. The gain can be varied by applying an external DC voltage. The internally fixed gain is obtained at 5.0 V.  Output pin of the S/H circuit in TEST mode. |

| 20  | SECAM<br>IN    | _                        | 150mVp-p<br>(burst) | Vcc   15.2P 40k   20k   20k   7/1/2 | Input pin of the SECAM detector in REC mode.                                                                                                                                               |

| No. | Symbol         |                   | age                                                       | Equivalent circuit                               | Description                                                                                                                                                              |

|-----|----------------|-------------------|-----------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | MODE           | DC -              | AC                                                        | Vcc   Sub)                                       | Mode selection*1 is possible by applying an external DC voltage.  REC: 0 to 1.3 V PB: 1.7 to 2.8 V JOG: 3.2 to 5.0 V                                                     |

| 22  | BELL<br>IN     | _                 | 83mVp-p<br>(SECAM<br>burst)<br>117mVp-p<br>(PAL<br>burst) | VCC 15.2P 4k 15.2P ₹13.5k 15.2P ₹13.5k 100k ₹39k | Input pin of the SECAM signal. Input pin of the SECAM detector in playback mode.                                                                                         |

| 23  | φADJ           | 5.0V<br>(typical) | _                                                         | (Sub)  38k 39k (X2)                              | EX burst phase adjustment pin. The phase can be varied by applying an external DC voltage. The internally fixed phase is obtained at 5.0 V. VCO output pin in TEST mode. |

| 24  | BELL<br>FILTER | 3.0V              | _                                                         | 200 (X2) (X2) (X3) (X3)                          | Connecting pin of the time constant of the BELL and C-BELL filters.                                                                                                      |

Note) \*1. Refer to Mode Description.

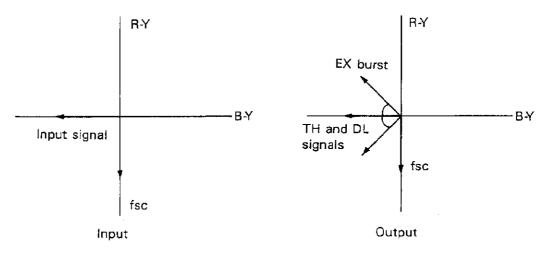

\*2. PAL playback signal (TH, DL and EX burst)

The DL signal is symmetrical to the TH signal (PAL playback signal) about the B-Y axis. The burst signal produced from the fsc (chrominance subcarrier) in the IC is known as the EX burst. The EX burst is inserted into the playback chrominance signal in JOG mode.

## **Mode Description**

| Mode  | Control<br>pin | Voltage        | Description                                                                                                     |  |  |

|-------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| PAL   |                | 0 to 1.0 V     | Fixed PAL mode                                                                                                  |  |  |

|       | 3 pin          | High impedance | Automatic selection of PAL or SECAM                                                                             |  |  |

| SECAM |                | 3.0 to 5.0 V   | Fixed SECAM mode                                                                                                |  |  |

| PAL-M |                | 0 to 0.5 V     | The PAL-M signal is output from pin 15 by inputting an NTSC signal to pin 2. (For details, see "Notes on Use".) |  |  |

| RESET | 7 pin          | 3.6 to 4.1 V   | The logic block (AFC ID, 150% masking and 1/2 division) in the AFC (fH-PLL) is turned off.                      |  |  |

| TEST  |                | 4.3 to 5.0 V   | The operation of the AFC ID, VCO and S/H blocks in the AFC (fH-PLL) is checked.                                 |  |  |

| DL    |                | 0 to 2.0 V     | The DL signal is output from pin 15.                                                                            |  |  |

| _     | 17 pin         | High impedance | The TH or DL signal selected by the SQ detector decision is output.                                             |  |  |

| TH    |                | 3.0 to 5.0 V   | The TH signal is output from pin 15.                                                                            |  |  |

| REC   |                | 0 to 1.3 V     | REC mode                                                                                                        |  |  |

| PB    | 21 pin         | 1.7 to 2.8 V   | Playback mode                                                                                                   |  |  |

| JOG   | •              | 3.2 to 5.0 V   | The EX burst is inserted into the original burst signal portion in PAL playback mode.                           |  |  |

See Fig.1. Ta = 25 °C, Vcc = 5.0V

|   | ņ        |

|---|----------|

|   | Ĭ        |

| • | Ë        |

|   | ï        |

|   | ğ        |

|   | 2        |

|   | 3        |

|   | c<br>c   |

|   | E        |

|   | <u>e</u> |

|    |                                                          |                            |     |                |                                       |              | ŀ   |          |              |                |          |          | ŀ           |             |              |                                  |            | -       | -           | L      |

|----|----------------------------------------------------------|----------------------------|-----|----------------|---------------------------------------|--------------|-----|----------|--------------|----------------|----------|----------|-------------|-------------|--------------|----------------------------------|------------|---------|-------------|--------|

| ź  | \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ | Cymphol                    | o g | witch<br>I: O, | Switch Condition<br>ON: O, OFF: blank | dition       | ايد |          | 83           | Bias Condition | ndition  |          |             | Test        | Output Wav   | Output Waveform and Test Content | ntent Min  |         |             | House  |

| G  | <u> </u>                                                 |                            | SW- | SW<br>2        | SW SW SW SW SW 1 2 3 4 5              | Sw<br>4      |     | οc       | ٧2           | ۸3             | ۲,       | ۷۱٫      | ٧2،         | Point       | Mode         |                                  |            |         |             |        |

| -  | Circuit Current<br>(PAL PB)                              | lcc (PP)                   |     |                |                                       |              |     | 5.00     | 2.5V         | 1.00           |          |          | 1.7v        | A           | PAL PB       | Of Australia                     | 17.5       | 25.     | 5 32.5      | тA     |

| 2  | Circuit Current<br>(SECAM REC)                           | loc (SR)                   |     |                |                                       | <del>-</del> |     | -        | <b>→</b>     | 3.00           |          |          | 1.3V        | ¥           | SECAM<br>REC |                                  | 20.0       | 0 27.0  | 34.0        | Ę      |

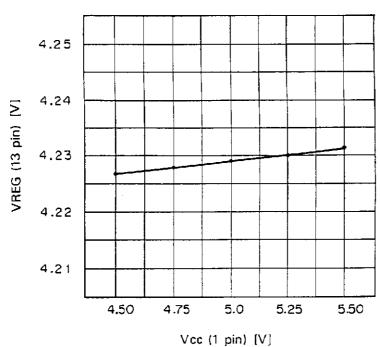

| 3  | VREG (5.0V)                                              | VREG<br>(5.0)              |     |                |                                       |              |     | -        | <b>→</b>     | 1.0V           |          |          | 1.7V        | Е           |              |                                  | 4.10       | 0 4.24  | 4.40        | >      |

| 4  | VREG (4.5V)                                              | VREG<br>(4.5)              |     |                |                                       | -            |     | 4.50     | <b>→</b>     | <b>→</b>       |          |          | -           | <b>-</b>    | 00 190       | 100 tool on 70                   | 4.10       | 0 4.24  | 4 4.40      | >      |

| co | VREG (5.5V)                                              | VREG<br>(5.5)              |     |                | <u> </u>                              |              |     | 5.5      | <b>-</b>     | <b>→</b>       |          |          | <b>→</b>    | <b>→</b>    | 2            | DC voltage test                  | 4.10       | 0 4.24  | 4 4.40      | >      |

| 9  | V (IREF)                                                 | V (IREF)                   |     |                |                                       |              | -   | 5.00     | <b>→</b>     | <b>→</b>       |          |          | <b>→</b>    | F           |              |                                  | 2.05       | 5 2.12  | 2 2.20      | >      |

| 7  | Input SW Crosstalk<br>(SECAM REC)                        | I-CT<br>(SR)               |     |                |                                       | 0            |     | -,       |              | 3.05           |          |          | 3.3         | G           | SECAM<br>REC | C OUT output level               |            | - 38    | 38.0 - 35.0 | dB dB  |

| 8  | Input SW Crosstalk<br>(SECAM PB)                         | LCT<br>(SP)                |     |                |                                       |              |     | <b>→</b> | -            | <b>→</b>       |          |          | 1.7V        | <b>→</b>    | SECAM PB     | test                             |            | -53.0   | .0 -45.0    | dB     |

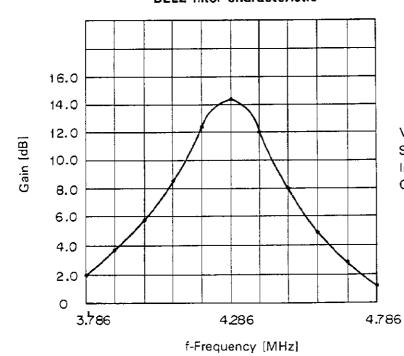

| 6  | BELL FILTER Gain                                         | 8F-G                       |     |                |                                       |              |     | -        | <b>→</b>     | <b>→</b>       |          |          | 1.3         | <b>→</b>    | SECAM<br>REC | C OUT output level               | 11.0       | 0 14.0  | 0.91 0      | ф      |

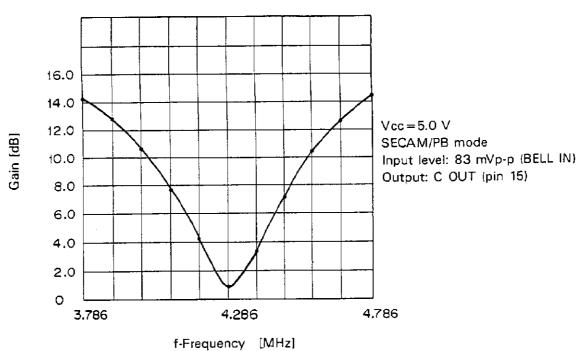

| 5  | C-BELL FILTER Gain                                       | CBF-G                      |     |                |                                       |              |     | -        | <b>→</b>     | <b>→</b>       |          |          | 5.          | <b>→</b>    | SECAM PB     | test                             | - 3        | 0 0     | 3.0         | dB     |

| =  | TH Amp Gain                                              | THA-G                      |     |                | 0                                     |              |     | -        | <b>→</b>     | 7.0            |          | 3.00     | 2.87        | I           |              | C OUT output level               | - 2.       | 5 -0.3  | 3 2.0       | gp     |

| 12 | TH/DL Amp Gain<br>Ratio                                  | DA-G                       |     |                | 0                                     |              |     |          | <b>→</b>     | <b>→</b>       |          | 2.00     | <b>→</b>    | †           | PAL PB       | test (4.43MHz)                   | -0.        | 0.6 0.4 | 4.1         | 8      |

| 13 | TH/DL Phase<br>Difference                                | дтн-ог                     |     |                | 0                                     |              |     | <b>→</b> | <b>→</b>     | <b>→</b>       |          | <b>→</b> |             | 9           |              | C OUT phase test                 | 90         | 06      | 120         | deg    |

| 14 | TH/EXB Level Ratio                                       | Ф ∨тн-ехв                  |     |                |                                       |              | ,   | <b>→</b> | >            | <b>→</b>       |          |          | 3.20        | I           |              | Output lev                       | -1-<br>-1- | 2.6     | 4 - 1       | 명      |

| 15 | EX Burst Level Ratio                                     | Δ Vεхв                     |     |                |                                       |              |     | <b>→</b> | <del> </del> | -+             |          |          | <del></del> | <del></del> | 20           | test                             | - 1.0      | 0       | 1.0         | 쁑      |

| 16 | EX Burst Phase<br>Difference                             | а вехв                     |     |                |                                       |              |     | <b>→</b> | <b>→</b>     | <b>→</b>       |          |          | <b>→</b>    | 9           |              | Phase test                       | 06         | 96      | 102         | deg    |

| 17 | TH-EX Burst Phase<br>Difference                          | Отн-ехв                    |     |                |                                       |              |     | -,       | <b>→</b>     | <b>→</b>       |          |          | <b>→</b>    | <b>→</b>    |              |                                  | 40         | 48      | 56          | deg    |

| 18 | PAL-M DL APC Loop<br>Characteristics                     | DL-APC<br>(PAL M)          |     | 0              |                                       |              |     | →,       | <b>→</b>     | <b>→</b>       | 5.00     | 8        | 2.87        | <b>-</b>    |              | C OUT phase test                 | - 100      |         | 90 - 80     | deg    |

| 19 | PAL-M EX Burst Level<br>Ratio                            | A VEXB                     |     | 0              |                                       |              |     |          | <b>→</b>     | <b>→</b>       | <b>→</b> | <b>→</b> | <b>→</b>    | <b>→</b>    | PAI -M PR    | C OUT output level<br>test       | ı          | 1.5 0   | 1.5         | B<br>B |

| 20 | PAL-M EX Burst<br>Phase Difference                       | A PEXB                     |     | 0              |                                       |              |     |          | <b>→</b>     |                | -        | <b>→</b> | -+          | <b>→</b>    |              | C OllT phase test                | - 104      | 1       | 96 88       | deg    |

| 21 | PAL-M DL-EX Burst<br>Phase Difference                    | <i>в</i> тн-єхв<br>(PAL M) |     | 0              |                                       |              | -   | <b>→</b> | <b>→</b>     |                |          |          | <b>→</b>    | <b>→</b>    |              | near present con o               | - 2        | 20 - 10 | 0 0         | deg    |

|    |                                                          |                            |     |                |                                       |              |     |          |              |                |          | İ        |             |             |              |                                  | ]          |         | i           |        |

| -      | 1                            | 1              | S.NO        | itch ( | Switch Condition<br>ON: O, OFF: blank | tion<br>tank |          |          | Bías t   | Bias Condition | E            |          | Test     | Output Wa | Output Waveform and Test Content | , 6.00<br>C.000 | اً ا  | 1    | Loida |

|--------|------------------------------|----------------|-------------|--------|---------------------------------------|--------------|----------|----------|----------|----------------|--------------|----------|----------|-----------|----------------------------------|-----------------|-------|------|-------|

| ė<br>Ž | Item                         | logwide        | SW SW SW SW | 3W. S  | 3.W.S.                                | ws t         | ۷ دو     | ۸۲       | ~        | 5              | <del>'</del> | V21      | Point    | Mode      |                                  |                 | . Ab. | Σ    | Units |

| 22     | SQ DET +V<br>Detection       | SQ (+)         |             | 0      |                                       |              | 5.00     | / 2.5V   | 1.00     | 3.87           |              | 2.8V     | -        | PAL       | DC voltage test at pin           | -122            |       | 86-  | geb   |

| 23     | SQ DET -V<br>Detection       | (-) 08         |             | 0      |                                       |              |          |          |          | <b>→</b>       |              | <b>→</b> | <b>→</b> | RESET     | 17                               | -35             |       | - 59 | deg   |

| 24     | Main SW Crosstalk<br>(TH)    | MSW-CT<br>(TH) |             |        | 0                                     |              | <b>→</b> | <b>→</b> | <b>→</b> |                | 3.0V         | ۷۲.1     | g        |           | C OUT output level test          |                 | -49   | -44  | ф     |

| 25     | AFC HD Timing                | Q-QH           |             |        |                                       |              | →        | <b>→</b> | *        |                |              | <b>→</b> | Q        |           | Tions to some                    | - 3.0           | -1.2  | 0.3  | μS    |

| 26     | AFC HD Width                 | M-QH           |             |        |                                       |              | <b>→</b> | -        | -        |                |              |          | <b>→</b> | PAL PB    | Or life test at bill             | 4.4             | 5.3   | 6.2  | мs    |

| 27     | AFC Lock Range (1)           | AFC-LR<br>(1)  |             |        |                                       |              | -        | -        | <b>-</b> |                |              | -        | <b>→</b> |           | Frequency test at plin           | - 55            |       | 55   | Hz    |

| 28     | AFC Lock Range (2)           | AFC-LR<br>(2)  |             |        |                                       |              | <b>→</b> | <b>→</b> | <b>→</b> |                |              | †        | <b>→</b> |           | 10                               | - 55            |       | 55   | Нž    |

| 29     | TIMING EX Burst<br>Delay     | EXB-D          |             |        |                                       |              | <b>→</b> | <b>→</b> | <b>→</b> |                |              | 3.2V     | 9        | 501 100   |                                  | 4.5             | 5.2   | 5.8  | μS    |

| 30     | TIMING EX Burst<br>Width     | EXB-W          |             |        |                                       |              | <b>→</b> | <b>→</b> | <b>→</b> |                |              | <b>→</b> |          | 2         | Time test                        | 3.9             | 4.4   | 5.1  | 57    |

| 31     | TIMING 1/2 FHMP<br>Delay     | 1/2FH-D        |             |        |                                       | 0            | <b>→</b> | <b>→</b> | <b>→</b> |                |              | ٧٢.٢     | Ú        | 99 199    |                                  | 32.0            | 36.0  | 40.0 | μS    |

| 32     | TIMING 1/2 FHMP<br>Duty      | 1/2FH-DU       |             |        |                                       | 0            | <b>→</b> | <b>→</b> | <b>→</b> |                |              |          | -        |           |                                  | 44              | 50    | 56   | %     |

| 33     | SECAM DETECTOR<br>DEMOD (PB) | SA (PB)        | 0           |        |                                       |              | <b>→</b> | <b>→</b> |          |                |              | 2.8V     | 8        | PB        | DC voltage test at pin 3         | 3.60            | 3.80  | 4.0  | >     |

| 34     | ACK Check                    | ACK            |             |        | 0                                     | :            | <b>→</b> | 0.5V     | 7.0      | >              | 5.00         |          | 9        | PAL PB    | C OUT output level test          |                 | - 58  | - 49 | ф     |

## **Test Methods of Electrical Characteristics**

|     |                                      |                                                | In                                    | put Signal         |                                       | Test Content                                                                                                               |

|-----|--------------------------------------|------------------------------------------------|---------------------------------------|--------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| No. | ltem                                 | VPAL                                           | Vse                                   | Vsyna              | Vfac                                  | rest content                                                                                                               |

| 1   | Circuit current<br>(PAL PB)          |                                                |                                       |                    |                                       |                                                                                                                            |

| 2   | Circuit current<br>(SECAM REC)       |                                                | į                                     |                    |                                       |                                                                                                                            |

| 3   | VREG (5.0V)                          |                                                |                                       |                    |                                       | Test the DC voltage at pin 13.                                                                                             |

| 4   | VREG (4.5V)                          |                                                |                                       |                    |                                       | Test the DC voltage at pin 13.                                                                                             |

| 5   | VREG (5.5V)                          |                                                |                                       |                    |                                       | Test the DC voltage at pin 13.                                                                                             |

| 6   | V (IREF)                             |                                                |                                       |                    |                                       | Test the DC voltage at pin 14.                                                                                             |

| 7   | Input SW<br>Crosstalk<br>(SECAM REC) |                                                | 4.286MHz<br>CW<br>350mVr-r            | 15.625kHz, 4.0Va=P |                                       | $20 \log \left\{ \frac{\text{C OUT (4.286MHz component)}}{\text{V}_{\text{SE}}} \right\}$                                  |

| 8   | Input SW<br>Crosstalk<br>(SECAM PB)  | 4.286MHz<br>CW<br>350mV <sub>P-P</sub>         |                                       | ļ                  |                                       | 20 log (C OUT (4.286MHz component) VPAL                                                                                    |

| 9   | BELL FILTER<br>Gain                  |                                                | 4.286MHz<br>CW<br>32mVr-r             | ţ                  |                                       | 20 log {C OUT (4.286MHz component) Vse                                                                                     |

| 10  | C-BELL FILTER<br>Gain                |                                                | 4.286MHz<br>CW<br>83mV <sub>P-P</sub> | +                  |                                       |                                                                                                                            |

| 11  | TH Amp Gain                          | CW delayed<br>by 135°<br>from Vfsc<br>350mVp-p |                                       | 1                  | 4.43MHz<br>CW<br>350mV <sub>P-P</sub> | 20 log { C OUT (4.43MHz) }                                                                                                 |

| 12  | TH/DL Amp Gain<br>Ratio              | <b>.</b>                                       |                                       | ļ                  | Ţ                                     | 20 log { Output level of T11 } C OUT (4.43MHz)                                                                             |

| 13  | TH/DL Phase<br>Difference            | CW delayed<br>by 135°<br>from Vfsc<br>150mVr-r |                                       | 1                  | ţ                                     | θοι-θτη                                                                                                                    |

| 14  | TH/EXB Level<br>Ratio                |                                                |                                       | ļ                  | ţ                                     | 20 log $\left\{ \frac{\text{T11 } (p-p)}{(\text{EB1} + \text{EB2})/2} \right\} - 7.4 dB$ $- \frac{1581}{7} \frac{1582}{7}$ |

| 15  | EX Burst Level<br>Ratio              |                                                |                                       | 1                  | 1                                     | VC                                                                                                                         |

|     |                                          |                                                                       | Ing | out Signal         |                                         | T Contact                                                                                                                                                          |

|-----|------------------------------------------|-----------------------------------------------------------------------|-----|--------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | ltem                                     | VPAL                                                                  | Vse | Vsync              | Visc                                    | Test Content                                                                                                                                                       |

| 16  | EX Burst Phase<br>Difference             | 4                                                                     |     | 15.825kHz, 4.0Vo-P | 4.43MHz,<br>CW<br>350mV <sub>F</sub> -p | $\Delta \theta(EB) = \theta_2 - \theta_1$                                                                                                                          |

| 17  | TH-EX Burst<br>Phase Difference          |                                                                       |     | <b>↓</b>           | ļ                                       | Phase difference between $	heta_1+	heta_2 -	heta_{ m TH}$ the center of EX burst and TH signal.                                                                    |

| 18  | PAL-M DL APC<br>Loop<br>Characteristic   | CW delayed<br>by 90° from<br>V <sub>fee</sub><br>150mV <sub>P-P</sub> |     | 15.734kHz 4.0Vo-P  | 3.58MHz<br>CW<br>350mV <sub>P-P</sub>   | Test $	heta$ (DL) on the basis of V <sub>150</sub>                                                                                                                 |

| 19  | PAL-M EX Burst<br>Level Ratio            |                                                                       |     | Ļ                  | ļ                                       | ν <sub>c</sub> ωια                                                                                                                                                 |

| 20  | PAL-M EX Burst<br>Phase Difference       |                                                                       |     | <b>↓</b>           | <b>↓</b>                                | $\Delta \theta(EB) =  \theta_1 - \theta_2 $                                                                                                                        |

| 21  | PAL-M DL-EX<br>Burst Phase<br>Difference |                                                                       |     | ı                  | ļ                                       | $\frac{\theta_1+\theta_2}{2}-\text{T18}  \begin{array}{c} \text{Phase difference be-} \\ \text{tween the center of EX} \\ \text{burst and DL signal.} \end{array}$ |

| 22  | SQ DET +V<br>Detection                   | Signal with<br>the phase<br>delayed<br>from Vrec<br>150mVr-r          |     | 15.625kHz 4.0Vo-p  | 4.43MHz<br>CW<br>350mV==                | Test the phase of V <sub>FAL</sub> (on the basis of V <sub>fsc</sub> ) when DC is changed from L to H (4.0V) at pin 17.                                            |

| 23  | SQ DET -V<br>Detection                   | Singal with<br>the phase<br>delayed<br>from Vrac<br>150mVr-r          |     | ļ                  | 1                                       | Test the phase of V <sub>PAL</sub> (on the basis of V <sub>fsc</sub> ) when DC is changed from H to L (OV) at pin 17.                                              |

| 24  | Main SW<br>Crosstalk (TH)                |                                                                       |     | ţ                  | ţ                                       | Test by TH signal timing.                                                                                                                                          |

| 25  | AFC HD Timing                            |                                                                       |     | ţ                  |                                         | Test the time at pin 10.                                                                                                                                           |

| 26  | AFC HD Width                             |                                                                       |     | 1                  |                                         | tw Ho 2.0v                                                                                                                                                         |

| 27  | AFC Lock Range                           |                                                                       |     |                    |                                         | Test the frequency at pin 10.                                                                                                                                      |

| 28  | AFC Lock Range<br>(2)                    |                                                                       |     | ↓ 19.0kHz          |                                         | (Input frequency $-\frac{1}{T}$ )                                                                                                                                  |

|     |                                 |                                        | ing                                                      | out Signal                    |                                       |                                                      | T C                              |

|-----|---------------------------------|----------------------------------------|----------------------------------------------------------|-------------------------------|---------------------------------------|------------------------------------------------------|----------------------------------|

| No. | ltem                            | VPAL                                   | Vae                                                      | Vayno                         | Vfsc                                  |                                                      | Test Content                     |

| 29  | TIMING EX Burst<br>Delay        |                                        |                                                          | 15.625kHz 4.0Vo-#             | 4.43MHz<br>CW<br>350mV <sub>P-P</sub> | td                                                   | Test the time at C OUT           |

| 30  | TIMING EX Burst<br>width        |                                        |                                                          | ţ                             | ļ                                     | tw                                                   | COUT                             |

| 31  | TIMING 1/2<br>FHMP Delay        |                                        |                                                          | ţ                             |                                       | td                                                   | Test the time at pin 4.          |

| 32  | TIMING 1/2<br>FHMP Duty         |                                        |                                                          | 1                             |                                       | $\frac{\mathbf{t}_1}{(\mathbf{t}_1 + \mathbf{t}_2)}$ | 1/2 FHMP 16                      |

| 33  | SECAM<br>DETECTOR<br>DEMOD (PB) |                                        | SECAM<br>Signal (Burst<br>level<br>83mV <sub>F-F</sub> ) | 15.625kHz 4.0V <sub>P-P</sub> |                                       | Test                                                 | the DC voltage at pin 3.         |

| 34  | ACK Check                       | 4.43MHz<br>CW,<br>350mV <sub>P-P</sub> |                                                          | 1                             |                                       | I                                                    | IT (4.43MHz) ⇒ V,<br>g (V/350mV) |

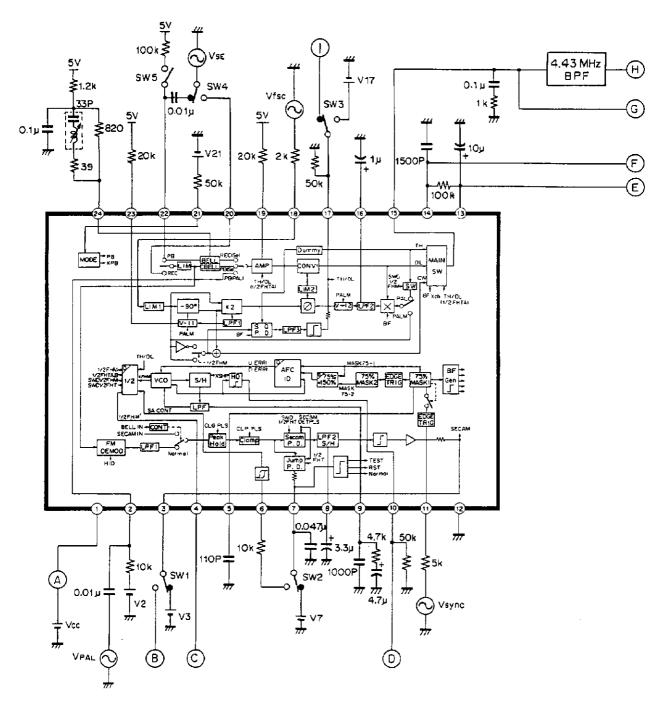

#### **Electrical Characteristics Test Circuit**

Fig. 1

#### **Description of Functions**

#### 1. Gain Adjustment Amplifier (DL Signal)

This amplifier adjusts the gain of the DL signal in PAL or PAL-M mode. The amplifier gain varies according to the DC voltage applied to pin 19. When 5 V is applied to pin 19, the internally fixed gain is obtained and the levels of the TH signal and the DL signal (4.43 MHz component in PAL mode, 3.58 MHz component in PAL-M mode) become the same.

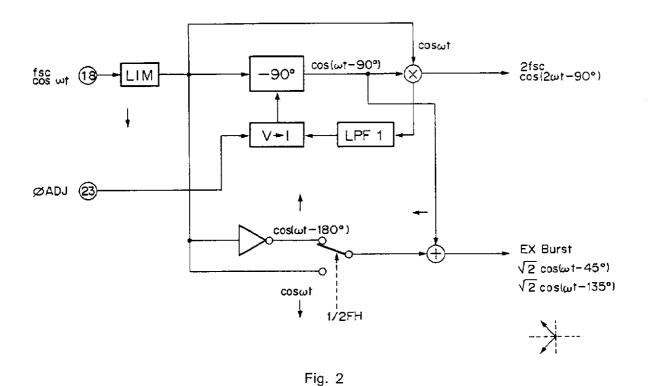

#### 2. fsc $-90^{\circ}$ PLL, $\times$ 2 and EX Burst Block

The fsc  $-90^{\circ}$  PLL consists of the  $-90^{\circ}$  phase shifter, multiplier, LPF (low pass filter) 1 and V/I converter. A signal delayed by  $90^{\circ}$  to the fsc is obtained in this PLL. By changing the DC voltage at pin 23, the amount of phase shift is varied, allowing adjustment of the phase of the EX burst and the duty (DC offset) of the 2 fsc. By applying 5 V at pin 23, the internally fixed phase shift is obtained. The 2 fsc is produced from the multiplier output ( $\times$  2 output).

The EX burst is produced by adding the fsc (or inverted fsc) to the fsc with  $90^{\circ}$  delay produced in the  $-90^{\circ}$  PLL.

The fsc and the inverted fsc are switched in a period of 1/2 fH, so the phase of the EX burst changes every 1 H.

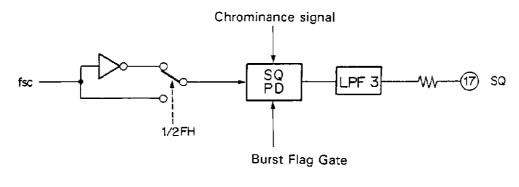

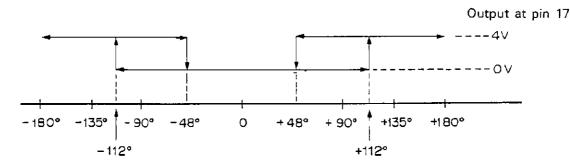

#### 3. SQ DET (Sequence Detector)

Fig. 3

The SQ DET detects the color alignment of the chrominance signal. The SQ PD is the phase detector which operates for a burst period only. This detects the color alignment by comparing the phase of the fsc signal inverted every 1 H with the phase of the burst of the chrominance signal.

Phase of the burst signal (on the basis of fsc and fsc)

The above figure shows the relation between the phase of the burst signal, the phase of the fsc (fsc) and the output at pin 17 (SQ). As shown in the figure, the hysteresis angle is about 64°. If the relation is as shown in the figure below, the detector judges it as the correct sequence and set the output at pin 17 to HIGH.

Fig. 5

Therefore, the center phase of the burst signal (about the B-Y axis) should be  $-90^{\circ}$  to the fsc.

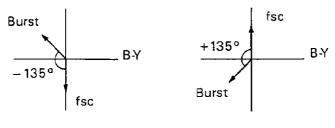

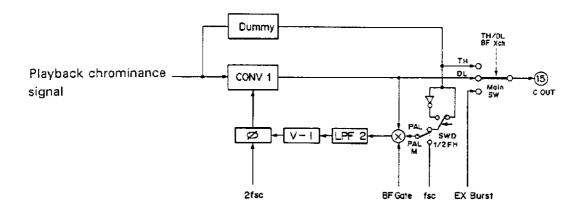

#### 4. V-Invert (V Axis Inversion Circuit)

For color alignment, the DL signal which is produced by inverting the chrominance signal (TH signal) about the B-Y axis is necessary.

The V-Invert block produces the DL signal from the TH signal. Fig. 6 shows the principle of the V-Invert block.

Define the B-Y axis of the playback chrominance signal as  $\cos \omega t$  and input the playback chrominance signal and the 2 fsc ( $\cos 2\omega t$ ) to the multiplier. By means of the frequency conversion of the 2 fsc, the input chrominance signal is inverted about the B-Y axis. The three fold frequency component ( $\cos 3\omega t$ ) is also output, but this component is rejected by the BPF in a later stage.

Fig. 7 shows the actual V-Invert block.

Fig. 7

The V-Invert circuit constructs the TH/DL APC loop that keep the phase difference between the burst of the TH signal and the burst of the DL signal to be  $90^{\circ}$ . This circuit detects the phase of the bursts of the TH and DL signals and varies the delay time of the phase shifter  $\phi$  with reference to the error current of APC loop. In PAL-M mode, the APC is applied to the fsc and the DL signal. Therefore, the input burst signal has a phase of  $90^{\circ}$  to the fsc. The CONV 1 is a multiplier to obtain the DL signal.

The Dummy supplies the same gain loss and the same phase delay as produced in CONV 1 to the TH signal so that there is no gain and phase difference between the TH signal and the DL signal.

The main SW outputs the TH or DL signal according to the TH/DL select signal (output at pin 17). When a BF Xch pulse is supplied (in JOG mode only), the EX burst is output.

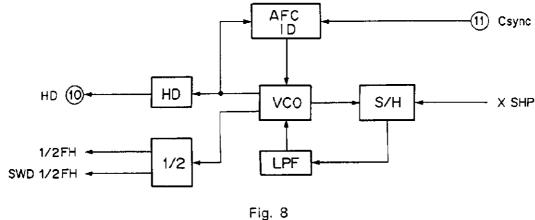

#### 5. fH PLL

The AFC ID compares the C sync frequency with the VCO frequency. When a frequency difference is present, the AFC ID outputs an up or down error and roughly compensates the VCO frequency. In this case, the AFC ID detects if the frequency difference continues for a period of 15H  $\times$  6 (5760  $\mu$ s), and AFC ID error is available only when the frequency difference continues for that period.

The AFC ID also detects the existence of C sync. When the C sync is missing in various speed mode, the AFC ID cuts off its output and maintains the state immediately before the output cutout.

The phase lock of the C sync and VCO frequencies is carried out in the PLL loop composed of the S/H and LPF circuits.

#### 6. BELL and C-BELL Filters

The Bell Filter is applied to the SECAM color TV signal to suppress the level near the chrominance subcarrier (For, For). In REC mode, the CXA1203 employs the BELL filter (having the inverted characteristics from the Bell Filter) to obtain the chrominance subcarrier of the same amplitude at every hue. The output signal from the BELL filter is sent to the record signal processing block of chrominance signal in the CXA1200.

In playback mode, the chrominance signal processed in the CXA1200 is input to the C-BELL (having the same characteristics as the Bell Filter) filter of the CXA1203 to equalize the input signal with the SECAM color TV signal. The output from the C-BELL filter is mixed with the Y signal in the CXA1200 and sent to the CXA1201. The typical input level of the BELL filter is 32 mVp-p, and that of the C-BELL filter is 83 mVp-p.

#### 7. SECAM Detector Circuit

The SECAM detector circuit employed in the CXA1203 converts the chrominance subcarrier frequency\* to a voltage, and detects the color system by the voltage variation: PAL system if no voltage variation is present, or SECAM system if the voltage varies every 1H. When the color alignment is carried out in SECAM mode, the SECAM ACK output (pin 3) is always set to HIGH by inputting the SECAM JUMP output (pin 7) to the DLDP (pin 6).

\* PAL system: color burst signal (4.43361875 MHz) SECAM system: line ID signal For: 4.40625 MHz

Fob: 4.25000 MHz

#### Notes on Use

#### 1. Phase Adjustment in PAL Playback Mode

The phase of the EX burst signal can be adjusted with the phase of the input fsc (chrominance subcarrier). The phase of the DL signal can be adjusted by applying a current to pin 16. Adjust the phase of the fsc so that the phase of the EX burst signal in JOG playback mode matches the phase of the color burst signal in normal playback mode at the PB CHROMA output (pin 15). Then, adjust the current to be applied to pin 16 so that the DL signal becomes symmetrical to the TH signal about the BY axis.

#### 2. PAL-M mode

Fig. 11

Input an NTSC signal to pin 2, the fsc signal (3.58 MHz) to pin 18 and the C sync signal (15.75 MHz) to pin 11. Then the PAL-M playback signal is obtained at PB CHROMA output (pin 15). To adjust the phase, first input a burst signal with the same phase as the BY axis, and adjust the phase of the fsc to be input so that the phase of the TH signal matches the center phase of the EX burst at pin 15. Then adjust the current to be applied to pin 16 so that the phase of the DL signal matches the center phase of the EX burst. In PAL-M mode, pin 17 (SQ ID) should be fixed to L.

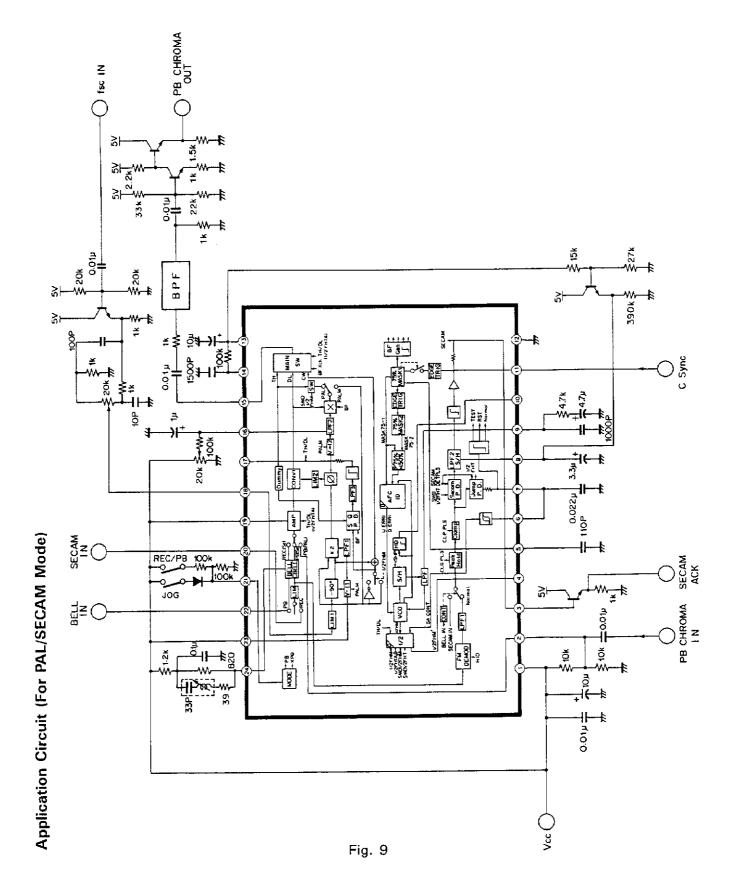

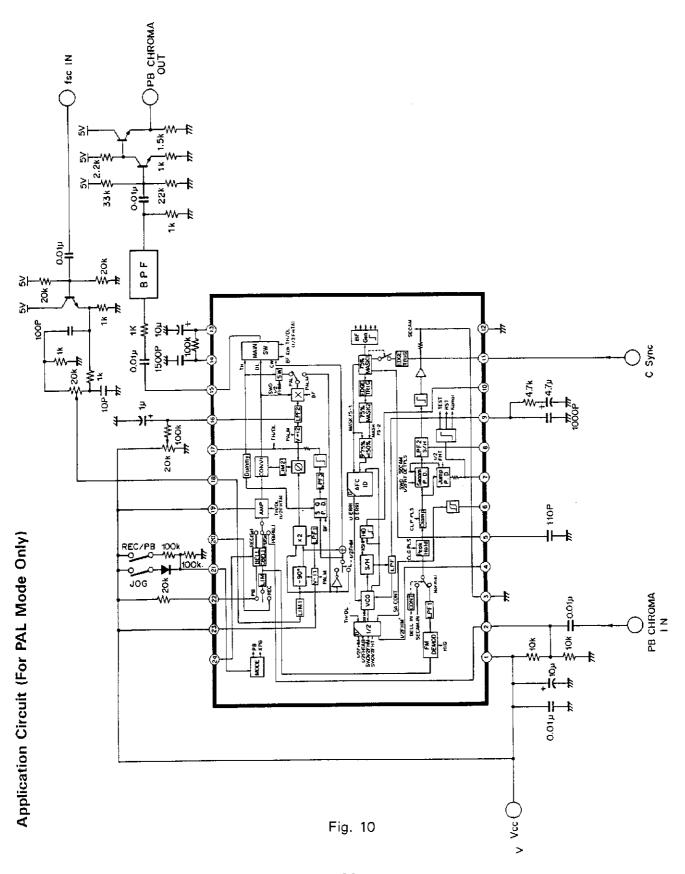

#### 3. PAL Only Mode

In PAL only mode, a part of the SECAM detector block is turned off by fixing pin 22 (BELL IN) to H. This reduces the current consumption to 1.2 mA. The connections for other pins are the same as shown in Fig. 10 "Application Circuit (PAL only mode)".

## V REG supply voltage characteristic

#### **BELL** filter characteristic

Vcc = 5.0 V SECAM/REC mode Input level: 32 mVp-p (BELL IN) Output: C OUT (pin 15)

## C-BELL filter characteristic

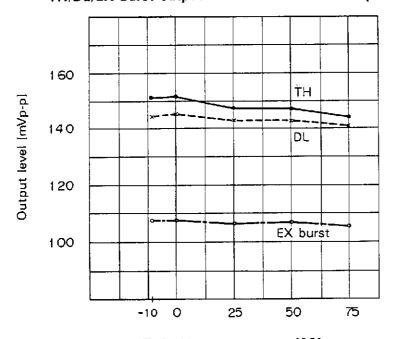

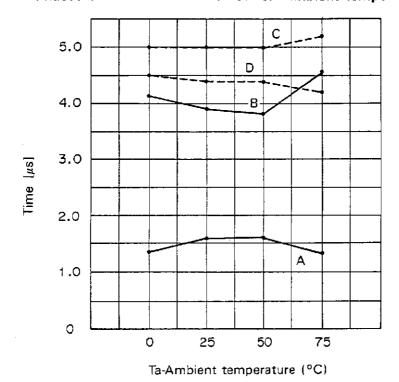

## TH/DL/EX burst output levels vs. Ambient temperature

Ta-Ambient temperature [°C]

Vcc=5.0 V PAL/PB mode

Input level: 150 mVp-p (PB C IN)

fsc: 350 mVp-p

Output: 4.43 MHz BPF OUT (The output level is the average

during 2 H).

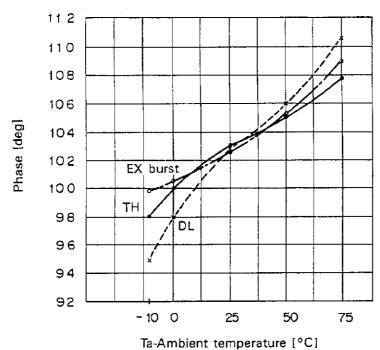

#### TH/DL/EX burst phases vs. Ambient temperature

Vcc = 5.0 V

PAL/PB mode

Input level: 150 mVp-p

(PB C IN)

fsc: 350 mVp-p

Output: C OUT (pin 15)

The phase is the absolute value determined by measuring the center angle of the TL, DL or EX burst during 2 H with reference to the fsc (at pin 18).

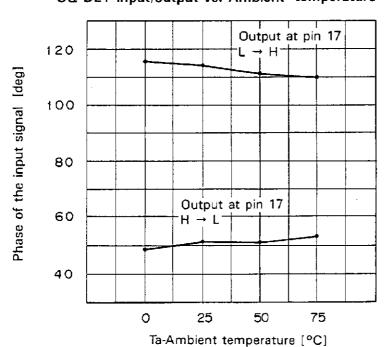

## SQ DET input/output vs. Ambient temperature

Vcc=5.0 V

PAL/RESET mode

Input level: 150 mVp-p (PB C IN)

fsc: 350 mVp-p

Output: SQ ID (pin 17)

(The phase of the input

signal is the absolute

value of the phase delay

to the fsc. This is

determined by delaying

the phase of the input

signal to the fsc and

measuring the phase

delay when the output

changes.)

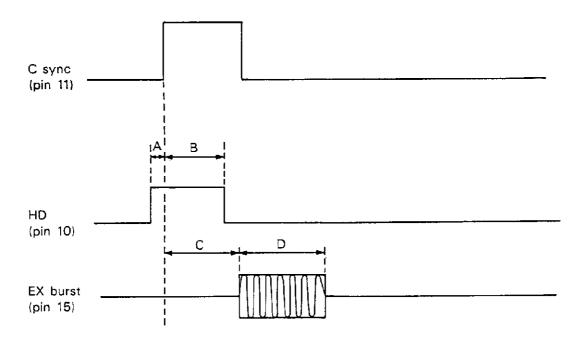

## Relation of the phase of each pulse to the C sync singal

## Phases of the HD and EX burst vs. Ambient temperature

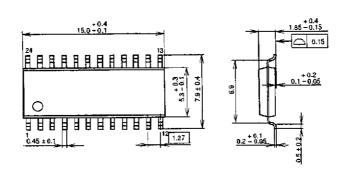

Package Outline

Unit: mm

**CXA1203M**

24PIN SOP (PLASTIC)

PACKAGE STRUCTURE

| SONY CODE  | SOP-24P-L01   |

|------------|---------------|

| EIAJ CODE  | SOP024-P-0300 |

| TEDEC CODE |               |

| EPOXY RÉSIN     |

|-----------------|

| SOLDER PLATING  |

| 42/COPPER ALLOY |

| 0.3g            |

|                 |

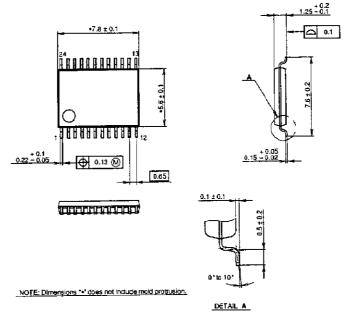

## CXA1203N

24PIN SSOP(PLASTIC)

|  | PACKAGE S |

|--|-----------|

| SONY GODE  | SSOP-24P-L01   |

|------------|----------------|

| EIAJ CODE  | SSOP024-P-0056 |

| JEDEC CODE |                |

| PACKAGE STRUCTURE |                             |  |

|-------------------|-----------------------------|--|

| PACKAGE MATERIAL  | EPOXY RESIN                 |  |

| LEAD TREATMENT    | SOLDER/PALLADIUM<br>PLATING |  |

| LEAD MATERIAL     | 42/COPPER ALLOY             |  |

| PACKAGE MASS      | 0.1g                        |  |

NOTE: PALLADIUM PLATING

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).