# HD6844, HD68A44, HD68B44\* DMAC (Direct Memory Access Controller)

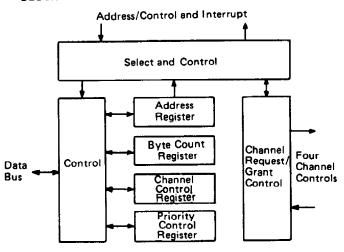

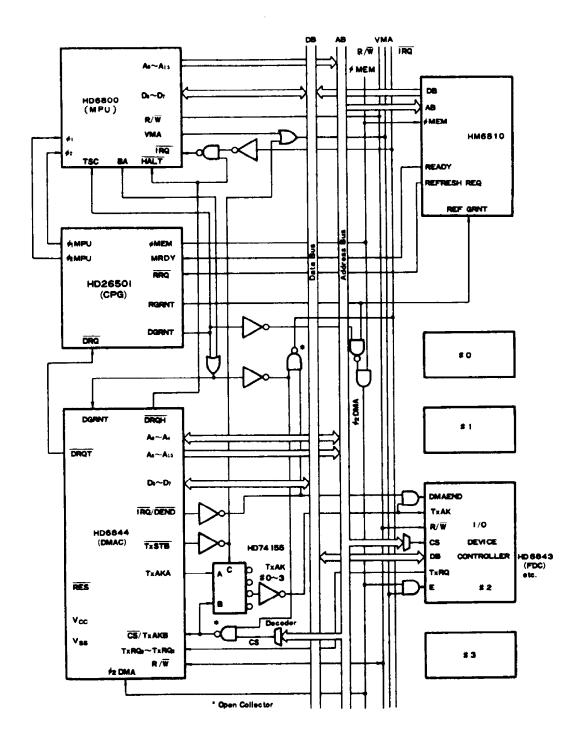

The HD6844 Direct Memory Access Controller (DMAC) performs the function of transferring data directly between memory and peripheral device controllers. It controls the address and data buses in place of the MPU in bus organized systems such as the HMCS6800 Microprocessor System.

The bus interface of the HD6844 includes select, read/write, interrupt, transfer request/grant, and bus interface logic to allow the data transfer over an 8-bit bidirectional data bus. The functional configuration of the DMAC is programmed via the data bus. The internal structure provides for control and handling of four individual channels, each of which is separately configured. Programmable control registers provide control for the transfer location and length, individual channel control and transfer mode configuration, priority of servicing, data chaining, and interrupt control. Status and control lines provide control to the peripheral controllers.

The mode of transfer for each channel can be programmed as cycle-stealing or a burst transfer mode.

Typical applications would be with the Floppy Disk Controller (FDC), etc..

#### **FEATURES**

- Four DMA Channels, Each Having a 16-Bit Address Register and a 16-Bit Byte Count Register

- 1 M Byte/Sec (HD6844), 1.5 M Byte/Sec (HD68A44), 2.0 M Byte/Sec (HD68B44)

Maximum Data Transfer Rate

- Selection of Fixed or Rotating Priority Service Control

- Separate Control Bits for Each Channel

- Data Chain Function

- Address Increment or Decrement Update

- Programmable Interrupts and DMA End to Peripheral Controllers

- Compatible with MC6844, MC68A44, MC68B44

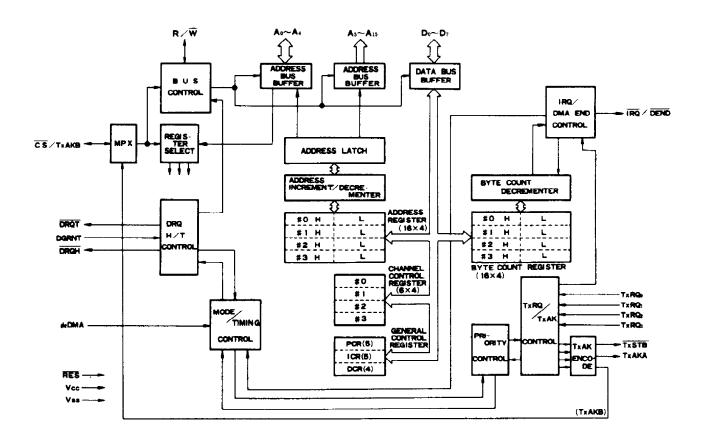

#### **BLOCK DIAGRAM**

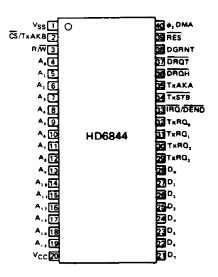

### ■ PIN ARRANGEMENT

(Top View)

\*Old type name: HD46504, HD46504-1, HD46504-2.

### ■ ABSOLUTE MAXIMUM RATINGS

| ltem                  | Symbol            | Value       | Unit |

|-----------------------|-------------------|-------------|------|

| Supply Voltage        | V <sub>cc</sub> * | -0.3 ~ +7.0 | V    |

| Input Voltage         | V <sub>in</sub> * | -0.3 ~ +7.0 | V    |

| Operating Temperature | Topr              | -20 ~ +75   | °C   |

| Storage Temperature   | T <sub>sto</sub>  | -55 ~ +150  | °C   |

<sup>\*</sup> With respect to V<sub>SS</sub> (SYSTEM GND)

(NOTE) Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect reliability of LSI.

### ■ RECOMMENDED OPERATING CONDITIONS

| Item                  | Symbol            | min  | typ | max             | Unit |

|-----------------------|-------------------|------|-----|-----------------|------|

| Power Supply Voltage  | V <sub>cc</sub> * | 4.75 | 5.0 | 5.25            | V    |

| Input Voltage         | V <sub>IL</sub> * | -0.3 | -   | 0.8             | V    |

| mput vortage          | V <sub>IH</sub> * | 2.0  |     | V <sub>cc</sub> | V    |

| Operating Temperature | Topr              | -20  | 25  | 75              | °c   |

<sup>\*</sup> With respect to VSS (SYSTEM GND)

### ■ ELECTRICAL CHARACTERISTICS (V<sub>CC</sub>=5V±5%, V<sub>SS</sub>=0V, Ta=-20~+75°C, unless otherwise noted.)

### • DC CHARACTERISTICS

| lto                                        | em                                                                           | Symbol           | Test Condition                                        | min  | typ* | max  | Unit     |

|--------------------------------------------|------------------------------------------------------------------------------|------------------|-------------------------------------------------------|------|------|------|----------|

| Input "High" Voltage                       |                                                                              | V <sub>iH</sub>  |                                                       | 2.0  | -    | Vcc  | <b>V</b> |

| Input "Low" Voltage                        |                                                                              | VIL              |                                                       | -0.3 |      | 0.8  | V        |

| Input Leakage Current                      | TxRQ <sub>0</sub> ~ <sub>3</sub> , φ <sub>2</sub> DMA,<br>RES, DGRNT         | l <sub>in</sub>  | V <sub>in</sub> =0~5.25V                              | -2.5 | -    | 2.5  | μА       |

| Three-State (off state)<br>Leakage Current | A <sub>0</sub> ~A <sub>15</sub> , D <sub>0</sub> ~D <sub>7</sub> , R/W       | I <sub>TSI</sub> | V <sub>in</sub> =0.4~2.4V                             | -10  | _    | 10   | μА       |

|                                            | D <sub>0</sub> ~D <sub>7</sub>                                               |                  | I <sub>OH</sub> =-205μA                               | 2.4  | _    | _    |          |

| Output "High" Voltage                      | A <sub>0</sub> ~A <sub>15</sub> , R/W                                        | VoH              | I <sub>OH</sub> =-145μA                               | 2.4  | _    |      | ٧        |

|                                            | All Other Outputs                                                            |                  | I <sub>OH</sub> =-100μA                               | 2.4  | _    | _    |          |

| Output "Low" Voltage                       |                                                                              | Vol              | I <sub>OL</sub> =1.6mA                                | _    | _    | 0.4  | v        |

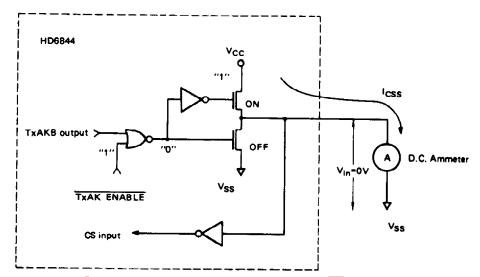

| Source Current                             | CS/TxAKB                                                                     | Icss             | V <sub>in</sub> =0V, Fig. 10                          |      | 10   | 16   | mA       |

| Power Dissipation                          |                                                                              | PD               |                                                       |      | 500  | 1000 | mW       |

|                                            | φ <sub>2</sub> DMA                                                           |                  |                                                       | _    | _    | 20   |          |

| Input Capacitance                          | D <sub>0</sub> ~D <sub>7</sub> , CS, A <sub>0</sub> ~A <sub>4</sub> ,<br>R/W | C <sub>in</sub>  | V <sub>in</sub> =0V, T <sub>a</sub> =25°C<br>f=1.0MHz | -    | -    | 12.5 | рF       |

|                                            | TxRQ <sub>0</sub> ~ <sub>3</sub> , RES,<br>DGRNT                             | ·                | I – I. UMITIZ                                         | -    | _    | 10   |          |

| Output Capacitance                         |                                                                              | Cout             | V <sub>in</sub> =0V, T <sub>e</sub> =25°C, f=1MHz     | _    | _    | 12   | pF       |

<sup>\*</sup> V<sub>CC</sub>=5.0V, T<sub>a</sub>=25° C

### AC CHARACTERISTICS (Load Condition Fig. 9)

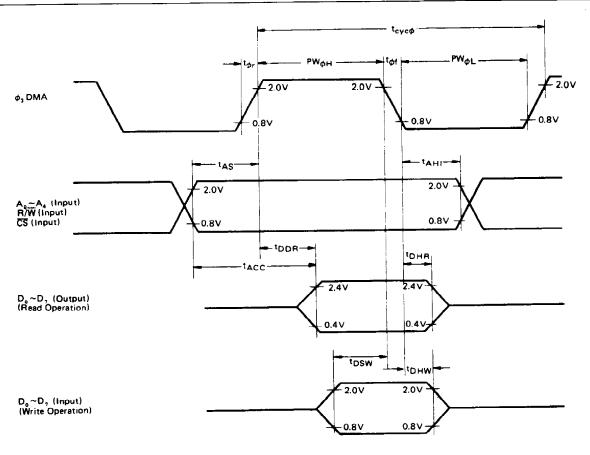

### 1. CLOCK TIMING

|                                |              | Ī                  | Combal Test |      | Test HD6844 HD68A44 |     |     | 4   | HD68B44 |     |     |            |      |

|--------------------------------|--------------|--------------------|-------------|------|---------------------|-----|-----|-----|---------|-----|-----|------------|------|

| ltem                           |              | Symbol             | Condition   | min  | typ                 | max | min | typ | max     | min | typ | max        | Unit |

| φ <sub>2</sub> DMA Cycle Time  |              | ι <sub>cyc</sub> φ | Fig. 2      | 1000 | _                   | -   | 666 | -   |         | 500 | _   |            | ns   |

|                                | "High" Level | PWOH               | Fig. 2      | 450  | -                   | -   | 280 | -   | -       | 235 | 1   | <b>-</b> . | ns   |

| φ <sub>2</sub> DMA Pulse Width | "Low" Level  | PW <sub>ØL</sub>   | Fig. 2      | 400  |                     | _   | 230 | -   | _       | 210 | -   | -          | ns.  |

| φ, DMA Rise and Fali           | Time         | Tor, tot           | Fig. 2      |      | -                   | 25  | -   | -   | 25      | -   | _   | 25         | ns   |

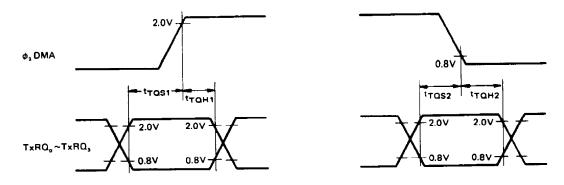

### 2. DMA TIMING (Load Condition Fig. 9)

|                                      |                                                 |                    | Test      |     | HD6844 |          | ٠   | ID68A4 | 4        |     | HD68B4 | 4   | Unit |

|--------------------------------------|-------------------------------------------------|--------------------|-----------|-----|--------|----------|-----|--------|----------|-----|--------|-----|------|

| İtem                                 |                                                 | Symbol             | Condition | min | typ    | max      | min | typ    | max      | min | typ    | max | 0    |

| T DO 0-1 - T-1                       | φ <sub>2</sub> DMA Rising<br>Edge               | t <sub>TQ\$1</sub> |           | 120 | -      | -        | 120 | _      | <u>-</u> | 120 | -      | -   | ns   |

| TxRQ Setup Time                      | φ, DMA Falling<br>Edge                          | t <sub>TQS2</sub>  | Fig. 3    | 210 | _      | -        | 210 | _      | -        | 155 | -      | -   |      |

| Turno unita Timo                     | φ <sub>2</sub> DMA Rising<br>Edge               | t <sub>TQH1</sub>  | Fig. 3    | 20  |        | 1        | 10  | _      | _        | 10  | <br>   | -   | ns   |

| TxRQ Hold Time                       | φ <sub>2</sub> DMA Falling<br>Edge              | <sup>t</sup> TQH2  |           | 20  | _      | _        | 10  | _      | _        | 10  | -      | -   |      |

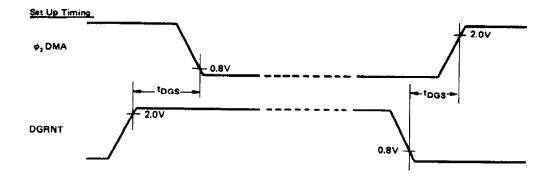

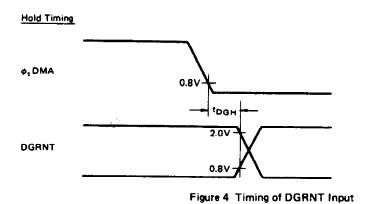

| DGRNT Setup Time                     | DGRNT                                           | <sup>t</sup> DGS   | Fig. 4    | 155 |        |          | 125 | _      |          | 115 |        |     | ns   |

| DGRNT Hold Time                      | DGRNT                                           | <sup>t</sup> DGH   | 7 Fig. *  | 10  |        |          | 10  | _      | _        | 10  | _      |     |      |

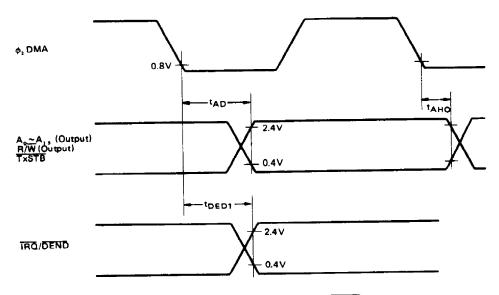

| Address Output<br>Delay Time         | A <sub>0</sub> ~A <sub>15</sub> , R/W,<br>TxSTB | t <sub>AD</sub>    | Fig. 6    | -   | -      | 270      | _   | -      | 180      | _   | -      | 160 | ns   |

| Address Output                       | A <sub>0</sub> ~A <sub>15</sub> , R/W           |                    | Fig. 6    | 30  | -      | <u> </u> | 20  | -      | -        | 20  |        | _   | ns   |

| Hold Time                            | TxSTB                                           | OHA                | Fig. 7    | 35  | -      | -        | 35  | _      | <b>-</b> | 35  | -      |     |      |

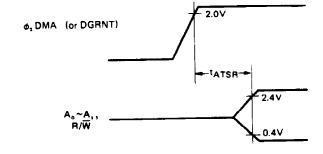

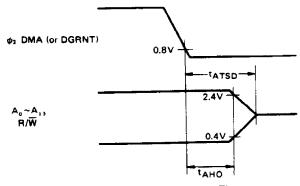

| Address Three-State<br>Delay Time    | A <sub>o</sub> ~A <sub>is</sub> , R/W           | <sup>†</sup> ATSD  | Fig. 7    | -   |        | 270      | _   | _      | 270      | _   | -      | 270 | ns   |

| Address Three-State<br>Recovery Time | A,~A,, R/W                                      | <sup>t</sup> ATSR  | Fig. 7    | _   | _      | 270      | _   | _      | 270      | -   | _      | 270 | ns   |

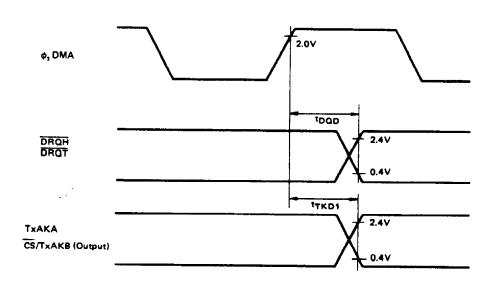

| Delay Time                           | DRQH, DRQT                                      | <sup>†</sup> DQD   | Fig. 5    | -   |        | 375      |     |        | 250      | _   | _      | 210 | ns   |

| T.AK Dalas Time                      | φ <sub>2</sub> DMA Rising<br>Edge               | <sup>†</sup> TKD1  | Fig. 5    | _   | -      | 400      |     |        | 310      |     | _      | 250 | ns   |

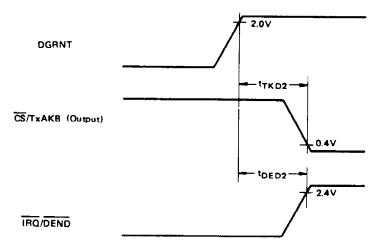

| TxAK Delay Time                      | DGRNT Rising<br>Edge                            | <sup>t</sup> TKD2  | Fig. 8    | -   | -      | 190      | -   | -      | 160      |     | _      | 150 |      |

| IRQ/DEND Delay                       | φ <sub>2</sub> DMA Falling<br>Edge              | <sup>t</sup> DED1  | Fig. 6    | -   | -      | 300      | -   | _      | 250      | -   | -      | 210 | ns   |

| Time                                 | DGRNT Rising<br>Edge                            | †DED2              | Fig. 8    | _   | -      | 190      | -   | -      | 160      | -   | -      | 125 |      |

### 3. BUS TIMING (Load Condition Fig. 9)

### 1) READ TIMING

|                            |                    |                  | Test      |     | HD6844 | 1   | ۱ ۱ | HD68A4 | 4   |     | HD6884 | 4   | Unit |

|----------------------------|--------------------|------------------|-----------|-----|--------|-----|-----|--------|-----|-----|--------|-----|------|

| Item                       |                    | Symbol           | Condition | min | typ    | max | min | typ    | max | min | typ    | max | Omi  |

| Address Setup Time         | A.~A., R/W,        | <sup>t</sup> AS  |           | 140 | -      | -   | 140 | _      | -   | 70  | -      | -   | ns   |

| Address Input Hold<br>Time | A, ~A, R/W,        | t <sub>AHI</sub> |           | 10  | -      | -   | 10  | -      | -   | 10  | _      | -   | ns   |

| Data Delay Time            | D,~D,              | toda             | Fig. 2    | -   | -      | 320 | -   | _      | 220 | _   | -      | 180 | ns   |

| Data Access Time           | D <sub>o</sub> ~D, | tACC             |           | -   | -      | 460 | -   | -      | 360 | _   | -      | 280 | ns   |

| Data Output Hold<br>Time   | D <sub>o</sub> ~D, | t <sub>DHR</sub> |           | 10  | -      | -   | 10  | -      |     | 10  | _      | _   | ns   |

### 2) WRITE TIMING

| İtem                       |                                | Symbol           | Test      |     | HD6844   |     |     | HD68A4 | 4   |     | HD68B4 | 4   |      |

|----------------------------|--------------------------------|------------------|-----------|-----|----------|-----|-----|--------|-----|-----|--------|-----|------|

|                            |                                | 3,               | Condition | min | typ      | max | min | typ    | max | min | typ    | max | Unit |

| Address Setup Time         | A₀~A₄, R/W,<br>CS              | <sup>t</sup> AS  |           | 140 | -        | _   | 140 | _      | -   | 70  | -      | -   | ns   |

| Address Input Hold<br>Time | A, ~A,, R/W,                   | <sup>t</sup> AHI | Fig. 2    | 10  | -        | -   | 10  | -      | -   | 10  | -      | -   | ns   |

| Data Setup Time            | D <sub>0</sub> ~D <sub>1</sub> | tDSW             | 1         | 195 | <u> </u> | -   | 80  | -      | -   | 60  | -      |     | ns   |

| Data Input Hold<br>Time    | D <sub>o</sub> ~D,             | t <sub>DHW</sub> |           | 10  | -        | _   | 10  | -      | _   | 10  | _      | _   | ns   |

Figure 1 Expanded Block Diagram

Figure 2 Read/Write Sequence

Figure 3 Timing of TxRQ Input

Figure 5 Timing of DRQH, DRQT, TxAK Outputs

Figure 6 Timing of Address and IRQ/DEND Outputs

### Recovery Time of Address Three-state

### Delay Time of Address Three-state

Figure 7 Timing of Address Three-state

Figure 8 Timing of Synchronous DGRNT Output

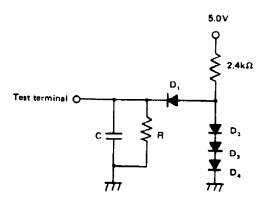

| Test terminal                         | С      | R     |

|---------------------------------------|--------|-------|

| D <sub>0</sub> ~D <sub>7</sub>        | 130 pF | 11 kΩ |

| A <sub>0</sub> ~A <sub>15</sub> , R/W | 90 pF  | 16 kΩ |

| CS/TxAKB                              | 50 pF  | 24 kΩ |

| All other outputs                     | 30 pF  | 24 kΩ |

D<sub>1</sub> ~D<sub>4</sub> : 1\$2074 (€) or equivalent.

Figure 9 Load Circuit

Figure 10 Source Current Messurement Circuit for CS/TxAKB Terminal

#### DEVICE OPERATION

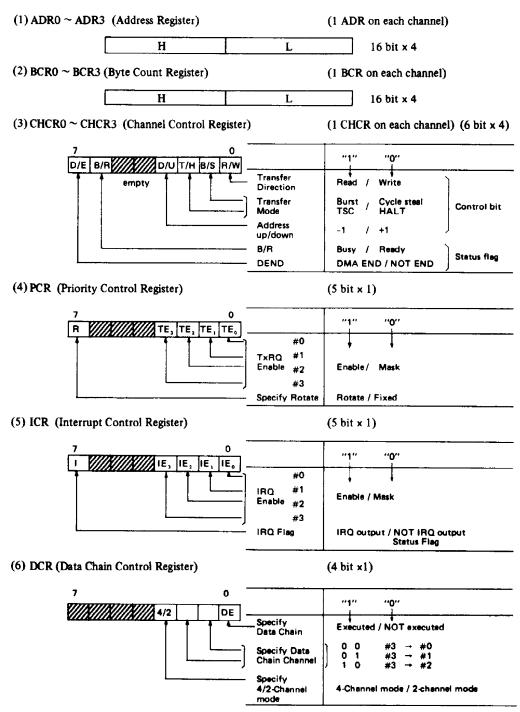

The DMAC has fifteen addressable registers, eight of them are sixteen bits in length. Each channel has a separate Address Register and a Byte Count Register, each of which is sixteen bits. There are also four Channel Control Registers. The three General Control Registers common to all four channels are the Priority Control Register, the Interrupt Control Register, and the Data Chain Register.

To prepare a channel for DMA, the Address Registers must be loaded with the starting memory address and the Byte Count Register loaded with the number of bytes to be transferred. The bits in the Channel Control Register establish the direction of the transfer, the mode, and the address increment or decrement after each cycle. Each channel can be set for one of three transfer modes: Three-State Control (TSC) Steal, Halt Steal, or Halt Burst. Two read-only status bits in the Channel Control Register indicate when the channel is busy transferring data and when the DMA transfer is completed.

The Priority Control Register enables the transfer requests from the peripheral controllers and establishes either a fixed priority or rotating priority scheme of servicing these requests.

When the DMA transfer for a channel is complete (the Byte Count Register is zero), a  $\overline{DMA}$  End signal is directed to the peripheral controller and an  $\overline{IRQ}$  goes to the MPU. Enabling of these interrupts is done in the interrupt Control Register. The IRQ flag bit is read from this register.

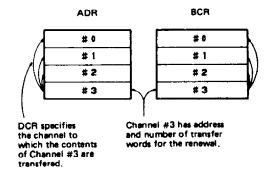

Chaining of data transfers is controlled by the Data Chain Register. When enabled, the contents of the Address and Byte Count Registers for channel #3 are put into the registers of the channel selected for chaining when its Byte Count Register becomes zero. This allows for repetitively reading or writing a block of memory.

During the DMA mode, the DMAC controls the address bus and data bus for the system as well as providing the R/W line and a signal to be used as VMA. When a peripheral device controller desires a DMA transfer, it is requested by a Transfer Request. Assuming this request is enabled and meets the test of highest priority, the DMAC will issue a DMA Request. When the DMAC receives the DMA Grant, it gives a Transfer Acknowledge to the peripheral device controller, at which time the data is transferred. When the channel's Byte Count Register equals zero, the transfer is complete and a DMA End is given to the peripheral device controller, and an IRQ is given to the MPU.

### Initialization

During a power-on sequence, the DMAC is reset via the RES input. All registers, with the exception of the Address and Byte Count Registers, are set to a logic "0" state. This disables all requests and the Data Chain function while masking all interrupts. The Address, Byte Count, and Channel Control Registers must be programmed before the respective transfer request bit is enabled in the Priority Control Register.

#### Transfer Modes

There are three ways in which a DMA transfer may be done. The one used is determined by the data transfer rate required, the number of channels attached, and the hardware complexity allowable. Refer to Figures 12, 16 and 17.

Two of the modes, TSC Steal and Halt Steal, are done by cycle-stealing from the MPU. The Three-State Control (TSC) Steal mode is initiated by the DMAC bringing the  $\overline{DRQT}$  line "Low". This line goes to the system clock driver which returns a "High" on DGRNT on the rising edge of the system  $\phi_1$  clock. The DGRNT signal must cause the address control and data

lines to go to the high impedance state. The DMAC now supplies the address from the Address Register of the channel requesting. It also supplies the  $R/\overline{W}$  signal as determined from the Channel Control Register. After one byte is transferred, control is returned to the MPU. This method stretches the  $\phi_1$  and  $\phi_2$  clocks while the DMAC uses the memory.

The second method of cycle-stealing is the Halt Steal mode. This method actually halts the MPU instead of stretching the  $\phi_1$  clock for the transfer period. This mode is initiated by the DMAC bringing the DRQH line "Low". This line connects to the MPU HALT input. The MPU Bus Available (BA) line is the DGRNT input to the DMAC. While the MPU is halted, its Address Bus, Data Bus, and R/W are in the high impedance state. The DMAC now supplies the address and R/W line. After one byte is transferred, the HALT line is returned "High" and the MPU regains control. In this mode, the MPU stops internal activity and is removed from the system while the DMAC uses the memory.

The third mode of transfer is the Halt Burst mode. This mode is similar to the Halt Steal mode, except that the transfer does not stop with one byte. The MPU is halted while an entire block of data is transferred. When the channel's Byte Count Register equals zero, the transfer is complete and control is returned to the MPU. This mode gives the highest data transfer rate, at the expense of the MPU being inactive during the transfer period.

#### ■ INPUT/OUTPUT FUNCTIONS

### DMAC Interface Signals for the MPU

The DMAC interfaces with the HMCS6800 MPU through the eight-bit bidirectional data bus, the  $\overline{CS}$  line, five address lines, an  $\overline{IRQ}$  line, the Read/Write line, and the  $\overline{RES}$  line. These signals, in conjunction with the HMCS6800 VMA output, permit the MPU to have access to the DMAC. Four other lines associated with the MPU and the clock driver are the  $\overline{DRQT}$ ,  $\overline{DRQH}$ , DGRNT, and the  $\phi_2$  DMA.

### Bidirectional Data (Do~D7)

I/O Pin No. 28 ~ 21

The Bidirectional Data lines  $(D_0 \sim D_7)$  allow for data transfer between the DMAC and the MPU. The data bus output drivers are three-state devices that remain in the high impedance state except when the MPU performs DMAC read operations.

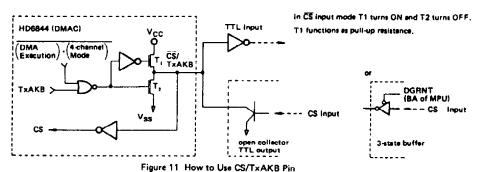

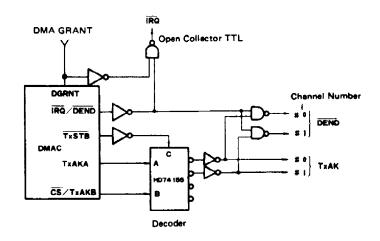

### Chip Select/Transfer Acknowledge B (CS/T x AKB)

This line is multiplexed, serving both as an input and an output.  $\overline{\text{CS}}/\text{TxAKB}$  is an output in the four-channel mode during the DMA transfer. At all other times, it is a high impedance TTL compatible input used to address the DMAC. The DMAC is selected when  $\overline{\text{CS}}/\text{TxAKB}$  is "Low". VMA must be used in generating this input to insure that false selects will not occur. Transfers of data to and from the DMAC are then performed under the control of the  $\phi 2$  DMA, Read/Write, and  $A_0 \sim A_4$  address lines. In the four-channel mode when TxAKB is needed, the  $\overline{\text{CS}}$  gate must have an open-collector output (a pull-up resistor should not be used). In the two-channel mode,  $\overline{\text{CS}}/\text{TxAKB}$  is always an input.

### Address Lines $(A_0 \sim A_4)$

Address lines  $A_0 \sim A_4$  are both input and output lines. In the MPU mode, these are high impedance inputs used to address the DMAC registers. In the DMA mode, these lines are outputs which are set to the contents of the Address Register of the channel being processed.

### Interrupt Request/DMA End (IRA/DEND)

Output Pin No. 33

IRQ/DEND is a TTL compatible, active "Low" output that is used to interrupt the MPU and to signal the peripheral controller that the data <u>block transfer</u> has ended. If the Interrupt has been enabled, the <u>IRQ/DEND</u> line will go "Low" after the last DMA cycle of a transfer. An open collector gate must be connected to DGRNT and <u>IRQ/DEND</u> to prevent false interrupts from the DEND signal when interrupts are not enabled. Refer to the section of "DMA End Control".

### • Read/Write (R/W)

I/O Pin No. 3

Read/Write is a TTL compatible line that is a high impedance input in the MPU mode and an output in the DMA mode. In the MPU mode, it is used to control the direction of data flow through the DMAC's input/output data bus interface. When Read/Write is "High" (MPU read cycle) and the chip is selected, DMAC data output buffers are turned on and a selected register is read. When it is "Low", the DMAC output drivers are turned off and the MPU writes into a selected register.

In the DMA mode, Read/Write is an output to drive the memory and peripheral controllers. Its state is determined by bit 0 of the Channel Control Register for the channel being serviced. When Read/Write is "High", the memory is read and the data from the memory is written into the peripheral controller. When it is "Low", the peripheral controller is read and its data stored in the memory. In the DMA mode, the DMAC data buffers are off.

### Rest (RES)

Input Pin No. 39

The RES input provides a means of resetting the DMAC from an external source. In the "Low" state, the RES input causes all registers, with the exception of the Address and Byte Count Registers, to be reset to the logic "0" state. This disables all transfer requests, masks all interrupts, disables the data chain function, and puts each Channel Control Register into the condition of memory write, Halt Steal transfer mode, and address increment.

### Transfer Signals to the MPU

Two DMA request output lines and a DMA Grant input line, together with the system clock, synchronize the DMAC with the MPU system.

### DMA Request Three-State Control Steal (DRQT)

Output Pin No. 37

This active "Low" output requests a DMA transfer for a channel configured for the TSC Steal transfer mode. This line is connected to the system clock driver, requesting a  $\phi_1$  clock stretch. It will remain in the "Low" state until the transfer has begun.

### DMA Request Hait (DRQH)

Output Pin No. 36

This active "Low" output requests a DMA transfer for a channel programmed for the Halt Steal or Halt Burst mode transfer. This line is connected directly to the MPU HALT input and remains "Low" until the last byte has begun to be transferred.

### DMA Grant (DGRNT)

Input Pin No. 38

This is a high impedance input to the DMAC, giving it control of the system busses. For the TSC Steal mode, the signal comes from the system clock drive circuit (DMA Grant), indicating that the clock is being stretched. For either of the Halt modes, the signal is the Bus Available from the MPU, indicating that the MPU has

halted and turned control of its busses over to the DMAC. For a design involving TSC Steal and Halt mode transfers, this input must be the OR of the clock driven DMA Grant and the MPU BA.

#### $\phi_2$ DMA

Input Pin No. 40

Transferring in and out of the DMAC registers, sampling of channel request lines and gating of other control signals to the system is done internally in conjunction with the  $\phi_2$  DMA high impedance input. This input must be the system memory clock (non-stretched  $\phi_2$  clock).

### Transfer Signals From the Peripheral Controller

### Transfer Request (T × RQ<sub>0</sub> ~ T × RQ<sub>3</sub>)

Input Pin No.  $32 \sim 29$

Each of the four channels has its own high impedance input request for transfer line. The peripheral controller requests a transfer by setting its  $T \times RQ$  line "High" (a logic "1"). The lines are sampled according to the priority and enabling established in the Priority Control Register. In the Steal mode and the first byte of the Halt Burst mode, the  $T \times RQ$  signals are tested on the positive edge of  $\phi_2$  DMA and the highest priority channel is strobed. Once strobed, the  $T \times RQ$ s are not tested until that channel's data transfer is finished. In the succeeding bytes of the Halt Burst mode transfer, the  $T \times RQ$  is tested on the negative edge of  $\phi_2$  DMA, and data is transferred on the next  $\phi_2$  DMA cycle if  $T \times RQ$  is "High".

### Transfer Signals to the Peripheral Controller

Two encoded lines select the channel to be serviced. A strobe line acknowledges the request and performs the transfer. The DEND line signals to the peripheral controller that the DMA transfer is completed.

### Transfer Acknowledge A (T × AKA)

Output Pin No. 35

The Transfer Acknowledge LA ( $\underline{T} \times AKA$ ) is a TTL compatible output used in conjunction with the  $\overline{CS}/T \times AKB$  line to select the channel to be strobed for transfer and to give the DMA End Signal. In the two-channel mode, only  $T \times AKA$  is used to select channel 0 or channel 1, and  $\overline{CS}/T \times AKB$  is always an input.

### Chip Select/Transfer Acknowledge B (CST/×AKB)

I/O Pin No. 2

In the DMA mode, this dual purpose line is encoded together with  $T \times AKA$  to select the channel being serviced. Table 1 shows the encoding order.

| CS/T x AKB | T×AKA | Channel # |

|------------|-------|-----------|

| 0          | 0     | 0         |

| 0          | 1     | 1         |

| 1          | 0     | 2         |

| 1          | 1     | 3         |

### Transfer Strobe (T×STB)

Output Pin No. 34

The  $\overline{T \times STB}$  causes acknowledgement to be given to the peripheral controller and transfers the data to or from the memory. This line is also intended to be the VMA  $\underline{signal}$  for the system in the DMA mode. In a one-channel system,  $\overline{T \times STB}$  may be inverted and run to the peripheral  $\underline{controller}$ 's Acknowledge input. In a two or  $\underline{four}$ -channel system,  $\overline{T \times STB}$  enables the decode of  $\overline{T \times AKA}$  and  $\overline{CS/T \times AKB}$  to select the device controller to be acknowledged.

### **@HITACHI**

### Interrupt Request/DMA End (IRQ/DEND)

In the DMA mode, this dual purpose line is "Low" for the last byte of transfer, indicating a DMA End. This occurs when the Byte Count register decrements to zero.

This line, through the decode of TxAKA and CS/TxAKB, can be used to strobe a DMA End to each device controller.

#### Address Lines to the Memory

### Address Lines (A<sub>0</sub>~A<sub>15</sub>)

These output lines are in the high impedance state during the MPU mode. In the DMA mode, these lines are outputs which are set to the contents of the Address Register of the channel being processed.

### ■ THE DMAC REGISTERS

The HD6844 (DMAC) has Address Register (ADR), Byte Count Register (BCR), Channel Control Register (CHCR), and General Control Register (GCR).

General Control Register (GCR) is composed of Priority Control Register (PCR) that controls priority among the channels, Interrupt Control Register (ICR) that controls interrupt and Data Chain Control Register (DCR) that controls data chain function, Refer to Table 2 and Figure 1.

These are Read/Write registers and MPU can exchange the data with DMAC when  $\overline{CS}$  is at "Low" level,  $A_0 \sim A_4$  specifies the address of the registers. How to specify the registers is shown in Table 2.

2-byte ADR and BCR can be read or written by one instruction, using 2-byte instruction of the MPU.

### Function of Internal Registers ADR (Address Register)

Each channel has 16-bit Address Register. Initial address of memory used for DMA transfer is programmed to this register. The contents of ADR are output to address bus  $(A_0 \sim A_{15})$  during DMA transfer operation. When 1-byte transfer has completed, the 16-bit address is incremented or decremented by

The address which the MPU reads out is the renewed one, that is, the memory address for the next transfer. When 1-block transfer has completed, final memory address +1 or -1 is read

| Table 2 | Internal  | Registers   | of the | DMAC |

|---------|-----------|-------------|--------|------|

|         | Internati | - NOUISIOIS | UI UI  |      |

|                             |        | l       |                | Add                   | iress Bus S    | ignal          |                | Address      |  |

|-----------------------------|--------|---------|----------------|-----------------------|----------------|----------------|----------------|--------------|--|

| Register Name               | Symbol | Channel | A <sub>4</sub> | <b>A</b> <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | (Hexadecimal |  |

|                             | ADRH   | 0       | 0              | 0                     | 0              | 0              | 0              | 0.0          |  |

| Address Register            | ADRL   | 0       | 0              | 0                     | 0              | 0              | 1              | 01           |  |

|                             | BCRH   | 0       | 0              | 0                     | 0              | 1              | 0              | 02           |  |

| Byte Count Register         | BCRL   | 0       | 0              | 0                     | 0              | 1              | 1              | 03           |  |

|                             | ADRH   | 1       | 0              | 0                     | 1              | 0              | 0              | 04           |  |

| Address Register            | ADRL   | 1       | 0              | 0                     | 1              | 0              | 1              | 0.5          |  |

|                             | BCRH   | 1 1     | 0              | 0                     | 1              | 1              | 0              | 06           |  |

| Byte Count Register         | BCRL   | 1       | 0              | 0                     | 1              | 1              | 1              | 0 7          |  |

|                             | ADRH   | 2       | 0              | 1                     | 0              | 0              | 0              | 0.8          |  |

| Address Register            | ADRL   | 2       | 0              | 1                     | 0              | 0              | 1              | 09           |  |

|                             | BCRH   | 2       | 0              | 1                     | 0              | 1              | 0              | 0 A          |  |

| Byte Count Register         | BCRL   | 2       | 0              | 1                     | 0              | 1              | 1              | ОВ           |  |

|                             | ADRH   | 3       | 0              | 1                     | 1              | 0              | 0              | 0 C          |  |

| Address Register            | ADRL   | 3       | 0              | 1                     | 1              | 0              | 1              | Q O          |  |

|                             | BCRH   | 3       | 0              | 1                     | 1              | 1              | 0              | 0 E          |  |

| Byte Count Register         | BCRL   | 3       | 0              | 1                     | 1              | 1              | 1 1            | 0 F          |  |

|                             | CHCR   | 0       | 1              | 0                     | 0              | 0              | 0              | 10           |  |

|                             | CHCR   | 1       | 1              | 0                     | 0              | 0              | 1              | 11           |  |

| Channel Control Register    | CHCR   | 2       | 1              | 0                     | 0              | 1              | 0              | 1 2          |  |

|                             | CHCR   | 3       | 1              | 0                     | 0              | 1              | 1              | 13           |  |

| Priority Control Register   | PCR    | -       | 1              | 0                     | 1              | 0              | 0              | 14           |  |

| Interrupt Control Register  | ICR    | -       | 1              | 0                     | 1              | 0              | 1              | 1 5          |  |

| Data Chain Control Register | DCR    | _       | 1              | 0                     | 1              | 1              | 0              | 1 6          |  |

(NOTE) 1) All the registers can be accessed by Read/Write operation. Unused bit of the register is read out "0".

2) H/L of ADR and BCR meens the higher (H) 8 bits/the lower (L) 8 bits of a 16-bit register.

3) Being allocated to continuous address, 16-bit ADR and BCR can be read or written by one instruction, using MPU's 2-byte LOAD/STORE instruction.

Register Address

e.g. LDX \$ \_\_\_ 0 \overline{\text{C}} \overline{\text{C}} \overline{\text{C}} \overline{\text{C}} \overline{\text{L}} \overline{\text{C}} \overline{\text{C}} \overline{\text{C}} \overline{\text{C}} \overline{\text{L}} \overline{\text{C}} \overline{\

### **BCR (Byte Count Register)**

Each channel has a 16-bit Byte Count Register. Number of DMA transfer words is programmed into this register. The content of the Byte Count Register is decremented by one everytime one-byte transfer has completed. When it becomes "0", DEND output goes "Low" level and informs I/O controller of the end of one-block DMA transfer. When IRQ is not masked, IRQ output goes "Low" level and MPU is interrupted to be informed of the end of DMA transfer. Moreover, IRQ and DEND signals are output, multiplexed with IRQ/DEND pin.

### CHCR (Channel Control Register)

Each channel has Channel Control Register. This register is

used to program the control information of its corresponding channel. Structure of CHCR is shown in Table 3.

(1) R/W Control (specifies the direction of transfer) Bit - CHCR Bit 0

This bit controls the direction of DMA transfer. When it is at "1", R/W signal of DMAC goes "High" level during DMA transfer operation. This means to read out memory and write into I/O controller, that is, data is transferred from memory to I/O controller.

When it is at '0", R/W output goes "Low" level and data is transferred from I/O controller to memory.

Table 3 Bit Structure of CHCR (Channel Control Register)

| Bit | Name              | Read/Write | Function                                                     |                                                             |  |  |  |  |  |

|-----|-------------------|------------|--------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|

| No. | 149116            | Head/Wille | "1"                                                          | "0"                                                         |  |  |  |  |  |

| 0   | R/W               | R/W        | Transfer from memory to I/O controller (R/W output = "High") | Transfer from I/O controller to memory (R/W output = "Low") |  |  |  |  |  |

| 1   | Burst/Cycle Steal | R/W        | Burst Mode                                                   | Cycle Steal Mode*                                           |  |  |  |  |  |

| 2   | TSC/HALT          | R/W        | TSC Mode                                                     | HALT Mode*                                                  |  |  |  |  |  |

| 3   | Address down/up   | R/W        | Address: -1                                                  | Address: +1                                                 |  |  |  |  |  |

| 4   | Not used          | _          | _                                                            | _                                                           |  |  |  |  |  |

| 5   | Not used          | _          | _                                                            | _                                                           |  |  |  |  |  |

| 6   | Busy/Ready Flag   | R          | Busy<br>(DMA Transfer Operation)                             | Ready<br>(No DMA Transfer Operation                         |  |  |  |  |  |

| 7   | DEND Flag         | R          | DMA End & Interrupt                                          | No Interrupt                                                |  |  |  |  |  |

Burst transfer in TSC mode is prohibited. R: Read, W: Write

Note that during DMA transfer operation, the function of  $R/\overline{W}$  signal is accommodated to the memory Read/Write operation. Therefore, on the side of I/O device during DMA transfer operation,  $R/\overline{W}$  input should be interpreted in inverse of the MPU Read/Write. That is, data should be output when  $R/\overline{W}$  input is at "Low" level (In the case of MPU's read operation, I/O device outputs the data when it is at "High" level).

This arises from that during DMA transfer operation, I/O side performs data transfer independently instead of MPU. Moreover, such family LSI as HD6843 (FDC), etc. has this function and R/W signal is automatically interpreted inversely.

### (2) Burst/Cycle Steal Bit - CHCR Bit 1

This bit is used to decide that DMA transfer should be performed in burst mode or cycle steal mode. When it is at "1", it specifies burst mode. That is, once DMA transfer is performed, MPU remains stopped until one-block data transfer is completed.

When this bit is "0", it specifies cycle steal mode. That is, everytime one-byte transfer has completed, MPU takes back the bus control, and DMA transfer and MPU operation are performed in time sharing.

(NOTE) Only in the case of HALT mode, burst mode can be specified. In TSC mode, burst mode cannot be specified.

### (3) TSC/HALT Mode Bit - CHCR Bit 2

This bit is used to decide that DMA transfer should be

performed by using MPU's TSC function or HALT function. When it is at "0", DMA transfer request signal is output from DRQH of DMAC.

When it is at "1", DMA transfer request signal is output from DROT of DMAC.

### (4) Address down/up Bit - CHCR Bit 3

This bit is used to decide that the address of memory region used for DMA transfer should be renewed up (increment of address) or down (decrement of address). When it is at "1", the address is decremented by one after one-byte transfer. When it is at "0", the address is incremented by one.

### (5) Busy/Ready Flag Bit - CHCR Bit 6

This bit is a status flag to indicate whether its corresponding channel is performing DMA transfer or not. (READ only)

When it receives the first TxRQ of its corresponding channel, it goes to "1". When one-block transfer is completed and BCR becomes "0", it is reset to "0".

Also this flag is cleared when corresponding TxRQ Enable Bit in the PCR becomes "0".

### (6) DEND Flag Bit - CHCR Bit 7

This bit is an interrupt flag to indicate that one-block DMA transfer of its corresponding channel has completed. (READ only).

When one-block transfer of its corresponding channel is completed and BCR becomes "0", it goes to "1". As soon as this flag is read out, i.e. CHCR of this channel is read

### **OHITACHI**

out, it is reset to "0".

Moreover, this bit is connected to IRQ output. When it is at "1" and IRQ enable bit (within ICR register described later) is at "1", IRQ output goes "Low" level.

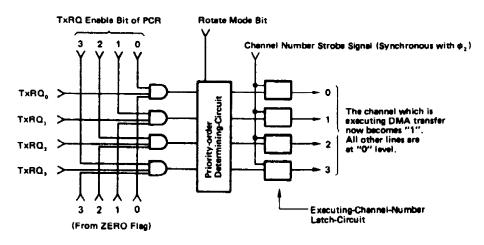

### PCR (Priority Control Register)

Priority Control Register is a 5-bit register to decide the operation mode of priority control circuit. Structure of PCR is shown in Table 4.

Table 4 Bit Structure of PCR (Priority Control Register)

| Bit |                                     | Read   | Fu                             | nction                                             |

|-----|-------------------------------------|--------|--------------------------------|----------------------------------------------------|

| No. | Name                                | /Write | "1"                            | 0                                                  |

| 0   | TxRQ Enable #0 (TxEN <sub>0</sub> ) | R/W    | TxRQ of Channel 0 is accepted. | TxRQ of Channel 0 is not accepted                  |

| 1   | TxRQ Enable #1 (TxEN <sub>1</sub> ) | R/W    | TxRQ of Channel 1 is accepted. | TxRQ of Channel 1 is not accepted                  |

| 2   | TxRQ Enable #2 (TxEN <sub>2</sub> ) | R/W    | TxRQ of Channel 2 is accepted. | TxRQ of Channel 2 is not accepted                  |

| 3   | TxRQ Enable #3 (TxEN <sub>3</sub> ) | R/W    | TxRQ of Channel 3 is accepted. | TxRQ of Channel 3 is not accepted                  |

| 4   | ]                                   | - 1    | _                              |                                                    |

| 5   | Not used                            | -      | <del>-</del>                   | <del>-</del>                                       |

| 6   |                                     | _      | _                              |                                                    |

| 7   | Rotate Control                      | R/W    | Rotate Mode                    | The order of priority is fixed at numerical order. |

R: Read, W: Write

### (1) TxRQ Enable Bit (TxEN<sub>0</sub>~TxEN<sub>3</sub>) - PCR Bit 0~3

Each channel has this TxRQ Enable bit. When it is at "1", TxRQ input of its corresponding channel is accepted to perform DMA transfer. When it goes to "0", TxRQ of its corresponding channel is masked not to be received and TxAK is not output. During DMA transfer operation, when this bit goes to "0" before BCR becomes "0", following TxRQ input is not accepted and DMA transfer is interrupted. Then contents of ADR and BCR remain unchanged. When it rises to "1" again, DMA transfer is reopened. Therefore, in the case of cycle steal DMA, it is possible for the program to change the priority of the specific channel temporarily by manipulating this bit.

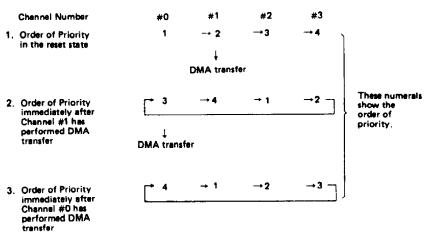

(2) Rotate Control Bit - PCR Bit 7

When this bit is at "0", the order of priority among DMA channels is fixed at numerical order. That is, Channel 0 is given a first priority and then is followed by Channel  $1 \rightarrow 2 \rightarrow 3$ .

When this bit is at "1", priority control is due to rotate mode. That is, the channel that ended in the first time is given a first priority and the channel ended in the last time is controlled to be given a last priority.

### ICR (Interrupt Control Register)

Interrupt Control Register is a 5-bit register to control  $\overline{IRQ}$  output. Its structure is shown in Table 5.

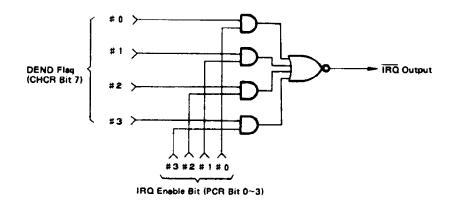

(1) IRQ Enable Bit - ICR Bit 0~3

Each channel has IRQ Enable Bit. When this bit is at "1" and DEND Flag of its corresponding channel is set to "1". IRQ output goes "Low" level. But when it is at "0", IRQ output is masked not to be output even if DEND Flag is set to "1".

These bits enable to control to output only a necessary channel to IRO.

(2) IRQ Flag - ICR Bit 7

This is a read-only bit and the status of IRQ output is directly reflected on it. That is, when IRQ output goes to "Low" level, it becomes "1".

IRQ output of DMAC is output as logical OR of 4-channel DEND Flag according to the following equation. IRQ = (DEND<sub>0</sub>·IRQ Enable<sub>0</sub>) + (DEND<sub>1</sub>·IRQ

Enable<sub>1</sub>) + (DEND<sub>2</sub>·IRQ Enable<sub>2</sub>) + (DEND<sub>3</sub>·IRQ Enable<sub>3</sub>)

### DCR (Data Chain Control Register)

Data Chain Control Register is a 4-bit register and three of those bits are used to control data chain function. Remaining one bit is used to specify 2-channel/4-channel mode.

Structure of DCR is shown in Table 6.

### (1) Data Chain Enable Bit - DCR Bit 0

When this bit is at "1", data chain function of DMAC is enabled. That is, when DMA transfer of a specified channel has completed and BCR goes to "0", the contents of ADR and BCR of Channel #3 are automatically transferred to ADR and BCR of the specified channel.

(2) Data Chain Channel Bit - DCR Bit 1~2

These bits are used to specify which channel should be used for the data chain. How to specify the channel is shown in Table 7. Data Chain Channel bit specifies the channel to which data should be transferred from Channel #3. Channel #3 contains the data for replacement. Channel #3 is fixed and cannot be changed.

(3) 2/4-channel Mode Bit - DCR Bit 3

This bit has no relation to the data chain function.

It is used to specify whether  $\overline{CS}/TxAKB$  is used for only input pin or I/O pin. When this bit is "0",  $\overline{CS}/TxAKB$  becomes  $\overline{CS}$  input pin in 2-channel mode since TxAKB output is not necessary for application up to 2-channel.

When this bit is "1", CS/TxAKB becomes I/O pin in 4-channel mode (See Fig. 11).

## 5

Table 5 ICR (Interrupt Control Register)

| Bit | Name          | Read   | Function                               |                                    |  |

|-----|---------------|--------|----------------------------------------|------------------------------------|--|

| No. | Name          | /Write | "1"                                    | "0"                                |  |

| 0   | IRQ Enable #0 | R/W    | IRQ of Channel 0 is able to be output. | IRQ output of Channel 0 is masked. |  |

| 1   | IRQ Enable #1 | R/W    | IRQ of Channel 1 is able to be output. | IRQ output of Channel 1 is masked. |  |

| 2   | IRQ Enable #2 | R/W    | IRQ of Channel 2 is able to be output, | IRQ output of Channel 2 is masked. |  |

| 3   | IRQ Enable #3 | R/W    | IRQ of Channel 3 is able to be output. | IRQ output of Channel 3 is masked. |  |

| 4   |               | _      | -                                      | -                                  |  |

| 5   | Not used      | _      | . <del>-</del>                         | _                                  |  |

| 6   | J             | _      |                                        | _                                  |  |

| 7   | IRQ Flag      | R      | IRQ output "Low"                       | IRQ output "High" (off state)      |  |

R: Read, W: Write

Table 6 Bit Structure of DCR (Data Chain Control Register)

| Bit | Name                   | Read<br>/Write | Function                                                              |                                                            |  |

|-----|------------------------|----------------|-----------------------------------------------------------------------|------------------------------------------------------------|--|

| No. | Name                   |                | "1"                                                                   | "0"                                                        |  |

| 0   | Data Chain Enable      | R/W            | Data Chain is performed.                                              | Data Chain is not performed.                               |  |

| 1   | D . O . O              | R/W            | The channel which performs Data                                       |                                                            |  |

| 2   | Data Chain Channel R/W |                | (The channel where contents of ADR and BCR of Channel #3 are loaded.) |                                                            |  |

| 3   | 2/4-Channel Mode       | R/W            | 4-Channel Mode (CS/TxAKB is I/O pin.)                                 | 2-Channel Mode (CS/TxAKB is designated to only input pin.) |  |

| 4   |                        |                | _                                                                     | _                                                          |  |

| 5   | Not used               | _              | _                                                                     | -                                                          |  |

| 6   |                        | -              | _                                                                     | _                                                          |  |

| 7   |                        |                |                                                                       |                                                            |  |

R: Read, W: Write

Table 7 How to specify Data Chain Channel

| DCR<br>Bit 1 | DCR<br>Bit 2 | Specified<br>Channel |

|--------------|--------------|----------------------|

| 0            | 0            | Channel #0           |

| 1            | 0            | Channel #1           |

| 0            | 1            | Channel #2           |

| 1            | 1            | _                    |

MPU Mode

DMA Mode

T×STB

DGRNT

CS = input

T×AKB = output

CS

T×AKB

Figure 11A CS/T × AKB input/output Timing

### . OPERATION OF THE DMAC

### Transfer Mode of the DMAC

There are three DMA transfer modes such as HALT Cycle Steal, HALT Burst and TSC Cycle Steal. Operation in each mode is explained in the following.

### **HALT Cycle Steal Mode**

This is a basic DMA transfer mode utilizing HALT state of MPU. In this mode, everytime 1-byte transfer has completed, MPU takes back the bus control and executes instruction cycle. That is, DMA transfer and MPU operation are performed in time sharing.

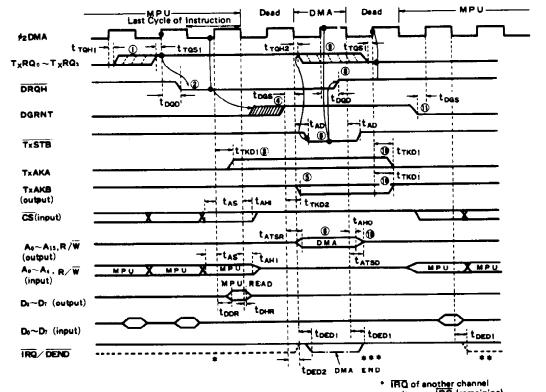

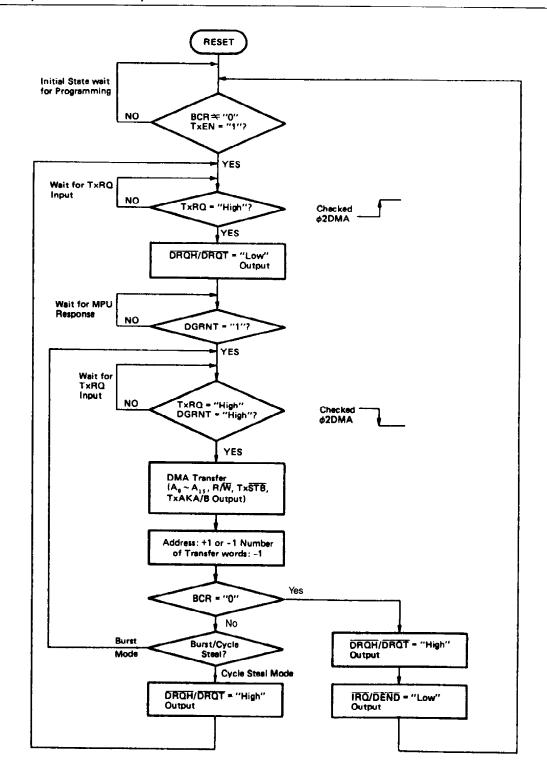

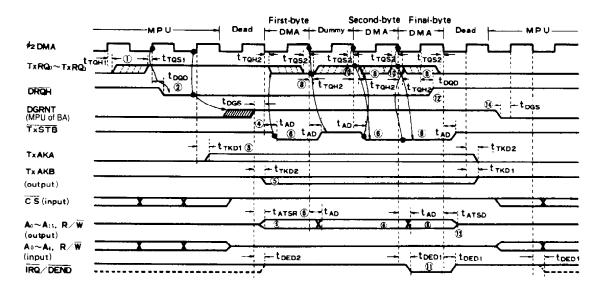

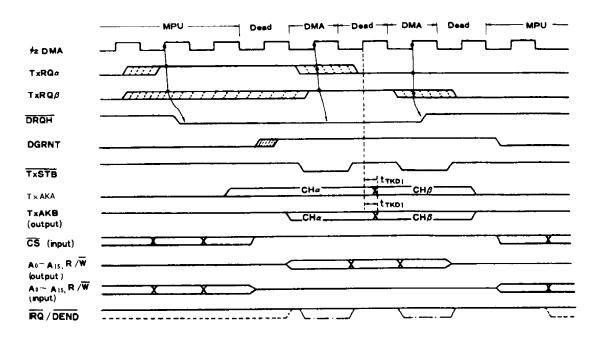

Timing chart is shown in Fig. 12 and flow chart is shown in Fig. 13. Procedure of transfer operation is the following. (No.  $\bigcirc$   $\frown$   $\bigcirc$  in Fig. 12 correspond to the following items.)

- TxRQ<sub>0</sub>~TxRQ<sub>3</sub> input is checked at the rising edge of \$\phi 2DMA. When it is at "High" level, it gets into the following operation.

- ② DROH="Low" is output and MPU is requested to stop its operation.

- TxAKA is driven (Level output).

- MPU stops its operation and DMAC waits until DGRNT goes to "High" level.

- (5) When DGRNT goes to "High" level, DMAC drives TxAKB, A0~A15 and R/W lines.

- ® TxSTB is given to perform DMA transfer.

- Address is incremented or decremented by one and number of transfer words is decremented by one.

- When DRQH rises to "High" level, MPU gets into Instruction Cycle again.

- TxRQ falls to "Low" level.

- 10  $A_0 \sim A_{15}$  and  $R/\overline{W}$  get into high impedance state again.

- 1 DGRNT falls to "Low" level.

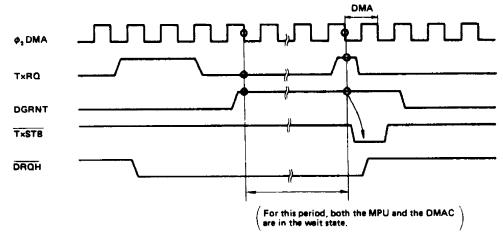

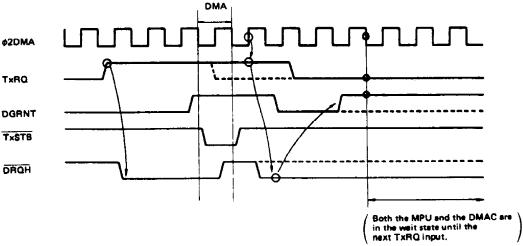

- [Note] TxRQo~TxRQo input in HALT cycle steal is, in principle as shown in Fig. 12, set to "High" every 1-byte transfer on account of I/O request. When TxSTB of the DMAC is driven, it is reset to "Low". Take care not to be against this principle, or the following states may happen.

- (1) In the case where TxRQ becomes "High", but it is reset to "Low" before DGRNT becomes "High". In this case, the DMAC is in the wait state without sending out TxSTB until TxRQ rises to "High" again. As DRQH remains "Low" the MPU is forced to be stopped, and the system is in dead lock state until TxRQ rises to "High" again (Fig. 14).

- (2) In the case where TxRQ is not reset to "Low" though TxSTB has been driven.

In this case, unless TxRQ returns to "Low" by the time φ<sub>2</sub>DMA rises after TxSTB has risen to "High", it is considered as a new I/O request, which leads the above-mentioned operation ①,②——. If TxRQ falls to "Low" immediately after that, the same state as (1) happens (Fig. 15).

\* IRQ of another channel or its own IRQ (remaining) \*\* Its own IRQ (output) or its own IRQ (remaining) or IRQ of another channel \*\*\* This is the last cycle of transfer

Figure 12 HALT Cycle Steal Mode

Figure 13 Flow Chart of DMAC Operation

Figure 14 Extraordinary TxRQ Input (1)

In the case where TxRQ is reset to "Low" before the transfer

Figure 15 Extraordinary TxRQ Input (2)

$\left(\begin{array}{c} \text{In the case where TxRQ doesn't fall to "Low" after the transfer has been completed.} \end{array}\right)$

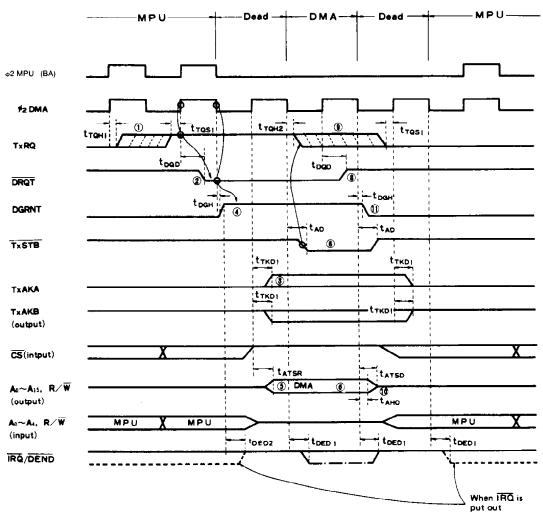

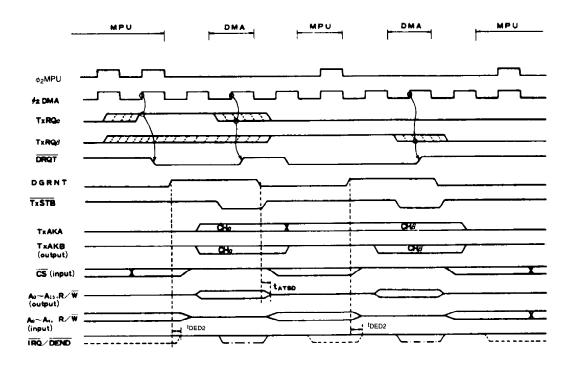

#### **HALT Burst Mode**

In the case of cycle steal mode, MPU gets into Instruction Cycle everytime 1-byte transfer has completed. But in the case of burst mode, MPU remains stopped until 1-block transfer is finished. That is, DRQH continues to be output "Low" level until BCR becomes "0".

Its timing chart and flow chart are shown in Fig. 16 and Fig. 13 respectively. Procedure of transfer is the following (No. ①

- ~ 14 in Fig. 16 correspond to the following items).

- TxRQ input is checked at the rising edge of \$\phi\_2\$ DMA. When

it is at "High" level, it gest into the following operation.

- ② DRQH="Low" level is given and MPU is requested to stop its operation

- 3 TxAKA is driven.

- 4 MPU stops and DMAC waits for DGRNT rising "High" level.

- When DGRNT rises "High" level, DMAC drives TxAKB, A<sub>0</sub> ~A<sub>15</sub>, and R/W lines.

- 6 TxSTB is sent out to perform DMA transfer.

- Address is incremented or decremented by one and number of transfer words is decremented by one.

- ® TxRQ falls to "Low" level.

- When number of transfer words is 0, from 10 to 40 operations are performed.

- When BCR is not "0", TxRQ is checked at the falling edge of φ<sub>2</sub> DMA.When TxRQ is at "High" level, DMA transfer is performed through (6) ~ (8) again. When TxRQ is not at "High" level, DMAC waits for becoming "High" level.

- ① IRQ/DEND output goes to "Low" level.

- ③  $A_0 \sim A_{15}$  and  $R/\overline{W}$  get into high impedance state.

- (A) DGRNT falls to "Low" level.

The transfer of the first byte ( $\bigcirc$   $\sim$   $\bigcirc$ ) is performed in the same way as that in HALT cycle steal mode. But in the second-byte and subsequent transfer, TxRQ is checked at the falling edge of  $\phi_2$  DMA and if TxRQ is at "High" level, DMA transfer is performed at the following cycle. Therefore, a high-speed response (MAX. 1 byte/1 cycle) is feasible.

In burst mode, TxRQ should be also, in principle, set to "High" when I/O request is asserted, and reset to "Low" when TxSTB goes to "Low". If TxRQ is asserted as level input without being reset, DMA transfer is performed at all cycles of  $\phi_2$  DMA since TxRQ is always at "High" level at the falling edge of  $\phi_2$  DMA. Its example is shown in the second-byte and the third-byte transfer in Fig. 16.

Figure 16 HALT Burst Mode

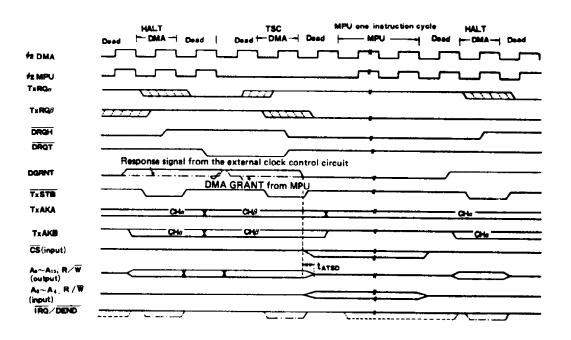

### TSC Cycle Steal Mode

In the above-mentioned modes, DMA is performed by using the HALT function of the MPU. In TSC cycle steal mode, DMA is performed by using the TSC function of the MPU.

Its timing chart and flow chart are shown in Fig. 17 and Fig. 13 respectively.

Basic operation of the DMAC is the same as that in HALT cycle steal mode, but the detailed timing is different. The difference is explained in the following.

- (1) DRQT is used for DMA transfer request instead of DRQH.

- (2) DROT is sent to the external clock control circuit to

extend clock E  $(\phi_2)$  of MPU.

(3) To DGRNT, the external clock control circuit inputs response signals.

In TSC mode, there isn't a burst mode. Because the MPU clock cannot be extended for a long time because MPU performs dynamic operation. When TSC mode is specified, DRQT returns to "High" and the MPU gets into the instruction cycle everytime 1-byte transfer has finished.

Figure 17 TSC Cycle Steal Mode

### • Priority Control Basic priority Control

There are two kinds of the DMAC priority control function. One is to mask TxRQ on each channel by TxRQ Enable bit of PCR. The other is priority-order-determining-circuit which the DMAC has as a hardware.

Moreover, the priority-order-determining-circuit has two operation modes (the rotate mode and the normal mode).

Structure of the priority control circuit is shown in Fig. 18. As shown in Fig. 18, TxRQ of the channel whose TxRQ Enable bit is at "1" level becomes an input of the priority-order-determining-circuit. Then it is checked whether TxRQ is at "High" level or not.

(Note) In this case, ZERO flag needs to be at "1" level. ZERO flag will be described later.

If one of TxRQ<sub>0</sub>~TxRQ<sub>3</sub> is at "High" level, its channel is selected, being given a first priority. Then it is latched by an executing-channel-number-latch-circuit to perform DMA transfer. Once an executing channel is determined and latched, it is unchanged until its DMA transfer has been completed. That is, the channel number strobe signal of DMAC doesn't go to "1" and the contents of the channel-number-latch-circuit are unchanged. In the cycle steal mode, the channel is fixed until 1-byte transfer has completed. In the burst mode, it is fixed until BCR becomes "0".

Figure 18 Structure of Priority Control Circuit

Therefore, once a long-period DMA transfer of a channel is performed in the burst mode, other channels need to wait until it has completed even if they have higher priority than the channel. Take much care to this point in designing response time to TxRQ of DMA channel.

(Note) As explained above, TxRQ input is latched internally. So

once it is accepted and latched, the channel number cannot be changed even though it returns to "Low". But as explained in HALT Cycle Steal Mode, DMA transfer is not performed unless TxRQ rises to "High" again.

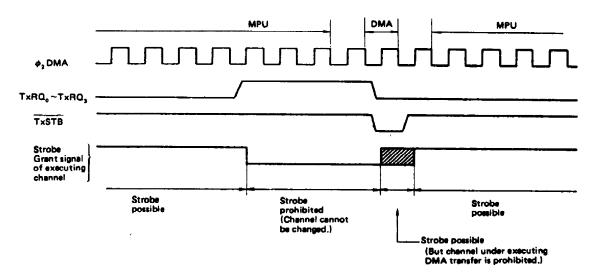

Strobe timing of executing-channel-number-latch-circuit which allow modification or decision of executing channel is shown in Fig. 19.

Figure 19 Strobe Timing of Executing-Channel-Number-Latch-Circuit (the cycle steal mode)

But, as shown in Fig. 19, only the channel under executing DMA transfer is prohibited to accept TxRQ during DMA transfer operation, in order that one more byte transfer may not be

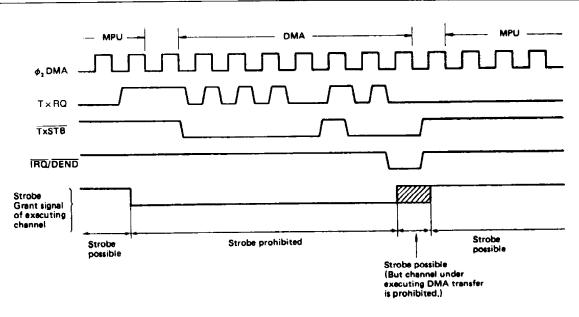

performed when the reset timing of TxRQ is delayed. Strobe timing in the burst mode is shown in Fig. 20.

Figure 20 Strobe Timing of Executing-Channel-Number-Latch-Circuit (the burst mode)

#### **Rotate Mode**

There are two operation modes in priority-order-determining circuit. These are Normal Mode and Rotate Mode. In the normal mode, the order of priority is fixed at numerical order. (Channel 0 is given a first priority and then is followed by Channel  $1 \rightarrow 2 \rightarrow 3$ .) In the rotate mode, the channel next to the channel with

which DMA was executed in the last sequence, is given a first priority and the channel in the last sequence is given a last priority. But immediately after it gets into the reset state, the order of priority is the following: Channel  $0 \rightarrow 1 \rightarrow 2 \rightarrow 3$ .

An example of the rotate mode is shown in Fig. 21.

Figure 21 Example of Operation in the Rotate Mode

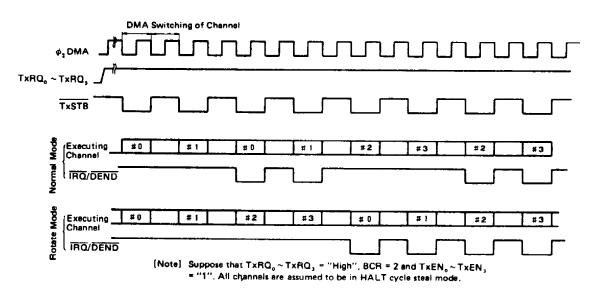

Next, Fig. 22 shows an example of the difference between the operation in the rotate mode and that in the normal mode. In this example, TxRQ of all channels is always at "High" level. Moreover, BCR=2 and TxEN=1 are assumed. As a transfer mode, HALT cycle steal mode is used.

5

Figure 22 Difference between the operation in the rotate mode and that in the normal mode

The reason why the order of priority is not  $\#0 \to \#0 \to \#1$ → #1 → --- in the normal mode is that during DMA transfer operation, TxRQ of an executing channel is prohibited from being accepted.

### **DMA Operation Timing with priority control**

When more than 2 channels perform DMA transfer in parallel, the abovementioned priority-order-determining-circuit is used to determine the priority. The channel with lower priority waits until the channel with higher priority completes the transfer. Then it gets into DMA transfer operation. In this case, The following combinations of transfer modes are conceivable.

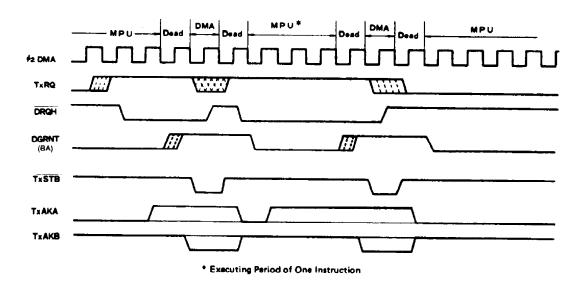

- (1) From HALT mode to HALT mode (Fig. 23)

- (2) From TSC mode to TSC mode (Fig. 24)

- (3) From HALT mode to TSC mode

(4) From TSC mode to HALT mode

In changing from HALT mode to HALT mode, only one dead cycle is intervened. That is, even in the cycle steal mode, DMA transfer of the next channel is performed without returning the bus control to the MPU (DRQH remains "Low").

In changing from TSC mode to TSC mode, DMA transfer

of the next channel is performed, after returning the bus control to MPU for one cycle.

In the case of HALT - HALT, it doesn't return the bus control to MPU in order not to increase the response time of DMA transfer and dead cycles of the system.

On the other hand, in the case of TSC - TSC mode, same mean cannot be applicable because MPU clock cannot remain stopped for a long time as in the case of HALT mode.

Both in the case of HALT - TSC mode and in the case of TSC → HALT mode, DMA operation timing is based on the same idea as the above two kinds of mode change. (In detail, see Fig. 25).

The timing in the case where the next byte is transfered without changing the channel is shown in Fig. 26. This is the case of HALT → HALT mode. In this case, the bus control returns to MPU, before the next byte is transfered. In the case of TSC → TSC mode, its timing is almost the same as than in Fig. 24, that is, after 1-byte transfer has completed, MPU executes the Instruction Cycle for one clock and then DMAC executes 1-byte transfer again.

Figure 23 Channel Change (HALT Mode → HALT Mode)

Figure 24 Channel Change (TSC Mode → TSC Mode)

Figure 25 Channel Change (HALT Mode → TSC Mode → HALT Mode)

Figure 26 Successive 2-byte Transfer of One Channel (HALT Cycle Steal Mode)

HALT → HALT (by one channel)

#### Status Flag

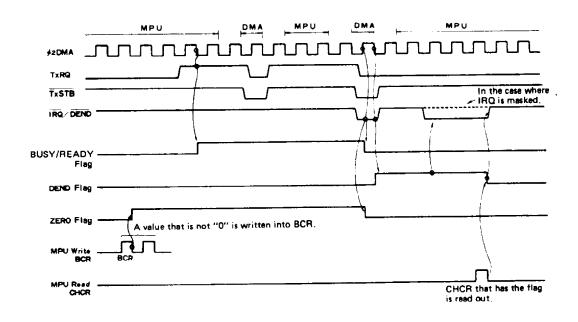

DMAC has BUSY Flag, DEND Flag and ZERO Flag on each channel. The former two of these flags can be read out by MPU, but ZERO Flag cannot be read out. Set and reset timing of each flag are shown in Fig. 27.

#### BUSY/READY Flag

This flag is set to "1" when it accepts the first-byte TxRQ of its corresponding channel. After 1-block transfer has completed and BCR becomes "0", it is reset to "0". Therefore, while this flag is "1", that is, its corresponding channel is being used, the next block transfer cannot be performed.

Also this flag is cleared when corresponding TxRQ Enable Bit is, the PCR becomes "0".

### **DEND Flag**

This is the interrupt flag to indicate the end of DMA transfer of its corresponding channel. After 1-block transfer has completed and BCR becomes "0", this flag is set to "1". This flag is reset to "0" immediately after the Channel Control Register having this flag is read out.

### **ZERO Flag**

This is the internal flag to indicate whether the data stored in the BCR is "0" or not (It cannot be read out).

Figure 27 Timing of Status Flag (Suppose that BCR is 2 in the initial state)

When BCR is "0", ZERO Flag is "0". When BCR is not "0", it is "1".

In the reset state, this flag is "0". If data that is not "0" is written into BCR, this flag is set to "1". When BCR becomes "0" after 1-block data transfer has completed, or MPU writes "0" into BCR, this flag is reset to "0".

The function of ZERO Flag is to prohibit accepting TxRQ of its corresponding channel while this flag is "0" (that is, BCR is "0") (See Fig. 18). While ZERO Flag is "0", TxRQ is not accepted even if TxEN is "1". This function avoids an false operation even if "High" input is provided to TxRQ before the initialization of the register.

When RES pin goes to "Low", this flag becomes "0", but the number in BCR is not reset to "0". Therefore, the state of this flag and BCR are not the same. In this case new data should be written into BCR (Then ZERO Flag becomes "1").

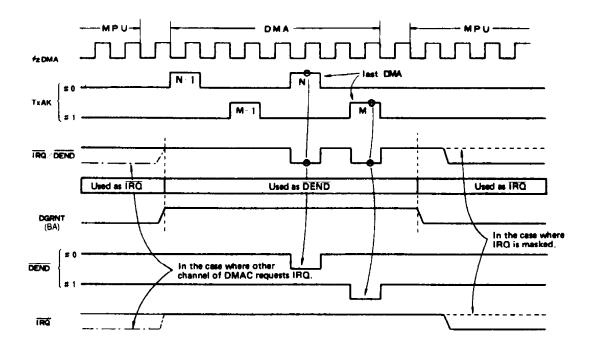

### DMA End Control

### Function of IRQ/DEND Pin

DMAC has  $\overline{IRQ}$  output and  $\overline{DEND}$  output to perform DMA End Control. These are multiplexed outputs to  $\overline{IRQ}/$

DEND pin.

The function of DEND output is to inform I/O controller of the end of 1-block transfer. After 1-block transfer has been completed and BCR becomes "O", DEND output provides "Low" pulse whose cycle is one clock, being synchronous with the final 1-byte data transfer. 4 channels have only one DEND output in common, so each channel determines whether DEND output is its own output or not, combining with TxAK signal. When TxAK of the channel is "High" and DEND is "Low", it shows that the cycle is the last one of DMA (See Fig. 29 and 30).

The function of IRQ output is to inform MPU of the end of 1-block transfer by interrupting it. As shown in Fig. 28, IRQ output is logical AND-OR of the interrupt flag (DEND Flag) and IRQ Enable bit of each channel.

IRQ and DEND outputs are multiplexed. IRQ/DEND pin is used as DEND output during DMAC cycle and IRQ output during MPU cycle. Moreover, DGRNT signal separates DEND and IRQ by its "High" or "Low". In detail, see Fig. 29 and Fig. 30.

## 5

Figure 28 Logic of IRQ Output

Figure 29 Timing of IRQ/DEND Output

Figure 30 How to Use IRQ/DEND Output Signal

#### Unusual DMA End

Following section describes how to terminate or change normal sequence of DMA transfer.

- (1) When "0" is written into BCR

- When "0" is written into BCR before it becomes "0", subsequent TxRQ are not accepted and this causes the termination of the DMA transfer since the internal ZERO Flag is reset to "0". In this case, note that DEND pulse is not provided.

- (2) When "1" is written into BCR

- When "1", instead of "0", is written into BCR, only the next TxRQ is accepted and 1-byte DMA transfer is performed. In this case, DEND pulse is provided, being synchronous with the last transfer.

- (3) When another value is written into ADR & BCR during the transfer

- When the data in ADR & BCR are changed during the transfer, the following transfer is performed according to the change of the data.

- (4) When "0" is written into TxRQ Enable bit

- When TxEN is reset to "0" during the transfer, this causes TxRQ comes not to be accepted and the transfer halts. But the state is different from that in the case (1), the number in BCR remains unchanged. Therefore, when TxEN is set to "1" again, the transfer is performed again.

- (5) When RES pin is set to "Low"

- When RES is provided during the transfer, the transfer stops.

- Then all of the control registers and their internal flags are reset to "0". But the data in ADR & BCR are not reset.

### (Supplement)

It is only in the cycle steal mode that DMAC registers such as BCR and ADR can be read or written during the transfer. In the burst mode, it is usually impossible (But special external circuits enable it).

### Data Chain Function

The data chain function of DMAC is to transfer the contents of ADR & BCR of Channel #3 to ADR & BCR of a specified channel automatically and renew the data of them after the channel has completed 1-block transfer.

Figure 31 Data Chain Operation

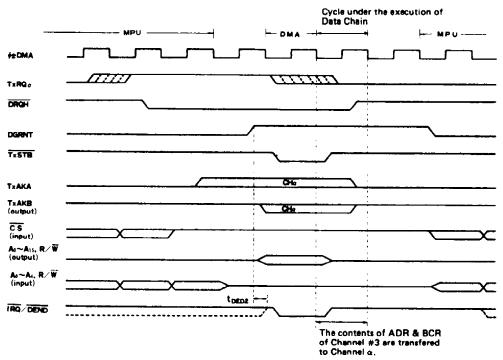

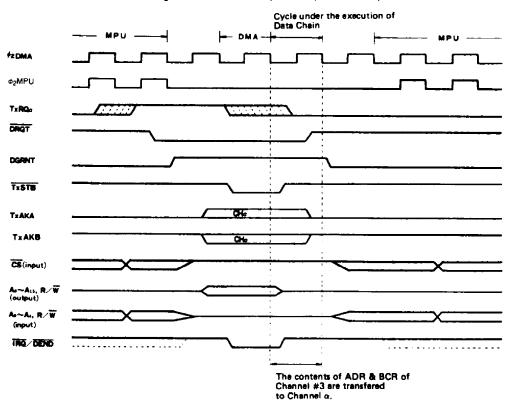

Its detailed timing is shown in Fig. 32 and Fig. 33. As shown in these figures the contents of ADR & BCR of Channel #3 are transfered to the channel during the clock cycle next to the last one of 1-block transfer (which provides DEND pulse). Then DROH or DROT provides "Low" output for one more clock cycle than in the normal case. Therefore, MPU takes back the bus control again 1-clock later than in the normal case, that is, after the data renewal of the specified channel by the data chain from Channel #3.

In the TSC mode, the stretching period of  $\operatorname{clock}\phi_1$  is longer than in the normal case.

The contents of ADR & BCR of Channel #3 remain unchanged as long as new data are not written by MPU, even if the data chain is executed.

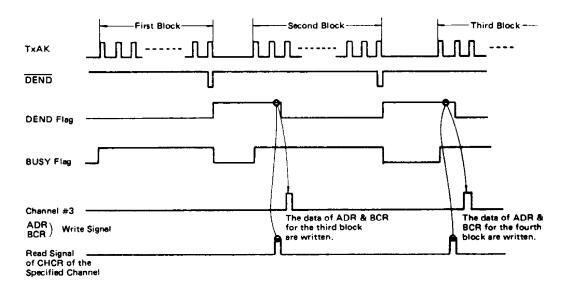

As for DEND output, DEND Flag and BUSY Flag in the case of data chain execution, they function in the same way as in the normal case. They provide DEND pulse everytime 1-block transfer has completed, and then DEND Flag is set to "1". Therefore, in the case where more than 3-block data chain is needed, DEND Flag is used for the execution. Its sequence is shown in Fig. 34. First, DEND Flag="1" that shows the end of the first-block data chain is read out. Next, the data of ADR & BCR for the third-block data chain need to be written into Channel #3, in parallel with the execution of the second-block data chain. (This data chain is feasible only in the cycle steal mode.)

Figure 32 Data Chain Operation (HALT Mode)

Figure 33 Data Chain Operation (TSC Mode)

Figure 34 Sequence of More than 3-block Data Chain

#### DMAC PROGRAMMING

Preparation of a channel for a DMA transfer requires:

- 1) Load the starting address into the Address Register.

- 2) Load the number of bytes into the Byte Count Register.

- 3) Program the Channel Control Register for the transfer characteristics: direction (bit 0), mode (bits 1 and 2), and the address update (bit 3).

The channel is now configured. To enable the transfer

request, set the appropriate enable bit (bits 0~3) of the Priority Control Register, as well as the Rotate Control bit.

If an interrupt on DMA End is desired, the enable bit (bits 0~3) of the Interrupt Control Register must be set.

If data chaining for the channel is necessary, it is programmed into the Data Chain Register and the appropriate data must be written into the Address and Byte Count Registers for channel #3.

|                      | Address |                           |                    |          | Register | r Content                    |                              |                              |                              |

|----------------------|---------|---------------------------|--------------------|----------|----------|------------------------------|------------------------------|------------------------------|------------------------------|

| Register             | (Hex)   | Bit 7                     | Bit 6              | Bit 5    | Bit 4    | Bit 3                        | Bit 2                        | Bit 1                        | Bit O                        |

| Channel<br>Control   | 1x*     | DMA End<br>Flag<br>(DEND) | Busy/Ready<br>Flag | Not Used | Not Used | Address<br>Up/Down           | TSC/<br>Halt                 | Burst/<br>Steel              | Reed/Write<br>(R/W)          |

| Priority<br>Control  | 14      | Rotate<br>Control         | Not Used           | Not Used | Not Used | TxRQ<br>Enable #3<br>(TxEN3) | TxRQ<br>Enable #2<br>(TxEN2) | TxRQ<br>Enable #1<br>(TxEN1) | TxRQ<br>Enable #0<br>(TxEN0) |

| Interrupt<br>Control | 15      | IRQ<br>Flag               | Not Used           | Not Used | Not Used | IRQ<br>Enable #3<br>(IE3)    | IRQ<br>Enable #2<br>(IE2)    | IRQ<br>Enable #1<br>(IE1)    | IRQ<br>Enable #0<br>(IEO)    |

| Data Chain           | 16      | Not Used                  | Not Used           | Not Used | Not Used | Two/Four<br>Channel          | Data Chain<br>Channel        | Deta Chain<br>Channel        | Data Chain<br>Enable         |

Table 8 DMAC Programming Model

A comparison of the response times and maximum transfer rates is shown in Table 9. The data are shown for a system clock rate of 1 MHz.

The two 8-bit bytes that form the registers in Table 10 are placed in consecutive memory locations, making it very easy to use the MPU index register in programming them.

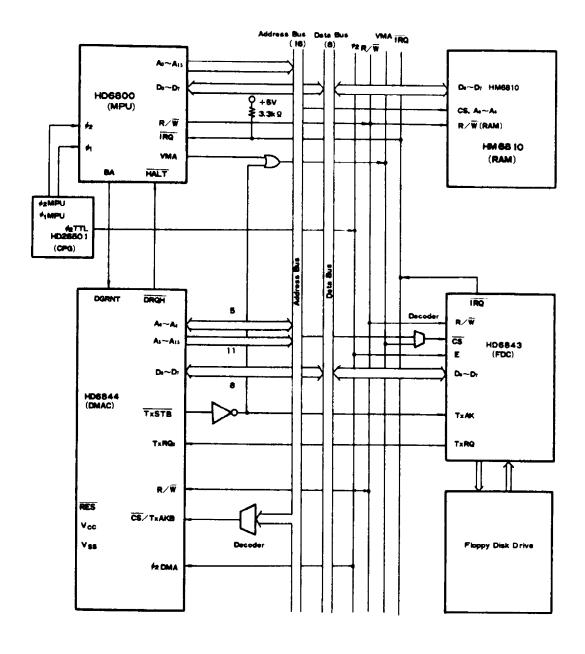

Fig. 38 shows an example of its minimum structure (1 channel, HALT mode, combination with FDC). Fig. 39 shows an example of its maximum structure. (but only one DMAC is used.)

Select A

Select B

Select (2/4)

<sup>\*</sup> The x represents the binary equivalent of the channel desired.

Table 9 Maximum Transfer Speed & Response Time of the DMAC when toyog equals 1 µsec.

| Mode  HALT Cycle Steal                  |          | Maximum Transfer                        | Response Time (μsec)                   |                         |  |

|-----------------------------------------|----------|-----------------------------------------|----------------------------------------|-------------------------|--|

|                                         |          | Speed (µsec/byte)                       | maximum                                | minimum                 |  |

|                                         |          | (executing time of one instruction) + 3 | (executing time<br>of one instruction) | 3.5 + t <sub>TQS1</sub> |  |

| HALT Burst first byte since second byte | _        | +3.5 - t <sub>TQH1</sub>                | 1031                                   |                         |  |

|                                         |          | ľ                                       | 2 - t <sub>TQH2</sub>                  | 1 + t <sub>TQS2</sub>   |  |

| TSC Cyc                                 | le Steal | 4                                       | 3.5 - t <sub>TQH1</sub>                | 2.5 + t <sub>TQH1</sub> |  |

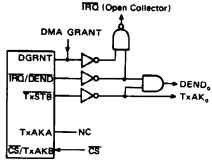

Figure 35 One Channel

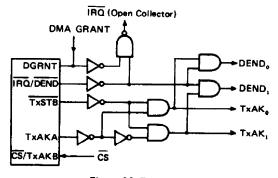

Figure 36 Two Channel

Table 10 Address and Byte Count Registers

| Register        | Channel | Address<br>(Hex) |  |

|-----------------|---------|------------------|--|

| Address High    | 0       | 0                |  |

| Address Low     | 0       | 1                |  |

| Byte Count High | 0       | 2                |  |

| Byte Count Low  | 0       | 3                |  |

| Address High    | 1       | 4                |  |

| Address Low     | 1       | 5                |  |

| Byte Count High | 1       | 6                |  |

| Byte Count Low  | 1       | 7                |  |

| Address High    | 2       | 8                |  |

| Address Low     | 2       | 9                |  |

| Byte Count High | 2       | A                |  |

| Byte Count Low  | 2       | В                |  |

| Address High    | 3       | С                |  |

| Address Low     | 3       | D                |  |

| Byte Count High | 3       | E                |  |

| Byte Count Low  | 3       | F                |  |

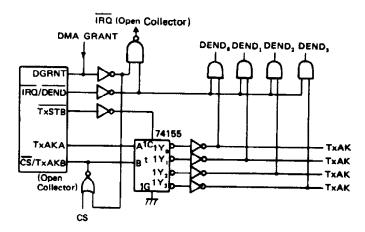

Figure 37 Four-Channel

Figure 38 Example of DMA System Structure (1) (minimum)

Figure 39 Example of DMA System Structure (2) (maximum)

### APPENDIX

### Contents of the DMAC Registers