## LM4962 Boomer® Audio Power Amplifier Series

# **Ceramic Speaker Driver**

### **General Description**

The LM4962 is an audio power amplifier primarily designed for driving Ceramic Speaker for applications in Cell Phones, Smart Phones, PDA's and other portable applications. It is capable of driving 15Vpp (typ) BTL with less than 1% THD+N from a  $3.2\mathrm{V}_{\mathrm{DC}}$  power supply. The LM4962 features and low power consumption shutdown mode, an internal thermal shutdown protection mechanism, along with over current protection (OCP) and over voltage protection (OVP).

Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal number of external components. The LM4962 does not require bootstrap capacitors, or snubber circuits.

The LM4962 also features a Band-Switch function which allows the user to use one amplifier device for both receiver (earpiece) mode and ringer/loudspeaker mode.

The LM4962 contains advanced pop & click circuitry that eliminates noises which would otherwise occur during turn-on and turn-off transitions. Additionally, the internal boost converter features a soft-start function.

The LM4962 is unity-gain stable and can be configured by external gain-setting resistors.

### **Key Specifications**

- Quiescent Power Supply Current (Boost Converter + Amplifier)

9mA (typ)

- Voltage Swing in BTL at 1% THD, f=1KHz 15Vp-p (typ)

- Shutdown current 0.1µA (typ)

- OVP 8.5V < V<sub>AMP</sub> < 9.5V

### **Features**

- Pop & click circuitry eliminates noise during turn-on and turn-off transitions

- Low current shutdown mode

- Low quiescent current

- Mono 15Vp-p BTL output,  $R_L = 2\mu F + 9.4\Omega$ , f = 1kHz, 1% THD+N

- Over-current protection

- Over-Voltage Protection

- Unity-gain stable

- External gain configuration capability

- Including Band switch function

- Leakage cut switch (SW-LEAK)

- Soft-Start function

- Space-saving micro SMD package (2mm x 2.5mm)

### **Applications**

- Smart phones

- Mobile Phones and Multimedia Terminals

- PDA's, Internet Appliances, and Portable Gaming

- Portable DVD

- Digital still cameras/camcorders

Boomer® is a registered trademark of National Semiconductor Corporation.

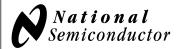

# **Connection Diagrams**

### micro SMD Package

Top View

Order Number LM4962TL

See NS Package Number TLA2011A

micro SMD Top Marking

20142233

Top View

XY = Date Code

TT = Die Run Traceability

G = Boomer Family

F7 = LM4962TL

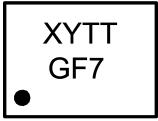

## **Typical Application**

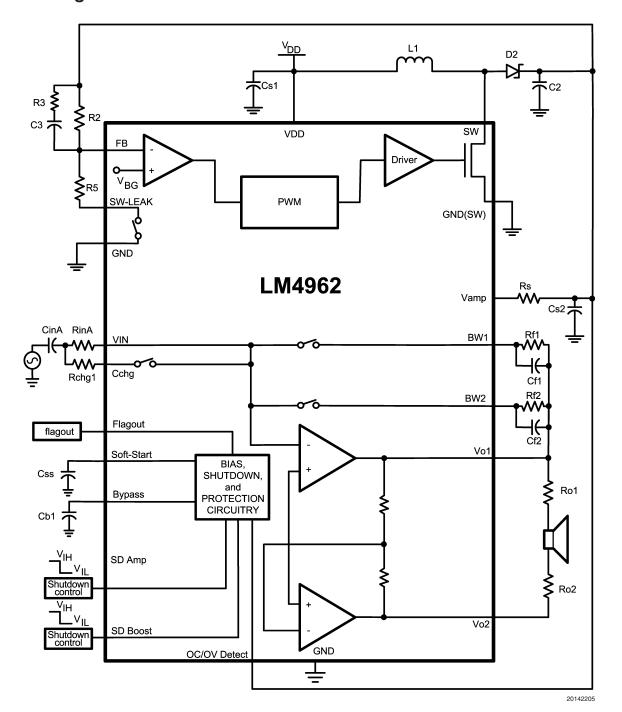

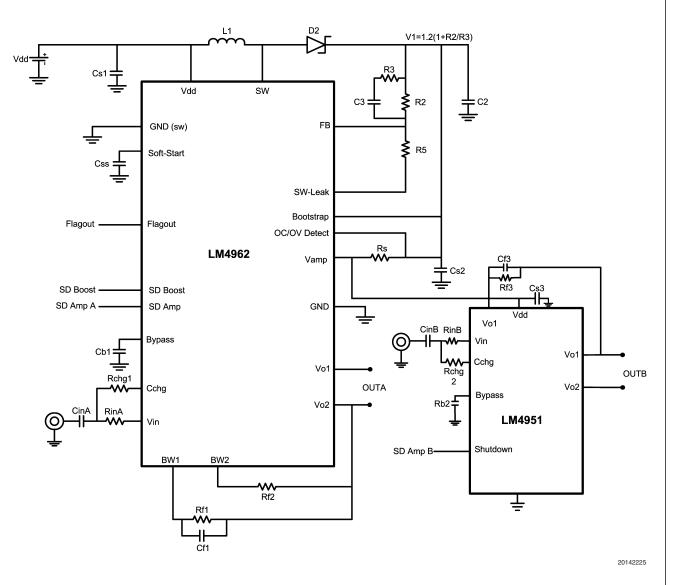

FIGURE 1. Typical Audio Amplifier Application Circuit

## **Block Diagram**

FIGURE 2. LM4962 Block Diagram

### Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (V<sub>DD</sub>) 9.5V Amplifier Supply Voltage (V<sub>AMP</sub>) 9.5V -65°C to +150°C Storage Temperature Input Voltage -0.3V to  $V_{DD} + 0.3V$ Power Dissipation (Note 3) Internally limited ESD Susceptibility (Note 4) 2000V 200V ESD Susceptibility (Note 5) Junction Temperature 150°C Thermal Resistance

$\theta_{JA}$  (µSMD) (Note 12)

73°C/W

See AN-1187 'Leadless Leadframe Packaging (LLP).'

### **Operating Ratings**

Temperature Range

$$\begin{split} T_{MIN} &\leq T_{A} \leq T_{MAX} \text{ (Note 10)} & -40^{\circ}\text{C} \leq T_{A} \leq +85^{\circ}\text{C} \\ \text{Supply Voltage (V}_{DD}) & 3.0\text{V} < \text{V}_{DD} < 5.0\text{V} \end{split}$$

Amplifier Supply Voltage (V<sub>1</sub>)

(Note 11)  $2.7V < V_{AMP} < 9.0V$

### **Electrical Characteristics**

The following specifications apply for  $V_{DD}$  = 3.2V,  $A_{V\text{-BTL}}$  = 26dB,  $Z_L$  =  $2\mu F + 9.4\Omega$ , Cb =  $1.0\mu F$ ,  $R_2$  =25K $\Omega$ ,  $R_5$  =4.9K $\Omega$  unless otherwise specified. Limits apply for  $T_A$  =  $25^{\circ}C$ .

| Symbol                | Parameter                                   | Conditions                                                                | LM4962   |              | Units     |

|-----------------------|---------------------------------------------|---------------------------------------------------------------------------|----------|--------------|-----------|

|                       |                                             |                                                                           | Typical  | Limit        | (Limits)  |

|                       |                                             |                                                                           | (Note 6) | (Notes 7, 8) |           |

| I <sub>DD</sub>       | Quiescent Power Supply Current              | $V_{IN} = 0V$ ,                                                           | 9        | 12           | mA (max)  |

|                       | in Boosted Ringer Mode                      |                                                                           |          |              |           |

| Iddrcv                | Quiescent Power Supply Current              | SD Boost = GND                                                            | 3        | 5            | mA (max)  |

|                       | in Receiver Mode                            | SD Amp = V <sub>DD</sub>                                                  |          |              |           |

| I <sub>SD</sub>       | Shutdown Current (Note 9)                   | SD Boost = SD Amp = GND                                                   | 0.1      | 2.0          | μA (max)  |

| $V_{LH}$              | Logic High Threshold Voltage                | For SD Boost, SD Amp                                                      |          | 1.2          | V (min)   |

| $V_{LL}$              | Logic Low Threshold Voltage                 | For SD Boost, SD Amp                                                      |          | 0.4          | V (max)   |

| R <sub>PULLDOWN</sub> | Pulldown Resistor                           | For SD Amp, SD Boost                                                      | 80       | 60           | kΩ (min)  |

| T <sub>WUBC</sub>     | Boost Converter Wake-up Time                | C <sub>SS</sub> = 10nF                                                    | 2        | 5            | ms (max)  |

| T <sub>WUA</sub>      | Audio Amplifier Wake-up Time                | (For Vdd = 2.7V to 8.5V)                                                  | 20       | 40           | msec      |

| V <sub>OUT</sub>      | Output Voltage Swing                        | THD = 1% (max), f = 1kHz                                                  | 15       | 14           | Vpp (min) |

| THD+N                 | Total Harmonic Distortion + Noise           | Vout = 14Vpp, f = 1kHz                                                    | 0.4      | 1.0          | %         |

| €OS                   | Output Noise                                | A-Weighted Filter, V <sub>IN</sub> = 0V                                   | 125      |              | μV        |

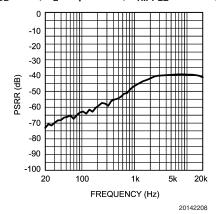

| PSRR                  | Power Supply Rejection Ratio                | V <sub>RIPPLE</sub> = 200mV <sub>p-p</sub> , f = 100Hz,<br>Input Referred | 86       | 71           | dB (min)  |

| Ron-sw-leak           | On Resistance on SW-Leak                    | SD Boost = GND                                                            | 30       | 50           | Ω (max)   |

|                       |                                             | Isink = 100μA                                                             |          |              |           |

| Ron                   | Flagout On resistance                       | Isink = 1mA                                                               | 50       | 100          | Ω (max)   |

| Vovp                  | Sensitivity of Over Voltage                 | Flagout = GND                                                             | 9.0      | 9.5          | V (max)   |

| νονρ                  | Protection on V <sub>AMP</sub>              |                                                                           |          | 8.5          | V (min)   |

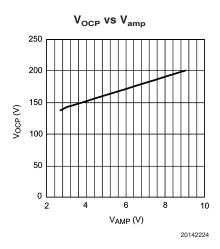

| Vocp                  | Sensitivity of Over Current                 | Flagout = GND                                                             | 185      | 275          | mV (max)  |

| <b>чоср</b>           | Protection (Voltage Across R <sub>S</sub> ) |                                                                           |          | 75           | mV (min)  |

| lleak                 | Leak Current on Flagout pin                 | Vflagout = V <sub>DD</sub>                                                |          | 2            | μA (max)  |

| I <sub>sw</sub>       | SW Current Limit                            |                                                                           | 2        | 2.7          | A (max)   |

|                       |                                             |                                                                           |          | 1.2          | A (min)   |

| TSD                   | Thermal Shutdown Temperature                |                                                                           |          | 150          | °C (min)  |

| Vos                   | Output Offset Voltage                       |                                                                           | 5        | 25           | mV        |

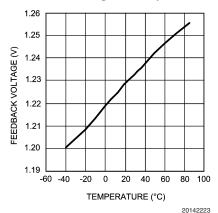

| $V_{FB}$              | Feedback Voltage                            | SD Boost = V <sub>DD</sub>                                                | 1.23     | 1.15         | V (min)   |

|                       |                                             | SD Amp = V <sub>DD</sub>                                                  |          | 1.31         | V (max)   |

### **Electrical Characteristics** (Continued)

- Note 1: All voltages are measured with respect to the GND pin, unless otherwise specified.

- **Note 2:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

- Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} T_A) / \theta_{JA}$  or the given in Absolute Maximum Ratings, whichever is lower.

- Note 4: Human body model, 100pF discharged through a 1.5k $\Omega$  resistor.

- Note 5: Machine Model, 220pF-240pF discharged through all pins.

- Note 6: Typicals are measured at 25°C and represent the parametric norm.

- Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

- Note 8: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

- Note 9: Shutdown current is measured in a normal room environment. The Shutdown pin should be driven as close as possible to Vin for minimum shutdown current.

- Note 10: Temperature range is tentative, pending characterization.

- Note 11: An amplifier supply voltage of 9.0V can only be obtained when the over current and over voltage protection circuitry is disabled (OV/OC Detect pin is disabled).

- Note 12: The value for a  $\theta_{JA}$  is measured with the LM4962 mounted on a 3" x 1.5" 4 layer board. The copper thickness for all 4 layers is 0.5oz (roughly 0.18mm).

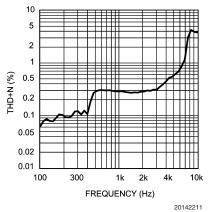

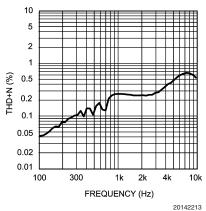

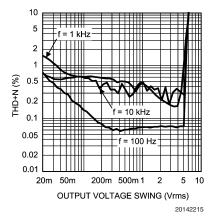

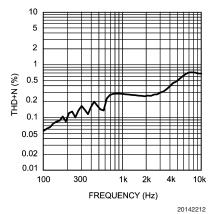

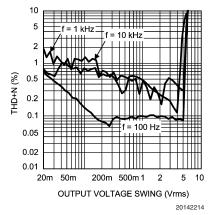

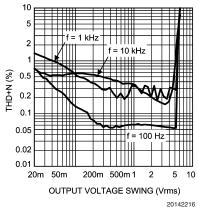

### **Typical Performance Characteristics**

THD+N vs Frequency  $\label{eq:VDD} {\rm V_{DD}=3.2V,\ V_O=4.95V_{RMS},\ Z_L=2\mu F+9.4\Omega}$

THD+N vs Frequency  $\label{eq:VDD} {\rm V_{DD}} = 5{\rm V,~V_O} = 4.95{\rm V_{RMS},~Z_L} = 2\mu{\rm F}{+}9.4\Omega$

THD+N vs Output Voltage Swing  $V_{DD}$  = 4.2V,  $Z_L$  =  $2\mu F$ +9.4 $\Omega$ , f = 1kHz

THD+N vs Frequency  $\label{eq:VDD} \text{V}_{\text{DD}} = \text{4.2V}, \, \text{V}_{\text{O}} = \text{4.95V}_{\text{RMS}}, \, \text{Z}_{\text{L}} = \text{2} \mu \text{F} + \text{9.4} \Omega$

THD+N vs Output Voltage Swing  $V_{DD}$  = 3.2V,  $Z_L$  =  $2\mu F$ +9.4 $\Omega$ , f = 1kHz

THD+N vs Output Voltage Swing  $V_{DD} = 5V$ ,  $Z_L = 2\mu F + 9.4\Omega$ , f = 1kHz

20142216

### Typical Performance Characteristics (Continued)

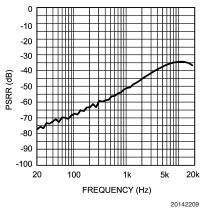

$\begin{aligned} & \text{PSRR vs Frequency} \\ \text{V}_{\text{DD}} = 3.2, \ \text{Z}_{\text{L}} = 2 \mu \text{F} + 9.4 \Omega, \ \text{V}_{\text{RIPPLE}} = 200 \text{mV}_{\text{P-P}} \end{aligned}$

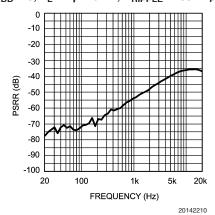

PSRR vs Frequency  $\label{eq:VDD} \textbf{V}_{\text{DD}} = 4.2, \, \textbf{Z}_{\text{L}} = 2 \mu \textbf{F} + 9.4 \Omega, \, \textbf{V}_{\text{RIPPLE}} = 200 \text{mV}_{\text{P-P}}$

PSRR vs Frequency

$V_{DD}$  = 5,  $Z_L$  = 2 $\mu$ F+9.4 $\Omega$ ,  $V_{RIPPLE}$ = 200m $V_{P-P}$

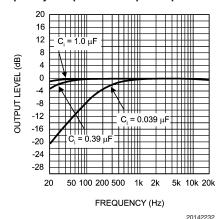

Frequency Response vs Input Capacitor Size

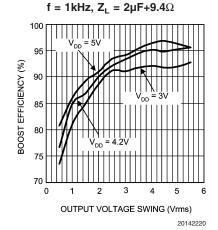

Boost Efficiency vs Output Voltage Swing

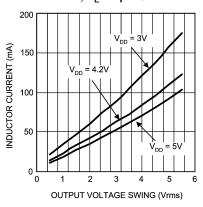

$\label{eq:current} \mbox{Inductor Current vs Output Voltage Swing} \\ \mbox{f = 1kHz, } \mbox{Z}_{\mbox{L}} = \mbox{2}\mu\mbox{F+9.4}\Omega \\$

20142221

## **Typical Performance Characteristics** (Continued)

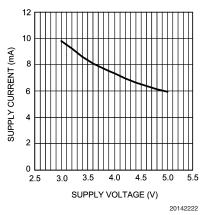

### Supply Current vs Supply Voltage

### Feedback Voltage vs Temperature

### **Application Information**

#### **BRIDGE CONFIGURATION EXPLANATION**

The Audio Amplifier portion of the LM4962 has two internal amplifiers allowing different amplifier configurations. The first amplifier's gain is externally configurable, whereas the second amplifier is internally fixed in a unity-gain, inverting configuration. The closed-loop gain of the first amplifier is set by selecting the ratio of Rf to Ri while the second amplifier's gain is fixed by the two internal  $20k\Omega$  resistors. Figure 1 shows that the output of amplifier one serves as the input to amplifier two. This results in both amplifiers producing signals identical in magnitude, but out of phase by  $180^\circ$ . Consequently, the differential gain for the Audio Amplifier is

$$A_{VD} = 2 * (Rf/Ri)$$

By driving the load differentially through outputs Vo1 and Vo2, an amplifier configuration commonly referred to as "bridged mode" is established. Bridged mode operation is different from the classic single-ended amplifier configuration where one side of the load is connected to ground.

A bridge amplifier design has a few distinct advantages over the single-ended configuration. It provides differential drive to the load, thus doubling the output swing for a specified supply voltage.

#### **AMPLIFIER POWER DISSIPATION**

Power dissipation is a major concern when designing a successful amplifier, whether the amplifier is bridged or single-ended. A direct consequence of the increased power delivered to the load by a bridge amplifier is an increase in internal power dissipation. Since the amplifier portion of the LM4962 has two operational amplifiers, the maximum internal power dissipation is 4 times that of a single-ended amplifier. The maximum power dissipation for a given BTL application can be derived from Equation 1.

$$P_{DMAX(AMP)} = 4(V_{DD})^2 / (2\pi^2 Z_L)$$

(1)

where

$$Z_L = R_o 1 + R_o 2 + 1/2\pi fc$$

#### **BOOST CONVERTER POWER DISSIPATION**

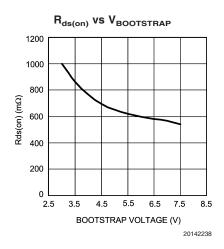

At higher duty cycles, the increased ON-time of the switch FET means the maximum output current will be determined by power dissipation within the LM4962 FET switch. The switch power dissipation from ON-time conduction is calculated by Equation 2.

$$P_{DMAX(SWITCH)} = DC \times I_{IND}(AVE)^2 \times R_{DS}(ON)$$

(2)

where DC is the duty cycle.

There will be some switching losses as well, so some derating needs to be applied when calculating IC power dissipation.

### TOTAL POWER DISSIPATION

The total power dissipation for the LM4962 can be calculated by adding Equation 1 and Equation 2 together to establish Equation 3:

$$\begin{split} P_{DMAX(TOTAL)} &= [4^{\star}(V_{DD})^2 / \\ 2\pi^2 Z_L] + [DCxI_{IND}(AVE)^2 x R_{DS}(ON)] \end{split} \tag{3}$$

The result from Equation 3 must not be greater than the power dissipation that results from Equation 4:

$$P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$$

(4)

For the LQA28A,  $\theta_{JA}=73^{\circ}\text{C/W}$ .  $T_{JMAX}=125^{\circ}\text{C}$  for the LM4962. Depending on the ambient temperature,  $T_{A}$ , of the system surroundings, Equation 4 can be used to find the maximum internal power dissipation supported by the IC packaging. If the result of Equation 3 is greater than that of Equation 4, then either the supply voltage must be increased, the load impedance increased or  $T_{A}$  reduced. For typical applications, power dissipation is not an issue. Power dissipation is a function of output power and thus, if typical operation is not around the maximum power dissipation point, the ambient temperature may be increased accordingly.

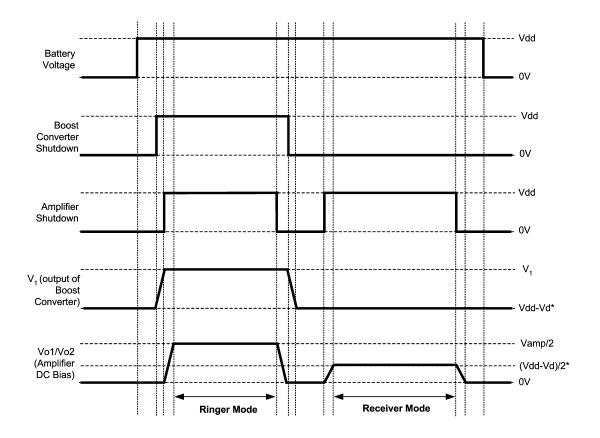

#### START-UP SEQUENCE

For the LM4962 correct start-up sequencing is important for optimal device performance. Using the correct start up sequence will improve click/pop performance as well as avoid transients that could reduce battery life. For ringer/loudspeaker mode, the supply voltage should be applied first and both the boost converter and the amplifier should be in shutdown. The boost converter can then be activated followed by the amplifier (see timing diagram Figure 3). If the boost converter shutdown is toggled while the amplifier is active a very audible pop will be heard.

#### SHUTDOWN FUNCTION

In many applications, a microcontroller or microprocessor output is used to control the shutdown circuitry to provide a quick, smooth transition into shutdown. Another solution is to use a single-pole, single-throw switch connected between  $V_{\rm DD}$  and Shutdown pins.

### **BAND SWITCH FUNCTION**

The LM4962 features a Band Switch function which allows the user to use one amplifier for both receiver (earpiece) mode and ringer/loudspeaker mode. When the boost converter and the amplifier are both active the device is is in ringer mode. This enables the boost converter and sets the externally configurable closed loop gain selection to BW1. If the boost converter is in the shutdown and the amplifier is active the device is in receiver mode. In this mode the gain selection is switched to BW2. This allows the amplifier to be powered directly from the battery minus the voltage drop across the Schottky diode.

|                     | SD Boost | SD Amp |

|---------------------|----------|--------|

| Receiver Mode (BW2) | Low      | High   |

| Boosted Ringer Mode | High     | High   |

| (BW1)               |          |        |

| Shutdown            | Low      | Low    |

#### **BOOTSTRAP PIN**

The bootstrap pin, featured in the LM4962, provides a voltage supply for the internal switch driver. Connecting the bootstrap pin to V1 (See Figure 1) allows for a higher voltage to drive the gate of the switch thereby reducing the Ron. This configuration is necessary in applications with heavier loads. The bootstrap pin can be connected to VDD when driving lighter loads to improve device performance (Iddq, THD+N, Noise, etc.).

\*Vd = Voltage drop across diode D2

20142219

FIGURE 3. Power on Sequence Timing Diagram

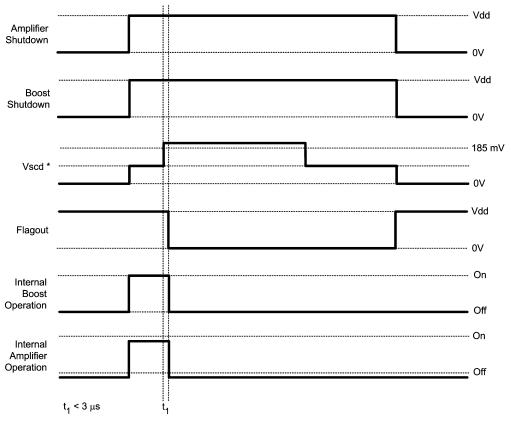

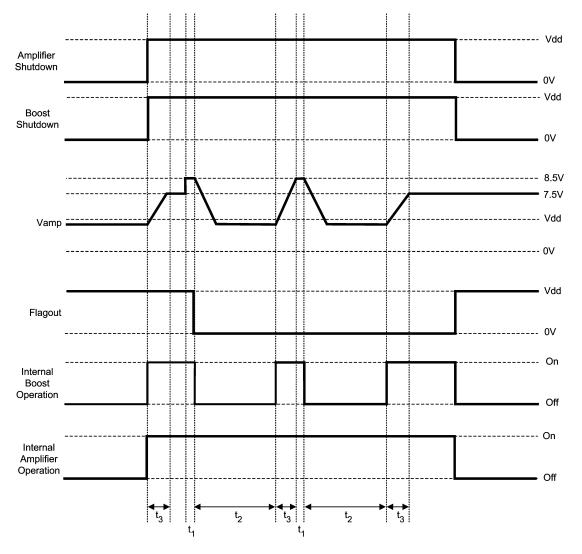

## OVER-CURRENT AND OVER-VOLTAGE PROTECTION FUNCTION

**Flagout Pin:** The Flagout pin indicates a fault when an over current or over voltage condition has been detected. The Flagout pin is high impedance when inactive. When active, the Flagout pin is pulled down to a  $50\Omega$  short to GND.

Over-Voltage Protection (OVP) Operation: When a voltage (Vamp) greater than 8.5V (min) is detected at the OC/OV Detect pin, the LM4962 indicates a fault by activating the Flagout pin. The boost converter momentarily shutdown and reinitialize the soft-start sequence. The Flagout pin will remain active until both shutdowns pins are pulled low.

Over-Current Protection (OCP) Operation: The OCP circuitry monitors the voltage across Rocd to detect the output current of the boost converter. If a voltage greater than 185mV (typ) is detected the device will shutdown and the Flagout pin will be activated. For the device to return to normal operation both shutdown pins need to be pulled low to reset the Flagout pin.

**Disable OCP:** The Over-Current Protection Circuitry can be disabled by shorting out  $R_{\rm S}$ . In this configuration the OVP circuitry is still active.

**Disable both OVP and OCP:** Both features can be disabled by grounding the OC/OV Detect pin. In this configuration the Flagout pin will be inactive.

### **Timing Diagrams**

<sup>\*</sup> Vscd refers to the voltage differential across Rscd

20142203

FIGURE 4. OCP Timing Diagram

t<sub>1</sub> <3 μs

t<sub>2</sub> = 16 ms

$t_3 = 3 \text{ ms}$

20142218

FIGURE 5. OVP Timing Diagram

#### PROPER SELECTION OF EXTERNAL COMPONENTS

Proper selection of external components in applications using integrated power amplifiers, and switching DC-DC converters, is critical for optimizing device and system performance. Consideration to component values must be used to maximize overall system quality.

The best capacitors for use with the switching converter portion of the LM4962 are multi-layer ceramic capacitors. They have the lowest ESR (equivalent series resistance) and highest resonance frequency, which makes them optimum for high frequency switching converters.

When selecting a ceramic capacitor, only X5R and X7R dielectric types should be used. Other types such as Z5U and Y5F have such severe loss of capacitance due to effects of temperature variation and applied voltage, they may provide as little as 20% of rated capacitance in many typical applications. Always consult capacitor manufacturer's data curves before selecting a capacitor. High-quality ceramic capacitors can be obtained from Taiyo-Yuden.

#### **POWER SUPPLY BYPASSING**

As with any amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. The capacitor location on both V1 and  $V_{\rm DD}$  pins should be as close to the device as possible.

## SELECTING INPUT CAPACITOR FOR AUDIO AMPLIFIER

One of the major considerations is the closedloop bandwidth of the amplifier. To a large extent, the bandwidth is dictated by the choice of external components shown in Figure 1. The input coupling capacitor,  $C_{\rm i}$ , forms a first order high pass filter which limits low frequency response. This value should be chosen based on needed frequency response for a few distinct reasons.

High value input capacitors are both expensive and space hungry in portable designs. Clearly, a certain value capacitor is needed to couple in low frequencies without severe attenuation. But ceramic speakers used in portable systems, whether internal or external, have little ability to reproduce signals below 100Hz to 150Hz. Thus, using a high value input capacitor may not increase actual system performance.

In addition to system cost and size, click and pop performance is affected by the value of the input coupling capacitor,  $C_i$ . A high value input coupling capacitor requires more charge to reach its quiescent DC voltage (nominally 1/2  $V_{\rm DD}$ ). This charge comes from the output via the feedback and is apt to create pops upon device enable. Thus, by minimizing the capacitor value based on desired low frequency response, turn-on pops can be minimized.

# SELECTING FEEDBACK CAPACITOR FOR AUDIO AMPLIFIER

The LM4962 is unity-gain stable which gives the designer maximum system flexability. However, to drive ceramic speakers, a typical application requires a closed-loop differential gain of 10. In this case a feedback capacitor (C<sub>1</sub>2) will be needed as shown in Figure 1 to bandwidth limit the amplifier.

This feedback capacitor creates a low pass filter that eliminates possible high frequency noise. Care should be taken

when calculating the -3dB frequency because an incorrect combination of  $R_{\rm f}$  and  $C_{\rm f}2$  will cause rolloff before the desired frequency

# SELECTING OUTPUT CAPACITOR ( $C_{o}$ ) FOR BOOST CONVERTER

A single 4.7µF to 10µF ceramic capacitor will provide sufficient output capacitance for most applications. If larger amounts of capacitance are desired for improved line support and transient response, tantalum capacitors can be used. Aluminum electrolytics with ultra low ESR such as Sanyo Oscon can be used, but are usually prohibitively expensive. Typical Al electrolytic capacitors are not suitable for switching frequencies above 500 kHz because of significant ringing and temperature rise due to self-heating from ripple current. An output capacitor with excessive ESR can also reduce phase margin and cause instability.

In general, if electrolytics are used, we recommended that they be paralleled with ceramic capacitors to reduce ringing, switching losses, and output voltage ripple.

## SELECTING INPUT CAPACITOR (Cs1) FOR BOOST CONVERTER

An input capacitor is required to serve as an energy reservoir for the current which must flow into the coil each time the switch turns ON. This capacitor must have extremely low ESR, so ceramic is the best choice. We recommend a nominal value of  $4.7\mu\text{F}$ , but larger values can be used. Since this capacitor reduces the amount of voltage ripple seen at the input pin, it also reduces the amount of EMI passed back along that line to other circuitry.

# SETTING THE OUTPUT VOLTAGE ( $V_1$ ) OF BOOST CONVERTER

The output voltage is set using the external resistors  $R_2$  and  $R_5$  (see Figure 1). A value of approximately  $25 \mathrm{k}\Omega$  is recommended for R2 to establish the open loop gain of the boost converter.

$$V_1 = V_{FB} [1 + (R_2 / R_5)]$$

(5)

## FEED-FORWARD COMPENSATION FOR BOOST CONVERTER

Although the LM4962's internal Boost converter is internally compensated, the external feed-forward capacitor  $C_f$  is required for stability (see Figure 1). Adding this capacitor puts a zero in the loop response of the converter. The recommended frequency for the zero fz should be approximately 60kHz. C3 can be calculated using the formula:

$$C_3 = 1 / (2\pi \times R_2 \times fz)$$

(6)

### **SELECTING A SOFT-START CAPACITOR (Css)**

The soft-start function charges the boost converter reference voltage slowly, which allows the output of the boost converter to ramp up slowly thus limiting the transient current at startup.

Selecting a soft-start capacitor (Css) value presents a trade off between the wake-up time of the boost converter ( $T_{WUBC}$ ) and the startup transient current. Using a larger capacitor value will increase wake-up time and decrease startup transient current; on the flip side, using a smaller capacitor value

will decrease wake-up time and increase the transient current seen at startup. A standard rule of thumb is to use a capacitor 1000 times smaller than the output capacitance of the boost converter (C2+Cs2). A 10nF soft-start capacitor is recommended for a typical application.

#### **SELECTING A VALUE FOR Rchg**

The audio power amplifier integrated in the LM4962 is designed for very fast turn on time. The Cchg pin allows the input capacitor (Ci) to charge quickly to improve click/pop performance. Resistor, Rchg, protects the Cchg pin from any over/under voltage conditions caused by excessive input signal, or an active input signal when the device is in shutdown. The recommended value for Rchg is  $1 k \Omega$ . If the input signal is less than  $V_{\rm DD} + 0.3 V$  and greater than -0.3 V, and if the input signal is disabled when in shutdown mode, Rchg may be shorted.

#### **SELECTING DIODES**

The external diode used in Figure 1 should be a Schottky diode. A 20V diode such as the MBR0520 from Fairchild Semiconductor is recommended.

The MBR05XX series of diodes are designed to handle a maximum average current of 0.5A. For applications exceeding 0.5A average but less than 1A, a Microsemi UPS5817 can be used.

#### **DUTY CYCLE**

The maximum duty cycle of the boost converter determines the maximum boost ratio of output-to-input voltage that the converter can attain in continuous mode of operation. The duty cycle for a given boost application is defined as:

Duty Cycle =

$$(V_{OUT} + V_{DIODE} - V_{DD}) / (V_{AMP} + V_{DIODE} - V_{SW})$$

This applies for continuous mode operation.

#### **INDUCTANCE VALUE**

The first question we are usually asked is: "How small can I make the inductor." (because they are the largest sized component and usually the most costly). The answer is not simple and involves trade-offs in performance. Larger inductors mean less inductor ripple current, which typically means less output voltage ripple (for a given size of output capacitor). Larger inductors also mean more load power can be delivered because the energy stored during each switching cycle is:

$$E = L/2 x (lp)2$$

Where "lp" is the peak inductor current. An important point to observe is that the LM4962 will limit its switch current based on peak current. This means that since lp(max) is fixed, increasing L will increase the maximum amount of power available to the load. Conversely, using too little inductance may limit the amount of load current which can be drawn from the output.

Best performance is usually obtained when the converter is operated in "continuous" mode at the load current range of interest, typically giving better load regulation and less output ripple. Continuous operation is defined as not allowing the inductor current to drop to zero during the cycle. It should

be noted that all boost converters shift over to discontinuous operation as the output load is reduced far enough, but a larger inductor stays "continuous" over a wider load current range.

Taiyo-Yudens NR4012 inductor series is recommended.

#### **MAXIMUM SWITCH CURRENT**

The maximum FET switch current available before the current limiter cuts in is dependent on duty cycle of the application. This is illustrated in a graph in the typical performance characterization section which shows typical values of switch current as a function of effective (actual) duty cycle.

# CALCULATING OUTPUT CURRENT OF BOOST CONVERTER (I<sub>AMP</sub>)

The load current of the Boost Converter is related to the average inductor current by the relation:

$$I_{AMP} = I_{IND}(AVG) \times (1 - DC)$$

(7)

Where "DC" is the duty cycle of the application. The switch current can be found by:

$$I_{SW} = I_{IND}(AVG) + 1/2 (I^{RIPPLE})$$

(8)

Inductor ripple current is dependent on inductance, duty cycle, supply voltage and frequency:

$$I_{BIPPLE} = DC \times (V_{DD}-V_{SW}) / (f \times L)$$

(9)

combining all terms, we can develop an expression which allows the maximum available load current to be calculated:

$$I_{AMP}(max) = (1-DC)x(I_{SW}(max)-DC(V_{DD}-V_{SW}))/2fL(10)$$

The equation shown to calculate maximum load current takes into account the losses in the inductor or turn-OFF switching losses of the FET and diode.

### DESIGN PARAMETERS V<sub>SW</sub> AND I<sub>SW</sub>

The value of the FET "ON" voltage (referred to as  $V_{\rm SW}$  in equations 7 thru 10) is dependent on load current. A good approximation can be obtained by multiplying the "ON Resistance" of the FET times the average inductor current.

The maximum peak switch current the device can deliver is dependent on duty cycle.

### **INDUCTOR SUPPLIERS**

The recommended inductors for the LM4962 is the Taiyo-Yuden NR4012. When selecting an inductor, make certain that the continuous current rating is high enough to avoid saturation at peak currents. A suitable core type must be used to minimize core (switching) losses, and wire power losses must be considered when selecting the current rating.

### **PCB LAYOUT GUIDELINES**

High frequency boost converters require very careful layout of components in order to get stable operation and low noise. All components must be as close as possible to the LM4962 device. It is recommended that a 4-layer PCB be used so that internal ground planes are available. See Figures 6–11 for demo board reference schematic and layout.

Some additional guidelines to be observed:

- 1. Keep the path between L1, D2, and C2 extremely short. Parasitic trace inductance in series with D2 and C2 will increase noise and ringing.

- 2. If internal ground planes are available (recommended) use vias to connect directly to ground at pins A3 and D1 of U1, as well as the negative sides of capacitors  $C_s1$  and C2.

- 3. To ensure correct operation of this device, it is essential that the GND (SW) pin (A3), GND pin (D1), and the negative side of Cs2 be connected to the same GND plane. Cs2 should be placed as close as possible to these two GND planes.

## GENERAL MIXED-SIGNAL LAYOUT RECOMMENDATION

This section provides practical guidelines for mixed signal PCB layout that involves various digital/analog power and ground traces. Designers should note that these are only "rule-of-thumb" recommendations and the actual results will depend heavily on the final layout.

#### **Power and Ground Circuits**

For 2 layer mixed signal design, it is important to isolate the digital power and ground trace paths from the analog power and ground trace paths. Star trace routing techniques (bringing individual traces back to a central point rather than daisy chaining traces together in a serial manner) can have a

major impact on low level signal performance. Star trace routing refers to using individual traces to feed power and ground to each circuit or even device. This technique will take require a greater amount of design time but will not increase the final price of the board. The only extra parts required may be some jumpers.

#### Single-Point Power / Ground Connection

The analog power traces should be connected to the digital traces through a single point (link). A "Pi-filter" can be helpful in minimizing high frequency noise coupling between the analog and digital sections. It is further recommended to place digital and analog power traces over the corresponding digital and analog ground traces to minimize noise coupling.

### **Placement of Digital and Analog Components**

All digital components and high-speed digital signals traces should be located as far away as possible from analog components and circuit traces.

#### **Avoiding Typical Design / Layout Problems**

Avoid ground loops or running digital and analog traces parallel to each other (side-by-side) on the same PCB layer. When traces must cross over each other do it at 90 degrees. Running digital and analog traces at 90 degrees to each other from the top to the bottom side as much as possible will minimize capacitive noise coupling and crosstalk.

FIGURE 6. Demo Board Schematic

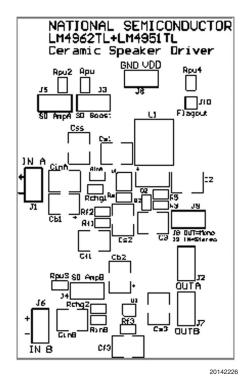

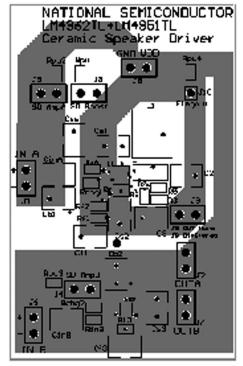

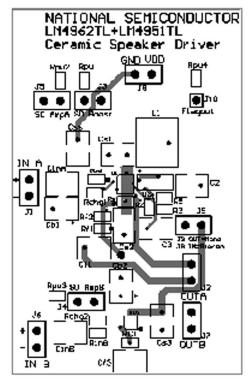

FIGURE 7. Silkscreen

20142236

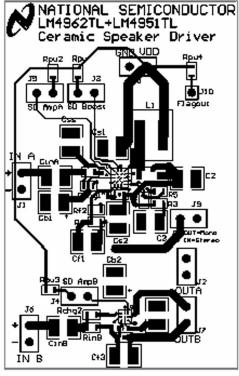

FIGURE 8. Top Layer

20142237

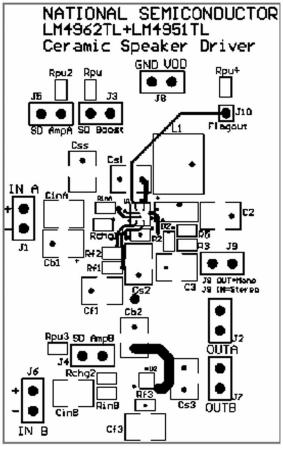

FIGURE 9. Mid- Layer 1

20142229

FIGURE 10. Mid- Layer 2

20142230

FIGURE 11. Bottom Layer

# **Revision History**

| Rev | Date     | Description                                 |  |

|-----|----------|---------------------------------------------|--|

| 1.0 | 7/15/05  | Edited 20142201.                            |  |

| 1.1 | 9/27/05  | Edited the table underneath Figure 1 and    |  |

|     |          | added the pin out pkg.                      |  |

| 1.2 | 10/24/05 | Added the 2 timing dgs.                     |  |

| 1.3 | 10/28/05 | Added 201422 05 and replaced 01 with 06.    |  |

| 1.4 | 10/31/05 | Edited 201422 05 and 06.                    |  |

| 1.5 | 11/09/05 | Replaced 20142202 with 20142207.            |  |

| 1.6 | 11/10/05 | Some texts edits.                           |  |

| 1.7 | 11/16/05 | Added the Application Section.              |  |

| 1.8 | 12/13/05 | Texts edits and edited some graphics.       |  |

| 1.9 | 12/15/05 | Edited art 19.                              |  |

| 2.0 | 12/16/05 | Input some texts edits, released D/S to the |  |

|     |          | Web.                                        |  |

| 2.1 | 01/06/06 | Added additional Application information,   |  |

|     |          | then re-released D/S to the WEB.            |  |

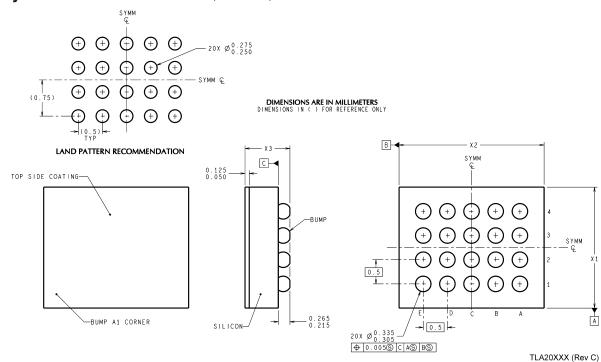

### Physical Dimensions inches (millimeters) unless otherwise noted

Thin micro SMD Order Number LM4962TL **NS Package Number TLA2011A**  $X1 = 1.970 \pm 0.03$ mm  $X2 = 2.466 \pm 0.03$ mm  $X3 = 0.600 \pm 0.075$ mm

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

**National Semiconductor Americas Customer** Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560