## LMC6442

# Dual Micropower Rail-to-Rail Output Single Supply Operational Amplifier

## **General Description**

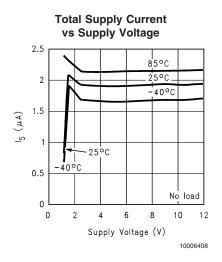

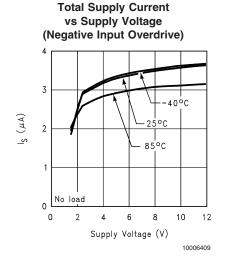

The LMC6442 is ideal for battery powered systems, where very low supply current (less than one microamp per amplifier) and Rail-to-Rail output swing is required. It is characterized for 2.2V to 10V operation, and at 2.2V supply, the LMC6442 is ideal for single (Li-Ion) or two cell (NiCad or alkaline) battery systems.

The LMC6442 is designed for battery powered systems that require long service life through low supply current, such as smoke and gas detectors, and pager or personal communications systems.

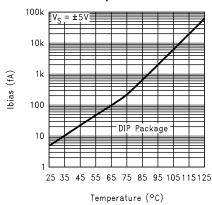

Operation from single supply is enhanced by the wide common mode input voltage range which includes the ground (or negative supply) for ground sensing applications. Very low (5fA, typical) input bias current and near constant supply current over supply voltage enhance the LMC6442's performance near the end-of-life battery voltage.

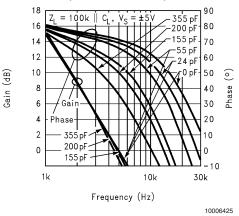

Designed for closed loop gains of greater than plus two (or minus one), the amplifier has typically 9.5 KHz GBWP (Gain Bandwidth Product). Unity gain can be used with a simple compensation circuit, which also allows capacitive loads of up to 300 pF to be driven, as described in the Application Notes section.

For compact assembly the LMC6442 is available in the MSOP 8 pin package, about one half the size required by the SOIC 8 pin package. 8 pin DIP and 8 pin SOIC are also available.

### **Features**

(Typical,  $V_S = 2.2V$ )

Output Swing to within 30 mV of supply rail

■ High voltage gain 103 dB

■ Gain Bandwidth Product 9.5 KHz ■ Guaranteed for: 2.2V, 5V, 10V

■ Low Supply Current 0.95 µA/Amplifier

■ 2.1 µW/Amplifier Power consumption

■ Stable for  $A_V \ge +2$  or  $A_V \le -1$

## **Applications**

- Portable instruments

- Smoke/gas/CO/fire detectors

- Pagers/cell phones

- Instrumentation

- Thermostats

- Occupancy sensors

- Cameras

- Active badges

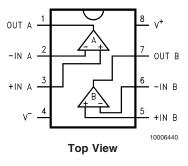

# **Connection Diagram**

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance (Note 2) 2 kV

Differential Input Voltage  $\pm$ Supply Voltages Voltage at Input/Output Pin  $(V^+) + 0.3V, (V^-) - 0.3V$

Supply Voltage  $(V^+ - V^-)$ : 16V

Current at Input Pin (Note 10) ±5 mA

Current at Output Pin(Notes 3, 7) ±30 mA Lead Temp. (soldering 10 sec) 260°C

Storage Temp. Range:  $-65^{\circ}\text{C} \text{ to } +150^{\circ}\text{C}$

Junction Temp. (Note 4)

# **Operating Ratings**(Note 1)

Supply Voltage  $1.8V \le V_S \le 11V$ Junction Temperature  $-40^{\circ}\text{C} < T_J < +85^{\circ}\text{C}$

150°C

Range: LMC6442AI, LMC6442I Thermal Resistance ( $\theta_{JA}$ )

M Package, 8-pin Surface 193°C/W

Mount

MSOP Package 235°C/W N Package, 8-pin Molded DIP 115°C/W

### 2.2V Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 2.2V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L = 1$  M $\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                                 | Conditions                                            | Typ<br>(Note 5) | LMC6442AI<br>Limit<br>(Note 6) | LMC6442I<br>Limit<br>(Note 6) | Units       |

|-------------------|-------------------------------------------|-------------------------------------------------------|-----------------|--------------------------------|-------------------------------|-------------|

| V <sub>os</sub>   | Input Offset Voltage                      |                                                       |                 | ±3                             | ±7                            | mV          |

| 105               | par emeer remage                          |                                                       | -0.75           | ±4                             | ±8                            | max         |

| TCV <sub>OS</sub> | Temp. coefficient of input offset voltage |                                                       | 0.4             |                                |                               | μV/°C       |

| I <sub>B</sub>    | Input Bias Current                        | (Note 14)                                             | 0.005           | 4                              | 4                             | pA<br>max   |

| I <sub>OS</sub>   | Input Offset Current                      | (Note 14)                                             | 0.0025          | 2                              | 2                             | pA<br>max   |

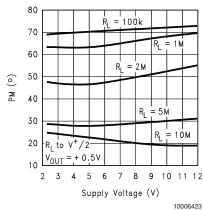

| CMRR              | Common Mode<br>Rejection Ratio            | -0.1V ≤ V <sub>CM</sub> ≤0.5V                         | 92              | 67<br><b>67</b>                | 67<br><b>67</b>               | dB min      |

| C <sub>IN</sub>   | Common Mode Input Capacitance             |                                                       | 4.7             |                                |                               | pF          |

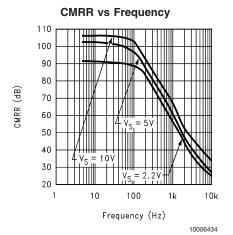

| PSRR              | Power Supply Rejection Ratio              | V <sub>S</sub> = 2.5 V to 10V                         | 95              | 75<br><b>75</b>                | 75<br><b>75</b>               | dB<br>min   |

| V <sub>CM</sub>   | Input Common-Mode<br>Voltage Range        | 01455 . 50 .15                                        | 1.3             | 1.05<br><b>0.95</b>            | 1.05<br><b>0.95</b>           | V<br>min    |

|                   |                                           | CMRR ≥ 50 dB                                          | -0.3            | -0.2<br><b>0</b>               | -0.2<br><b>0</b>              | V<br>max    |

| A <sub>V</sub>    | Large Signal Voltage                      | Sourcing (Note 11)                                    | 100             |                                |                               | ID          |

|                   | Gain                                      | Sinking(Note 11)                                      | 94              |                                |                               | dB<br>min   |

|                   |                                           | V <sub>O</sub> = 0.22V to 2V                          | 103             | 80                             | 80                            | ] ''''''    |

| V <sub>O</sub>    | Output Swing                              | V <sub>ID</sub> = 100 mV (Note 13)                    | 2.18            | 2.15<br><b>2.15</b>            | 2.15<br><b>2.15</b>           | V<br>min    |

|                   |                                           | $V_{ID} = -100 \text{ mV (Note 13)}$                  | 22              | 60<br><b>60</b>                | 60<br><b>60</b>               | mV<br>max   |

| I <sub>sc</sub>   | Output Short Circuit<br>Current           | Sourcing, V <sub>ID</sub> = 100 mV<br>(Notes 12, 13)  | 50              | 18<br><b>17</b>                | 18<br><b>17</b>               | μА          |

|                   |                                           | Sinking, $V_{ID} = -100 \text{ mV}$<br>(Notes 12, 13) | 50              | 20<br><b>19</b>                | 20<br><b>19</b>               | min         |

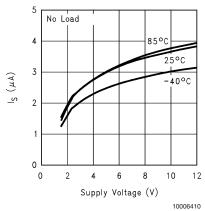

| I <sub>S</sub>    | Supply Current (2 amplifiers)             | R <sub>L</sub> = open                                 | 1.90            | 2.4<br><b>3.0</b>              | 2.6<br><b>3.2</b>             | μA<br>- max |

| 40.51             |                                           | V <sup>+</sup> = 1.8V, R <sub>L</sub> = open          | 2.10            |                                |                               |             |

| SR SR             | rical Characteristics Slew Rate (Note 8)  |                                                       | 2.2             |                                |                               | V/ms        |

## 2.2V Electrical Characteristics (Continued)

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 2.2V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L = 1 \text{ M}\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter      | Conditions | Typ<br>(Note 5) | LMC6442AI<br>Limit<br>(Note 6) | LMC6442I<br>Limit<br>(Note 6) | Units  |

|----------------|----------------|------------|-----------------|--------------------------------|-------------------------------|--------|

| GBWP           | Gain-Bandwidth |            | 9.5             |                                |                               | KHz    |

|                | Product        |            |                 |                                |                               |        |

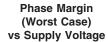

| φ <sub>m</sub> | Phase Margin   | (Note 15)  | 63              |                                |                               | Degree |

### **5V Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L = 1~M\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol                                  | Parameter ical Characteristics     | Conditions                                            | Typ<br>(Note 5) | LMC6442AI<br>Limit<br>(Note 6) | LMC6442I<br>Limit<br>(Note 6) | Units     |

|-----------------------------------------|------------------------------------|-------------------------------------------------------|-----------------|--------------------------------|-------------------------------|-----------|

|                                         |                                    | T                                                     |                 | +0                             | <b>+7</b>                     |           |

| V <sub>OS</sub>                         | Input Offset Voltage               |                                                       | -0.75           | ±3<br>±4                       | ±7<br><b>±8</b>               | mV<br>max |

| TCV <sub>os</sub>                       | Temp. coefficient of               |                                                       | 0.4             |                                |                               | μV/°C     |

| TOVOS                                   | input offset voltage               |                                                       | 0.4             |                                |                               | μν/ Ο     |

| I <sub>B</sub>                          | Input Bias Current                 | (Note 14)                                             | 0.005           | 4                              | 4                             | pA<br>max |

| I <sub>os</sub>                         | Input Offset Current               | (Note 14)                                             | 0.0025          | 2                              | 2                             | pA<br>max |

| CMRR                                    | Common Mode                        | -0.1V ≤ V <sub>CM</sub> ≤3.5V                         | 102             | 70                             | 70                            | dB        |

| • • • • • • • • • • • • • • • • • • • • | Rejection Ratio                    | 0.1.1 = 1.CM =0.01                                    |                 | 70                             | 70                            | min       |

| C <sub>IN</sub>                         | Common Mode Input Capacitance      |                                                       | 4.1             |                                |                               | pF        |

| PSRR                                    | Power Supply                       | V <sub>S</sub> = 2.5 V to 10V                         | 05              | 75                             | 75                            | dB        |

|                                         | Rejection Ratio                    |                                                       | 95              | 75                             | 75                            | min       |

| V <sub>CM</sub>                         | Input Common-Mode<br>Voltage Range | CMRR ≥ 50 dB                                          | 4.1             | 3.85                           | 3.85                          | V         |

|                                         |                                    |                                                       | 4.1             | 3.75                           | 3.75                          | min       |

|                                         |                                    |                                                       | -0.4            | -0.2                           | -0.2                          | V         |

|                                         |                                    |                                                       |                 | 0                              | 0                             | max       |

| A <sub>V</sub> L                        | Large Signal Voltage<br>Gain       | Sourcing (Note 11)                                    | 100             |                                |                               | dB        |

|                                         |                                    | Sinking (Note 11)                                     | 94              |                                |                               | min       |

|                                         |                                    | $V_{\rm O} = 0.5 V$ to 4.5 V                          | 103             | 80                             | 80                            |           |

| $V_{O}$                                 | Output Swing                       | V <sub>ID</sub> = 100 mV                              | 4.99            | 4.95                           | 4.95                          | V         |

|                                         |                                    | (Note 13)                                             |                 | 4.95                           | 4.95                          | min       |

|                                         |                                    | $V_{ID} = -100 \text{ mV}$                            | 20              | 50                             | 50                            | mV        |

|                                         |                                    | (Note 13)                                             |                 | 50                             | 50                            | max       |

| I <sub>SC</sub>                         | Output Short Circuit               | Sourcing, V <sub>ID</sub> = 100 mV                    | 500             | 300                            | 300                           |           |

|                                         | Current                            | (Notes 12, 13)                                        |                 | 200                            | 200                           | μA        |

|                                         |                                    | Sinking, $V_{ID} = -100 \text{ mV}$<br>(Notes 12, 13) | 350             | 200<br><b>150</b>              | 200<br><b>150</b>             | min       |

| I <sub>S</sub>                          | Supply Current (2 amplifiers)      | R <sub>L</sub> = open                                 | 1.90            | 2.4<br><b>3.0</b>              | 2.6<br><b>3.2</b>             | μA<br>max |

| AC Electr                               | ical Characteristics               |                                                       |                 |                                |                               | 1         |

| SR                                      | Slew Rate (Note 8)                 |                                                       | 4.1             | 2.5                            | 2.5                           | V/ms      |

| GBWP                                    | Gain-Bandwidth Product             |                                                       | 10              |                                |                               | KHz       |

| φ <sub>m</sub>                          | Phase Margin                       | (Note 15)                                             | 64              |                                |                               | Degree    |

# **5V Electrical Characteristics** (Continued)

Unless otherwise specified, all limits guaranteed for  $T_J=25^{\circ}C$ ,  $V^+=5V$ ,  $V^-=0V$ ,  $V_{CM}=V_O=V^+/2$ , and  $R_L=1~M\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol | Parameter      | Conditions                            | Typ<br>(Note 5) | LMC6442AI<br>Limit<br>(Note 6) | LMC6442I<br>Limit<br>(Note 6) | Units |

|--------|----------------|---------------------------------------|-----------------|--------------------------------|-------------------------------|-------|

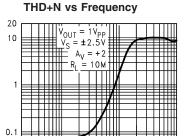

| THD    | Total Harmonic | $A_V = +2$ , $f = 100$ Hz,            | 0.08            |                                |                               | %     |

|        | Distortion     | $R_L = 10M\Omega$ , $V_{OUT} = 1 Vpp$ |                 |                                |                               |       |

### **10V Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 10V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L = 1~M\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                                 | Conditions                                            | Typ<br>(Note 5) | LMC6442AI<br>Limit<br>(Note 6) | LMC6442I<br>Limit<br>(Note 6) | Units     |

|-------------------|-------------------------------------------|-------------------------------------------------------|-----------------|--------------------------------|-------------------------------|-----------|

|                   | rical Characteristics                     | T                                                     |                 |                                |                               | 1         |

| $V_{OS}$          | Input Offset Voltage                      |                                                       | -1.5            | ±3                             | ±7                            | mV        |

|                   |                                           |                                                       |                 | ±4                             | ±8                            | max       |

| TCV <sub>os</sub> | Temp. coefficient of input offset voltage |                                                       | 0.4             |                                |                               | μV/°C     |

| I <sub>B</sub>    | Input Bias Current                        | (Note 14)                                             | 0.005           | 4                              | 4                             | pA<br>max |

| I <sub>os</sub>   | Input Offset Current                      | (Note 14)                                             | 0.0025          | 2                              | 2                             | pA<br>max |

| CMRR              | Common Mode                               | -0.1V ≤ V <sub>CM</sub> ≤8.5V                         | 105             | 70                             | 70                            | dB        |

|                   | Rejection Ratio                           |                                                       |                 | 70                             | 70                            | min       |

| C <sub>IN</sub>   | Common Mode Input Capacitance             |                                                       | 3.5             |                                |                               | pF        |

| PSRR              | Power Supply                              | V <sub>S</sub> = 2.5 V to 10V                         | 95              | 75                             | 75                            | dB        |

|                   | Rejection Ratio                           |                                                       | 95              | 75                             | 75                            | min       |

| $V_{CM}$          | Input Common-Mode                         |                                                       | 9.1             | 8.85                           | 8.85                          | V         |

|                   | Voltage Range                             |                                                       | 9.1             | 8.75                           | 8.75                          | min       |

|                   |                                           |                                                       | -0.4            | -0.2                           | -0.2                          | V         |

|                   |                                           |                                                       |                 | 0                              | 0                             | max       |

| $A_V$             | Large Signal Voltage                      | Sourcing (Note 11)                                    | 120             |                                |                               | ما ا      |

|                   | Gain                                      | Sinking (Note 11)                                     | 100             |                                |                               | dB<br>min |

|                   |                                           | V <sub>O</sub> = 0.5V to 9.5V                         | 104             | 80                             | 80                            | ] ''''''  |

| Vo                | Output Swing                              | V <sub>ID</sub> = 100 mV                              | 9.99            | 9.97                           | 9.97                          | V         |

|                   |                                           | (Note 13)                                             |                 | 9.97                           | 9.97                          | min       |

|                   |                                           | $V_{ID} = -100 \text{ mV(Note } 13)$                  | 22              | 50                             | 50                            | mV        |

|                   |                                           |                                                       |                 | 50                             | 50                            | max       |

| I <sub>sc</sub>   | Output Short Circuit                      | Sourcing, V <sub>ID</sub> = 100 mV                    | 2100            | 1200                           | 1200                          |           |

|                   | Current                                   | (Notes 12, 13)                                        |                 | 1000                           | 1000                          | μΑ        |

|                   |                                           | Sinking, $V_{ID} = -100 \text{ mV}$<br>(Notes 12, 13) | 900             | 600<br><b>500</b>              | 600<br><b>500</b>             | min       |

| Is                | Supply Current (2                         | R <sub>L</sub> = open                                 | 1.90            | 2.4                            | 2.6                           | μΑ        |

|                   | amplifiers)                               |                                                       |                 | 3.0                            | 3.2                           | max       |

| AC Electr         | ical Characteristics                      |                                                       |                 |                                |                               |           |

| SR                | Slew Rate(Note 8)                         |                                                       | 4.1             | 2.5                            | 2.5                           | V/ms      |

| GBWP              | Gain-Bandwidth<br>Product                 |                                                       | 10.5            |                                |                               | KHz       |

| φ <sub>m</sub>    | Phase Margin                              | (Note 15)                                             | 68              |                                |                               | Degre     |

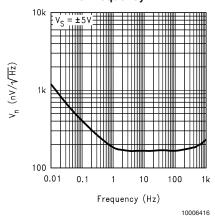

| e <sub>n</sub>    | Input-Referred Voltage Noise              | R <sub>L</sub> = open<br>f = 10 Hz                    | 170             |                                |                               | nV/√H     |

### 10V Electrical Characteristics (Continued)

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 10V$ ,  $V_- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , and  $R_L = 1~M\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter           | Conditions            | Typ<br>(Note 5) | LMC6442AI<br>Limit<br>(Note 6) | LMC6442I<br>Limit<br>(Note 6) | Units  |

|----------------|---------------------|-----------------------|-----------------|--------------------------------|-------------------------------|--------|

| i <sub>n</sub> | Input-Referred      | R <sub>L</sub> = open | 0.0002          |                                |                               | pA/√Hz |

|                | Current Noise       | f = 10 Hz             |                 |                                |                               |        |

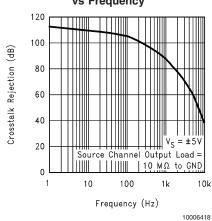

|                | Crosstalk Rejection | (Note 9)              | 85              |                                |                               | dB     |

## **Electrical Characteristics (continued)**

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

**Note 2:** Human body model, 1.5 k $\Omega$  in series with 100 pF.

Note 3: Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C. Output currents in excess of ±30 mA over long term may adversely affect reliability.

Note 4: The maximum power dissipation is a function of  $T_{J(max)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(max)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly into a PC board.

Note 5: Typical Values represent the most likely parametric norm.

Note 6: All limits are guaranteed by testing or statistical analysis unless otherwise specified.

Note 7: Do not short circuit output to V+, when V+ is greater than 13V or reliability will be adversely affected.

Note 8: Slew rate is the slower of the rising and falling slew rates.

Note 9: Input referred,  $V^+ = 10V$  and  $R_L = 10~M\Omega$  connected to 5V. Each amp excited in turn with 1 KHz to produce about 10 Vpp output.

Note 10: Limiting input pin current is only necessary for input voltages that exceed absolute maximum input voltage ratings.

Note 11: R<sub>L</sub> connected to V<sup>+</sup>/2. For Sourcing Test,  $V_O > V^+/2$ . For Sinking tests,  $V_O < V^+/2$ .

Note 12: Output shorted to ground for sourcing, and shorted to V+ for sinking short circuit current test.

Note 13: V<sub>ID</sub> is differential input voltage referenced to inverting input.

Note 14: Limits guaranteed by design.

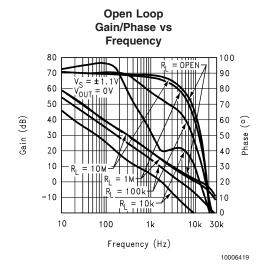

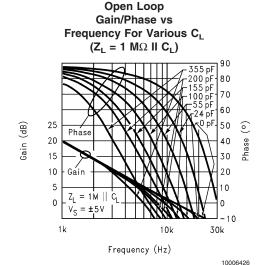

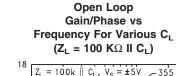

Note 15: See the Typical Performance Characteristics and Application Notes sections for more details.

# **Typical Performance Characteristics**

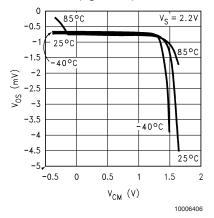

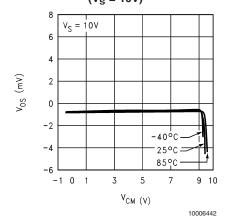

$\rm V_S=5V,$  Single Supply,  $\rm T_A=25^{\circ}C$  unless otherwise specified

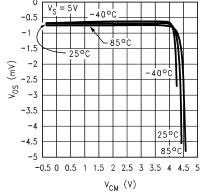

### Offset Voltage vs Common Mode Voltage (V<sub>S</sub> = 2.2V)

### Offset Voltage vs Common Mode Voltage (V<sub>S</sub> = 10V)

# Input Bias Current vs Temperature

10006441

### Offset Voltage vs Common Mode Voltage $(V_S = 5V)$

10006407

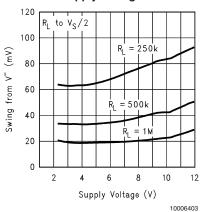

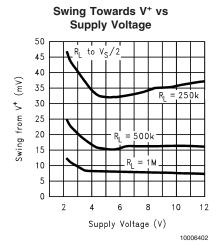

#### Swing Towards V<sup>-</sup> vs Supply Voltage

### vs Temperature 120 to $V_S/2$ 100 80 Swing (mV) 60 500k, Neg Swing 20 0 20 60 80 85 -40 -20 40 Temperature (°C) 10006401

Swing From Rail(s)

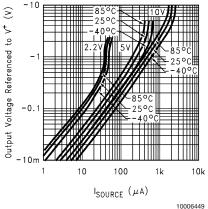

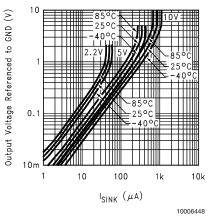

Output Source Current vs Output Voltage

Output Sink Current vs Output Voltage

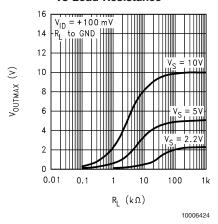

Maximum Output Voltage vs Load Resistance

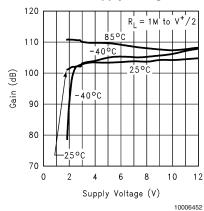

Large Signal Voltage Gain vs Supply Voltage

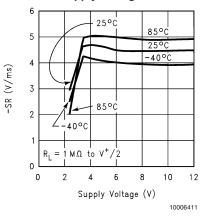

### Negative Slew Rate vs Supply Voltage

# Input Voltage Noise vs Frequency

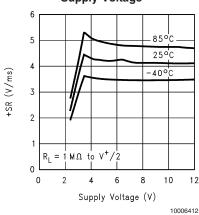

### Positive Slew Rate vs Supply Voltage

# Cross-Talk Rejection vs Frequency

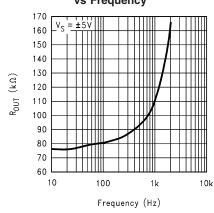

# Output Impedance vs Frequency

10006433

THD+N (%)

0.01

20

# **Typical Performance Characteristics** $V_S = 5V$ , Single Supply, $T_A = 25^{\circ}C$ unless otherwise specified (Continued)

0 1k Frequency (Hz)

10006428

10k

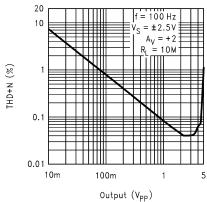

### THD+N vs Amplitude

10006427

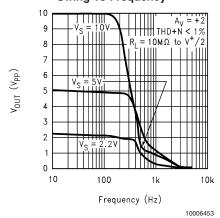

### Maximum Output Swing vs Frequency

100

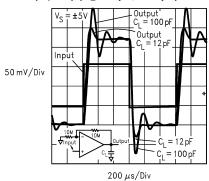

Small Signal Step Response (A<sub>V</sub>=+2) (C<sub>L</sub>=12 pF, 100 pF)

Large Signal Step

Response  $(A_V=+2) (C_L=100 pF)$

10006451

10006429

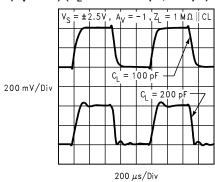

# Typical Performance Characteristics $V_s = 5V$ , Single Supply, $T_A = 25^{\circ}C$ unless otherwise

specified (Continued)

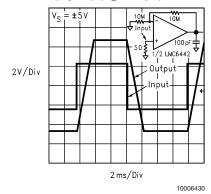

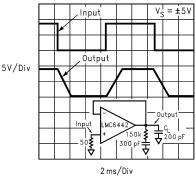

### Large Signal Step Response (A<sub>V</sub> = +1) (C<sub>L</sub>= 200pF)

10006432

# **Applications Information**

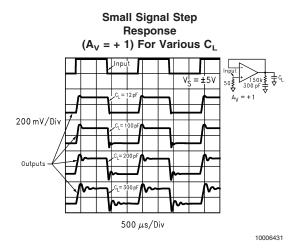

#### **USING LMC6442 IN UNITY GAIN APPLICATIONS**

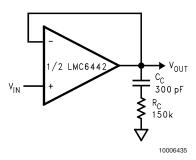

LMC6442 is optimized for maximum bandwidth and minimal external components when operating at a minimum closed loop gain of +2 (or -1). However, it is also possible to operate the device in a unity gain configuration by adding external compensation as shown in Figure 1:

FIGURE 1.  $A_V = +1$  Operation by adding  $C_c$  and  $R_c$

Using this compensation technique it is possible to drive capacitive loads of up to 300 pF without causing oscillations (see the Typical Performance Characteristics for step response plots). This compensation can also be used with other gain settings in order to improve stability, especially when driving capacitive loads (for optimum performance,  $\rm R_{c}$  and  $\rm C_{c}$  may need to be adjusted).

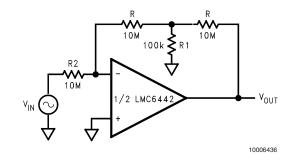

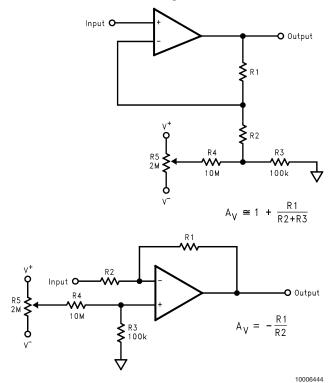

#### **USING "T" NETWORK**

Compromises need to be made whenever high gain inverting stages need to achieve a high input impedance as well. This is especially important in low current applications which tend to deal with high resistance values. Using a traditional inverting amplifier, gain is inversely proportional to the resistor value tied between the inverting terminal and input while the input impedance is equal to this value. For example, in order to build an inverting amplifier with an input impedance of  $10 M\Omega$  and a gain of 100, one needs to come up with a feedback resistor of  $1000 M\Omega$  -an expensive task.

An alternate solution is to use a "T" Network in the feedback path, as shown in Fig. 2.

Closed loop gain,  $A_V$  is given by:

$$A_{V} = -\frac{R^{2}}{R^{2}} \bullet \left(\frac{2}{R} + \frac{1}{R^{1}}\right)$$

FIGURE 2. "T" Network Used to Replace High Value Resistor

It must be noted, however, that using this scheme, the realizable bandwidth would be less than the theoretical maximum. With feedback factor,  $\beta$ , defined as:

$$\beta \cong \frac{R2}{R2 + R} \bullet \frac{R1}{R1 + R}$$

for R2 >> R1

$$BW(-3~dB)\approx~GBWP~\bullet~\beta$$

In this case, assuming a GBWP of about 10 KHz, the expected BW would be around 50 Hz (vs 100 Hz with the conventional inverting amplifier).

Looking at the problem from a different view, with  $R_F$  defined by  $A_V$ •Rin, one could select a value for R in the "T" Network and then determine R1 based on this selection:

$$R1 = \frac{R^2}{R_F - 2R}$$

### **Applications Information** (Continued)

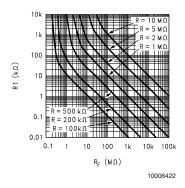

FIGURE 3. "T" Network Values for Various Values of R

For convenience, Fig. 3 shows R1 vs  $R_{\rm F}$  for different values of R.

#### **DESIGN CONSIDERATIONS FOR CAPACITIVE LOADS**

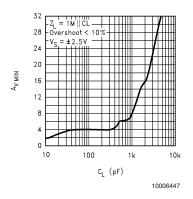

As with many other opamps, the LMC6442 is more stable at higher closed loop gains when driving a capacitive load. Figure 4 shows minimum closed loop gain versus load capacitance, to achieve less than 10% overshoot in the output small signal response. In addition, the LMC6442 is more stable when it provides more output current to the load and when its output voltage does not swing close to V<sup>-</sup>.

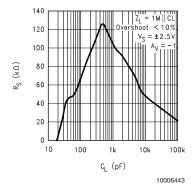

The LMC6442 is more tolerant to capacitive loads when the equivalent output load resistance is lowered or when output voltage is 1V or greater from the V $^-$  supply. The capacitive load drive capability is also improved by adding an isolating resistor in series with the load and the output of the device. Figure 5 shows the value of this resistor for various capacitive loads (A $_{\rm V}=-1$ ), while limiting the output to less than 10 % overshoot.

Referring to the Typical Performance Characteristics plot of Phase Margin (Worst Case) vs Supply Voltage, note that Phase Margin increases as the equivalent output load resistance is lowered. This plot shows the expected Phase Margin when the device output is very close to V $^-$ , which is the least stable condition of operation. Comparing this Phase Margin value to the one read off the Open Loop Gain/Phase vs Frequency plot, one can predict the improvement in Phase Margin if the output does not swing close to V $^-$ . This dependence of Phase Margin on output voltage is minimized as long as the output load,  $R_{\rm L}$ , is about  $1 \rm M\Omega$  or less.

**Output Phase Reversal:** The LMC6442 is immune against this behavior even when the input voltages exceed the common mode voltage range.

**Output Time Delay:** Due to the ultra low power consumption of the device, there could be as long as 2.5 ms of time delay from when power is applied to when the device output reaches its final value.

FIGURE 4. Minimum Operating Gain vs Capactive Load

FIGURE 5. Isolating Resistor Value vs Capactive Load

# **Application Circuits**

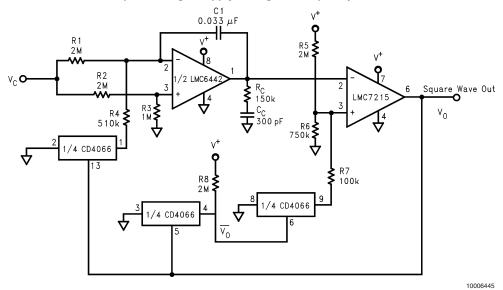

### Micropower Single Supply Voltage to Frequency Converter

V  $^{+}$  = 5V:  $I_{S}$  < 10 $\mu A,~f/V_{C}$  = 4.3 (Hz/V)

R1

$$\cong$$

4R4

R2 = 2R3

$$f(Hz) = \frac{V_C}{3R_1C_1V^+ \left[\frac{R6}{R5+R6} - \frac{(R6 \parallel R7)}{(R6 \parallel R7)+R5}\right]} \cong \frac{V_C(R5+R6)}{3R_1C_1V^+(R6-R7)} \text{ for } R5 >> R6 \text{ and } R6 >> R7$$

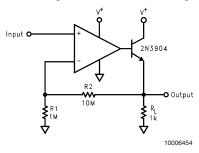

### **Gain Stage with Current Boosting**

# Application Circuits (Continued)

### Offset Nulling Schemes

# **Ordering Information**

|            | Temperature R                                            | NCC                         | Cummiliani     |                          |                                   |  |

|------------|----------------------------------------------------------|-----------------------------|----------------|--------------------------|-----------------------------------|--|

| Package    | Industrial –40°C to +85°C                                | Military -55°C to<br>+125°C | NSC<br>Drawing | Supplied<br>AS           | Package Marking                   |  |

| 8-pin SO-8 | LMC6442AIM, LMC6442IM                                    | -                           | M08A           | Rails                    |                                   |  |

|            | LMC6442AIMX, LMC6442IMX                                  | -                           | M08A           | 2.5K<br>Tape and<br>Reel | LMC6442AIM<br>LMC6442IM           |  |

| MSOP       | LMC6442AIMM,<br>LMC6442AIMMX, LMC6442IMM,<br>LMC6442IMMX | -                           | MUA08A         | Rails                    | A08A                              |  |

|            | LMC6442AIMMX,<br>LMC6442IMMX                             | -                           | MUA08A         | 3K Tape<br>and Reel      |                                   |  |

| 8-pin DIP  | LMC6442AIN, LMC6442IN                                    | -                           | N08E           | Rails                    | LMC6442AIN,<br>LMC6442IN          |  |

| 8-pin CDIP | -                                                        | 5962-9761301QPA             | J08A           | Rails                    | LMC6442AMJ-QML<br>5962-976130IQPA |  |

| 10-pin SO  | -                                                        | 5962-9761301QXA             | WG10A          | Trays                    | LMC6442AMWG-Q<br>9761301QXA       |  |

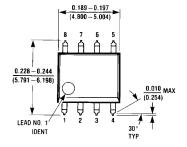

# **Physical Dimensions** inches (millimeters) unless otherwise noted

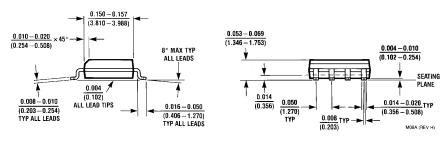

8-Lead (0.150" Wide) Molded Small Outline Package, JEDEC Order Number LMC6442AIM or LMC6442IM or LMC6442AIMX or LMC6442IMX **NS Package Number M08A**

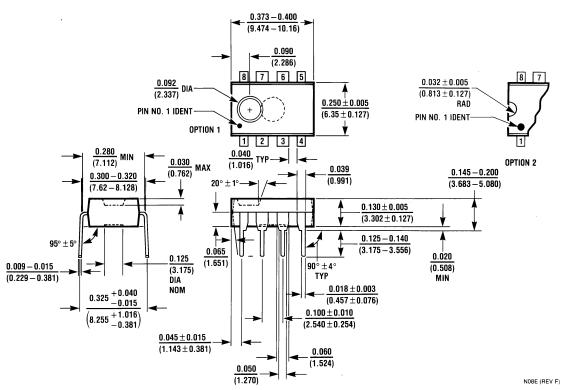

8-Lead (0.300" Wide) Molded Dual-In-Line Package Order Number LMC6442AIN or LMC6442IN or LMC6442INX **NS Package Number N08E**

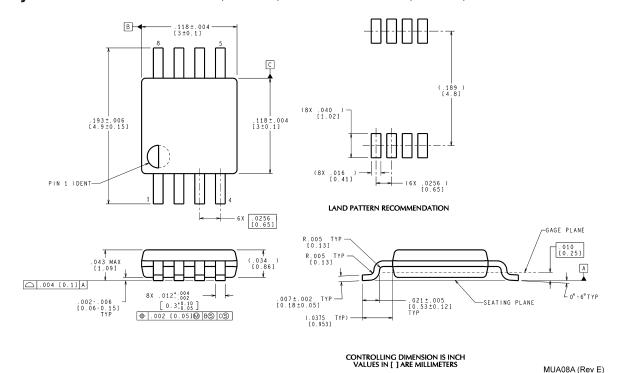

### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

8-Lead (0.118" Wide) Molded Mini Small Outline Package

Order Number LMC6442AIMM or LMC6442IMMX or LMC6442IMMX

NS Package Number MUA08A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560