# Bank Interleaved Memory System for an Am29030™ Microprocessor

Application Note

by David Stoenner

This application note explains how to modify the EZ-030 demonstration board to increase the bus speed from 16 MHz to 30 MHz.

#### INTRODUCTION

Although memory has grown faster over the years, memory speed has not kept up with the speed of processors or the demand for even faster microprocessor systems, be they desktop or embedded. The EZ-030 demonstration board addresses the need for a low-cost and simple memory system for the AMD Family of Am29030 microprocessor RISC-based machines, yet it is limited to a maximum bus speed of 16 MHz (see the EZ-030 Demonstration Board Theory of Operation application note for more information). When faster memories, faster PAL® devices, and faster multiplexers (74F157s) are substituted in the EZ-030 board design, 20 MHz is possible, but only in PGA versions.

Somewhere in the gray area of 20 to 25 MHz is the point where memory can no longer be single-cycled out of one memory bank. The limiting factor is the CAS access time and the processor setup time for data. However, DRAMs have a shorter data valid time from their output enable. So, if two banks are connected at the data pins and then independently cycled and the output enable (OE) of each bank is used to multiplex the values together, the memories can support the single-cycle access for which the 29K™ Family is so famous. This technique is called *bank interleaving*.

This application note explains how a few simple enhancements to the EZ-030 logic design, along with another memory bank, can extend the upper frequency limit to 30 MHz.

#### CHANGES TO DESIGN

To achieve a 30-MHz speed, make the following changes to the EZ-030 logic design:

- Replace the 16-MHz Am29030 processor with a 33-MHz Am29030 processor

- Add a memory bank

- Add an extra 16V8 to the lower address lines of the Am29030 processor for advanced counting

- Change the MSTR\_CON PAL device from a 16V8 to a 22V10

- Change the CAS\_DEC PAL device from a 16V8 to a 22V10

## Add a Memory Bank and a Counter

In a bank interleaved memory design, two memory systems with their outputs connected together form a single data bus. While one bank provides data for the current cycle, the other bank gets the next value. This requires the new bank to be ahead of the current bank, which requires an address one greater than what the processor provides. This is accomplished in the design by adding a counter on the lower processor address lines that drives the CAS addresses in the memory bank. Processor address A2 is used to select between banks while A9–A3 drive CAS A6–A0. This means the count can be loaded, incremented, or held in the counter. Since the CAS address is not needed until the second clock cycle, there is plenty of time to get the counter up-to-date with the correct address.

Note that this counter needs to be pre-incremented if the burst starts at an address boundary where A2 of the access is 1. In this case, the odd memory bank starts up first but the counter is quickly incremented to the next value, so the new CAS can start the even bank access at the next larger A9–A3 value. No address counting past A9 is needed since internal address comparators on the Am29030 processor stop all burst transactions on the bus at 1K boundaries.

## Change the MSTR\_CON PAL Device

The second design change is in the master state machine. Since the clock is now higher in frequency but the memories are not any faster, the first access must have a greater number of clock cycles to have the same time value as those at 16 MHz. The memories used are 80-ns RAS access DRAMs, so at least a 3 clock-cycle access is needed once a RAS is started. RAS is not started until a  $\overline{\text{REQ}}$  from the processor has been asserted for one clock cycle, which makes the first access in this memory system 4 clocks.

The other value that must be accounted for is RAS precharge, the value that RAS is de-asserted before the next RAS access. This value is 50 ns in 80-ns memory, which was 1 clock at 16 MHz but is now 2 clocks at 30 MHz. Both of these requirements add two more states to the master control PAL device and thereby necessitate a larger number of outputs than was in the previous design. This is accomplished by changing the

Publication# 18478 Rev. A Amendment /0 Issue Date: May 1994

16V8 MSTR\_CON PAL device in the EZ-030 board design to a 22V10. In addition, the RDY term in the EZ-030 board MSTL\_CTL PAL device is moved outside all the PAL devices and put in a simple 74F08 used to OR the two sources of RDY (MEM\_RDY and SERIAL\_RDY) for the processor.

## Change the CAS\_DEC PAL Device

The third design change centers around the memory subsystem. The two banks are common in their RAS generation and address multiplexing, but the CAS generation must take into account the two separate banks as well as the need to be byte-writable on an individual basis. This requires 10 outputs for this function, so the CAS\_DEC PAL device in the EZ-030 board design is now replaced with another 22V10.

These are the needed design changes at a high level; the next section looks at the PAL devices in more detail.

#### THEORY OF OPERATION

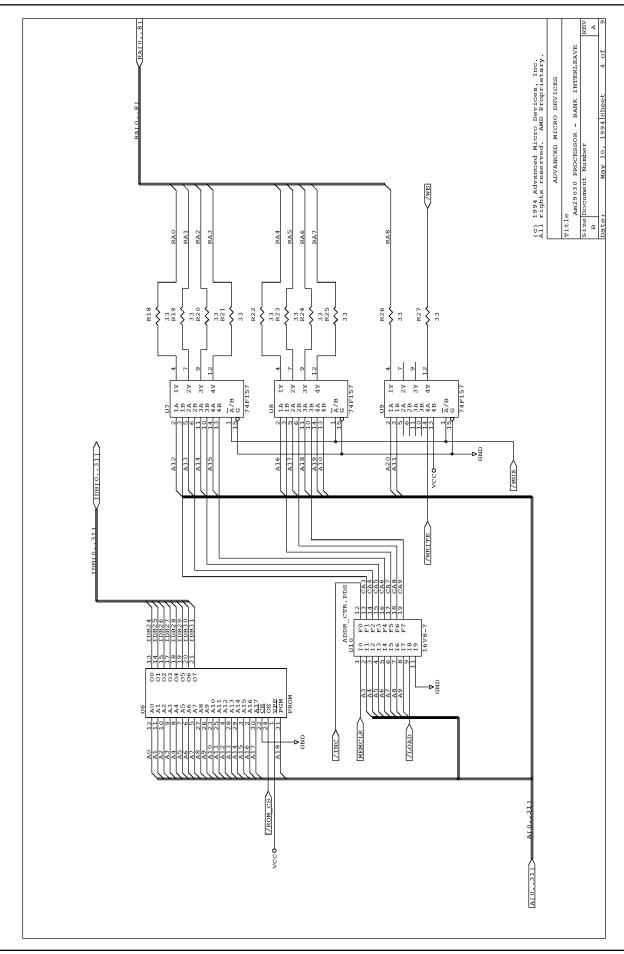

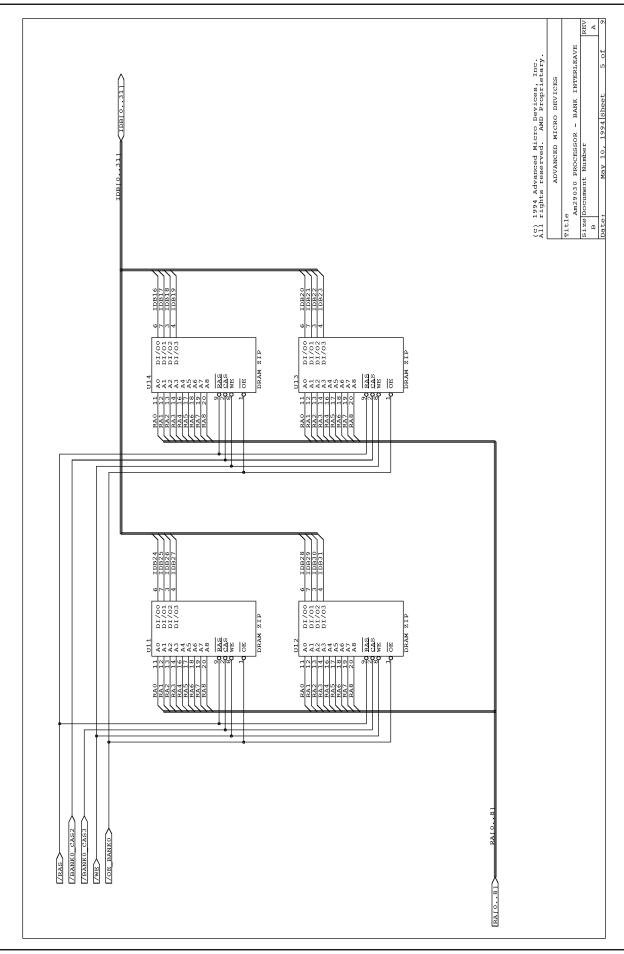

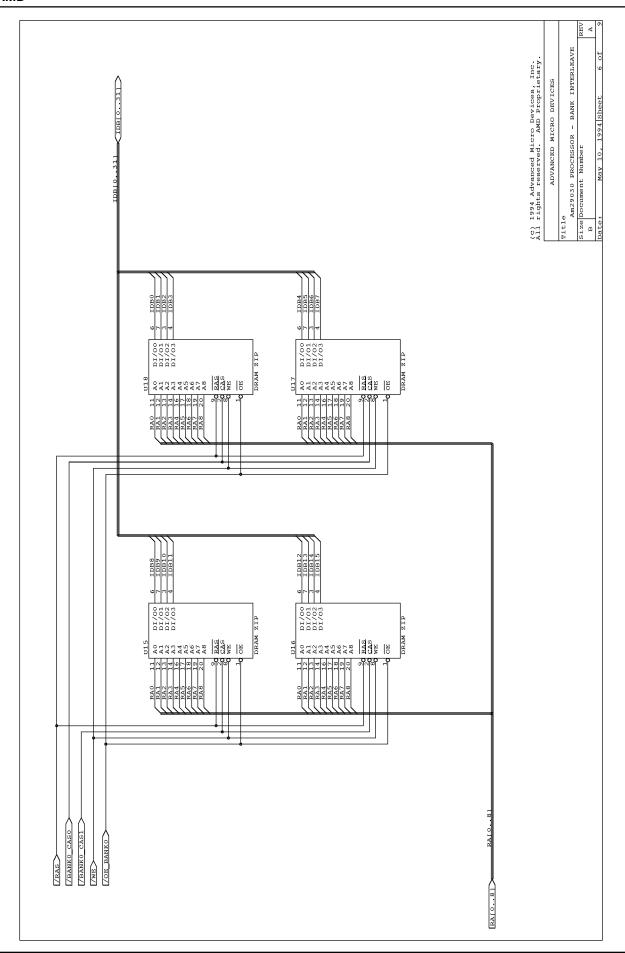

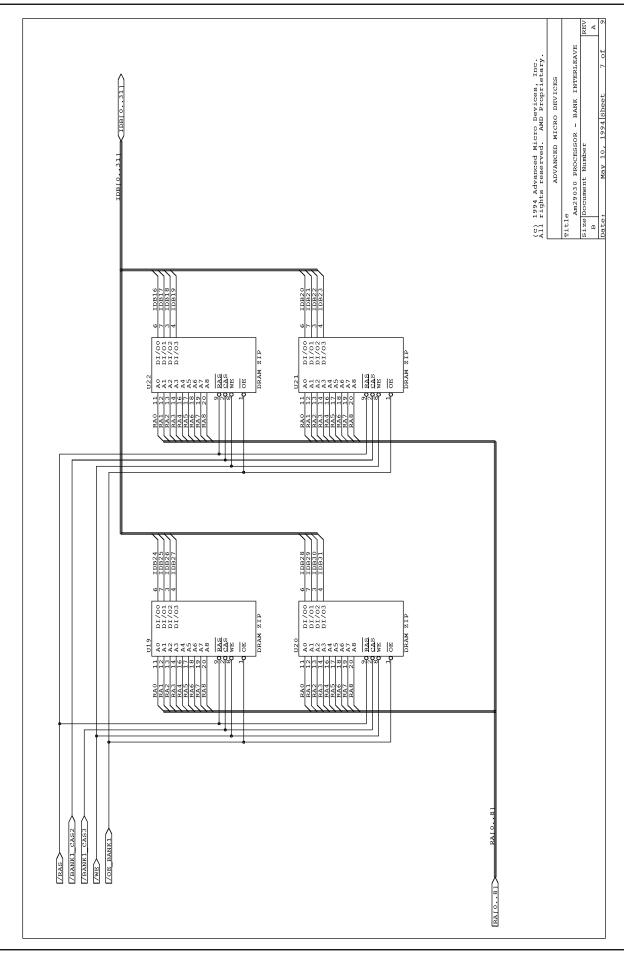

The MSTR CON, CAS DEC, REFRESH, ADD\_CTR PAL devices are discussed in the following sections. The PAL equations referenced are provided in Appendix B at the end of the document. (The SERIAL PAL device is the same as that discussed in the EZ-030 board application note; the SERIAL PAL equations are shown in Appendix B.) Appendix A contains the schematics for the design.

## **MSTR CON PAL Device**

The state machine in the MSTR CON PAL device represents the heart of the bank interleaved memory design. It controls the main memory functions of both the DRAM access and the refresh of the DRAMs, and also provides decoding and timing for the ROM access. This is done in a way that hides the refreshes so they do not impact performance; for example, DRAM refresh can be performed while ROM is being accessed. Additionally, state bits are shared between state machines so that extra flip-flops are not needed. For example, this sharing is done for ROM access because a 3-cycle access on ROM is needed at 30 MHz, while in 16 MHz only 2 cycles are needed. So a simple division by 2 needs to change to a division by 3, which requires one more state bit.

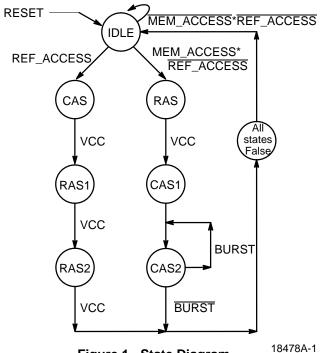

The state machine in Figure 1 shows the normal path of the EZ-030 board design, where IDLE is the state in which the machine is at rest and is ready to arbitrate a decision as to which path is chosen.

A refresh has priority in the arbiter, so a REF\_ACCESS is taken regardless of the state of REQ in the Am29030 processor. MEM\_ACCESS is taken only when there is no REF\_REQ with a REQ, and when the address lines A31=1 and A30=0 are valid. The last state of CAS in the MEM ACCESS holds and MEM RDY is driven True in this state until the BURST signal from the Am29030 processor goes False.

Figure 1. State Diagram

If the BURST signal is False when REQ is asserted at the beginning of an access, this is a single access and the machine goes to the bottom and cycles back around. An extra precharge clock cycle is needed at the end of a memory cycle to ensure that no two accesses are too close. This is accomplished by waiting until all state bits go False before moving to the IDLE state. Once the state machine moves to IDLE, it can re-arbitrate. Because the IDLE cycle occurs before either RAS or CAS can be asserted, this ensures that 2 clock cycles are performed on back-to-back accesses with RAS False, which meets the precharge requirement.

OE\_BANK0 serves as a dual-function signal to the state machine. It is used on MEM ACCESS to enable the even bank and is normally a division by 2 in a burst sequence. However, a new state is needed in REF\_AC-CESS to time the memory cycle so, in a refresh cycle, OE\_BANK0 is used to signal the last state (RAS2) of a refresh cycle. OE\_BANK0 and OE\_BANK\_1 are also used in MEM ACCESS to provide an indication of the last state as well as provide the output enable (OE) multiplexing for the DRAMs.

The remaining signals used for a DRAM access are RAS, INC, and MEM RDY. RAS is a term that is registered to provide the highest speed to the memory interface. RAS has the same timing as MEM\_ACCESS, or is delayed by one clock so that a REF ACCESS can provide the CAS-before-RAS signaling for a refresh.

INC controls the incrementing of the address counter on the Am29030 processor's A9-A3 bits. INC is a registered term for ease of state control. It becomes True in an access that starts with A2=0, as MEM RDY becomes True at the 3-clock cycle from RAS. INC then starts a division by 2 until all accesses have been completed. If A2=1 on the first access, INC becomes True one clock cycle before MEM\_RDY becomes True, so as to increment the CAS address to the next higher bank before the even bank CAS can be asserted.

MEM\_RDY is also a registered term and provides all ready generation for both DRAM and ROM access. In MEM\_ACCESS, MEM\_RDY becomes True once, if BURST from the Am29030 processor is False on the first access; or, if BURST is True on the first access, MEM\_RDY stays True as long as BURST stays True from the Am29030 processor.

ROM access does not use the master state machine but instead uses the MEM\_RDY line to provide one of the clock cycles of access timing. There are, however, three cycles that are needed.

The first cycle is a  $\overline{REQ}$  signal from the Am29030 processor, with A31=0 and A30=0. Because a ROM access is taking place, the state bit INC, which controls the address pre-counter, is not needed for a REF\_ACCESS. So, in the second cycle, INC is set to True. Finally, in the third cycle, MEM\_RDY is set to True. Then both bits are set to False as the Am29030 processor changes the address on the bus for the next access.

Just as in the EZ-030 board design, this modified design carries forth the single ROM for boot-up and monitor code, so the  $\overline{\text{RDN}}$  pin is controlled for all ROM accesses by the ROM\_CS term in the MSTR\_CON PAL device. During reset, this pin is False (high) so this signals the internal logic of the Am29030 processor that a  $\overline{\text{RDN}}$  is 8-bits wide as opposed to 16-bits wide.

## **CAS\_DEC PAL Device**

The CAS\_DEC PAL device has all the CAS signal generation as well as two extra terms: DIV\_CLK and SE-COND\_ACCESS. DIV\_CLK clocks the refresh counter and the I/O control PAL device, which is needed because of the higher clock rate of this design as compared to the EZ-030 board design. This keeps the two PAL devices compatible to their original timing.

SECOND\_ACCESS is used in the CAS pulse generation and controls the INC term in the MSTR\_CON PAL device. It goes True after the first access to DRAM has

taken place and stays True until MEM\_ACCESS goes False.

The CAS pulse generation is the most complicated of the modifications. There are eight CAS lines: one set of four for the even bank and one set of four for the odd bank. Each set of four controls byte-enable access, especially for writes to memory. Reads are always performed 32 bits (one word) at a time. The equations are then essentially copies of each other, with only the corresponding byte enable (WEx) used for writes and OE BANKx used for bank control (see Equation 1).

The equations are divided into three parts. Part 1 is one line [1.a] and supports CAS before RAS refresh. Part 3 is one line [1.h] that controls writes. Writes are simply an AND of the MEM CLK and the controlling OE BANK term and the WEx term that controls that byte. Part 2 is the middle six terms [1.b-1.g] and forms the read pulse shaping. The CAS pulse starts out with SECOND\_AC-CESS False and the OE\_BANK control True [1.b]. CAS is then held True as a regenerative latch [1.c] if it does go True. It is also held True through an entire cycle if SE-COND ACCESS is False and MEM RDY is True [1.d]. When the SECOND\_ACCESS term is True, the next three lines [1.e-1.g] form a pulse that makes CAS for this bank False for half a clock cycle on the opposite bank access [1.e]. This CAS False gets the new address in the CAS address latch on the inside of the DRAMs. Then the next line [1.f] provides a cross term to prevent output glitches while the OE\_BANK term switches, and then the CAS is held True for the entire cycle that its own OE\_BANK is True. All these equations [1.e-1.g] then provide a CAS pulse that is False for half a clock cycle, and True for the rest of the clock cycle and then the next full clock cycle, making the 2 clock-cycle access. Because of the higher clock frequency that provides a half clock cycle of 16.5 ns, no delay line is needed in this design as was needed in the EZ-030 board design. Note also in the PAL equation section that minimization is turned off for all the CAS equations because the cross term is logically redundant (but not from a timing standpoint) and if minimized out would create glitches on the CAS line that would adversely effect the DRAMs.

#### REFRESH PAL Device

The REFRESH PAL device is identical to the one used in the EZ-030 board design and is a 7-bit counter that

| BANKO CASO = REF_ACCESS                                    | [1.a] |

|------------------------------------------------------------|-------|

| + MEM_ACCESS*SECOND_ACCESS*WRITE*OE_BANK0*MEM_RDY*MEMCLK   | [1.b] |

| + MEM_ACCESS*SECOND_ACCESS*WRITE*OE_BANK0*BANK0_CAS0       | [1.c] |

| + MEM_ACCESS*SECOND_ACCESS*WRITE*OE_BANK1*MEM_RDY*MEMCLK   | [1.d] |

| + MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANK0*WRITE          | [1.e] |

| + MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANK1*WRITE*MEMCLK   | [1.f] |

| + MEM_ACCESS*SECOND_ACCESS*MEM_RDY*WRITE*BANK0_CAS0*MEMCLK | [1.g] |

| + MEM_ACCESS*MEM_RDY*OE_BANK0*WRITE*WE0*MEMCLK             | [1.h] |

**Equation 1. CAS\_DEC PAL Equation**

counts off 128 DIV\_CLK before setting REF\_REQ. REF\_REQ is held active until MSTR\_CON acknowledges this request by issuing a REF\_ACCESS. This then resets the REF\_REQ bit. The count of 256 33-ns cycles gives a refresh of 8.45  $\mu s$ , which is an over refresh but accounts for the possibility of an Am29030 processor burst losing a whole cycle count in the REFRESH PAL device.

#### ADDR CTR PAL Device

The last PAL device to examine is the ADDR\_CTR PAL device. This device is a 7-bit counter that is in between the A9–A3 address bits of the Am29030 processor and the 74F157 address multiplexers. This PAL device has two control terms: LOAD and INC. All the bits are registered with the MEM\_CLK, making this PAL device a clocked, loadable, and controllable counter. LOAD is controlled by IDLE of the MSTR\_CON PAL device and when the master state machine is in IDLE, the output registers are constantly being updated by their corresponding address bits. When a MEM\_ACCESS starts, the address is held until MSTR\_CON gives an INC control and then the outputs count up by 1.

## **Additional Considerations**

One hidden caveat in both the original and modified designs is that the write signal passes through the 74F157 multiplexers. This is because refresh has priority over memory accesses, and because 4-Mbyte DRAMs and above have a new test mode such that if write is Low during a CAS before RAS refresh, DRAM is put in a special test mode. By not making MUX True during a REF\_ACCESS and by putting WRITE from the processor into the multiplexer, the problem is not only prevented but the write signal to the DRAM is buffered.

#### TIMING ANALYSIS

The timing analysis is simple in this design. There are four critical paths to examine: the ROM access, the RAS access, the CAS access, and the OE access.

#### **ROM Access Time**

The ROM access is controlled by the processor address valid time, plus the address access time of the ROM, plus the Am29030 processor setup time. The equation is as follows:

T

$$_{\rm clk-q\,29030}$$

+ T  $_{\rm ROM\,access}$  + T  $_{\rm setup\,29030} \leq 3~{\rm MEMCLKs}$

This results in a value of 13 + ROM access +  $9 \le 99$ , making a ROM of access time 77 ns or less acceptable. AMD makes 70-ns EPROMs so that speed is used for this design.

### **RAS Access Time**

RAS access time is given by the following equation:

$$T_{clk-q 22V10-7} + T_{RAS access} + T_{setup 29030} \le 3 MEMCLKs$$

This results in a value of  $5 + 80 + 9 \le 99$ , which is acceptable.

## **CAS Access Time**

CAS access time is given by the following equation:

$$T_{clk-q 22V10-7} + T_{CAS access} + T_{setup 29030} \le 2 MEMCLKs$$

This results in a value of  $5 + 35 + 9 \le 66$ , which is acceptable.

#### **OE Access Time**

The real critical-path item is the OE access time. Its equation is given by the following:

T

$$_{\text{clk-q }22\text{V}10-7}$$

+ T  $_{\text{OE access}}$  + T  $_{\text{setup }29030}$   $\leq$  MEMCLK

This results in a value of  $5 + 20 + 9 \le 33$ , or  $34 \le 33$ . Although the result is off by 1 ns, it can still be used if all of the memory subsystem is kept very close to the processor to minimize transmission line issues, knowing that the worst-case timing is always at high temperature, low voltage, and worst-case parts, simultaneously. This could be guaranteed in a manufacturing environment by running the design at 33 MHz for all system tests and then shipping at 30 MHz as designed.

#### CONCLUSION

Although bank interleaving is not without an attendant cost factor and complexity of design, the design presented in this application note shows how easily an extension to the original EZ-030 board design can be made to bring the speed up to double the original design. The increased complexity turns out to be only one extra PAL device. A delay line from the original design was even eliminated. The performance of this modified design is a 4 clock-cycle first access and single-cycle burst, while the original EZ-030 board design is a 3 clock-cycle first access and single-cycle burst. The extra cost of the design is only the increase in the cost of 7.5-ns PAL devices and the extra memory array, plus the cost of a 33-MHz Am29030 processor as opposed to a 16-MHz Am29030 processor. The performance, while not quite double, comes close in a very compact design.

## **SUGGESTED REFERENCE**

- EZ-030 Demonstration Board Theory of Operation application note, order# 17580, Advanced Micro Devices

- Redesigning the EZ-030 Demonstration Board with a PCI I/O Bus application note, order# 18468, Advanced Micro Devices

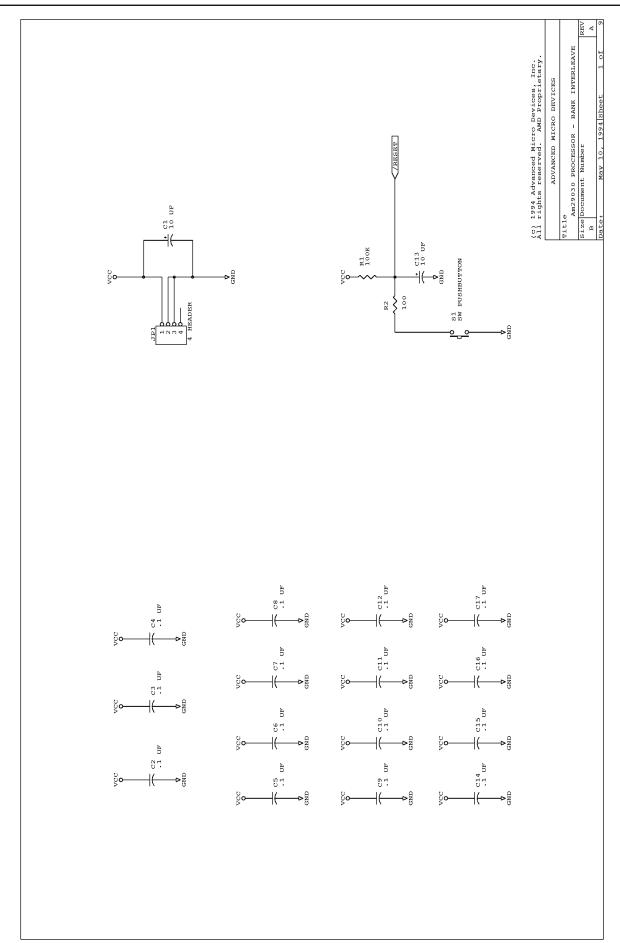

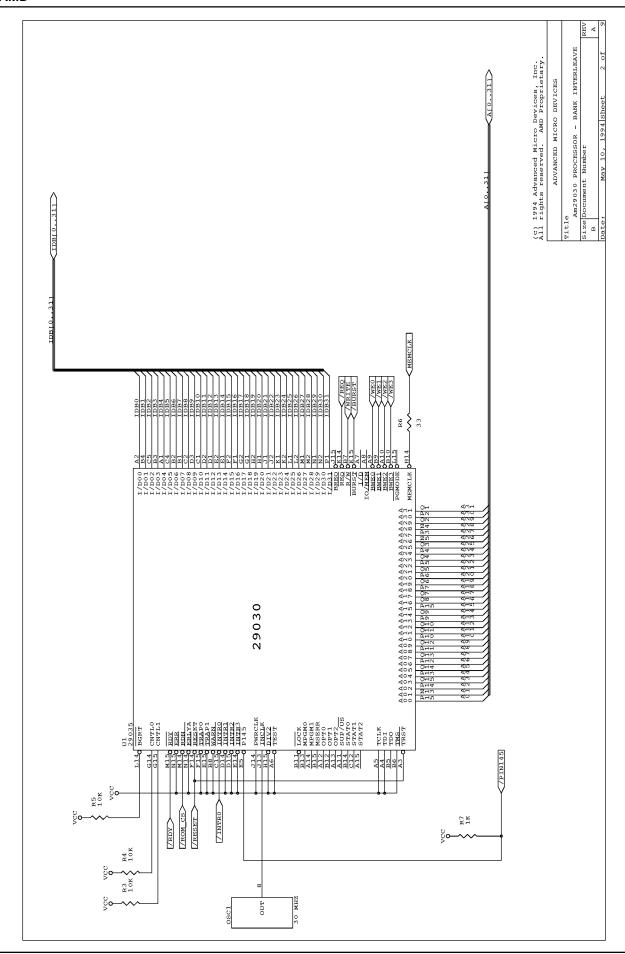

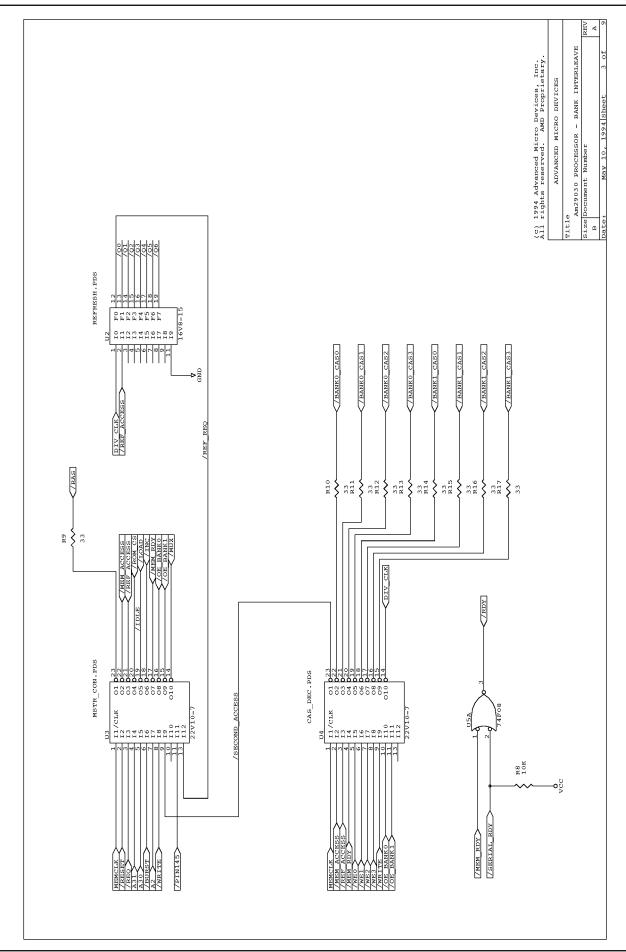

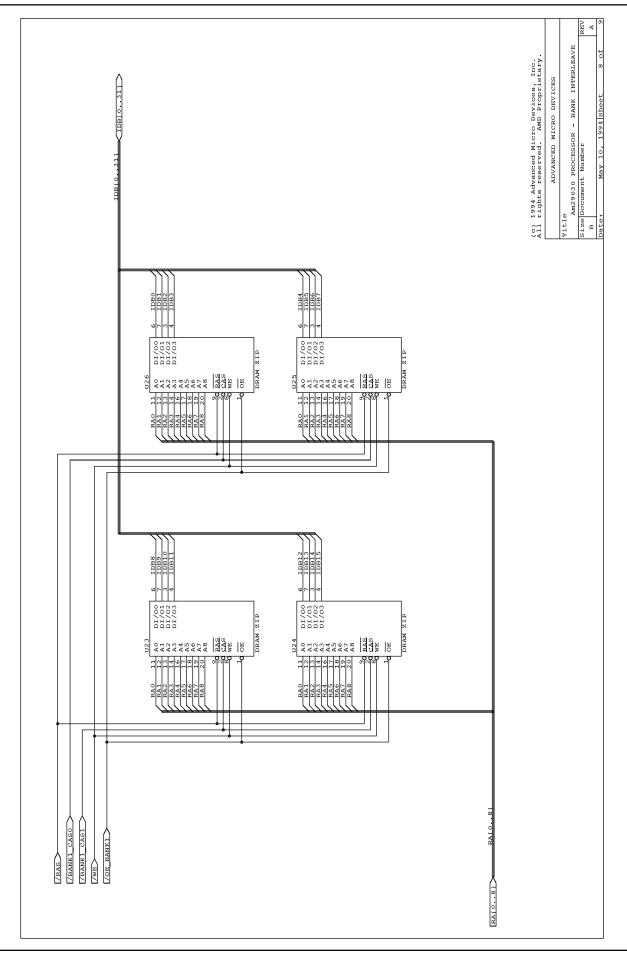

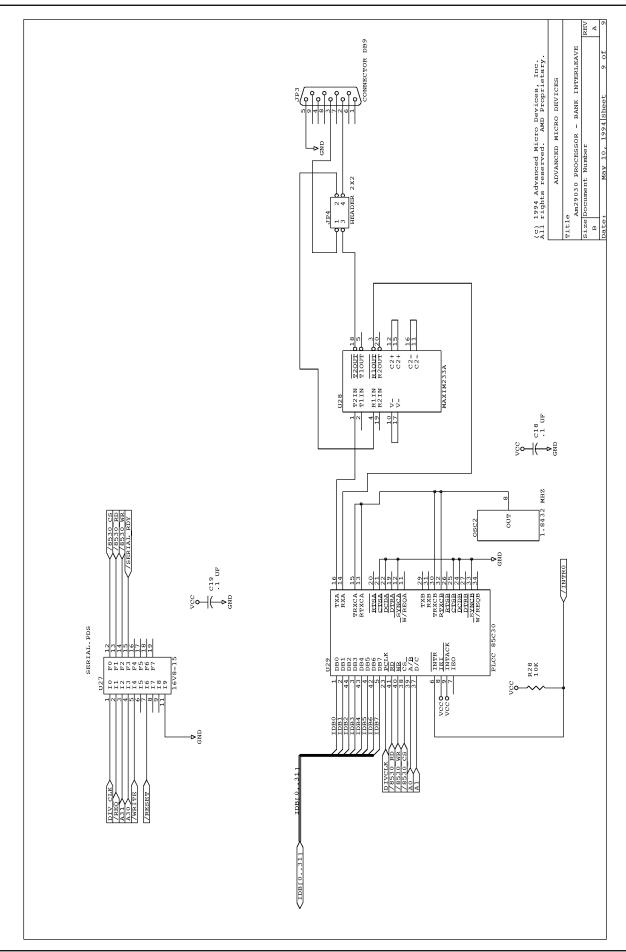

## **Appendix A. Schematics**

The schematics for this design are shown on the pages that follow.

## APPENDIX B. PAL EQUATIONS

This appendix shows the PAL equations in PALASM® software syntax for: the MSTR\_CON equations, the CAS\_DEC equations, the REFRESH equations, the ADDR\_CTR equations, and the SERIAL equations.

## MSTR\_CON PAL EQUATIONS

```

; PALASM Software Design Description

;----- Declaration Segment -----

MEMORY CYCLE GENERATOR FOR 32-BIT INTERLEAVED Am29030 PROCESSOR DESIGN

TITLE

PATTERN MSTR_CON.PDS

REVISION B

AUTHOR DAVID STOENNER

COMPANY AMD

06/22/92

DATE

CHIP U3 PALCE22V10 DEVICE

;-----PIN Declarations -------

MEMCLK

PIN 1

PIN 2

/RESET

PIN 3

/REQ

PIN 4

A31

PIN 5

A30

PIN

6

/BURST

PIN 7

Α2.

PIN 8

/WRITE

PIN 9

/SECOND_ACCESS

PIN

10

NC

PIN 11

/PIN145

PIN 12

GND

PIN 13

/REF_REQ

PIN 14

/MUX

PIN

15

/OE_BANK1

REGISTERED

PIN 16

/OE_BANKO

REGISTERED

PIN 17

/MEM_RDY

REGISTERED

PIN 18

/INC

REGISTERED

PIN 19

/IDLE

REGISTERED

PIN 20

/ROM_CS

/REF_ACCESS

REGISTERED

PIN 21

PIN 22

/MEM_ACCESS

REGISTERED

PIN 23

/RAS

REGISTERED

PIN 24

VCC

;----- Boolean Equation Segment -----

EQUATIONS

ROM_CS = REQ*/A31*/A30*/PIN145 + RESET

IDLE := /IDLE*/MEM_ACCESS*/REF_ACCESS

+ RESET

+ /IDLE*/MEM_ACCESS*/REF_ACCESS*/RAS

+ IDLE*/(REQ*A31*/A30)*/REF_REQ

+ PIN145*/REF REQ

REF ACCESS :=

IDLE*REF REQ*/REF ACCESS

+ REF_ACCESS*REF_REQ

```

+ REF\_ACCESS\*/OE\_BANK0

```

MEM_ACCESS :=

IDLE*REQ*A31*/A30*/REF_REQ*/MEM_ACCESS*/PIN145

+ MEM ACCESS*/MEM RDY

+ MEM_ACCESS*BURST

REQ*/A31*/A30*INC*/MEM_RDY*/PIN145

MEM_RDY :=

+ MEM_ACCESS*(OE_BANK0 + OE_BANK1)*/MEM_RDY

+ MEM_ACCESS*MEM_RDY*BURST

RAS :=

IDLE*REQ*A31*/A30*/REF_REQ*/MEM_ACCESS*/PIN145

+ MEM_ACCESS*/MEM_RDY

+ MEM_ACCESS*BURST

+ REF_ACCESS*/RAS

+ REF_ACCESS*RAS*/OE_BANK0

MUX =

MEM ACCESS*RAS*/MEMCLK

+ MEM_ACCESS*RAS*MUX

INC := REQ*/A31*/A30*/INC*/MEM_RDY*/PIN145

+ REQ*/A31*/A30*INC*/MEM_RDY*/PIN145

+ MEM_ACCESS*/WRITE*/SECOND_ACCESS*A2*/INC*BURST

+ MEM_ACCESS*/WRITE*/SECOND_ACCESS*(OE_BANK0 + OE_BANK1)*/A2*BURST*/INC

+ MEM ACCESS*OE BANK1*WRITE*/SECOND ACCESS*A2*/INC*BURST

+ MEM_ACCESS*MEM_RDY*/INC*BURST

OE_BANKO :=

REF_ACCESS*RAS

+ MEM ACCESS*/A2*/MEM RDY*/OE BANKO

+ MEM_ACCESS*OE_BANK0*/MEM_RDY

+ MEM_ACCESS*OE_BANK1*MEM_RDY*BURST

OE BANK1 :=

MEM ACCESS*A2*/MEM RDY*/OE BANK1

+ MEM_ACCESS*OE_BANK1*/MEM_RDY

+ MEM_ACCESS*OE_BANKO*MEM_RDY*BURST

CAS DEC PAL EQUATIONS

; PALASM Software Design Description

;----- Declaration Segment ------

TITLE RAS AND CAS GENERATOR FOR Am29030 PROCESSOR 32-BIT INTERLEAVE

PATTERN CAS DEC.PDS

REVISION B

AUTHOR DAVID STOENNER

COMPANY AMD

DATE

06/22/92

CHIP U4 PALCE22V10 DEVICE

;----- PIN Declarations ------

MEMCLK

PIN 1

PIN 2

/MEM_ACCESS

PIN 3

/REF_ACCESS

/MEM_RDY

PIN 4

PIN 5

/WEO

PIN 6

/WE1

PIN 7

/WE2

PIN 8

/WE3

PIN 9

/WRITE

```

```

PIN

10

/OE_BANKO

PIN

/OE BANK1

11

PIN 12

GND

PIN 13

NC

PIN 14

DIV_CLK

PIN 15

/BANK1_CAS3

/BANK1_CAS2

PIN 16

PIN 17

/BANK1_CAS1

PIN 18

/BANK1 CAS0

PIN 19

/BANK0_CAS3

PIN 20

/BANKO CAS2

PIN 21

/BANK0_CAS1

/BANKO_CASO

PIN 22

PIN 23

/SECOND_ACCESS

PIN 24

VCC

;----- Boolean Equation Segment -----

EQUATIONS

MINIMIZE_OFF

DIV_CLK := /DIV_CLK

SECOND ACCESS := MEM RDY

+ SECOND_ACCESS*MEM_ACCESS

BANKO_CASO =

REF_ACCESS

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*OE_BANK0*/MEM_RDY*/MEMCLK

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*OE_BANK0*BANK0_CAS0

+ MEM ACCESS*/SECOND ACCESS*/WRITE*OE BANK1*MEM RDY*/MEMCLK

+ MEM ACCESS*SECOND ACCESS*MEM RDY*OE BANKO*/WRITE

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANK1*/WRITE*/MEMCLK

+ MEM ACCESS*SECOND ACCESS*MEM RDY*/WRITE*BANK0 CAS0*MEMCLK

+ MEM_ACCESS*MEM_RDY*OE_BANK0*WRITE*WE0*/MEMCLK

BANKO_CAS1 =

REF_ACCESS

+ MEM ACCESS*/SECOND ACCESS*/WRITE*OE BANKO*/MEM RDY*/MEMCLK

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*OE_BANK0*BANK0_CAS1

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*OE_BANK1*MEM_RDY*/MEMCLK

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANKO*/WRITE

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANK1*/WRITE*/MEMCLK

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*/WRITE*BANKO_CAS1*MEMCLK

+ MEM_ACCESS*MEM_RDY*OE_BANKO*WRITE*WE1*/MEMCLK

BANK0 CAS2 =

REF ACCESS

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*OE_BANKO*/MEM_RDY*/MEMCLK

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*OE_BANKO*BANKO_CAS2

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*OE_BANK1*MEM_RDY*/MEMCLK

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANKO*/WRITE

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANK1*/WRITE*/MEMCLK

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*/WRITE*BANK0_CAS2*MEMCLK

+ MEM_ACCESS*MEM_RDY*OE_BANKO*WRITE*WE2*/MEMCLK

BANKO_CAS3 = REF_ACCESS

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*OE_BANKO*/MEM_RDY*/MEMCLK

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*OE_BANK0*BANK0_CAS3

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*OE_BANK1*MEM_RDY*/MEMCLK

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANKO*/WRITE

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANK1*/WRITE*/MEMCLK

```

```

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*/WRITE*BANK0_CAS3*MEMCLK

+ MEM ACCESS*MEM RDY*OE BANKO*WRITE*WE3*/MEMCLK

BANK1 CAS0 = REF ACCESS

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*(OE_BANK0 + OE_BANK1)*/MEMCLK

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*BANK1_CAS0

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANK1*/WRITE

+ MEM ACCESS*SECOND ACCESS*MEM RDY*OE BANKO*/WRITE*/MEMCLK

+ MEM ACCESS*SECOND ACCESS*MEM RDY*/WRITE*BANK1 CASO*MEMCLK

+ MEM_ACCESS*MEM_RDY*OE_BANK1*WRITE*WE0*/MEMCLK

BANK1_CAS1 = REF_ACCESS

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*(OE_BANK0 + OE_BANK1)*/MEMCLK

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*BANK1_CAS1

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANK1*/WRITE

+ MEM ACCESS*SECOND ACCESS*MEM RDY*OE BANKO*/WRITE*/MEMCLK

+ MEM ACCESS*SECOND ACCESS*MEM RDY*/WRITE*BANK1 CAS1*MEMCLK

+ MEM_ACCESS*MEM_RDY*OE_BANK1*WRITE*WE1*/MEMCLK

REF_ACCESS

BANK1_CAS2 =

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*(OE_BANK0 + OE_BANK1)*/MEMCLK

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*BANK1_CAS2

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANK1*/WRITE

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANKO*/WRITE*/MEMCLK

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*/WRITE*BANK1_CAS2*MEMCLK

+ MEM_ACCESS*MEM_RDY*OE_BANK1*WRITE*WE2*/MEMCLK

BANK1_CAS3 = REF_ACCESS

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*(OE_BANK0 + OE_BANK1)*/MEMCLK

+ MEM_ACCESS*/SECOND_ACCESS*/WRITE*BANK1_CAS3

+ MEM ACCESS*SECOND ACCESS*MEM RDY*OE BANK1*/WRITE

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*OE_BANKO*/WRITE*/MEMCLK

+ MEM_ACCESS*SECOND_ACCESS*MEM_RDY*/WRITE*BANK1_CAS3*MEMCLK

+ MEM_ACCESS*MEM_RDY*OE_BANK1*WRITE*WE3*/MEMCLK

REFRESH PAL EQUATIONS

; PALASM Software Design Description

;----- Declaration Segment ------

REFRESH TIMER FOR Am29030 PROCESSOR

TITLE

PATTERN REFRESH.PDS

REVISION A

AUTHOR DAVID STOENNER

COMPANY AMD

DATE 03/03/92

CHIP U2 PALCE16V8 DEVICE

;-----PIN Declarations ---------

PIN 1

MEMCLK

PIN 2

/REF_ACCESS

PIN 3

NC

PIN 4

NC

PIN 5

NC

NC

PIN 6

PIN 7

NC

PIN 8

```

```

PIN

9

NC

PIN

10

GND

PIN 11

/OE

PIN 12

/REF_REQ

REGISTERED

PIN 13

/Q0

REGISTERED

PIN 14

/Q1

REGISTERED

PIN

15

/Q2

REGISTERED

/Q3

PIN 16

REGISTERED

PIN 17

/04

REGISTERED

PIN 18

/Q5

REGISTERED

PIN 19

REGISTERED

/06

PIN 20

VCC

;----- Boolean Equation Segment -----

EQUATIONS

Q0 := /Q0

Q1 := Q1 :+: Q0

Q2 := Q2 :+: (Q1*Q0)

Q3 := Q3 :+: (Q2*Q1*Q0)

Q4 := Q4 :+: (Q3*Q2*Q1*Q0)

Q5 := Q5 :+: (Q4*Q3*Q2*Q1*Q0)

Q6 := Q6 :+: (Q5*Q4*Q3*Q2*Q1*Q0)

REF_REQ := Q6*Q5*Q4*Q3*Q2*Q1*Q0

+ REF_REQ*/REF_ACCESS

;-----

ADDR_CTR PAL EQUATIONS

; PALASM Software Design Description

;----- Declaration Segment ------

TITLE ADDRESS COUNTER & INCREMENTER FOR 32-BIT BANK INTERLEAVED Am29030 PROCES-

SOR

PATTERN ADDR_CTR.PDS

REVISION A

AUTHOR DAVID STOENNER

COMPANY AMD

DATE

06/15/92

CHIP U10 PALCE16V8 DEVICE

;----- PIN Declarations -------

PIN 1

MEMCLK

PIN 2

Α3

PIN 3

Α4

PIN 4

A5

PIN 5

Αб

PIN 6

Α7

PIN

7

A8

PIN 8

Α9

```

```

PIN 9

/LOAD

PIN 10

GND

PIN 11

/OE

PIN 12

/INC

PIN 13

CA3

REGISTERED

PIN 14

CA4

REGISTERED

PIN 15

CA5

REGISTERED

PIN 16

САб

REGISTERED

PIN 17

CA7

REGISTERED

PIN 18

CA8

REGISTERED

PIN 19

CA9

REGISTERED

PIN 20

VCC

;----- Boolean Equation Segment -----

EQUATIONS

CA3 := INC*/CA3

+ LOAD*A3

CA4 := INC*(CA4 :+: CA3)

+ LOAD*A4

CA5 := INC*(CA5 :+: (CA4*CA3))

+ LOAD*A5

CA6 := INC*(CA6 :+: (CA5*CA4*CA3))

+ LOAD*A6

CA7 := INC*(CA7 :+: (CA6*CA5*CA4*CA3))

+ LOAD*A7

CA8 := INC*(CA8 :+: (CA7*CA6*CA5*CA4*CA3))

+ LOAD*A8

CA9 := INC*(CA9 :+: (CA8*CA7*CA6*CA5*CA4*CA3))

+ LOAD*A9

;-----

SERIAL PAL EQUATIONS

; PALASM Software Design Description

;----- Declaration Segment ------

TITLE 8530 CONTROLLER

PATTERN SERIAL.PDS

REVISION A

AUTHOR DAVID STOENNER

COMPANY AMD

DATE 03/03/1992

CHIP UXX PAL16V8 DEVICE

;----- PIN Declarations ------

PIN 1

CLK

PIN 2

/REQ

PIN 3

A31

```

```

A30

PIN 4

PIN 5

/SIPW

PIN 6

NC

PIN 7

/RESET_IN

PIN 8

NC

PIN 9

NC

PIN 10

GND

PIN 11

/OE

PIN 12

/8530 CS

PIN 13

/8530_RD

PIN 14

/8530_WR

PIN 15

/8530_RDY

PIN 16

/NC1

PIN 17

/NC2

PIN 18

NC

PIN 19

/COM1INT

PIN 20

VCC

;----- Boolean Equation Segment -----

EQUATIONS

8530_{CS} = REQ*A31*A30

8530_RD := 8530_CS*/SIPW*/8530_RD*/8530_RDY

+ 8530_RD*/8530_RDY

+ RESET_IN

8530_WR := 8530_CS*SIPW*/8530_WR*/8530_RDY

+ 8530_WR*/NC1*/8530_RDY

+ 8530_WR*/NC2*/8530_RDY

+ RESET_IN

NC1 := (8530_RD + 8530_WR)*/NC1*/8530_RDY

NC2 := (8530\_RD + 8530\_WR)*(NC1:+:NC2)*/8530\_RDY

8530_{RDY} := NC1*NC2*/8530_{RDY}

```

Copyright © 1994 Advanced Micro Devices, Inc. All rights reserved. 29K and Am29030 are trademarks, and PAL and PALASM are registered trademarks of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.