#### **Philips Components**

| Document No.  | 853–1438              |

|---------------|-----------------------|

| ECN No.       | 99800                 |

| Date of Issue | June 14, 1990         |

| Status        | Product Specification |

| ECL Products  |                       |

#### **FEATURES**

- Typical propagation delay from clock to output: 3.5ns

- ●Typical ECL supply current (–IECL): 110mA

- ●Typical TTL supply current (ITTL): 25mA

- Low logic level of ECL output doubles as a high impedance state

- •ECL output drives 25 Ohm loads

- •4,000 Volt ESD protection for all pins

- Controlled edge rates for quieter bus operation

#### DESCRIPTION

The 100982 is a six-bit, translating transceiver with registers. It allows the

# 100982

# Hex ECL-TTL Translating Transceiver with Registers

exchange of data between a 100K ECL bus and a TTL bus. The A data lines are 100K ECL—compatible and bidirectional. The B data lines are TTL—compatible and bidirectional. The control lines are 100K ECL—compatible.

There are three basic modes of operation for the device: When data flows from A to B, an ECL-to-TTL translation occurs. When data flows from B to A, a TTL-to-ECL translation occurs. Finally, A can be disconnected from B, preventing any data exchange between the ECL and TTL buses.

The 100982 has two storage registers, one for each direction of data flow (A to B, B to A). Data is stored on the rising edge of the clock pulse (CPAB, CPBA), provided that the clock enable (CEAB, CEBA) is Low.

Each 100K ECL output (A side) can drive a load as low as 25 Ohms (i.e. a 50 Ohm bus terminated at each end with 50 Ohms to –2.0V). When an ECL output goes Low, its emitter—follower turns off. As a result, the Low logic level approaches the termination voltage (–2.0V) and represents a high impedance state. A High on the ECL output enable (OEBA) will also cut off the emitter—follower, producing the same high impedance state

The TTL outputs (B side) have three-state capability. A High on the TTL output enable (OEAB) will put the TTL outputs into a high impedance state.

Power may be applied to the VECL and VTTL pins in any order.

All unused inputs can be left open due to integrated pull-down resistors.

#### ORDERING INFORMATION

| DESCRIPTION | ORDER CODE |

|-------------|------------|

| 28-Pin PLCC | 100982A    |

100982

## **PIN DESCRIPTION**

| PINS                            | DESCRIPTION                                                   |

|---------------------------------|---------------------------------------------------------------|

| $A_0 - A_5$                     | Bidirectional data lines (100K ECL compatible)                |

| B <sub>0</sub> - B <sub>5</sub> | Bidirectional data lines (TTL compatible)                     |

| OEAB                            | B output enable (100K ECL compatible)                         |

| OEBA                            | A output enable (100K ECL compatible)                         |

| CPAB                            | Clock pulse input for A-to-B data flow (100K ECL compatible)  |

| CPBA                            | Clock pulse input for B-to-A data flow (100K ECL compatible)  |

| CEAB                            | Clock enable input for A-to-B data flow (100K ECL compatible) |

| CEBA                            | Clock enable input for B-to-A data flow (100K ECL compatible) |

| VECL                            | ECL supply voltage                                            |

| VTTL                            | TTL supply voltage                                            |

| GNDECL <sub>1</sub>             | Ground for ECL internal logic and reference generator         |

| GNDECL <sub>2</sub>             | Ground for ECL outputs                                        |

| GNDTTL                          | TTL ground                                                    |

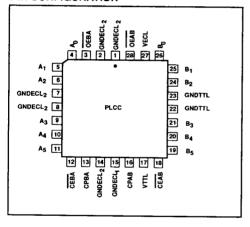

## **PIN CONFIGURATION**

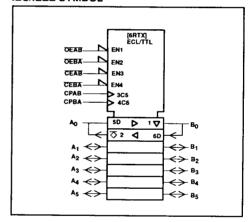

## **IEC/IEEE SYMBOL**

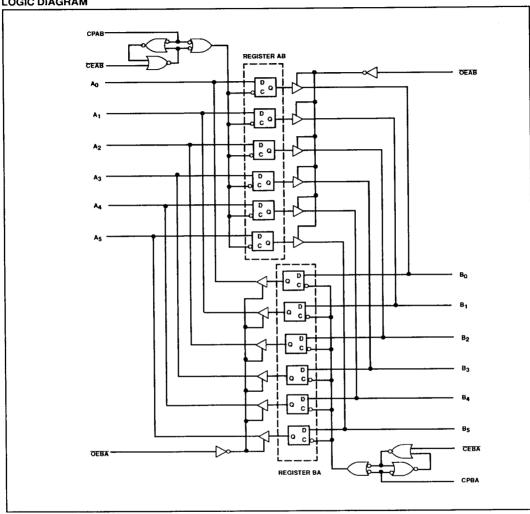

## **LOGIC DIAGRAM**

NOTE:

Pins B<sub>0</sub> through B<sub>5</sub> are TTL-compatible. Pins CPAB, CPBA, CEAB, CEBA, OEAB, OEBA, and A<sub>0</sub> through A<sub>5</sub> are ECL-compatible.

100982

#### **FUNCTION TABLE**

| ENA  | BLES | CLOCK    | INPUT | REGISTER | OUTPUT         | OPERATING MODE                                               |

|------|------|----------|-------|----------|----------------|--------------------------------------------------------------|

| OEAB | CEAB | CPAB     | An    | AB       | B <sub>n</sub> | A-TO-B DATA PATH (ECL-TO-TTL TRANSLATION)                    |

| OEBA | CEBA | CPBA     | Bn    | BA       | An             | B-TO-A DATA PATH (TTL-TO-ECL TRANSLATION)                    |

| L    | L    | 1        | L     | L        | L              | Load data into register and present at outputs               |

| L    | L    | 1        | Н     | н        | н              |                                                              |

| L    | L    | <b></b>  | X     | L        | L              |                                                              |

| L    | L    | <b>1</b> | X     | н        | н              | Hold data in register and present at outputs                 |

| L    | Н    | X        | х     | Ĺ        | L              |                                                              |

| L    | Н    | Х        | X     | Н        | Н              |                                                              |

| н    | L    | 1        | L     | L        | Z              | Load data into register with outputs in high impedance state |

| Н    | Ļ    | <b>1</b> | н     | Н        | Z              | - , , , ,                                                    |

| Н    | L    | <b></b>  | ×     | NC       | Z              | Hold data in register with outputs in high impedance state   |

| H    | Н    | ×        | x     | NC       | z              | - , , , ,                                                    |

#### NOTES:

H = High voltage level

L = Low voltage level

X = Don't care

NC = No change

= High impedance state

- Low-to-High transition 1

- No Low-to-High transition

Any combination of A-to-B and B-to-A operations may be carried out concurrently, provided that no signal is driven into an active (enabled)

output.

# ABSOLUTE MAXIMUM RATINGS FOR ECL- COMPATIBLE LINES GNDECL, =GNDECL, =GNDTTL =ground

T<sub>A</sub>=0°C to +85°C unless otherwise specified

| SYMBOL          | PARAMETER LIMITS                                                        |              | UNIT |

|-----------------|-------------------------------------------------------------------------|--------------|------|

| VECL            | ECL supply voltage range                                                | -7.0 to +0.5 | V    |

| V <sub>IN</sub> | Input voltage (V <sub>IN</sub> should never be more negative than VECL) | VECL to +0.5 | V    |

| ю               | Output source current (continuous)                                      | -100         | mA   |

#### NOTE:

# ABSOLUTE MAXIMUM RATINGS FOR TTL-COMPATIBLE LINES GNDECL1 = GNDECL2 = GNDTTL = ground,

T<sub>A</sub> =0°C to +85°C unless otherwise specified.

| 01/110           | T                                       | <del></del>  |      |

|------------------|-----------------------------------------|--------------|------|

| SYMBOL           | PARAMETER                               | LIMITS       | UNIT |

| VTTL             | TTL supply voltage range                | -0.5 to +7.0 | v    |

| V <sub>IN</sub>  | Input voltage                           | -0.5 to VTTL | V    |

| IIN              | Input current                           | -30 to +5.0  | mA   |

| V <sub>OUT</sub> | Voltage applied to output in High state | −0.5 to VTTL | V    |

| lout             | Current applied to output in Low state  | +96          | mA   |

| Ts               | Storage temperature range               | -65 to +150  | °C   |

| Tj               | Maximum junction temperature            | +150         | °c   |

582

Operation beyond the limits set forth in this table may impair the useful life of the device.

Operation beyond the limits set forth in this table may impair the useful life of the device.

100982

#### DC OPERATING CONDITIONS FOR ECL-COMPATIBLE LINES

|                                                     |                                                                       | TEST         |           | LIMITS |       |      |  |

|-----------------------------------------------------|-----------------------------------------------------------------------|--------------|-----------|--------|-------|------|--|

| SYMBOL GNDECL <sub>1</sub> GNDECL <sub>2</sub> VECL | PARAMETER                                                             | CONDITION    | MIN. NOM. |        | MAX.  | TINU |  |

| GNDECL <sub>1</sub>                                 | Ground for ECL internal logic and reference generator                 |              | 0         | 0      | 0     | V    |  |

| GNDECL <sub>2</sub>                                 | Ground for ECL outputs                                                |              | 0         | 0      | 0     | V    |  |

| VECL                                                | ECL supply voltage                                                    |              | -4.8      | -4.5   | -4.2  | V    |  |

| VECL                                                | ECL supply voltage when operating with the 10K or the 10KH ECL family |              | -5.7      |        |       | ٧    |  |

|                                                     |                                                                       | VECL = -4.2V | -1150     |        |       |      |  |

| VECL                                                | High level input voltage                                              | VECL = -4.5V | -1165     | 1      | -880  | m∨   |  |

|                                                     |                                                                       | VECL = -4.8V | -1165     | 1      |       | 1    |  |

|                                                     |                                                                       | VECL = -4.2V |           |        | -1475 | m۷   |  |

| V <sub>IL</sub>                                     | Low level input voltage                                               | VECL = -4.5V | -1810     |        | -1475 | m۷   |  |

| -                                                   |                                                                       | VECL = -4.8V | 1         |        | -1490 | mV   |  |

NOTE:

When operating at other than the specified VECL voltages (-4.2V, -4.5V, -4.8V), the DC and AC electrical characteristics will vary slightly from their specified values.

#### DC OPERATING CONDITIONS FOR TTL-COMPATIBLE LINES

| SYMBOL           | PARAMETER                           | MIN. | NOM. | MAX. | UNIT |

|------------------|-------------------------------------|------|------|------|------|

| GNDTTL           | TTL ground                          | 0    | 0    | 0    | V    |

| VTTL             | TTL supply voltage                  | +4.5 | +5.0 | +5.5 | V    |

| V <sub>iH</sub>  | High level input voltage            | +2.0 |      | 1    | V    |

| VIL              | Low level input voltage             |      |      | +0.8 | V    |

| -l <sub>OH</sub> | High level output current           |      |      | 15   | mA   |

| loL              | Low level output current            |      |      | 48   | mA   |

| TA               | Operating ambient temperature range | 0    | +25  | +85  | °C   |

100982

## DC ELECTRICAL CHARACTERISTICS FOR ECL-COMPATIBLE LINES

$GNDECL_1 = GNDECL_2 = GNDTTL = ground$ , VECL = -4.8V to -4.2V, VTTL = +4.5V to +5.5V,  $T_A = 0$ °C to +85°C unless otherwise specified1.3,4

|                     |                                       |                                          | TEST                                                                                                                                            |                                                                                                                  |       |      |                                              |      |

|---------------------|---------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|------|----------------------------------------------|------|

| SYMBOL              | PARAMETE                              | ER                                       | CONDITIONS <sup>2</sup>                                                                                                                         |                                                                                                                  | MIN.  | TYP. | MAX.                                         | UNIT |

|                     |                                       |                                          | Store High state in register BA.                                                                                                                | VECL = -4.2V                                                                                                     | -1020 |      | -870                                         | mV   |

| V <sub>OH</sub> T I | High level output voltage             |                                          | $A_n \text{ is tested with a 25}\Omega \text{ load} \\ \text{terminated to V}_T = -2.0 \text{V} \pm 0.010 \text{V}.$                            | VECL = -4.5V                                                                                                     | -1025 | -955 | -880                                         | mV   |

|                     |                                       |                                          | OEBA at VILMIN.                                                                                                                                 | VECL = -4.8V                                                                                                     | -1035 |      | -880                                         | mV   |

|                     |                                       |                                          | Store High state in register BA.                                                                                                                | VECL = -4.2V                                                                                                     | -1030 |      |                                              | mV   |

| $V_{OHT}$           | High level output threshold voltage   |                                          | A <sub>n</sub> is tested with a 25 $\Omega$ load terminated to V <sub>T</sub> = -2.0V $\pm$ 0.010V.                                             | VECL = -4.5V                                                                                                     | -1035 |      | -                                            | mV   |

|                     |                                       |                                          | OEBA at V <sub>ILMAX</sub> .                                                                                                                    | VECL = -4.8V                                                                                                     | -1045 |      |                                              | mV   |

| loz                 | Off-state output current <sup>5</sup> |                                          |                                                                                                                                                 | Store High state in register BA. OEBA and OEAB at V <sub>IHMAX</sub> . Apply –2.1V to A <sub>n</sub> under test. |       |      |                                              | μА   |

|                     |                                       | An                                       | A <sub>n</sub> under test at V <sub>IHMAX</sub> , other A <sub>n</sub> at V <sub>IHMAX</sub> .                                                  |                                                                                                                  |       |      | 120                                          | μА   |

| IH                  | High level input current <sup>5</sup> | OEAB, OEBA,<br>CEAB, CEBA,<br>CPAB, CPBA | One control line under test at V <sub>IHMAX</sub> , all other control lines at V <sub>ILMIN</sub> . All A <sub>n</sub> and B <sub>n</sub> open. |                                                                                                                  |       |      | 955 -880<br>-880<br>-880<br>90<br>120<br>140 | μА   |

|                     |                                       | An                                       | One A <sub>n</sub> under test at V <sub>ILMIN</sub> , other A <sub>n</sub> V <sub>IHMAX</sub> . OEBA at V <sub>IHMAX</sub> .                    | at                                                                                                               | 10    |      |                                              | μА   |

|                     | Low level input current <sup>5</sup>  | OEAB, OEBA,<br>CEAB, CEBA,<br>CPAB, CPBA | One control line under test at V <sub>ILMIN</sub> , all other control lines at V <sub>IHMAX</sub> . All A <sub>n</sub> and B <sub>n</sub> open. |                                                                                                                  | 10    |      |                                              | μА   |

| -IECL               | ECL supply current                    |                                          | All A <sub>n</sub> at V <sub>IHMAX</sub> . OEBA at V <sub>IHMAX</sub> .                                                                         |                                                                                                                  | 64    | 110  | 150                                          | mA   |

#### NOTES:

- 1. The specified limits represent the worst case values for the parameter. Since these worst case values normally occur at the supply voltage and temperature extremes, additional noise immunity can be achieved by decreasing the allowable operating condition ranges.

- 2. Conditions for testing shown in the tables are not necessarily worst case. For worst case testing guidelines, refer to DC Testing, Chapter 1, Section 3.

- 3. The specified limits shown in the DC electrical characteristics table can be met only after thermal equilibrium has been established. Thermal equilibrium is established by applying power for at least 2 minutes, with maintaining transverse airflow of 2.5 meters/sec (500 linear feet/min) over the device, mounted either in a test socket or on a printed circuit board. Test voltage values are given in the DC

- The device can function down to VECL = –5.7V, allowing operation with either the 10K or the 10KH family. Correction factors can be used to calculate new DC limits for the extended VECL range. For more information, see Chapter 10, Section 4.

- 5. For bidirectional lines, this parameter includes currents due to output leakage and input pull-down resistors.

100982

#### DC ELECTRICAL CHARACTERISTICS FOR TTL-COMPATIBLE LINES

GNDECL1 = GNDECL2 = GNDTTL = ground, VECL = -4.8V to -4.2V, VTTL = 4.5V to 5.5V, TA = 0°C to +85°C unlles otherwise specified 1.3

| ***              | TEST                                                                 |                                                                                                       |                              |      | LIMITS |      |      |  |

|------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------|------|--------|------|------|--|

| SYMBOL           | PARAMETER                                                            | CONDITIONS <sup>2</sup>                                                                               |                              | MIN. | TYP.   | MAX. | UNIT |  |

| VoH              | High level output voltage                                            | Store High state in register AB.                                                                      | I <sub>OH</sub> = -3mA       | 2.4  |        |      | ٧    |  |

|                  |                                                                      | OEAB at VILMIN                                                                                        | I <sub>OH</sub> = -15mA      | 2.0  |        |      | ٧    |  |

| V <sub>OL</sub>  | Low level output voltage                                             | Store Low state in register AB.                                                                       | I <sub>OL</sub> = +24mA      |      | 0.35   | 0.50 | ٧    |  |

|                  |                                                                      | OEAB at VILMIN.                                                                                       | I <sub>OL</sub> = +48mA      |      | 0.40   | 0.55 | V    |  |

| V <sub>IK</sub>  | Input clamp voltage                                                  | Apply –18mA to B <sub>n</sub> under test with other B <sub>n</sub> open. OEAB at V <sub>IHMAX</sub> . |                              |      | -0.73  |      | V    |  |

| I <sub>1</sub>   | Input current at maximum input voltage4                              | $B_n$ under test at +5.5V, other $B_n$ at $V_{IHMAX}$ . VTTL = +5.5V.                                 |                              |      | 500    | μА   |      |  |

| I <sub>OZH</sub> | Off-state output current,<br>High level voltage applied <sup>5</sup> | Store Low state in register AB. OE VIHMAX. Apply 2.7V to Bn under tes                                 | AB and OEBA at st.           |      |        | 80   | μА   |  |

| lozL             | Off-state output current,<br>Low level voltage applied <sup>6</sup>  | Store High state in register AB. Of VIHMAX. Apply 0.5V to Bn under te                                 | AB and OEBA at st.           |      |        | 40   | μА   |  |

| -los             | Short circuit output current <sup>7</sup>                            | Store High state in register AB. O at ground. OEAB at V <sub>ILMIN</sub> .                            | ne B <sub>n</sub> under test | 60   | 95     | 225  | mA   |  |

| ITTLH            | TTL supply current with outputs High                                 | Store High state in register AB. Of                                                                   |                              | 20   | 30     | mA   |      |  |

| ITTLL            | TTL supply current with outputs Low                                  | Store Low state in register AB. OF                                                                    | AB at V <sub>ILMIN</sub>     |      | 25     | 35   | mA   |  |

| ITTLZ            | TTL supply current with outputs in the high impedance state          | OEAB at V <sub>IHMAX</sub> .                                                                          |                              |      | 30     | 40   | mA   |  |

#### NOTES

- The specified limits represent the worst case values for the parameter. Since these worst case values normally occur at the supply voltage and temperature extremes, additional noise immunity can be achieved by decreasing the allowable operating condition ranges

- Conditions for testing shown in the tables are not necessarily worst case. For worst case testing guidelines, refer to DC Testing, Chapter 1, Section 3.

- 3. The specified limits shown in the DC electrical characteristics table can be met only after thermal equilibrium has been established. Thermal equilibrium is established by applying power for at least 2 minutes, while maintaining transverse airflow of 2.5 meters/sec (500 linear feet/min) over the device, mounted either in a test socket or on a printed circuit board. Test voltage values are given in the DC operating conditions table.

- 4. This parameter includes output leakage current.

- 5. This parameter includes input reverse leakage current.

- 6. This parameter includes forward input current.

- 7. Not more than one output should be shorted at a time. The other outputs should not be loaded. For testing los, the use of a high-speed test apparatus and/or sample-and-hold techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any sequence of parameter tests, log tests should be performed last.

585

100982

# AC ELECTRICAL CHARACTERISTICS FOR TTL-TO-ECL DATA FLOW

PLCC GNDECL<sub>1</sub> = GNDECL<sub>2</sub> = GNDTTL = ground, VECL = -5.7V to -4.2V, VTTL = 4.5V to 5.5V.

|                                          | PARAMETER                                     | TEST CONDITIONS |                      | LIMITS     |                        |            |                        |            |          |  |

|------------------------------------------|-----------------------------------------------|-----------------|----------------------|------------|------------------------|------------|------------------------|------------|----------|--|

| SYMBOL                                   |                                               |                 | T <sub>A</sub> = 0°C |            | T <sub>A</sub> = +25°C |            | T <sub>A</sub> = +85°C |            | TINU     |  |

|                                          |                                               |                 | MIN.                 | MAX.       | MIN.                   | MAX.       | MIN.                   | MAX.       | 1        |  |

| f <sub>MAX</sub>                         | Maximum clock frequency<br>CPBA               | Waveform 1      | 400                  |            | 400                    |            | 400                    |            | MHz      |  |

| t <sub>PZH</sub><br>t <sub>PHZ</sub>     | Propagation delay<br>CPBA to A <sub>n</sub>   | Waveform 1      | 2.0<br>0.5           | 4.5<br>3.0 | 2.0<br>0.5             | 4.5<br>3.0 | 2.0<br>0.5             | 4.5<br>3.0 | ns<br>ns |  |

| t <sub>PZH</sub>                         | Output enable time<br>OEBA to An              | Waveform 3      | 2.0                  | 4.5        | 2.0                    | 4.5        | 2.0                    | 4.5        | ns       |  |

| t <sub>PHZ</sub>                         | Output disable time<br>OEBA to A <sub>n</sub> | Waveform 3      | 0.5                  | 2.5        | 0.5                    | 2.5        | 0.5                    | 2.5        | ns       |  |

| t <sub>TZH</sub><br>t <sub>THZ</sub>     | Transition time for A <sub>n</sub>            | Waveform 1      | 0.5<br>0.5           | 2.5<br>2.5 | 0.5<br>0.5             | 2.5<br>2.5 | 0.5<br>0.5             | 2.5<br>2.5 | ns<br>ns |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup time<br>B <sub>n</sub> to CPBA          | Waveform 1      | 3.5<br>4.0           |            | 3.5<br>4.0             |            | 3.5<br>4.0             |            | ns<br>ns |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time<br>CPBA to B <sub>n</sub>           | Waveform 1      | 0                    |            | 0                      |            | 0                      |            | ns<br>ns |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup time<br>CEBA to CPBA                    | Waveform 2      | 1.0<br>1.5           |            | 1.0<br>1.5             |            | 1.0<br>1.5             |            | ns<br>ns |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time<br>CPBA to CEBA                     | Waveform 2      | 1.0<br>1.0           |            | 1.0<br>1.0             |            | 1.0<br>1.0             |            | ns<br>ns |  |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | Pulse width<br>CPBA                           | Waveform 1      | 1.0<br>1.0           |            | 1.0<br>1.0             |            | 1.0<br>1.0             |            | ns<br>ns |  |

NOTE:

For AC test setup information, see AC Testing, Chapter 2, Section 3.

## AC ELECTRICAL CHARACTERISTICS FOR ECL-TO-TTL DATA FLOW

PLCC GNDECL<sub>1</sub> = GNDECL<sub>2</sub> = GNDTTL = ground, VECL = -5.7V to -4.2V, VTTL = 4.5V to 5.5V.

|                                          |                                               | TEST CONDITIONS | LIMITS           |                      |            |            |                        |            |          |

|------------------------------------------|-----------------------------------------------|-----------------|------------------|----------------------|------------|------------|------------------------|------------|----------|

| SYMBOL                                   | PARAMETER                                     |                 | T <sub>A</sub> = | T <sub>A</sub> = 0°C |            | +25°C      | T <sub>A</sub> = +85°C |            | UNIT     |

|                                          |                                               |                 | MIN.             | MAX.                 | MIN.       | MAX.       | MIN.                   | MAX.       | 1        |

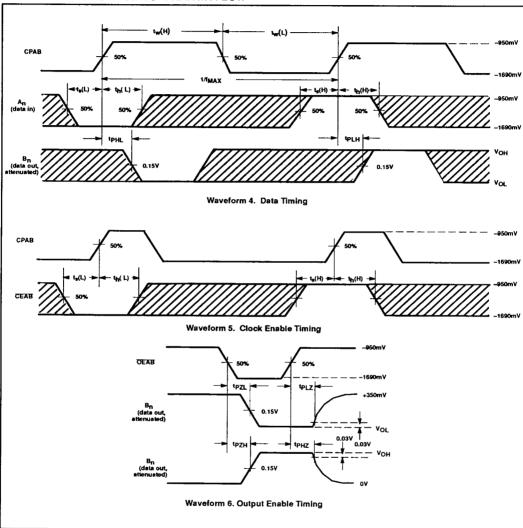

| f <sub>MAX</sub>                         | Maximum clock frequency<br>CPAB               | Waveform 4      | 300              |                      | 300        |            | 300                    |            | MHz      |

| t <sub>PLH</sub><br>t <sub>PHL</sub>     | Propagation delay<br>CPAB to B <sub>n</sub>   | Waveform 4      | 1.5<br>2.0       | 4.0<br>4.5           | 1.5<br>2.0 | 4.0<br>4.5 | 1.5<br>2.0             | 4.0<br>4.5 | ns<br>ns |

| t <sub>PZH</sub><br>t <sub>PZL</sub>     | Output enable time<br>OEAB to B <sub>n</sub>  | Waveform 6      | 1.5<br>2.0       | 4.0<br>5.0           | 1.5<br>2.0 | 4.0<br>5.0 | 1.5<br>2.0             | 4.0<br>5.0 | ns<br>ns |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub>     | Output disable time<br>OEAB to B <sub>n</sub> | Waveform 6      | 2.0<br>4.0       | 5.0<br>7.0           | 2.0<br>4.0 | 5.0<br>7.0 | 2.0<br>4.0             | 5.0<br>7.0 | ns<br>ns |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup time<br>A <sub>n</sub> to CPAB          | Waveform 4      | 1.0<br>1.0       |                      | 1.0<br>1.0 |            | 1.0<br>1.0             |            | ns<br>ns |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time<br>CPAB to A <sub>n</sub>           | Waveform 4      | 1.0              |                      | 1.0<br>1.0 |            | 1.0<br>1.0             |            | ns<br>ns |

| t <sub>s(H)</sub><br>t <sub>s(L)</sub>   | Setup time<br>CEAB to CPAB                    | Waveform 5      | 1.0<br>1.0       |                      | 1.0<br>1.0 |            | 1.0<br>1.0             |            | ns<br>ns |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time<br>CPAB to CEAB                     | Waveform 5      | 1.0<br>1.5       |                      | 1.0<br>1.5 |            | 1.0<br>1.5             |            | ns<br>ns |

| tw(H)<br>tw(L)                           | Pulse width<br>CPAB                           | Waveform 4      | 1.0<br>1.0       |                      | 1.0        |            | 1.0                    |            | ns<br>ns |

NOTE:

For AC test setup information, see AC Testing, Chapter 2, Section 3.

June 14, 1990 586

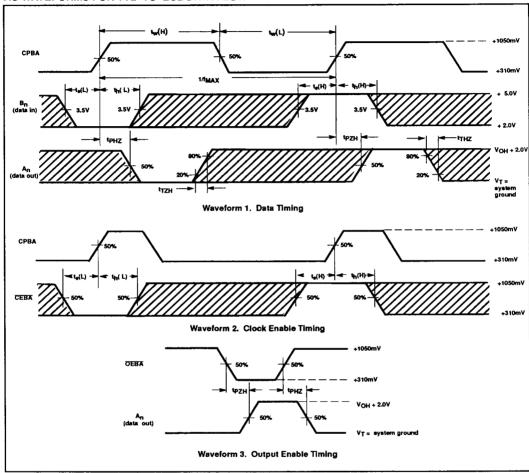

## AC WAVEFORMS FOR TTL-TO-ECL DATA FLOW

NOTE

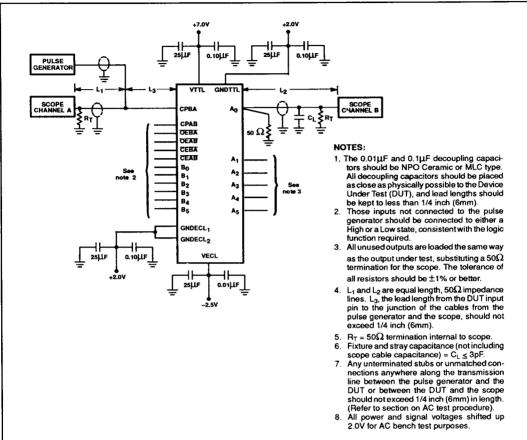

All power and signal voltages shifted up 2.0V for AC bench test purposes.

100982

# AC WAVEFORMS FOR ECL-TO-TTL DATA FLOW

## AC TEST CIRCUIT FOR TTL-TO-ECL DATA FLOW

100982

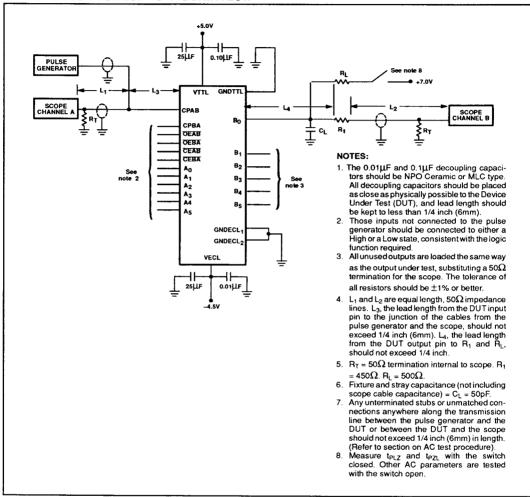

### AC TEST CIRCUIT FOR ECL-TO-TTL DATA FLOW

June 14, 1990 590

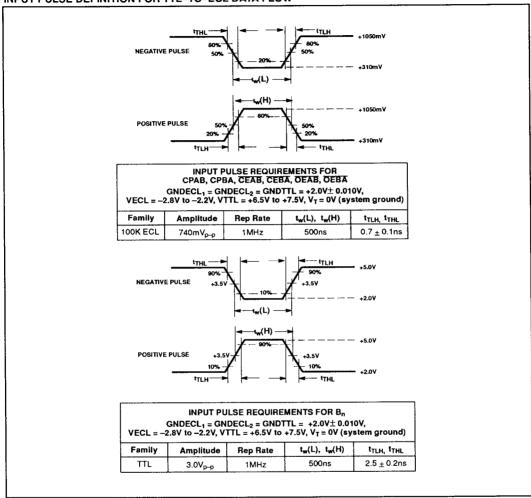

#### INPUT PULSE DEFINITION FOR TTL-TO-ECL DATA FLOW

591

## NOTE:

All power and signal voltages shifted up 2.0V for AC bench test purposes.

100982

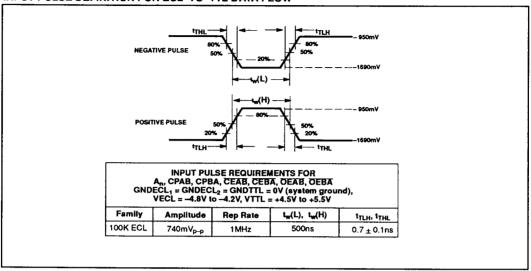

## INPUT PULSE DEFINITION FOR ECL-TO-TTL DATA FLOW

June 14, 1990 592