digital to synchro converter 25VA 16 bit

series 192A300

#### **FEATURES**

- Fully protected output

- Reference powered

- No DC power required

- Microprocessor compatible

- Double buffered digital inputs

- ±4 arc-minute accuracy

- "locked rotor" protection

- Fully isolated operation

- BIT (built-in-test) output

- Drives CT, CDX and TR loads

### **APPLICATIONS**

- Training Simulators

- Fire Control Systems

- Retransmission Systems

- Remote Indicators

#### **GENERAL DATA**

The series 192A300 is a 25VA, 60 or 400Hz synchro driver with a built-in 16 bit digital to synchro converter providing a 4 arc-minute accuracy. The unit requires only reference power and incorporates an internal "pulsating power supply" that reduces internal power dissipation. The 192A300 has a low (0.1%) scale factor variation with angle that further helps reduce internal power when driving TR loads. The unit is fully isolated, inputs, outputs and reference.

The 25VA output makes the 192A300 ideal for driving single or multiple active Torque Receivers or passive Control Differential Transmitters and Control Transformers. A built-in "kick" circuit is incorporated to prevent Torque Receiver hang-ups. The output stage is fully protected, including current limiting, short circuit protection, thermal cut-off and transient suppression making the unit virtually indestructible.

The logic interface includes a built-in-test (BIT) output which continuously monitors for output short circuits, over-current or over-temperature conditions. A disable (DIS) input allows the output amplifier stage to be forced into a high impedance mode. Both this input and output are optically isolated.

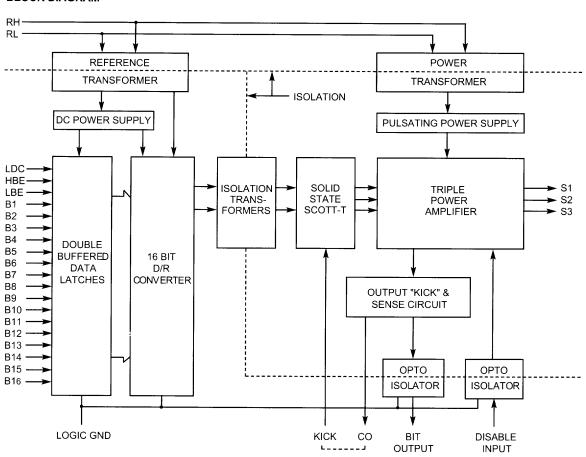

# THEORY OF OPERATION

Operation of the 192A300 is illustrated in the block diagram, page 3. The reference input voltage (RH-RL) is received by both the power and reference transformers. The power transformer provides bias and

pulsating power supply voltages to the output stage; while the reference transformer provides power supply voltages for the input latches and D/R converter and is therefore referenced to "logic ground". The reference transformer also provides an isolated scaled-down reference voltage to the D/R converter.

The digital word representing the input angle is applied to the D/R converter via double buffered transparent latches, that are configured to accept independently-enabled bytes of 8 bits each. These bytes are controlled by the HBE (high byte enable) and LBE (low byte enable) logic inputs. When interfacing to a 16 bit data bus, both HBE and LBE can be enabled simultaneously to accept a 16 bit word. The LDC (load converter) input loads the contents of the high and low byte latches into the D/R converter.

The D/R converter converts the 16 bit digital angle to precision sine and cosine voltages that in turn are applied to isolation transformers and converted to a synchro format. The resultant 3 signals are then applied to the output stage.

The output stage consists of three precision power amplifiers powered from the pulsating power supply. The pulsating power supply greatly reduces the dissipation in the output stage by allowing the output transistors to operate with less average voltage across them as compared to operating from fixed dc supplies. The amplifiers incorporate a fast acting short circuit protection, current limiting, voltage transient protection and a thermal shut-down feature.

| SPECIFICATIONS                                  |                                                                           |  |  |  |

|-------------------------------------------------|---------------------------------------------------------------------------|--|--|--|

| Parameter                                       | Value                                                                     |  |  |  |

| Accuracy¹                                       | ±4.0 arc minutes                                                          |  |  |  |

| Reference Input                                 |                                                                           |  |  |  |

| Voltage <sup>2</sup>                            | 26Vrms ±10%                                                               |  |  |  |

| •                                               | 115Vrms ±10%                                                              |  |  |  |

| Frequency <sup>2</sup>                          | 57 to 63Hz                                                                |  |  |  |

|                                                 | 360 to 440Hz                                                              |  |  |  |

| Input Current                                   |                                                                           |  |  |  |

| 115Vrms                                         |                                                                           |  |  |  |

| No Load                                         | 70mArms max.                                                              |  |  |  |

| 25VA                                            | 500mArms max.                                                             |  |  |  |

| Short Circuit                                   | 1.0Arms max.                                                              |  |  |  |

| 26Vrms                                          | 450 4                                                                     |  |  |  |

| No Load                                         | 150mArms max.                                                             |  |  |  |

| 25VA                                            | 2.5Arms max.<br>4.0Arms max.                                              |  |  |  |

| Short Circuit                                   | 4.UAITIIS IIIdx.                                                          |  |  |  |

| Synchro Output                                  | 44.004                                                                    |  |  |  |

| Voltage                                         | 11.8V or 90.0V L-L                                                        |  |  |  |

| Drive Capability                                | 25VA                                                                      |  |  |  |

| Transformation Ratio                            | . 40/                                                                     |  |  |  |

| Accuracy                                        | ±1%                                                                       |  |  |  |

| Variation with Angle                            | ±0.1%                                                                     |  |  |  |

| Output Settling Time                            |                                                                           |  |  |  |

| 60Hz<br>400Hz                                   | 2.0ms max.                                                                |  |  |  |

|                                                 | 0.5ms max.                                                                |  |  |  |

| Output Quadrature<br>Phase Shift                | 0.25% max.                                                                |  |  |  |

| 60Hz                                            | +7° typ.                                                                  |  |  |  |

| 400Hz                                           | +2° typ.                                                                  |  |  |  |

| Digital Inputs/Outputs                          |                                                                           |  |  |  |

| Logic Type                                      | TTL/CMOS compatible                                                       |  |  |  |

| Data Bits (B1-B16)                              |                                                                           |  |  |  |

| Coding                                          | Positive logic, parallel binary angle                                     |  |  |  |

|                                                 | Bit B1 = MSB, B16 = LSB                                                   |  |  |  |

| Input Current                                   | +50μA, active pull down to ground                                         |  |  |  |

| Input Latch Controls                            |                                                                           |  |  |  |

| Coding                                          | Logic "1" loads, logic "0" holds data                                     |  |  |  |

| HBE                                             | Loads bits B1-B8 into input latches                                       |  |  |  |

| LBE<br>LDC                                      | Loads bits B9-B16 into input latches Loads contents of input latches into |  |  |  |

| LDC                                             | D/R converter                                                             |  |  |  |

| Input Current                                   | -50µA, active pull-up to internal +5V                                     |  |  |  |

| Disable Input                                   | -30µA, active pail-up to internal 131                                     |  |  |  |

| Coding                                          | Logic "0" = synchro outputs enabled                                       |  |  |  |

|                                                 | Logic "1" = synchro outputs disabled                                      |  |  |  |

| Input Current                                   | -1.6mA max.                                                               |  |  |  |

| BIT Output                                      | T.OHIV CHICK.                                                             |  |  |  |

| Coding                                          | Logic "0" = no fault detected                                             |  |  |  |

|                                                 | Logic "1" = fault detected                                                |  |  |  |

| Logic Type                                      | TTL/CMOS compatible                                                       |  |  |  |

| Sink Current                                    | -1.6mA max.                                                               |  |  |  |

| Tomporaturo Danges                              |                                                                           |  |  |  |

| Temperature Ranges Standard                     | 0° to +70°C                                                               |  |  |  |

| Intermediate                                    | -25° to +85°C                                                             |  |  |  |

|                                                 | 20 10 100 0                                                               |  |  |  |

| NOTES:                                          |                                                                           |  |  |  |

| Accuracy applies for:     Accuracy applies for: | age and fraguency range                                                   |  |  |  |

- a. over reference voltage and frequency range.

- b. 10% reference harmonic distortion.

- c. any balanced load from no load to full load.

- d. over operating temperature range.

- 2. See ordering information.

A solid-state temperature sensor is attached to the top plate of the unit. When the power amplifiers temperature reaches 125°C their outputs are forced to a high impedance state. When the temperature drops to a safe level, the output stages are automatically restored to their normal state.

An internal "kick" circuit can be activated by connecting the (CO) output to the (KICK) input. When activated it prevents the possibility that a torque receiver could become locked at 180° from the true angle. It does this by momentarily shifting the electrical angle by 120° if the output is in current limit for more than a few seconds.

A disable input (DIS) allows the output stage to be forced into a high impedance mode for fault isolation or for controlling power-up sequencing in systems using many 192A300 converters.

A built-in-test output (BIT) provides a fault indication if there is an output short circuit or overload, or thermal shut-down that occurs when the case temperature exceeds 125°C. If the output stage is disabled via the (DIS) input the (BIT) output also indicates a fault condition.

## **DRIVING CT AND CDX LOADS**

When driving control transformer (CT) and control differential transmitter (CDX) loads the 192A300 must have enough steady state power capability to drive the Zso of the load. Generally a CT will be lightly loaded and the following equation can be used to calculate their VA requirement:

$$VA = \frac{.866V^2}{Zso}$$

Where: V = primary stator L-L voltage

Zso = stator input impedance with rotor open

In the case of a CDX load, its outputs are usually connected to another load. Therefore, when computing the VA requirement the other load must be taken into account as follows

$$VA = \frac{.866V^2 \times (Zso \times Zso')}{Zso + Zso'}$$

Where: V = CDX primary stator L-L voltage

Zso = CDX input impedance Zso' = load input impedance

### **DRIVING TR LOADS**

The 192A300 is designed to also drive single and multiple Torque Receiver (TR) loads. The D/S converter is specified to drive 11.8V TR loads whose Zss >  $1.0\Omega$  or 90V TR loads whose Zss >  $16\Omega$ .

There are some general considerations when driving TR's with the 192A300. Since both the 192A300 and TR are power sources that are connected together opposing each other, removal of the reference excitation to either will cause very large circulating currents in the stator lines. Theoretically a TR represents an infinite load impedance to the 192A300 output when at "null", TR shaft angle equals 192A300 angle. In actual practice the effective load impedance at "null" will be reduced by the effects of two variables; 1) Transformation ratio differences between the two devices, and 2) Reference to stator phase shift differences between the two devices. These effects give rise to a static VA requirement from the 192A300.

The 192A300 is designed to greatly minimize these effects and the static VA never exceeds 7.5VA when driving TR loads of specified Zss. Even under worse static VA conditions the 192A300 has enough additional VA capability to produce a torque gradient at the TR

In any torque synchro system there is a false null 180° opposed from the true null. If the 192A300 angle and the TR shaft angle are 180° opposed, the 192A300 is called upon to drive the Zss of the TR, causing maximum current and minimum "pull-out torque", the TR shaft could stall at this false null because of current limiting. This condition is known as "locked rotor". To prevent "locked rotor" the 192A300 incorporates a "kick" circuit that senses for over-current conditions. After a few seconds of an over-current condition the 192A300 output is shifted 120° for a few seconds, establishing a torque gradient to drive the TR shaft away from the false null. The "kick" circuit is activated by connecting the (CO) pin to the (KICK) pin.

### **BLOCK DIAGRAM**

# NOTES:

- 1. Dimensions are in inches.

- 2. Tolerances: .XX = ±.02

- $.XXX = \pm .010$

- 3. 400Hz models are 1.42 in. max.

- 4. 60Hz models are 2.18 in. max.

- 5. Units are supplied with mating connector

- 6. 400Hz models weigh 4 lbs. max.

- 7. 60Hz models weight 7 lbs. max.

| PIN | FUNCTION    | PIN | FUNCTION  |

|-----|-------------|-----|-----------|

| 1   | NC          | 26  | NC        |

| 2   | BIT         | 27  | NC        |

| 2 3 | NC          | 28  | NC        |

| 4   | S1 OUT      | 29  | NC        |

| 5   | TP          | 30  | HBE       |

| 6   | KICK        | 31  | LBE       |

| 7   | TP          | 32  | LDC       |

| 8   | TP          | 33  | LOGIC GND |

| 9   | NC          | 34  | NC        |

| 10  | NC          | 35  | BIT 1     |

| 11  | NC          | 36  | BIT 2     |

| 12  | NC          | 37  | BIT 3     |

| 13  | TP          | 38  | BIT 4     |

| 14  | DISABLE     | 39  | BIT 5     |

| 15  | NC          | 40  | BIT 6     |

| 16  | LOGIC GND   | 41  | BIT 7     |

| 17  | S3 OUT      | 42  | BIT 8     |

| 18  | CO          | 43  | BIT 9     |

| 19  | NC          | 44  | BIT 10    |

| 20  | TP          | 45  | BIT 11    |

| 21  | S2 OUT      | 46  | BIT 12    |

| 22  | NC          | 47  | BIT 13    |

| 23  | RH (Ref Hi) | 48  | BIT 14    |

| 24  | RL (Ref Lo) | 49  | BIT 15    |

| 25  | NC          | 50  | BIT 16    |

### NOTES:

- 1. NC means no connection is made to this pin internal to the unit.

- 2. TP means test point intended for factory use only, do not use or connect to this pin.

- 3. Pins 16 and 33 (LOGIC GND) are internally connected.

- 4. Connect "CO" to "KICK" to activate "kick" circuit.

## ORDERING INFORMATION

| 192A   | STATOR  | REFERENCE | REFERENCE |

|--------|---------|-----------|-----------|

| SUFFIX | VOLTAGE | FREQUENCY | VOLTAGE   |

| 301    | 11.8V   | 400HZ     | 26V       |

| 302    | 11.8V   | 400HZ     | 115V      |

| 303    | 90.0V   | 400HZ     | 115V      |

| 304    | 90.0V   | 60HZ      | 115V      |

Standard temperature range is  $0^{\circ}$  to  $+70^{\circ}$ C; add suffix IT to part number for intermediate temperature range (-25° to +85°C).