## Migration from Am29LV640DU to MirrorBit Am29LV640MU

**Application Note**

July 2003

The following document refers to Spansion memory products that are now offered by both Advanced Micro Devices and Fujitsu. Although the document is marked with the name of the company that originally developed the specification, these products will be offered to customers of both AMD and Fujitsu.

#### **Continuity of Specifications**

There is no change to this document as a result of offering the device as a Spansion product. Any changes that have been made are the result of normal documentation improvements and are noted in the document revision summary, where supported. Future routine revisions will occur when appropriate, and changes will be noted in a revision summary.

#### **Continuity of Ordering Part Numbers**

AMD and Fujitsu continue to support existing part numbers beginning with "Am" and "MBM". To order these products, please use only the Ordering Part Numbers listed in this document.

#### For More Information

Please contact your local AMD or Fujitsu sales office for additional information about Spansion memory solutions.

Publication Number 25628 Revision A Amendment 0 Issue Date January 2, 2002

#

### Migration from Am29LV640DU to MirrorBit<sup>™</sup> Am29LV640MU

#### **Application Note**

#### INTRODUCTION

**Note:** This application note assumes that users are familiar with Flash Technology and HW/SW System Design.

AMD's MirrorBit<sup>™</sup> technology offers customers a lowcost Flash Memory solution. MirrorBit technology enables a Flash memory product to hold twice as much data as standard Flash, without compromising device endurance, performance, or reliability.

AMD's MirrorBit Am29LV640MU device is pin-compatible with AMD's Am29LV640DU product. The products are very similar, enabling easy migration. Along with improvements added to the Am29LV640MU, there are a few minor changes between the two products. This application note will focus on these changes and new performance-enhancing features.

#### **Migrate to MirrorBit**

Am29LV640MU products are offered in the same 0.8mm pitch FBGA package and with the same pin out as AMD's Am29LV640DU product. As an extension to the previous product offering, the Am29LV640DU is also available in the 1.0 mm pitch Fortified BGA package to support migration to the 64 Mbit MirrorBit device, the Am29LV640MU. Existing systems using Am29LV640DU can migrate to MirrorBit Am29LV640MU without board redesign. For more information on alternate MirrorBit Packages, refer to the "MirrorBit Packages" application note, publication number 25694.

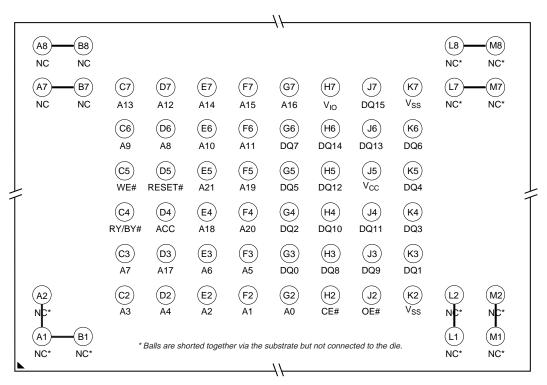

Figure 1. Fine-Pitch BGA Package (63-ball) Connection Diagram

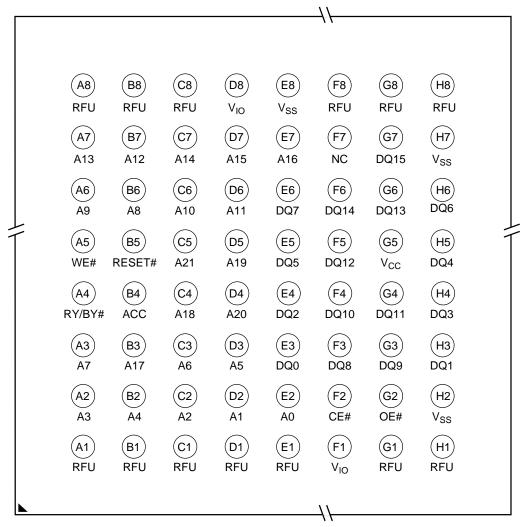

Figure 2. Fortified BGA (1.0 mm Pitch) Connection Diagram

## Device ID Change on AMD MirrorBit Devices

Device Identification (ID) in AMD Flash devices is available either via a software command sequence or through a high voltage hardware method. Device ID is a unique set of readable data values, which distinguishes between different vendors and device type. The main difference between Am29LV640DU and MirrorBit Am29LV640MU is the Am29LV640DU uses a single-byte device code whereas Am29LV640MU uses a three-byte device code.

Tables 1 and 2 show the difference between singlebyte device code and three-byte device code using the high-voltage hardware method.

| Description              | CE# | OE# | WE# | A21–<br>A15 | A14–<br>A10 | A9  | A8–<br>A7 | A6 | A5–A2 | A1 | A0 | DQ15–<br>DQ0 |

|--------------------------|-----|-----|-----|-------------|-------------|-----|-----------|----|-------|----|----|--------------|

| Manufacturer<br>ID: AMD  | L   | L   | Н   | х           | х           | VID | х         | L  | х     | L  | L  | 0001h        |

| Device ID:<br>Am29LV640D | L   | L   | Н   | х           | х           | VID | Х         | L  | х     | L  | н  | 22D7h        |

Table 1. Device ID for Am29LV640DU, High Voltage Method

**Note:**  $V_{ID} = 8.5 - 12.5 V.$

| Description                 | CE#                                   | OE# | WE# | A21–<br>A10 | A9              | A8 | A7 | A6 | A5–<br>A4 | A3 | A2 | A1 | A0 | DQ15-<br>DQ0 |

|-----------------------------|---------------------------------------|-----|-----|-------------|-----------------|----|----|----|-----------|----|----|----|----|--------------|

| Manufacturer<br>ID: AMD     | L                                     | L   | н   | х           | V <sub>ID</sub> | х  | х  | L  | х         | Х  | х  | L  | L  | 0001h        |

| Device ID<br>Read 1         | L                                     | L   | н   | х           | V <sub>ID</sub> | х  | х  | L  | х         | L  | L  | L  | Н  | 227Eh        |

| Device ID<br>Read 2         | L                                     | L   | н   | х           | V <sub>ID</sub> | х  | L  | L  | L         | Н  | Н  | Н  | L  | 2213h        |

| Device ID<br>Read 3         | L                                     | L   | н   | х           | V <sub>ID</sub> | х  | L  | L  | L         | Н  | Н  | Н  | Н  | 2201h        |

| <b>Note:</b> $V_{ID} = 8.5$ | lote: V <sub>ID</sub> = 8.5 – 12.5 V. |     |     |             |                 |    |    |    |           |    |    |    |    |              |

| Table 2. Device ID for Am29LV640MU, High Voltage Me | thod |

|-----------------------------------------------------|------|

|-----------------------------------------------------|------|

The Device ID read command sequence is extended from four to six cycles for MirrorBit devices. In the device code only the lower byte of the data bus is meaningful. All three bytes of the device code must be read to determine the device type. The first byte of the code (7E) only indicates that there are two more Device ID bytes to be read. For more detailed information on Three-Byte Device Code refer to Migration from Single-Byte to Three-Byte Device IDs" application note, publication number 25538.

Tables 3 and 4 illustrate different bus cycles between Am29LV640DU and Am29LV640MU.

#### Table 3. Device ID Command Sequence for Am29LV640DU

|                  | Bus Cycles |      |      |      |      |      |      |       |  |  |

|------------------|------------|------|------|------|------|------|------|-------|--|--|

|                  | Fir        | st   | Sec  | ond  | Thir | d    | Fc   | ourth |  |  |

| Command Sequence | Addr       | Data | Addr | Data | Addr | Data | Addr | Data  |  |  |

| Manufacturer ID  | 555        | AA   | 2AA  | 55   | 555  | 90   | X00  | 0001  |  |  |

| Device ID        | 555        | AA   | 2AA  | 55   | 555  | 90   | X01  | 22D7  |  |  |

| Table 4. Device ID Command Sequence for Am29LV640MU |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Bus Cycles      |      |      |      |      |      |      |      |      |      |      |      |      |

|-----------------|------|------|------|------|------|------|------|------|------|------|------|------|

| Command         | Fi   | rst  | Sec  | ond  | Th   | ird  | Fou  | ırth | Fit  | fth  | Six  | cth  |

| Sequence        | Addr | Data |

| Manufacturer ID | 555  | AA   | 2AA  | 55   | 555  | 90   | X00  | 0001 |      |      |      |      |

| Device ID       | 555  | AA   | 2AA  | 55   | 555  | 90   | X01  | 227E | X0E  | 2213 | X0F  | 2201 |

#### **Difference in Power Consumption**

MirrorBit Am29LV640MU devices have higher power consumption during active read. Active read current is higher due to the new page mode access feature. Erase/Program current is higher because the device will program up to 8 bits at a time instead of the traditional 4 bits. These new features mean that reading, programming, and erase occur in less time. The active power is higher but over a shorter period of time. Table 5 compares power consumption between Am29LV640DU and Am29LV640MU.

| Table 5. Power Consum | ption |

|-----------------------|-------|

|-----------------------|-------|

| Specification                   |                     | LV640MU           | LV640DU     |  |  |

|---------------------------------|---------------------|-------------------|-------------|--|--|

| Current Consumpt                | ion                 |                   |             |  |  |

| Initial Read                    |                     | 30 mA             | 9 mA        |  |  |

| Intra-Page Read                 |                     | 10 mA             | N/A         |  |  |

| Program                         |                     | 50 mA             | 26 mA       |  |  |

| Erase                           |                     | 50 mA             | 26 mA       |  |  |

| Standby                         |                     | 1 µA              | 0.4 µA      |  |  |

| Accelerated                     | ACC pin             | 10 mA             | 5 mA        |  |  |

| Program                         | V <sub>CC</sub> pin | 30 mA             | 15 mA       |  |  |

| Power Consumption               | on                  |                   |             |  |  |

| Random Read                     |                     | 90 mW             | 27 mW       |  |  |

| Intra-Page Read                 |                     | 30 mW             | N/A         |  |  |

| Program                         |                     | 150 mW            | 78 mW       |  |  |

| Erase                           |                     | 150 mW            | 78 mW       |  |  |

| 64 KByte Sector Era             | ise                 | 3 µW              | 1.2 µW      |  |  |

| Accelerated Program             | n (ACC pin)         | 210 mW            | 87 mW       |  |  |

| Energy Consumpti                | on (based o         | n operational tin | ning below) |  |  |

| 4-Word Read                     | Page                | 10.35 nJ          | N/A         |  |  |

| 4-Word Read                     | Random              | 32.4 nJ           | 9.72 nJ     |  |  |

| 16-Word Program                 | Buffer              | 14.16 µJ          | N/A         |  |  |

|                                 | Random              | 307.2 µJ          | 13.73 µJ    |  |  |

| 64 KByte Sector Era             | ase                 | 60 mJ             | 124.8 mJ    |  |  |

| 16-Word Accelerate<br>(ACC pin) | d Program           | 23.52 µJ 9.744 µJ |             |  |  |

| Operation Timing                |                     |                   |             |  |  |

| Initial Read                    |                     | 90 ns             | 90 ns       |  |  |

| Intra-Page Read                 |                     | 25 ns             | N/A         |  |  |

| 1-Word Program                  |                     | 5.9 µs            | 11 µs       |  |  |

| Sector Erase                    |                     | 0.4 s             | 1.6 s       |  |  |

| 1-Word Accelerated              | Program             | 7 µs              | 7 µs        |  |  |

## New Page Read Buffer and Write Buffer Features

Page Read Buffer and Page Write Buffer are two new performance-enhancing features in MirrorBit devices.

The Page Read Buffer feature increases read performance significantly. This mode provides faster read access speed for random locations within a page. The page size of the device is 4 words. Pages are located on 4 word boundaries. The first access within a page requires the full random access time for the device, 90 to 120ns depending on the speed grade. Subsequent accesses that remain within the same page address range, while Chip Select (CE#) remains asserted, have a reduced page access time of 25 to 40 ns. The page read buffer is automatically used by standard read accesses. No special commands or signals are needed. The system only needs to keep CE# active throughout page mode accesses and be aware of the reduced access time for accesses remaining within a page. The system can reduce the number of wait states for within page accesses and take advantage of the increased read performance.

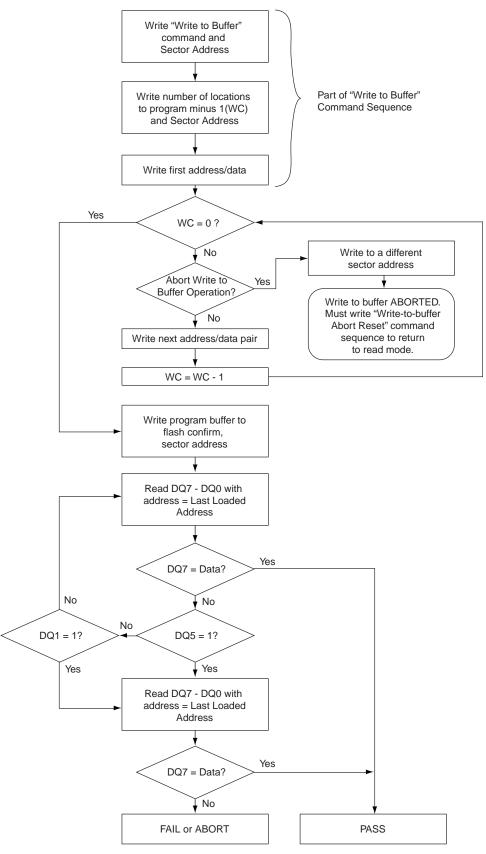

The addition of a Page Write Buffer doubles the programming throughput compared to current Am29LV640DU devices. The Page Write Buffer is a set of registers used to hold several words that are to be programmed as a group. The Page Write Buffer allows the system to write to a maximum of 16 words in one programming operation. The Write Buffer programming command sequence is initiated by first writing two unlock cycles. Below is the flowchart for Write Buffer Programming. See "MirrorBit<sup>TM</sup> Flash Memory Write Buffer Programming and Page Mode Read" application note, publication 25539, for more detailed information.

Figure 3. Write Buffer Programming Flowchart

### AMD 🗖

#### CONCLUSION

MirrorBit technology is a major landmark in Flash memory. MirrorBit devices provide a Flash memory solution at a lower cost, without compromising device performance, endurance, or reliability. Am29LV640MU devices in 0.8 mm FBGA are pin-compatible with AMD's current Am29LV640DU product family of devices in the same package ranging from 8 Mb to 64 Mb. Therefore it is easy to migrate from Am29LV640MU to Am29LV640DU. The addition of the Page Read Buffer and Page Write Buffer increases read performance and reduces the programming time bottleneck that is inherent to very high density Flash memory devices.

MirrorBit products are a superior and cost-competitive solution for designers requiring higher non-volatile memory densities.

#### Trademarks

Copyright © 2002 Advanced Micro Devices, Inc. All rights reserved.

AMD, the AMD logo, and combinations thereof are registered trademarks of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.