# 28C16A

# 16K (2K x 8) CMOS EEPROM

# **FEATURES**

- · Fast Read Access Time-150 ns

- · CMOS Technology for Low Power Dissipation

- 30 mA Active

- 100 μA Standby

- Fast Byte Write Time-200 μs or 1 ms

- · Data Retention >200 years

- High Endurance Minimum 10<sup>4</sup> Erase/Write Cycles

- · Automatic Write Operation

- Internal Control Timer

- Auto-Clear Before Write Operation

- On-Chip Address and Data Latches

- Data polling

- · Chip Clear Operation

- · Enhanced Data Protection

- Vcc Detector

- Pulse Filter

- Write Inhibit

- · Electronic Signature for Device Identification

- · 5-Volt-Only Operation

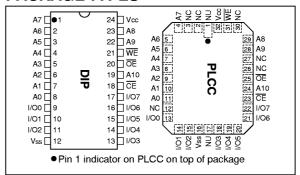

- · Organized 2Kx8 JEDEC Standard Pinout

- · 24-pin Dual-In-Line Package

- · 32-pin PLCC Package

- Available for Extended Temperature Ranges:

- Commercial: 0°C to +70°C

- Industrial: -40°C to +85°C

## **DESCRIPTION**

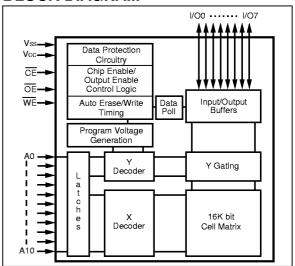

The Microchip Technology Inc. 28C16A is a CMOS 16K non-volatile electrically Erasable PROM. The 28C16A is accessed like a static RAM for the read or write cycles without the need of external components. During a "byte write", the address and data are latched internally, freeing the microprocessor address and data bus for other operations. Following the initiation of write cycle, the device will go to a busy state and automatically clear and write the latched data using an internal control timer. To determine when a write cycle is complete, the 28C16A uses Data polling. Data polling allows the user to read the location last written to when the write operation is complete. CMOS design and processing enables this part to be used in systems where reduced power consumption and reliability are required. A complete family of packages is offered to provide the utmost flexibility in applications.

# **PACKAGE TYPES**

# **BLOCK DIAGRAM**

# 1.0 ELECTRICAL CHARACTERISTICS

# 1.1 MAXIMUM RATINGS\*

Vcc and input voltages w.r.t. Vss ...... -0.6V to + 6.25V Voltage on  $\overline{OE}$  w.r.t. Vss ...... -0.6V to +13.5V Voltage on A9 w.r.t. Vss ...... -0.6V to +13.5V Output Voltage w.r.t. Vss ...... -0.6V to Vcc+0.6V Storage temperature ..... -65°C to +125°C Ambient temp. with power applied ...... -50°C to +95°C

\*Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 1-1: PIN FUNCTION TABLE

| Name        | Function                                    |  |  |  |  |  |  |

|-------------|---------------------------------------------|--|--|--|--|--|--|

| A0 - A10    | Address Inputs                              |  |  |  |  |  |  |

| CE          | Chip Enable                                 |  |  |  |  |  |  |

| ŌĒ          | Output Enable                               |  |  |  |  |  |  |

| WE          | Write Enable                                |  |  |  |  |  |  |

| 1/00 - 1/07 | Data Inputs/Outputs                         |  |  |  |  |  |  |

| Vcc         | +5V Power Supply                            |  |  |  |  |  |  |

| Vss         | Ground                                      |  |  |  |  |  |  |

| NC          | No Connect; No Internal Connection          |  |  |  |  |  |  |

| NU          | Not Used; No External Connection is Allowed |  |  |  |  |  |  |

TABLE 1-2: READ/WRITE OPERATION DC CHARACTERISTICS

| $VCC = +5V \pm 10\%$ $Commercial (C): Tamb = 0^{\circ}C  to  +70^{\circ}C$ $Industrial \qquad (I): Tamb = -40^{\circ}C  to  +85^{\circ}C$ |                                      |                                |             |               |                |                                                                                                                |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------|-------------|---------------|----------------|----------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                                                                                                 | Status                               | Symbol                         | Min         | Max           | Units          | Conditions                                                                                                     |  |

| Input Voltages                                                                                                                            | Logic '1'<br>Logic '0;               | VIH<br>VIL                     | 2.0<br>-0.1 | Vcc+1<br>0.8  | V<br>V         |                                                                                                                |  |

| Input Leakage                                                                                                                             | _                                    | lLi                            | -10         | 10            | μΑ             | VIN = -0.1V to VCC+1                                                                                           |  |

| Input Capacitance                                                                                                                         | _                                    | CIN                            | _           | 10            | pF             | VIN = 0V; Tamb = 25°C;<br>f = 1 MHz                                                                            |  |

| Output Voltages                                                                                                                           | Logic '1'<br>Logic '0'               | Voh<br>Vol                     | 2.4         | 0.45          | V<br>V         | IOH = -400μA<br>IOL = 2.1 mA                                                                                   |  |

| Output Leakage                                                                                                                            | _                                    | llo                            | -10         | 10            | μА             | VOUT = -0.1V to VCC+0.1V                                                                                       |  |

| Output Capacitance                                                                                                                        | _                                    | Соит                           | _           | 12            | pF             | VIN = 0V; Tamb = 25°C;<br>f = 1 MHz                                                                            |  |

| Power Supply Current,<br>Active                                                                                                           | TTL input                            | Icc                            | _           | 30            | mA             | f = 5 MHz (Note 1)<br>VCC = 5.5V;                                                                              |  |

| Power Supply Current,<br>Standby                                                                                                          | TTL input<br>TTL input<br>CMOS input | ICC(S)TTL ICC(S)TTL ICC(S)CMOS | _           | 2<br>3<br>100 | mA<br>mA<br>μA | CE = VIH (0°C to +70°C) CE = VIH (-40°C to +85°C) CE = VCC-0.3 to VCC+1 OE = VCC Other inputs equal VCC or VSS |  |

Note 1: AC power supply current above 5 MHz; 1 mA/MHz.

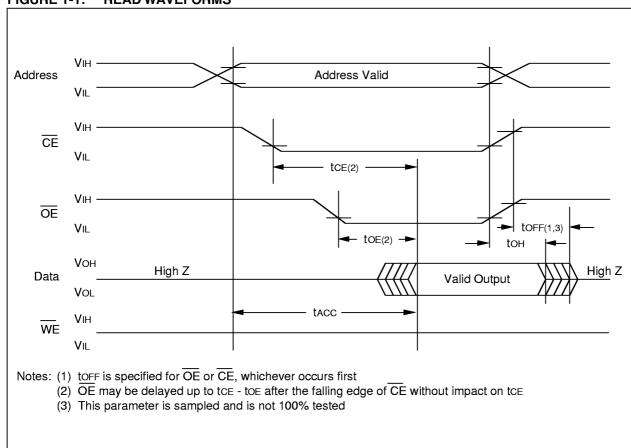

TABLE 1-3: READ OPERATION AC CHARACTERISTICS

AC Testing Waveform: VIH = 2.4V; VIL = 0.45V; VOH = 2.0V; VOI = 0.8V

Output Load: 1 TTL Load + 100pF

Input Rise and Fall Times: 20 ns

Ambient Temperature: Commercial (C): Tamb = 0°C to +70°0°C Industrial (I): Tamb = -40°C to +85°C

| Parameter                                                                                  | Sum  | 28C16A-15 |     | 28C16A-20 |     | 28C16A-25 |     | Units  | Conditions                                |

|--------------------------------------------------------------------------------------------|------|-----------|-----|-----------|-----|-----------|-----|--------|-------------------------------------------|

|                                                                                            | Sym  | Min       | Max | Min       | Max | Min       | Max | Units  | Conditions                                |

| Address to Output Delay                                                                    | tacc | _         | 150 |           | 200 |           | 250 | ns     | OE = CE = VIL                             |

| CE to Output Delay                                                                         | tCE  | _         | 150 | _         | 200 | _         | 250 | ns     | OE = VIL                                  |

| OE to Output Delay                                                                         | toe  | _         | 70  | _         | 80  | _         | 100 | ns     | CE = VIL                                  |

| CE or OE High to Output Float                                                              | toff | 0         | 50  | 0         | 55  | 0         | 70  | ns     |                                           |

| Output Hold from $\overline{\text{CE}}$ or $\overline{\text{OE}}$ , whichever occurs first | tон  | 0         | _   | 0         | _   | 0         | _   | ns     |                                           |

| Endurance                                                                                  | _    | 1M        | _   | 1M        | _   | 1M        | _   | cycles | 25°C, Vcc =<br>5.0V, Block<br>Mode (Note) |

Note: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific application, please consult the Total Endurance Model which can be obtained on our BBS or website.

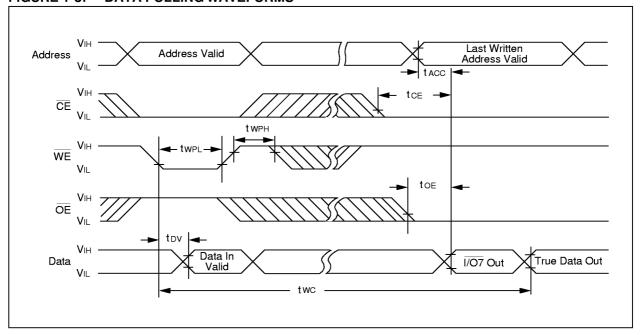

FIGURE 1-1: READ WAVEFORMS

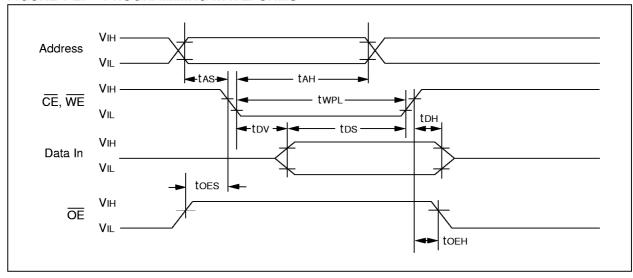

TABLE 1-4: BYTE WRITE AC CHARACTERISTICS

AC Testing Waveform: VIH = 2.4V and VIL = 0.45V; VOH = 2.0V; VOL = 0.8V

Output Load: 1 TTL Load + 100 pF

Input Rise/Fall Times: 20 ns

Ambient Temperature: Commercial (C): Tamb = 0°C to +70°C Industrial (I): Tamb = -40°C to +85°C

| Parameter                  | Symbol | Min | Max  | Units | Remarks        |  |  |

|----------------------------|--------|-----|------|-------|----------------|--|--|

| Address Set-Up Time        | tas    | 10  | _    | ns    |                |  |  |

| Address Hold Time          | tah    | 50  | _    | ns    |                |  |  |

| Data Set-Up Time           | tDS    | 50  | _    | ns    |                |  |  |

| Data Hold Time             | tDH    | 10  | _    | ns    |                |  |  |

| Write Pulse Width          | tWPL   | 100 | _    | ns    | Note 1         |  |  |

| Write Pulse High Time      | twph   | 50  | _    | ns    |                |  |  |

| OE Hold Time               | toeh   | 10  | _    | ns    |                |  |  |

| OE Set-Up Time             | toes   | 10  | _    | ns    |                |  |  |

| Data Valid Time            | tDV    | _   | 1000 | ns    | Note 2         |  |  |

| Write Cycle Time (28C16A)  | twc    | _   | 1    | ms    | 0.5 ms typical |  |  |

| Write Cycle Time (28C16AF) | twc    | _   | 200  | μs    | 100 μs typical |  |  |

Note 1: A write cycle can be initiated be  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$  going low, whichever occurs last. The data is latched on the positive edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever occurs first.

2: Data must be valid within 1000ns max. after a write cycle is initiated and must be stable at least until tDH after the positive edge of WE or CE, whichever occurs first.

FIGURE 1-2: PROGRAMMING WAVEFORMS

FIGURE 1-3: DATA POLLING WAVEFORMS

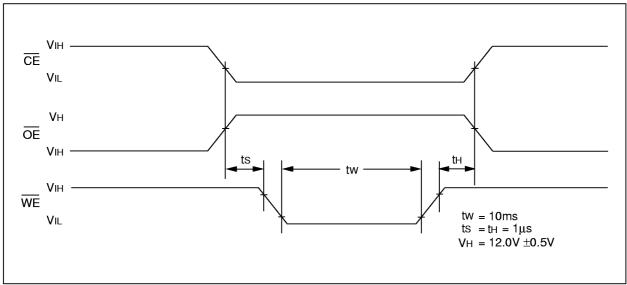

FIGURE 1-4: CHIP CLEAR WAVEFORMS

TABLE 1-5: SUPPLEMENTARY CONTROL

| Mode                                                        | CE  | ŌĒ  | WE  | <b>A</b> 9 | Vcc | I/Oı     |  |

|-------------------------------------------------------------|-----|-----|-----|------------|-----|----------|--|

| Chip Clear                                                  | VIL | VH  | VIL | Х          | Vcc |          |  |

| Extra Row Read                                              | VIL | VIL | VIH | A9 = VH    | Vcc | Data Out |  |

| Extra Row Write                                             | *   | VIH | *   | A9 = VH    | Vcc | Data In  |  |

| Note 1: VH = 12.0V±0.5V * Pulsed per programming waveforms. |     |     |     |            |     |          |  |

# 2.0 DEVICE OPERATION

The Microchip Technology Inc. 28C16A has four basic modes of operation—read, standby, write inhibit, and byte write—as outlined in the following table.

| Operation<br>Mode | CE                            | ŌĒ | WE | I/O    |  |  |  |

|-------------------|-------------------------------|----|----|--------|--|--|--|

| Read              | L                             | L  | Н  | Dout   |  |  |  |

| Standby           | Н                             | Х  | Х  | High Z |  |  |  |

| Write Inhibit     | Н                             | Х  | Х  | High Z |  |  |  |

| Write Inhibit     | Х                             | L  | Х  | High Z |  |  |  |

| Write Inhibit     | Х                             | Х  | Н  | High Z |  |  |  |

| Byte Write        | L                             | Н  | ┙  | DIN    |  |  |  |

| Byte Clear        | Automatic Before Each "Write" |    |    |        |  |  |  |

X = Any TTL level.

## 2.1 Read Mode

The 28C16A has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip enable  $(\overline{CE})$  is the power control and should be used for device selection. Output Enable  $(\overline{OE})$  is the output control and is used to gate data to the output pins independent of device selection. Assuming that addresses are stable, address access time (tACC) is equal to the delay from  $\overline{CE}$  to output (tCE). Data is available at the output toE after the falling edge of  $\overline{OE}$ , assuming that  $\overline{CE}$  has been low and addresses have been stable for at least tACC-tOE.

#### 2.2 Standby Mode

The 28C16A is placed in the standby mode by applying a high signal to the  $\overline{\text{CE}}$  input. When in the standby mode, the outputs are in a high impedance state, independent of the  $\overline{\text{OE}}$  input.

## 2.3 <u>Data Protection</u>

In order to ensure data integrity, especially during critical power-up and power-down transitions, the following enhanced data protection circuits are incorporated:

First, an internal Vcc detect (3.3 volts typical) will inhibit the initiation of non-volatile programming operation when Vcc is less than the Vcc detect circuit trip.

Second, there is a  $\overline{WE}$  filtering circuit that prevents  $\overline{WE}$  pulses of less than 10 ns duration from initiating a write cycle.

Third, holding  $\overline{WE}$  or  $\overline{CE}$  high or  $\overline{OE}$  low, inhibits a write cycle during power-on and power-off (Vcc).

#### 2.4 Write Mode

The 28C16A has a write cycle similar to that of a Static RAM. The write cycle is completely self-timed and initiated by a low going pulse on the  $\overline{WE}$  pin. On the falling edge of  $\overline{WE}$ , the address information is latched. On rising edge, the data and the control pins  $\overline{(CE)}$  and  $\overline{OE}$ ) are latched.

# 2.5 Data Polling

The 28C16A features Data polling to signal the completion of a byte write cycle. During a write cycle, an attempted read of the last byte written results in the data complement of I/O7 (I/O0 to I/O6 are indeterminable). After completion of the write cycle, true data is available. Data polling allows a simple read/compare operation to determine the status of the chip eliminating the need for external hardware.

# 2.6 <u>Electronic Signature for Device</u> Identification

An extra row of 32 bytes of EEPROM memory is available to the user for device identification. By raising A9 to  $12V \pm 0.5V$  and using address locations 7EO to 7FF, the additional bytes can be written to or read from in the same manner as the regular memory array.

## 2.7 Chip Clear

All data may be cleared to 1's in a chip clear cycle by raising  $\overline{OE}$  to 12 volts and bringing the  $\overline{WE}$  and  $\overline{CE}$  low. This procedure clears all data, except for the extra row.

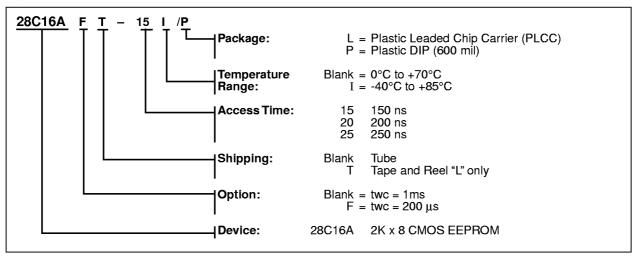

# 28C16A Product Identification System

To order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers, and refer to the factory or the listed sales offices.

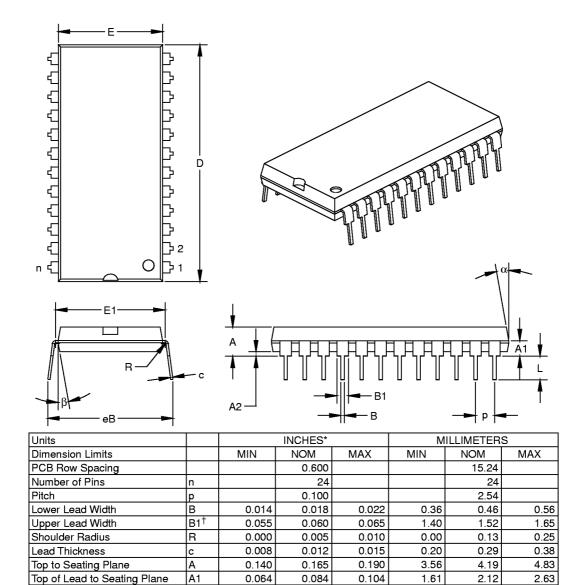

# **Packaging Diagrams and Parameters**

Package Type: K04-081 24-Lead Plastic Dual In-line (P) - 600 mil

0.084

0.025

0.125

1.250

0.550

0.577

0.660

10

10

0.030

0.135

1.255

0.560

0.592

0.690

15

1.61

0.51

2.92

31.62

13.72

14.27

16.00

5

2.12

0.64

3.18

31.75

13.97

14.66

16.76

10

10

2.63

0.76

3.43

31.88

14.22

15.04

17.53

15

15

0.064

0.020

0.115

1.245

0.540

0.562

0.630

5

A2

D‡

Ε‡

E1

lеВ

α

JEDEC equivalent: MS-011 AA

Base to Seating Plane

Molded Package Width

Radius to Radius Width

Mold Draft Angle Bottom

Overall Row Spacing

Mold Draft Angle Top

Tip to Seating Plane

Package Length

<sup>\*</sup> Controlling Parameter.

<sup>†</sup> Dimension "B1" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B1."

Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

# **Packaging Diagrams and Parameters**

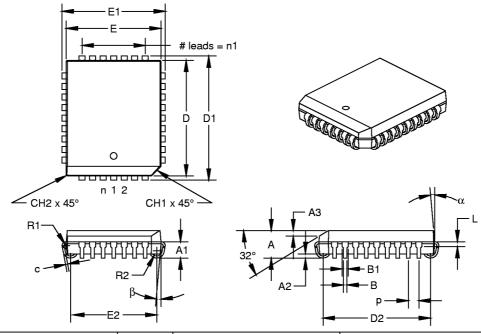

# Package Type: K04-023 32-Lead Plastic Leaded Chip Carrier (L) – Rectangle

| Units                   |                 |       | INCHES* |       | MILLIMETERS |       |       |

|-------------------------|-----------------|-------|---------|-------|-------------|-------|-------|

| Dimension Limits        |                 | MIN   | NOM     | MAX   | MIN         | NOM   | MAX   |

| Number of Pins          | n               |       | 32      |       |             | 32    |       |

| Pitch                   | р               |       | 0.050   |       |             | 1.27  |       |

| Overall Pack. Height    | Α               | 0.127 | 0.131   | 0.135 | 3.23        | 3.33  | 3.43  |

| Shoulder Height         | A1              | 0.060 | 0.078   | 0.095 | 1.52        | 1.97  | 2.41  |

| Standoff                | A2              | 0.015 | 0.020   | 0.025 | 0.38        | 0.51  | 0.64  |

| Side 1 Chamfer Dim.     | A3              | 0.021 | 0.026   | 0.031 | 0.53        | 0.66  | 0.79  |

| Corner Chamfer (1)      | CH1             | 0.035 | 0.045   | 0.055 | 0.89        | 1.14  | 1.40  |

| Corner Chamfer (other)  | CH2             | 0.000 | 0.005   | 0.010 | 0.00        | 0.13  | 0.25  |

| Overall Pack. Width     | E1              | 0.485 | 0.490   | 0.495 | 12.32       | 12.45 | 12.57 |

| Overall Pack. Length    | D1              | 0.585 | 0.590   | 0.595 | 14.86       | 14.99 | 15.11 |

| Molded Pack. Width      | E <sup>‡</sup>  | 0.447 | 0.450   | 0.453 | 11.35       | 11.43 | 11.51 |

| Molded Pack. Length     | D <sup>‡</sup>  | 0.547 | 0.550   | 0.553 | 13.89       | 13.97 | 14.05 |

| Footprint Width         | E2              | 0.380 | 0.410   | 0.440 | 9.65        | 10.41 | 11.18 |

| Footprint Length        | D2              | 0.480 | 0.510   | 0.540 | 12.19       | 12.95 | 13.72 |

| Pins along Width        | n1              |       | 7       |       |             | 7     |       |

| Lead Thickness          | С               | 0.008 | 0.010   | 0.012 | 0.20        | 0.25  | 0.30  |

| Upper Lead Width        | B1 <sup>†</sup> | 0.026 | 0.029   | 0.032 | 0.66        | 0.74  | 0.81  |

| Lower Lead Width        | В               | 0.013 | 0.017   | 0.021 | 0.33        | 0.43  | 0.53  |

| Upper Lead Length       | L               | 0.010 | 0.020   | 0.030 | 0.25        | 0.51  | 0.76  |

| Shoulder Inside Radius  | R1              | 0.003 | 0.008   | 0.013 | 0.08        | 0.20  | 0.33  |

| J-Bend Inside Radius    | R2              | 0.020 | 0.025   | 0.030 | 0.51        | 0.64  | 0.76  |

| Mold Draft Angle Top    | α               | 0     | 5       | 10    | 0           | 5     | 10    |

| Mold Draft Angle Bottom | β               | 0     | 5       | 10    | 0           | 5     | 10    |

<sup>\*</sup> Controlling Parameter.

JEDEC equivalent: MS-016 AE

<sup>†</sup> Dimension "B1" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B1."

<sup>&</sup>lt;sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."