# 497AE and 1215E Boundary-Scan Master 2 Advanced Operational Mode

#### **Features**

- The BSM2 is available in 2 versions:

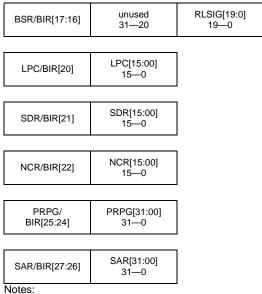

- The 497AE is available in a 28-pin SOJ package

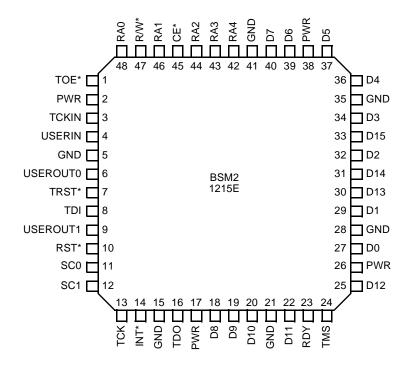

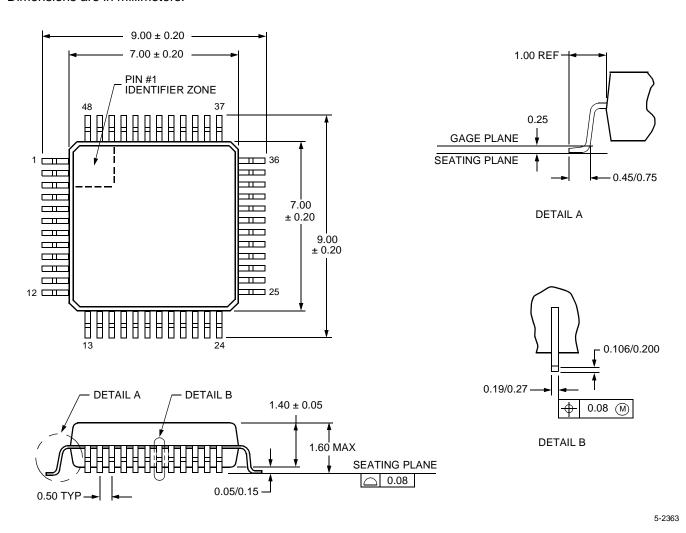

- The 1215E device is available in a 48-pin TQFP package

- The 497AE and 1215E differ in the following capabilities

- 497AE has an 8-bit data-bus and no user I/O signals

- 1215E has a 16-bit data-bus and 3 user I/O signals

- Selectable between two operational modes:

- 497AA compatibility

- Advanced Operational Mode (497AE)

- 3.3 V power supply, but fully 5 V (TTL) tolerant for all inputs and outputs

- Dedicated 8 kbits test data in (TDI) and test data out (TDO) buffers; FIFO or fully addressable

- Simple and flexible host interface options:

- 497AE, synchronous or asynchronous 8-bit data bus

- 1215E, 16-bit asynchronous data bus for maximum throughput

- Self-timing interface to a microprocessor/microcontroller

- Automatic test mode select (TMS) sequence generation

- Programmable test clock (TCK) generator with gated TCK mode

- Provides test reset (TRST\*) optional TAP signal

- External pin control to 3-state test access port (TAP) signals (1215E)

- Conflict-free automatic test pattern generator (ATPG)

- 32-bit signature analysis register (SAR) with response masking for repeatable signatures

- TCK output frequency of 65 MHz

- Maskable processor interrupts; no lockup condition

- Built-in self-test for >95% fault coverage

- Support protocols for multidrop backplane test configurations, such as TI's<sup>1</sup> addressable scan port protocol

- Provides retiming (pipeline) delays of up to 13 TCK cycles to correct skewing

- One general-purpose input, two general-purpose outputs. Outputs can be programmed for use as DMA control signals (1215E device only).

#### **Description**

The Agere Systems Inc. 497AE/1215E Boundary-Scan Master 2 (BSM2) communicates with a generic processor in parallel and controls the test and diagnosis (T&D) of a unit under test (UUT), which could be a device, board, or system, based on the ANSI/ IEEE<sup>2</sup> standard 1149.1-1990 TAP and Boundary-Scan (B-S) Architecture. It serializes test vectors. delivers them to the UUT using the standard protocol, and stores the UUT response as raw data or as a signature. An ATPG generates four common test sequences for interconnect test, cluster test, etc. The device also solves the potential problems of bus conflict and nonrepeatable board-level signatures associated with the B/S architecture. Finally, the BSM2 provides support for edge-connector/backplane test and system test and diagnosis.

The BSM2 comes in two package sizes. The 497AE is a 3.3 V, 28-pin SOJ package that provides both software and hardware backward compatibility to the 497AA BSM. The 1215E is a 3.3 V, 48-pin TQFP package with a 16-bit data bus and direct register access.

#### **Manual Description**

This manual describes the advanced operational modes of the 497AE and 1215E devices. The 1215E device offers higher throughput, using a 16-bit databus, and 3 user I/O signals. For additional information, contact your Agere Account Manager.

- \* Asterisk on any pin name indicates active-low.

- 1. TI is a registered trademark of Texas Instruments Inc.

- 2. *IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

#### **Table of Contents**

| Contents                                                                                             | Page |

|------------------------------------------------------------------------------------------------------|------|

| Features                                                                                             |      |

| Description                                                                                          | 1    |

| Manual Description                                                                                   | 1    |

| Introduction                                                                                         |      |

| Conventions                                                                                          | 5    |

| The BSM2                                                                                             |      |

| Architecture of the BSM2                                                                             | 7    |

| TAP, Power, and Ground Pins                                                                          | 7    |

| BSM_MD* (497AE only)                                                                                 | 7    |

| SYNC_HIF*                                                                                            | 7    |

| Processor Interface                                                                                  |      |

| Device Controller                                                                                    |      |

| Test Data Memories (FIFOs)                                                                           |      |

| User-Definable I/O (1215E Only)                                                                      |      |

| TCK Generator and Gating                                                                             |      |

| Automatic TMS Generator                                                                              |      |

| TAP State Tracker                                                                                    |      |

| Interrupt Control                                                                                    |      |

| Asynchronous and Synchronous Interface Modes                                                         |      |

| Asynchronous Operation (497AE and 1215E)                                                             |      |

| Synchronous Operation (497AE only)                                                                   |      |

| The BSM2 Scan Process                                                                                |      |

| Introduction                                                                                         |      |

| Defining TAP Controller States in a Scan Sequence                                                    | 11   |

| Writing, Reading, and Operation of the Input and Output Scan Data FIFOs (TVI and TVO)                | 11   |

| Overflow and Underflow Conditions                                                                    | 12   |

| Jump and Reset Commands                                                                              |      |

| TAP Manual Mode                                                                                      |      |

| Data Modification                                                                                    |      |

| Recirculation Scan                                                                                   |      |

| B-S Chain Selection                                                                                  |      |

| Retimed Delay Support                                                                                |      |

| Automatic Test Pattern Generation (ATPG), Scan Sequence Modification (SSM), and Signature Analysis . |      |

| BSM2 Registers Related to ATPG                                                                       |      |

| Scan-Sequence Modifier (SSM)                                                                         |      |

| ATPG: Hardware Generation of Test Sequences                                                          |      |

| Programming ATPG and SSM Functions                                                                   |      |

| Low Power Mode                                                                                       |      |

| BIST—Self-Test of the BSM2                                                                           |      |

| Introduction                                                                                         |      |

| Programming BIST in the BSM2                                                                         |      |

| Appendix A—BSM2 Pseudocode Examples                                                                  |      |

| Definitions of Terms                                                                                 |      |

| Initialize Device                                                                                    |      |

| Move to Stable State                                                                                 |      |

| Instruction Scan—Load Data in TVO, Unloaded from TVI                                                 |      |

| Data Scan—Data Loaded/Unloaded in Loop                                                               |      |

| Setting up and Running an ATPG Algorithm                                                             |      |

| Switching Between B-S Chains                                                                         |      |

| Programming Self-Test of the BSM2                                                                    | 33   |

### Table of Contents (continued)

| Contents                                                                                       | Page |

|------------------------------------------------------------------------------------------------|------|

| Appendix B—BSM2 Internal Register Descriptions                                                 | 35   |

| General Introduction and Conventions                                                           |      |

| BSM2 Register Addressing, Reading, and Writing                                                 |      |

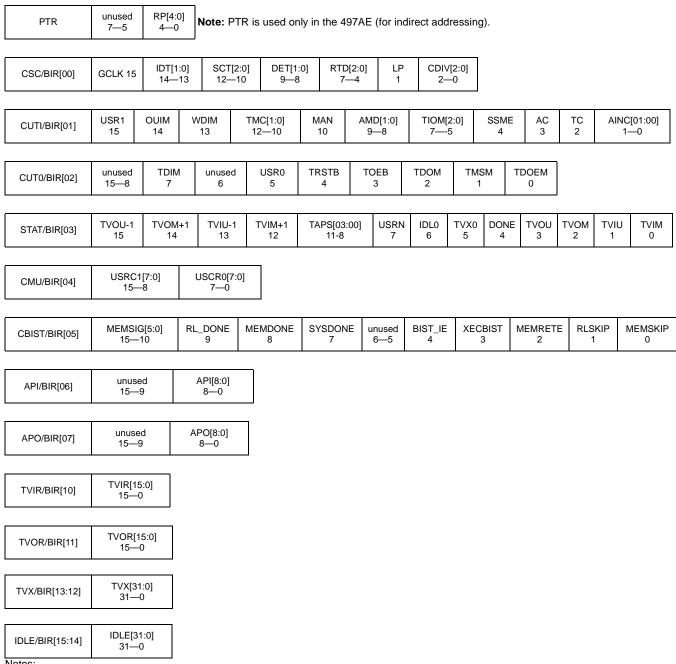

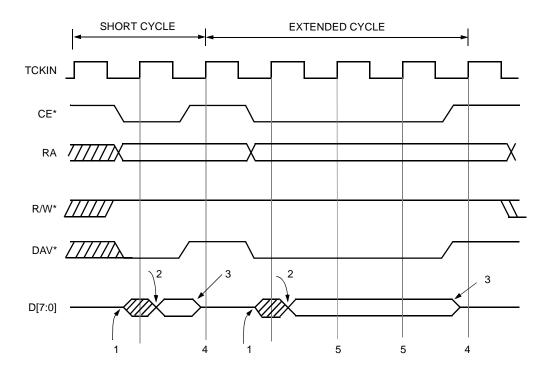

| PTR: Pointer Register                                                                          | 37   |

| CSC: Control-Scan/Clock Register                                                               | 38   |

| CUTI: Control-USEROUT1/Test Data/Interrupt Register                                            | 41   |

| CUTO: Control-USEROUT0/TAP Function/Output Enable Register                                     | 44   |

| STAT: Status Register                                                                          | 46   |

| CMU: Control-MASK/USEROUT0(1) Register                                                         | 49   |

| CBIST: Control-BIST Register                                                                   | 50   |

| API: TVI Address Pointer Register                                                              | 52   |

| APO: TVO Address Pointer Register                                                              | 53   |

| TVIR: TVI Memory Register                                                                      | 54   |

| TVOR: TVO Memory Register                                                                      | 55   |

| TVX: TVX Counter Register                                                                      | 56   |

| IDLE: IDLE Counter Register                                                                    | 57   |

| BSR: BIST Signature Register                                                                   | 58   |

| LPC: Loop Counter Register                                                                     | 59   |

| SDR: Scan Duration Register                                                                    |      |

| NCR: Net Count Register                                                                        |      |

| PRPG: ATPG Pseudorandom Pattern Generation Register                                            |      |

| SAR: ATPG Signature Analysis Register                                                          |      |

| BIR Quick Reference                                                                            |      |

| Appendix C—BSM2 (497AE) Data Sheet                                                             |      |

| Introduction                                                                                   | 66   |

| Pin Descriptions                                                                               |      |

| 5 V Tolerant Buffers                                                                           |      |

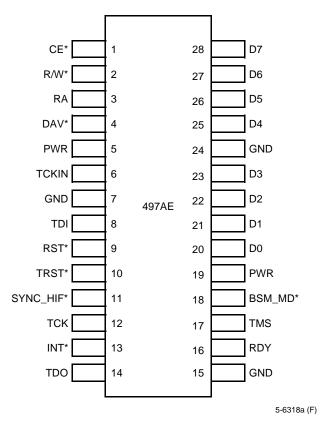

| Read/Write Cycle Timing—Synchronous Operation                                                  |      |

| Operating Conditions                                                                           | 74   |

| ac Timing Characteristics—Synchronous Operation                                                |      |

| ac Timing Characteristics—Asynchronous Operation                                               |      |

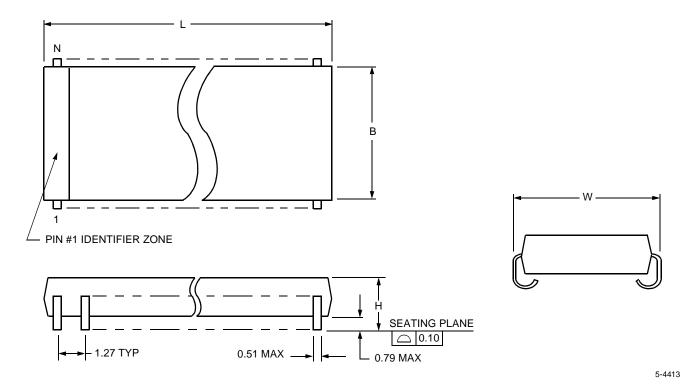

| Outline Diagram                                                                                |      |

| Appendix D—BSM2 (1215E) Data Sheet                                                             |      |

| Introduction                                                                                   |      |

| Pin Descriptions                                                                               |      |

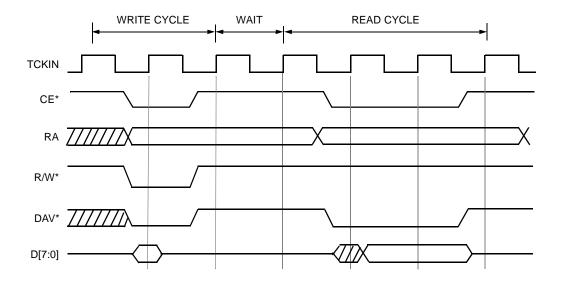

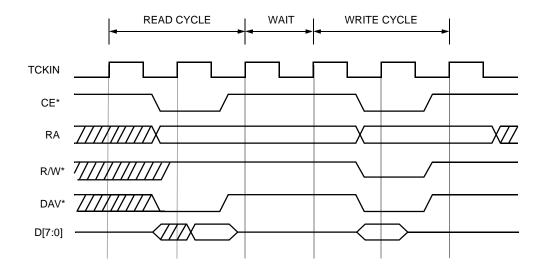

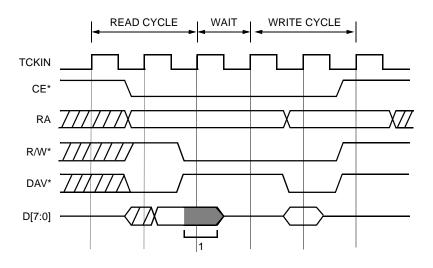

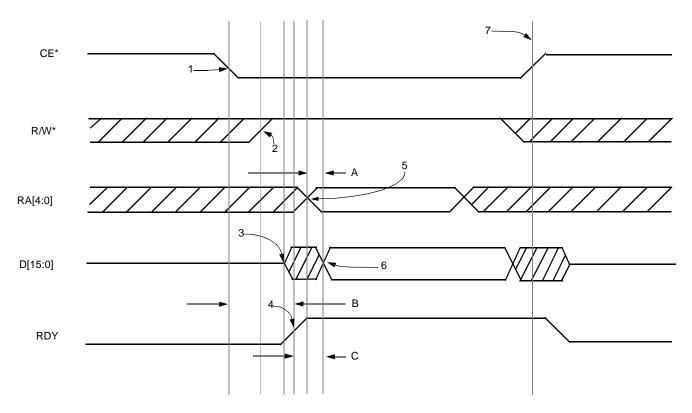

| Read/Write Cycle Timing—Asynchronous Operation                                                 |      |

| Operating Conditions                                                                           |      |

| ac Timing Characteristics                                                                      |      |

| Outline Diagram                                                                                | 84   |

| Appendix E—BSM2 Operation as a Function of Phase Relation of TCK and TCKIN at High Speeds with |      |

| Low-Valued Clock Divider                                                                       |      |

| malay.                                                                                         | 00   |

### Table of Contents (continued)

| Figures                                                                                                                                                       | Page      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

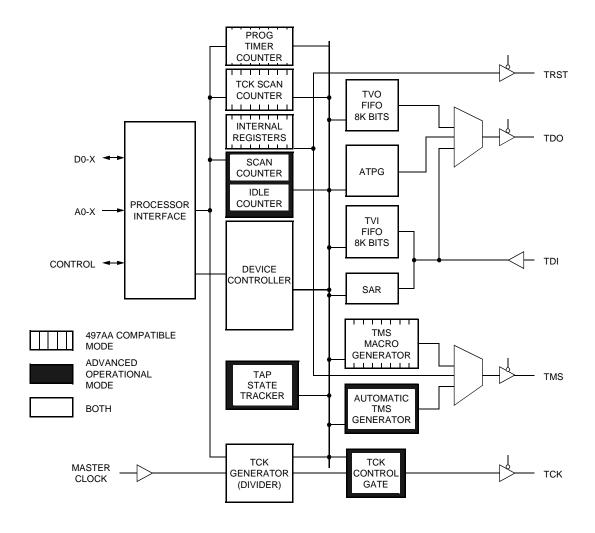

| Figure 1. BSM2 Architecture                                                                                                                                   | 6         |

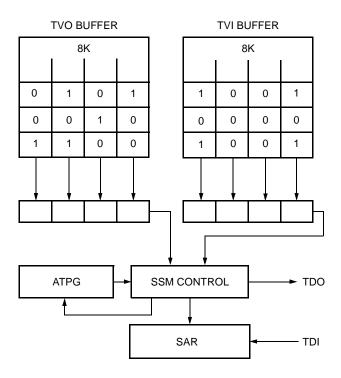

| Figure 2. Scan-Sequence Modifier (SSM)                                                                                                                        | 16        |

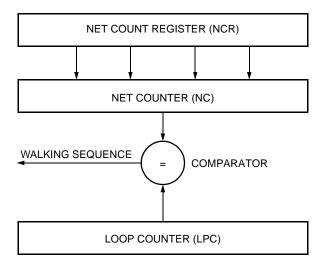

| Figure 3. Walking Sequence Test Generator                                                                                                                     | 19        |

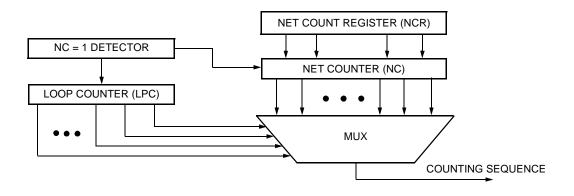

| Figure 4. Counting Sequence Test Generator                                                                                                                    | 20        |

| Figure 5. BIR Quick Reference                                                                                                                                 | 64        |

| Figure 6. BSM2 Pin Diagram (Package: 28-pin SOJ; Device Code: 497AE)                                                                                          |           |

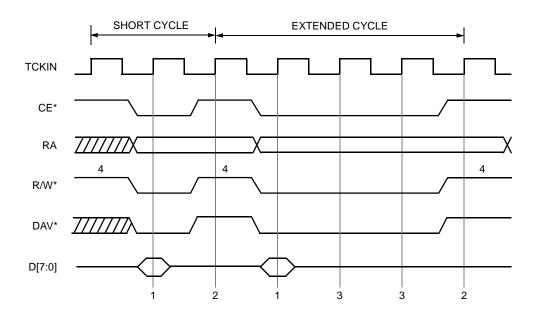

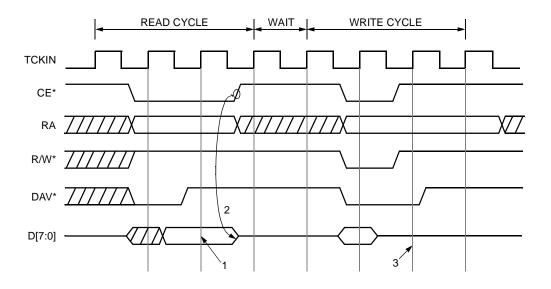

| Figure 7. 497AE Read Cycle Timing Diagram                                                                                                                     |           |

| Figure 8. 497AE Write Cycle Timing Diagram                                                                                                                    | 70        |

| Figure 9. 497AE Write-then-Read Cycle Timing DiagramFigure 10. 497AE Read-then-Write Cycle with CE* Deasserted Between Cycles                                 | / T       |

| Figure 11. 497AE Read-then-Write Cycle with CE* Asserted Through Cycles                                                                                       | / I<br>72 |

| Figure 12. 497AE Cycle with CE* and DAV* Deasserted Separately                                                                                                | 72<br>73  |

| Figure 13. Outline Diagram of 28-pin SOJ Package                                                                                                              |           |

| Figure 14. BSM2 Pin Diagram (Package: 48-pin TQFP; Device Code: 1215E)                                                                                        |           |

| Figure 15. 1215E Read Cycle Timing Diagram                                                                                                                    |           |

| Figure 16. 1215E Write Cycle Timing Diagram                                                                                                                   | 81        |

| Figure 17. Outline Diagram of 48-pin TQFP Package                                                                                                             |           |

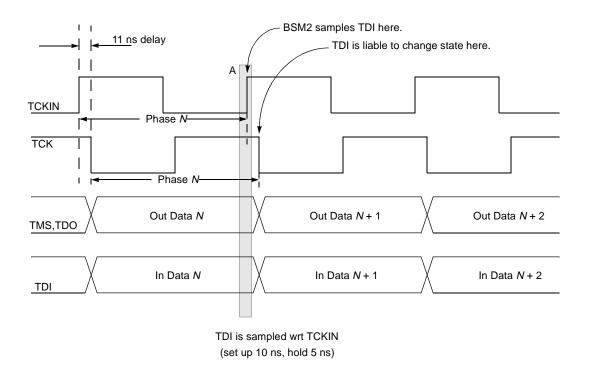

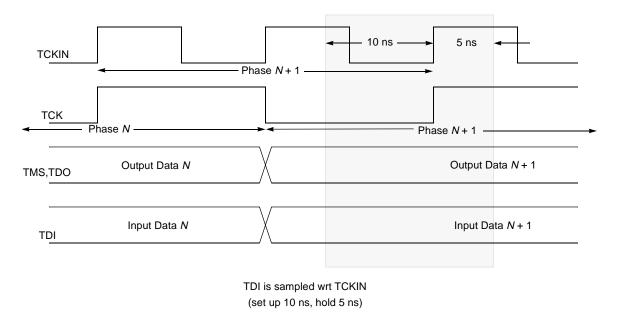

| Figure 18. Relationships of TCKIN, TCK, TDI, TDO, and TMS with TCKIN Frequency of 6.5 ns and TMS                                                              |           |

| Defined by Clock Divider Value of 1                                                                                                                           | 85        |

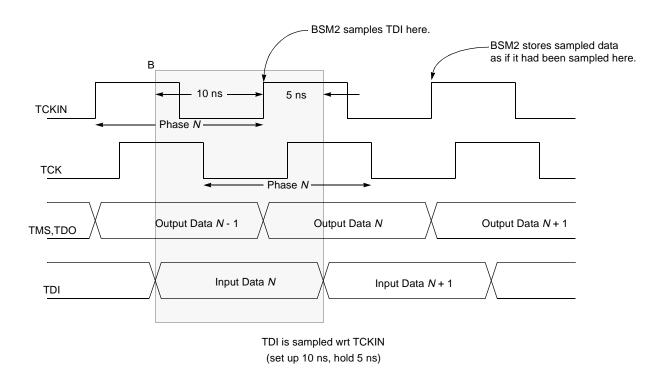

| Figure 19. Relationships of TCKIN, TCK, TDI, TDO, and TMS with TCKIN Frequency of 65 ns and TMS                                                               |           |

| Defined by Clock Divider Value of 1                                                                                                                           | 86        |

| Figure 20. Relationships of TCKIN, TCK, TDI, TDO, and TMS with TCKIN Frequency of 65 ns and TMS Defined by Clock Divider Value of 2                           | 87        |

| Tables                                                                                                                                                        | Page      |

| Table 1. ATPG Mode with SSM Enabled: How i <sup>th</sup> Bits of TVI and TVO Encode Cell Type and Control Source of TDO and Actions of ATPG and SAR Functions | )<br>17   |

| Table 2. Deterministic Mode with SSM Enabled: How i <sup>th</sup> Bit of TVI Encodes Source Cell in B-S Chain and                                             |           |

| Directs Operation of SAR                                                                                                                                      | 18        |

| Table 3. Descriptions of Registers Accessed in the Pseudocode Examples                                                                                        | 24        |

| Table 4. Description of Operations Used in Pseudocode                                                                                                         | 24        |

| Table 5. Register Descriptions (Advanced Operational Mode/497AA Compatible Mode) Relevant to BSM2 BIST                                                        |           |

| Table 6. 497AE Processor Interface Pins                                                                                                                       |           |

| Table 7. 497AE Board-Level TAP Interface Pins                                                                                                                 | 68        |

| Table 8. 497AE Power and Ground Pins                                                                                                                          |           |

| Table 9. 497AE Power Considerations                                                                                                                           |           |

| Table 10. 497AE Input/Output Characteristics                                                                                                                  |           |

| Table 11. 497AE Ambient and Storage Temperatures                                                                                                              |           |

| Table 12. 497AE Input Clock                                                                                                                                   | /5        |

| Table 13. 497AE Input Signals                                                                                                                                 | 75<br>75  |

| Table 15. 497AE Bidirectional Signals                                                                                                                         | 75<br>75  |

| Table 16. Summary of Outline Data for 28-pin SOJ Package                                                                                                      | 76        |

| Table 17. 1215E Processor Interface Pins                                                                                                                      | 78        |

| Table 18. 1215E Board-Level TAP Interface Pins                                                                                                                | 79        |

| Table 19. 1215E Power and Ground Pins                                                                                                                         |           |

| Table 20. 1215E Power Considerations                                                                                                                          | 82        |

| Table 21. 1215E Input/Output Characteristics                                                                                                                  | 82        |

| Table 22. 1215E Ambient and Storage Temperatures                                                                                                              | 82        |

| Table 23. 1215E Input Clock                                                                                                                                   | 83        |

| Table 24. 1215E Input Signals                                                                                                                                 | 83        |

| Table 25. 1215E Output Šignals                                                                                                                                | 83        |

|                                                                                                                                                               |           |

#### Introduction

#### Conventions

Throughout this document, an asterisk on any pin name indicates active-low.

The test and diagnostic processor interfaced to a BSM2 is simply called the controlling processor or the "rocessor.

#### The BSM2

The Agere 497AE/1215E Boundary-Scan Master 2 (BSM2) communicates with a generic processor in parallel and controls the test and diagnosis (T&D) of a unit-under-test (UUT)—a device, board, or system, based on the ANSI/IEEE1 Std 1149.1-1990 Test Access Port (TAP) and Boundary-Scan (B-S) Architecture and its supplements. The BSM2 serializes test vectors, delivers them to the UUT using the standard protocol, and stores UUT response as raw data or as a signature. An automatic test pattern generator (ATPG) generates four common test sequences for interconnect test, cluster test, etc. The BSM2 also solves potential problems of bus conflict and nonrepeatable board-level signatures associated with pseudorandom testing of a product through its B-S architecture. Finally, the BSM2 provides support for edge-connector/backplane test and system test and diagnosis.

The 497AE and 1215E represent a total redesign of the 5 V 497AA using 0.35  $\mu m$  CMOS technology. The major differences are that both parts have a higher operating frequency: 65 MHz, only require a 3.3 V power supply, and can operate over the temperature range of -40 °C to +85 °C. The new 497AE design maintains a high degree of hardware and software compatibility with the 497AA (manual MN98-030NTNB). New features and operational modes have been added to the 497AE and 1215E. The present manual describes operation of these parts in advanced operation mode:

Synchronous/asynchronous-8 mode (497AE)—the interface of the 497AE can operate either synchronously or asynchronously according to user selection. In addition, one of two internal operational modes is selectable—either the 497AA Compatibility Mode or the Advanced Operational Mode.

The Advanced Operational Mode is significantly different than the 497AA mode. There is an internal state machine that tracks the state of the TAP Controllers of the B-S devices currently in the UUT B-S chain connected to (addressed by) the BSM2. With this feature, TMS signal generation is greatly simplified, i.e., automatic. Access to the data memories is also simplified because they behave like FIFOs.

Asynchronous-16 interface (1215E)—this is similar to the 8-bit mode Advanced Operational Mode described above, but with a different package (48-pin TQFP) and a 16-bit data bus.

Although the 497AE supports 4 possible operational scenarios (2 different host interfaces, 2 different internal operational modes), the 1215E operates only with an asynchronous host interface and in Advanced Operational Mode. The Advanced Operational Modes are described in this document.

A systems approach was taken in defining the architecture of the BSM2. A major goal of the architecture was to minimize the housekeeping required by the processor, as well as to maximize the T&D throughput. Figure 1 depicts the architecture of the BSM2.

At the left of the figure is shown a generic microprocessor interface with address, data, and control signal connections. On the right side are shown the signals by which the BSM2 communicates with an ANSI/IEEE Std 1149.1-1990 TAP. Consequently, the BSM2 can be considered a protocol converter. The main subsystems of this device are listed below and will be discussed in more detail in the following sections:

- Processor Interface (PI)

- Device Controller

- BSM2 internal registers (see Appendix B)

- Test Data Memories (FIFOs)

- Automatic Test Pattern Generation (ATPG), Scan Sequence Modification, and Signature Analysis

- Automatic TMS Generator

- TAP State Tracker

- TCK Generator and Gating

- User-Definable I/O (1215E Only)

- Interrupt Control

<sup>\*</sup> *Adobe* and *Acrobat* are trademarks of Adobe Systems Incorporated.

Agere Systems Inc.

1663

#### **Introduction** (continued)

#### The BSM2 (continued)

Major functional units are given separate treatment in addition to the architectural descriptions:

- The BSM2 Scan Process

- Automatic Test Pattern Generation (ATPG), Scan Sequence Modification, and Signature Analysis

- Low Power Mode

- BIST—Self-Test of the BSM2

This document has five appendices:

- Appendix A—BSM2 Pseudocode Examples

- Appendix B—BSM2 Internal Register Descriptions

- Appendix C—BSM2 (497AE) Data Sheet

- Appendix D—BSM2 (1215E) Data Sheet

- Appendix E—BSM2 Operation as a Function of Phase Relation of TCK and TCKIN at High Speeds with Low-Valued Clock Divider

Appendix B includes description of programming the BSM2 registers. In addition, timing of actions resulting from writing to the registers is discussed.

Appendices C & D are data sheets for the two forms of the BSM2—the 497AE and the 1215E.

This manual assumes familiarity with ANSI/IEEE Std1149.1-1990, IEEE Std 1149.1a-1993, and IEEE Std 1149.1b-1994, obtainable from the IEEE Standards Office.

Figure 1. BSM2 Architecture

#### **Architecture of the BSM2**

#### TAP, Power, and Ground Pins

Both the 497AE (Table 7) and 1215E (Table 18) have a 5-pin TAP interface. Details of power and ground pinout can be found in Table 8 (497AE) and Table 19 (1215E).

#### BSM\_MD\* (497AE only)

This pin defines the operational mode of the device. It should be tied low for operation in 497AA compatible mode. If tied high or left unconnected, an internal pull-up will cause the device to operate in Advanced Operational mode. This pin should not be switched during operation of the BSM2.

#### SYNC HIF\*

This pin defines host interface operation. If SYNC\_HIF\* = 0, then the interface will operate synchronously as in 497AA mode. If SYNC\_HIF\* = 1 or if the pin is left unconnected, the interface will operate asynchronously (Figure 15 and Figure 16). There is an internal pull-up on this pin. This pin should not be switched during operation of the BSM2.

#### **Processor Interface**

The processor interface provides generic functionality including chip enable (CE\*), read/write control (R/W\*), data available/valid (DAV\*), master clock input (TCKIN), interface ready handshake control (RDY), and interrupt signalling (INT\*). The asterisk following a pin name indicates that the signal on that pin is active low.

Basic functional description of the pinout of the 497AE processor interface can be found in Table 6.

Basic functional description of the pinout of the 1215E processor interface can be found in Table 17.

#### 497AE Data Bus

The data bus (D[7:0]) of the 497AE is 8 bits wide permitting writing and reading of BSM2 Internal Registers (BIRs) on a byte-at-a-time basis. Details of read/write operation are provided in Appendix B under the heading 497AE Register Size, Byte Transfer, and Synchronization of Reads and Writes.

#### 1215E Data Bus

The data bus (D[15:0]) of the 1215E is 16 bits wide permitting writing and reading of the BIRs on a word-at-a-time basis. Details of read/write operation are provided in Appendix B under the heading 1215E Data Reads and Writes.

#### 497AE Addressing

The 497AE preserves the indirect addressing operation of the 497AA. The RA pin is used to address a Pointer Register (PTR). Once the PTR is selected, the register address of a BIR to be accessed is placed in the PTR by writing to the 497AE data bus. Details of this indirect addressing are provided in Appendix B under the heading 497AE Register Size, Byte Transfer, and Synchronization of Reads and Writes.

One difference between the 497AA Compatibility Mode and the Advanced Operational Mode of the 497AE is that the device is *not* reset by reading from PTR in Advanced Operational Mode.

#### 1215E Address Bus

The 1215E provides only a direct addressing method. The address bus comprises the pins RA[4:0]. Further information concerning use of the address bus is provided in Appendix B under the heading 1215E Addressing (Direct).

#### **Device Controller**

The device controller provides coordination and synchronization of the various modules depending on the selected modes of operation. All registers and memory are held in a static state until one of three command states are selected: Execute, Jump, or Reset. In the default mode, the TCK is free running, but can be set to a gated mode such that the clock is off when the device is in the nonexecuting mode.

In addition, the controller coordinates the internal selftest operations of the BSM2 (see under the heading BIST—Self-Test of the BSM2).

#### Architecture of the BSM2 (continued)

#### **Test Data Memories (FIFOs)**

There are two test data memories (TVI and TVO). Each consists of 8K bits organized in 512 16-bit words. They behave as FIFOs during normal load-scan-unload operation. In such a case, it is not necessary for the controlling processor to specify addresses for writing to, or reading from, the test data memories. To reset a FIFO, the relevant address pointer register (API or APO) can be loaded with the value 0.

However, in ATPG mode the test data memories do not operate as FIFOs. In such a case, these memories hold information about circuit interconnect necessary to create conflict-free ATPG. FIFO organization is not appropriate in ATPG mode. In this mode, BSM2 needs a memory pointer permitting it to loop through the circuit interconnection information—once for each vector to be generated. In ATPG mode, the words of the memories can be written and read individually using their respective address pointer registers, API and APO. (See Automatic Test Pattern Generation (ATPG), Scan Sequence Modification (SSM), and Signature Analysis.)

#### **TVI Test Data Memory (FIFO)**

This 8K-bit memory receives the output test data from the selected/attached B-S chain during normal scan operation.

During ATPG operation, the B-S chain output data stream is re-directed to a signature analysis register (SAR). The TVI test data memory is used during ATPG for a portion of a circuit map that permits the test generation function to avoid bus conflict in the application of otherwise circuit independent algorithms. More details on ATPG are found under the heading Automatic Test Pattern Generation (ATPG), Scan Sequence Modification (SSM), and Signature Analysis.

#### **TVO Test Data Memory (FIFO)**

This 8K-bit memory stores the test stimulus data to be scanned into a selected/attached B-S chain during normal scan operation.

During ATPG operation, the test stimulus is provided by the test pattern generation hardware. The TVO test data memory is used to store a portion of the circuit map mentioned above.

#### User-Definable I/O (1215E Only)

The 1215E provides three pins for user-definable I/O—USERIN, USEROUT1, and USEROUT2. These might be interfaced to a DMA controller, for example.

#### **USERIN**

The USERIN pin provides the capability of optionally monitoring the state of a user selected signal without adding additional parallel I/O decoding logic to a design. Because of pin limitations it is not available on the 497AE device. If it is unused in the 1215E design, it should not be left floating, but tied either high or low.

**Note:** The USERIN signal is not latched in the BSM2. Stability of this signal is the responsibility of the user.

#### **USEROUT0**

The USEROUT0 pin provides the means of signalling an interrupt to the controlling processor according to certain conditions of the Test Data Memories (FIFOs) (e.g., full, empty, etc.).

The pin can be considered to be the output of a 9-input OR tree as follows: The USR0 bit in the CUTO register is ORed with the STAT[15:12] and STAT [3:0] bits of the status register under control of a mask programmed in the USRC0[7:0] bits of the CMU register.

#### **USEROUT1**

The USEROUT1 pin provides the means of signalling an interrupt to the controlling processor according to certain conditions of the Test Data Memories (FIFOs) (e.g., full, empty, etc.).

The pin can be considered to be the output of a 9-input OR tree as follows: The USR1 bit in the CUTI register is ORed with the STAT[15:12] and STAT [3:0] bits of the status register under control of a mask programmed in the USRC1[7:0] bits of the CMU register.

#### Architecture of the BSM2 (continued)

#### **TCK Generator and Gating**

#### **TCK Generator**

The BSM2 derives the TCK signal for a selected/ attached B-S TAP from the Master Clock input signal (TCKIN) via a divider called the TCK Generator (Figure 1). The TCK Generator can be programed to divide the Master Clock by 2n with  $0 \le n \le 7$ . The value of n is programed in the CDIV[2:0] bits of the CSC register.

#### **TCK Gating**

The default state of the TCK signal is free-running, with a divide by 128 of the TCKIN signal. It can be set to a gated mode, in which TCK only operates when scanning or moving from TAP state to state. TCK is gated off when the TAP State Tracker (below) is in the idle state or the scan destination state or when data overflow or underflow conditions exist.

#### **Automatic TMS Generator**

In the normal mode (nonmanual), the TMS signal pattern is provided from an internal circuit that automatically determines the pattern based on the current state, the desired scan operation (e.g., data register scan), and the destination state. In the automatic pause mode, if there is data overflow or underflow, the automatic TMS generator commands the TAP Controllers of the selected/attached B-S chain to move to the appropriate Pause-xR state [or, if so programmed, pause via gating the clock signal on TCK (see above)] automatically until the condition is corrected.

#### **TAP State Tracker**

This functional block controls the signals produced by the BSM2 on its TMS output pin. By doing so, at any time during scan operation, the TAP State Tracker can provide to BSM2 internals the current TAP Controller state of the TAP Controllers on the selected/attached B-S chain. When a scan operation is initiated, the then current TAP Controller state (according to the TAP State Tracker) is used as the initial state of a sequence of states passing through the desired scan state (programmed by the controlling processor) and terminating in a target state (programmed by the controlling processor).

This method of scan sequence programming differs from that implemented in the original BSM (497AA). For more about BSM2 scan operation, see the description under the heading The BSM2 Scan Process. For more about the registers used to program the BSM2 scan operation, see descriptions of the TVX, IDLE, LPC, and SDR registers.

#### **Interrupt Control**

Interrupt control is achieved by programming the interrupt mask bits OUIM and WDIM (in the CUTI register) and BIST\_IE (in the CBIST register).

If any of these bits has the value 0, the interrupt signal, INT\*, will not respond to the relevant interrupt-provoking stimulus. The value of one of these bits is 1, it will bring INT\* low (active) according to the occurrence of the relevant stimulus.

Interrupt servicing software must scan all relevant status bits to determine the event that generated the interrupt. It is often appropriate to set the mask bits to 0 while eliminating the cause of an interrupt.

### Asynchronous and Synchronous Interface Modes

#### Asynchronous Operation (497AE and 1215E)

The device pinout tables for the 497AE will be found in Appendix C, beginning on page 67. The device pinout tables for the 1215E will be found in Appendix D, beginning on page 78.

An asterisk following a pin name indicates that it is active-low.

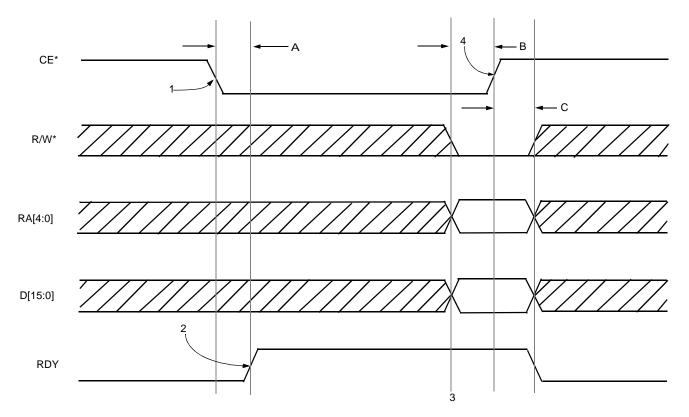

In asynchronous interface mode, the  $CE^*$  (chip enable) pin is the main control signal. The R/W\* pin controls the direction of the data bus when  $CE^* = 0$ .

On the output side of control, the RDY pin provides a handshake from the BSM2 to the controlling processor.

The defining characteristic of asynchronous interface mode is that the BSM2 protocol in this mode is independent of the BSM2 master clock signal (TCKIN). Internally, the device must synchronize with TCKIN; therefore, the RDY signal may be required to indicate whether BSM2 internal response to a previous access by the controlling processor is complete.

The RDY signal will never be active unless CE\* is.

An access cycle begins with the controlling processor driving CE\* = 0. The R/W\* pin is driven to the logic value defining the type of access desired.

If the BSM2 is not internally synchronized for a new access, then the BSM2 will hold the RDY signal inactive (=0) until internal synchronization is achieved. When the RDY signal = 1, the controlling processor can continue the access cycle.

At the end of the access cycle, the controlling processor drives CE\* = 1. Any capture of data by the BSM2 occurs on the rising edge of the CE\* signal—when CE\* goes inactive. In a read access cycle, any data on an output bus of the BSM2 is only correct after RDY = 1. The bus is no longer driven after the rising edge of CE\*.

Note:

If the BSM2 user can guarantee that accesses by the controlling processor will be separated by a minimum of 4 cycles on the TCKIN signal, then RDY pin does not need to be monitored by the controlling processor.

The Read sequence is as follows:

- The controlling processor requests an access by driving the signal on CE\* low.

- R/W\* is driven high. Consequently, the data bus will be driven by the BSM2 and contain data from the selected register once RDY = 1.

- After reading the data bus, the controlling processor drives the signal on CE\* high, terminating the access cycle.

The Write sequence is as follows:

- The controlling processor requests an access by driving the signal on CE\* low.

- R/W\* is driven low. Consequently, the data bus will be driven by the controlling processor and contain data to be written to a selected register.

- The BSM2 drives the signal on RDY high.

- The controlling processor drives the CE\* signal high.

- The data to be written is latched by the BSM2 on the rising edge of the CE\* signal.

- Relevant timing diagrams for the 1215E begin with Figure 15 on page 80. The operation of the 497AE on the pins with common names is identical to that of the 1215E.

#### Synchronous Operation (497AE only)

Synchronous operation of the 497AE strongly resembles the operation of the 497AA.

Relevant timing diagrams for the 497AE begin with Figure 7 on page 69.

#### The BSM2 Scan Process

#### Introduction

#### **Normal Scan Operation**

Normal scan operation in the BSM2 involves loading test input stimulus data into the TVO FIFO and defining a sequence of states in the TAP Controllers of the selected/attached B-S chain. This sequence is the shortest path through the finite state machine implementing the TAP Controller such that it begins at a defined starting TAP Controller state, passes through a defined TAP Controller state in which scanning occurs, may pass through a defined TAP Controller state in which the operation will "idle" for a defined amount of time, and terminates in a defined TAP Controller state.

During normal scan operation, test results output data is stored in the TVI FIFO.

Normal scan operation is selected by setting the TIOM[2:0] bits of the CUTI register to 001.

#### **Applying Stimulus While Ignoring Test Results**

If it is desired to ignore test results during a scan operation, the BSM2 can be programmed to do so by setting the TIOM[2:0] bits to 000.

This mode can be used when it is desired to improve scan downloads to a target device and avoid the overhead of the extra I/O operations needed for reading output from TVI. For example, the technique can be used to download software or to establish programmable logic prior to "burn-in."

See also the discussion of rapid upload of data under the heading Recirculation Scan.

### **Scanning Out Results Without Applying Test Stimulus**

To scan data from a selected/attached B-S chain without scanning new test stimulus into the chain, the TIOM[2:0] bits should be set to 100. In this "response only" mode, data from the chain is directed to the TVI FIFO or the SAR (as determined by current programming of for scan sequence modifier or SSM), but no data from the TVO FIFO or the ATPG function is scanned into the chain. Instead, the chain is simply reloaded with the data it previously contained in the manner described under the heading Recirculation Scan.

### **Defining TAP Controller States in a Scan Sequence**

The starting state is the current state of the TAP Controllers in the attached/selected B-S chain. This state is synchronized with the state known to the TAP State Tracker at power-up or by the use of TSRT\* to force the attached/selected B-S chain TAP controllers to the Test-Logic-Reset TAP Controller state. Once synchronization is established, the current state of the TAP controllers of the attached/selected B-S chain can be determined by the value of the TAPS[3:0] bits in the STAT register.

The TAP Controller state in which scanning is to occur is determined by the value of the SCT[2:0] bits in the CSC register.

The destination TAP Controller state is determined by the value of the DET[1:0] bits in the CSC register.

The "Idle" TAP Controller state is determined by the Idle Type bits (IDT[1:0]) in the CSC register. Note that if an "idle" TAP Controller state is specified that does not lie on the shortest path between the starting state and the destination state running through the scanning state, then that "idle" state will never be entered in the scan operation.

The number of cycles of the TCK signal for which the operation is to remain in the "idle" TAP Controller state is written to the IDLE register.

### Writing, Reading, and Operation of the Input and Output Scan Data FIFOs (TVI and TVO)

Pseudocode illustrating a normal scan process is illustrated on page 28.

The total number of bits to be scanned in a single vector is written to the TVX register.

The starting address for test stimulus data in the TVO FIFO is written to the APO register. The starting address for test results data in the TVI FIFO is written to the API register.

Establishing the type of scan operation is done by writing the TIOM[2:0] bits of the CUTI register. Execution is initiated by writing the EXEC bit of the CUTI register.

The status register allows the controlling processor to monitor the scan operation. For example, if all test result data in the TVI FIFO has been read, this will be indicated by the TVIM bit. If the TVO FIFO has not been filled with stimulus data, this will be indicated by the TVOU bit.

#### The BSM2 Scan Process (continued)

# Writing, Reading, and Operation of the Input and Output Scan Data FIFOs (TVI and TVO) (continued)

Prior to execution, the user may program a pause during a subsequent normal scan operation by gating the signal on TCK. This is done by use of the GCLK bit in the CSC register. The gated clock function is described under the heading TCK Gating.

#### **Overwriting TVO and Overreading TVI**

If the user writes to the TVO memory when it is full, data in the FIFO will be overwritten. If the user reads the TVI memory when it is empty, the value will be unpredictable and useless. In both cases the memory pointers will become incorrect; and, consequently, the FIFOs will be corrupted. The only way to recover is to reinitialize and restart the interrupted operation. The FIFOs are reinitialized by setting the values of both the address pointers (APO for TVO and API for TVI) to zero.

#### **Avoiding Overwriting TVO and Overreading TVI**

Overwriting TVO (overreading TVI) can be avoided by checking if TVO has been filled (or TVI emptied).

When TVO is full, the TVOU bit in the status register will have the value 1. When TVI is empty, the TVIM bit in the status register will have the value 1.

#### **Overflow and Underflow Conditions**

Overflow is the condition in which more data is scanned out of the selected/attached B-S chain than can be stored in the TVI test data memory.

Underflow is the condition in which insufficient data is loaded in the TVO test data memory for the current scan operation. Underflow is not projected when the TVO memory is loaded. The condition is discovered by the BSM2 when it arises during the subsequent scan operation.

When overflow or underflow of a test data memory (FIFO) occurs, the BSM2 can be programmed to always enter the appropriate Pause-xR TAP Controller state or to gate the test clock (halt the signal on TCK). The programming is done by the loading the appropri-

ate value in the GCLK bit of the CSC register prior to execution of a scan operation. When GCLK = 1, under-/overflow results in halting the test clock. When GCLK = 0, under-/overflow causes transfer of the TAP controllers in the selected/attached B-S chain to enter the nearest Pause-xR TAP Controller state.

#### **Jump and Reset Commands**

By use of the EXEC[1:0] bits of the CUTI register, the controlling processor can direct the BSM2 to drive the TAP State Tracker to specific TAP Controller states.

WARNING: The Jump and Reset commands execute whether or not there is any other ongoing process executing in the BSM2.

#### **Jump Command**

The jump command is designed to be used when a BSM2 is controlling more than one B-S chain and needs to the synchronize to the current state of the TAP Controllers in a newly selected B-S chain after having carried a sequence of operations on another.

This command is not locked out by a concurrently executing process.

The jump command results in the direct movement of the TAP State Tracker from the current TAP Controller state to any other one selected by programming. The move between states is not restricted to following an arc of the TAP Controller's finite state machine. Moreover, with the exception of a jump to/from the Test-Logic-Reset TAP Controller state, the TMS output signal is not effected; and the TAP Controllers of the formerly selected/attached B-S chain will only change state as directed by subsequent programming of the BSM2. When the jump is to/from the Test-Logic-Reset TAP Controller state, the signal on TMS must change from 0 to 1 or vice versa.

WARNING: Issuing the Jump Command while executing a scan operation, can produce undesirable results, although the results are predictable if the cycle of the TCK signal is long enough so that the controlling processor can monitor operations.

#### The BSM2 Scan Process (continued)

#### Jump and Reset Commands (continued)

#### **Reset Command**

This command overrides (halts) any current execution in any mode and internally resets the BSM2. Executing the Reset command does not activate the TRST\* signal.

The TAP State Tracker will indicate that the BSM2 has driven the TAP Controllers of the selected/attached B-S chain to the Test-Logic-Reset TAP Controller state. It is necessary to synchronize the TAP State Tracker with the selected/attached B-S chain by running TCK for five cycles with the TMS signal equal to 1 or by use of the TRST\* signal.

#### **TAP Manual Mode**

In the BSM2, it is possible to single step through a scan sequence in TAP Manual Mode. TAP Manual Mode is entered by writing a 1 to the MAN bit of the CUTI register.

The key to understanding TAP Manual Mode is the fact that writing the CUTO register not only supplies values to be driven on TMS, and TDO, but also produces the clock edge on TCK that causes the values to be driven. Likewise, reading the CUTO register not only is a means of capturing the value concurrently available on the TDI pin, but also produces the clock edge on TCK that cause the value in question to be captured from the output of the selected/attached B-S chain.

The CUTO register includes the bits that enable the operation of the TAP signals of the BSM2. Each TAP pin, other than TCK, is represented by a bit in the register. There is an additional bit operational in the manual mode only, TDOEM. In this mode, TDOEM controls enabling/disabling of the TDO output pin.

#### **Control of TCK Pin**

While writing (reading) the CUTO register causes an internal TAP Manual Mode TCK register to go low (high), this will not have effect on the value of the TCK pin of the BSM2 unless the pin is enabled for TAP Manual Mode by having the MAN bit of the CUTI register set. When the BSM2 is in TAP Manual Mode the normal connection of the TCK pin to the internal TCK generator (divider of the master clock) is overridden.

In this way the user can preselect the state of the TCK pin before going to the manual mode by either reading or writing to the CUTO register. In other words, once TAP Manual Mode is selected, the user does not need to worry about toggling TCK as it is done naturally by reading and writing to CUTO—with the same phase as defined in *IEEE* Std. 1149.1.

#### Control of TDI, TDO, TMS, and TRST\* pins

In TAP Manual Mode, the next values to be driven on the TDO and TMS pins of the BSM2 are written to the TDOM and TMSM bits (respectively) of the CUTO register. Enabling/disabling of the TDO pin is controlled by the value written to the TDOEM bit (unless overridden by the state of the TOEB bit). Likewise a reset of the TAP Controllers on the selected attached B-S chain is effected by writing CUTO with the value 1 in the TRSTB bit. (The use of the TRSTB bit is not restricted to TAP Manual Mode.)

In TAP Manual Mode, when the CUTO register is read, the value output from the selected/attached B-S chain will be found in the TDIM bit of that register.

#### **Data Modification**

#### **TDO Inversion**

The value of bits from various internal sources (e.g., TVO) and driven by the BSM on its TDO output signal can be inverted before they are scanned into a selected/attached B-S chain. This is achieved by the use of the TC bit (CUTI[02]).

#### **Signature Analysis for Deterministic Tests**

The signature analysis register (SAR) can be used to compress the results of deterministic scan testing as well as in the case of ATPG. The SAR is selected through the use of the SSM function. See the description under the headings Signature Analysis for Deterministic Tests, Scan-Sequence Modifier (SSM), and Programming ATPG and SSM Functions.

**Note:** The retimed delay function is not applicable to scan operation in which the SAR is the target for data scanned into TDI.

#### The BSM2 Scan Process (continued)

#### **Recirculation Scan**

Using the TIOM[2:0] bits of the CUTI register, it is possible to program the BSM2 to directly connect its TDI input to its TDO output within the device.

There are two types of recirculating scan—recirculate mode (TIOM[2:0]=101) and recirculate mode with response only (TIOM[2:0]=111).

The Test Data Memories (FIFOs) are disconnected, and data that was in the selected/attached B-S chain when recirculating scan began is recycled through the chain for the programmed number of bits. During the recirculating scan, the BSM2 adds no delay to the scan chain—a B-S chain of n cells recirculates in n cycles of the TCK clock signal.

The recirculate mode is useful for manual debugging of B-S chains. The following approach was provided by an experienced BSM (497AA) user and is equally applicable in the case of BSM2.

First, a standard data scan is used to preload all scan flip-flops in the B-S chain. This scan operation is terminated in the Pause-DR TAP Controller state. Because of software performing I/O to the BSM2, this data scan is bursty—the host computer cannot keep the pipe flushed; TAP Controllers in the B-S chain move from Shift-DR to Pause-DR, back to Shift-DR, etc., until all of the data has been scanned in. Once the scan chain is preloaded, the recirculate mode (without storing response) is employed. By executing a scan operation in the recirculate mode, the BSM2 causes all the TAP Controllers on the selected/attached B-S chain to enter the Shift-DR TAP Controller state and remain in that TAP Controller state for the total number of scan bits. The TAP leads of individual devices can then be probed with a scope to detect and display the serial bit pattern in its entirety. The TMS signal is used to gate monitoring of the TDO/TDI data.

In the case of the recirculate mode with response only, a common application is the upload of functional data via a processor/controller with a TAP; just as applying stimulus while ignoring results (TIOM[2:0]=000) optimizes download times, recirculate mode with response only optimizes upload times.

#### **B-S Chain Selection**

The BSM2 supports a test architecture in which there are multiple B-S chains. The BSM2 can be programmed to select one of such B-S chains using the ASP protocol and interface definition (e.g., supporting *TI*'s Addressable Scan Port devices).

#### **Retimed Delay Support**

In some applications of B-S, there can be selected/ attached chains that are physically distant from the BSM2. In these cases, clock skew between the signals of the TAP may become a problem. In order to alleviate the difficulty, designers may add intermediate latches (the same number for each BSM2 output signal) to deskew (retime) the signals (typically, TMS, TDO, and TDI). Each of the *n* latches in a given signal path will create one cycle of delay in the signal.

At the destination B-S chain, this is not a problem. The TMS and TDO signals will still be synchronized. The distant B-S chain will operate as if it were directly attached to TMS and TDO (after a delay of n cycles). The distant B-S chain will produce signals on the line driving the TDI signal of the BSM2. However, on the return path, the sequence of bits on the TDI signal will be delayed by the m latches in the TDI signal deskewing circuitry. The result is that the TDI signal is shifted by n+m cycles, where n+m is the total number of the latches in the signal path. The BSM can be programmed to take this delay into account when capturing the serial vectors scanned from the distant B-S chain.

The BSM2 can adjust to up to 13 latches in the deskewing circuitry by phase delaying the TDI signal by the value of the RTD bits. The programming of these bits is detailed in the discussion of the CSC register.

**Note:** The retimed delay support function applies only to scan operations when the TVI FIFO is selected as the target for input from TDI. It does not apply when the target for incoming scan data is the SAR.

This section describes the BSM2 ATPG and scan sequence modification (SSM). While the description refers to interconnect test, this capability is general and can be used to test logic through a selected/attached B-S chain as well as device interconnection. It may prove useful for cluster test—testing of non-B-S devices via the B-S paths of devices that surround the non-B-S devices. It can also be used to test the internal logic of devices.

In carrying out interconnect testing, it is possible that bus conflicts could arise if multiple devices on a single bus were enabled simultaneously. The BSM2 avoids this situation by using a concise form of a wiring list to inform the ATPG function of which B-S cells are at device inputs, which are at outputs, and which must be held to a constant value (e.g., because they drive enable signals on other devices). (See the section titled Scan-Sequence Modifier (SSM).)

This section initially describes some of the BSM2 registers and memory blocks that are used for ATPG. The operation of the SSM, the subsystem that modifies the scan vectors and controls the response compression, is then described in detail. The hardware implementation of the test sequences in the ATPG mode is illustrated.

#### **BSM2** Registers Related to ATPG

In this section, the registers used during ATPG are reviewed. Under the heading "Appendix B—BSM2 Internal Register Descriptions," all registers are described in greater detail.

Control of ATPG, SSM, and Signature Analysis

- CUTI[09:08]—These bits, also called AMD[1:0], permit the selection of one of the four possible patterns that the BSM2 ATPG is capable of generating. The output data of an ATPG algorithm may be inverted prior to scanning into a selected/attached B-S scan path under control of the AC bit (CUTI[03]) as illustrated in the description of the CUTI register.

- The SSME bit (CUTI[04]) serves the function of enabling or disabling SSM and, with it, the signature analysis register (SAR).

#### ATPG-Related Registers

- Loop counter (LPC)—This 16-bit counter contains the number of serial tests that are to be applied to the UUT. Every time a complete vector is shifted out, this counter is decremented.

- Scan duration register (SDR)—This 16-bit register contains the length of each serial test vector to be applied to the UUT. This value is the length of the scan path—the total of the lengths of the B-S data registers in all the chips on the selected/attached B-S ring. The value from this register is loaded in a scan duration counter (SDC) which is decremented every time a vector bit is shifted out. When SDC reaches zero, a signal is sent to decrement LPC. Then, if LPC is not 0, the SDC is reloaded from the SDR. When both SDC and LPC are zero, the BSM2 stops transmitting serial test data.

- Net count register (NCR)—This 16-bit register is used by the ATPG in conjunction with the net counter (NC), to generate counting and walking sequences.

- Signature analysis register and pseudorandom pattern generator (SAR and PRPG)—These are 32-bit registers. The seed values for both of these registers are programmable in advanced operational mode. The PRPG is both readable and writable in the advanced operational mode and write-only in the 497AA mode.

- Control-Scan/Clock register (CSC)—In this register the scan type bits (SCT[2:0]) must be set for Shift-DR scan type (i.e., loaded with the pattern 010) for ATPG operation. Also, the destination state for ATPG should be set to either Test-Logic-Reset or Run-Test/Idle. This is accomplished using the destination type bits (DET[1:0]).

- IDLE counter register (IDLE)—This register should be set to zero for ATPG operation to disable the IDT bits of the CSC register.

The BSM2 has two 8K memory buffers, called the test vector out (TVO) and test vector in (TVI) buffers. For deterministic tests, these two buffers hold test vectors and the response of the UUT. In the case of ATPG, the SSM uses these to store a structure map of the scan chain, as described in the next section.

#### Scan-Sequence Modifier (SSM)

This section describes a circuit called the SSM. It modifies a test sequence to ensure that no bus conflict will occur before the sequence is passed to the selected/attached B-S chain of the UUT. The modifier also enhances the efficiency of the test pattern generator, and controls the SAR so that only selected values are compressed. This module is used for modifying scan sequences in both ATPG and deterministic modes (see Figure 2).

5-6311 (F)

Figure 2. Scan-Sequence Modifier (SSM)

A B-S interconnect test sequence has three types of data:

- Type 1 is the test data that is to be applied to the output cells, one output cell per net. This data is determined by the test algorithm. This is the test stimulus information.

- Type 2 is output control data that determines whether a 3-state pin is active or in high impedance or the direction of a bidirectional pin. This information is determined by the board structure and does not change during application of a particular test algorithm. The control data is required to ensure that no bus conflicts occur due to the generated test. In general, this is the test information that needs to be held static. An example of this information, in the case of a cluster test, would be an enable signal that needs to be held low for meaningful tests to be applied.

- Type 3 is filler data that is scanned into the input cells at the receiving (input) sides of nets. This data is essentially don't care and is overwritten when a response is captured by these same cells. Filler data is required to permit the useful data, type 1 and type 2 data, to be scanned to the correct B-S cell positions on the B-S chain. Filler data is a placeholder for test response data.

#### Scan-Sequence Modifier (SSM) (continued)

A test algorithm or test generator generates type 1 data. The generated data is a function of the test algorithm and number of nets, and is independent of the type of nets, their ordering, etc. Type 2 and type 3 data is typically provided by test generation software that format the test sequences. It is the critical necessity of type 2 and type 3 data that makes it difficult to automatically generate interconnect test sequences in a board- or system-level BIST environment. The technique that the BSM2 uses takes advantage of the fact that type 2 and type 3 data are static. Consequently, if the value of this data and its location is recorded once, then it can be easily inserted into the output scan sequence, and used for identifying the cells with useful test information that should be compressed by the signature analysis register (SAR).

#### **SSM-ATPG Mode**

Figure 2 shows the SSM configuration with ATPG as the TDO source and SAR as the TDI destination. To achieve this configuration SSM is enabled by setting the SSME bit.

Assume there are *L* scan cells on the currently selected/attached B-S chain. The type 2 (control) data are placed in two buffers, occupying *L* bits of each buffer. The TVO/TVI memories (each 8K) of the BSM2 serve as the buffers. There is a one-to-one mapping between the *L* locations of these buffers and the *L* scan cells on the selected/ attached B-S chain. The controlling processor initializes TVI and TVO with type 2 data derived from UUT structural information. TVI identifies the control cells while TVO identifies input/output cells and supplies the data for control cells.

A 1 in location n in TVI identifies a control cell at position n in the selected/attached B-S chain. The value in TVO at the same location (n) contains the logic value that must be shifted into that control cell to avoid conflict during testing.

A 0 in location *m* in TVI implies that the cell in position *m* of the selected/attached B-S chain is either an input cell or output cell during the given test. A 1 in location *m* in TVO identifies the cell as an output cell and ATPG is enabled to supply test data for that cell location. A 0 in location *m* in TVI combined with a 0 in location *m* in TVO identifies the corresponding cell of the selected/attached B-S chain as an input cell. Since the data for such a cell is type 3, or filler data, any value can be applied to the scan cell at the corresponding B-S chain location. The BSM2 will always generate a 0 for filler data.

The table below defines the operation of the SSM and its interaction with SAR and the test pattern generator in the ATPG mode.

Table 1. ATPG Mode with SSM Enabled: How i<sup>th</sup> Bits of TVI and TVO Encode Cell Type and Control Source of TDO and Actions of ATPG and SAR Functions

| TVI(i) | TVO(i) | Cell Type | ATPG    | SAR     | Source of TDO |

|--------|--------|-----------|---------|---------|---------------|

| 1      | 1 or 0 | control   | disable | disable | TDO(i)        |

| 0      | 1      | output    | enable  | disable | ATPG(i)       |

| 0      | 0      | input     | disable | enable  | constant 0    |

Scan-Sequence Modifier (SSM) (continued)

#### SSM—Deterministic Mode with SAR as TDI Destination

The SSM serves a dual purpose. Not only does it select the appropriate source for data to be shifted out of the BSM2, it also has the information needed to select those bits in the stream of data being scanned into the BSM2 that correspond to bits sampled by input cells on the selected/attached B-S chain. To aid in understanding how this works, an important fact to observe is that, at any instant, when a test vector is being shifted into a selected/attached B-S chain, the B-S cell whose value is being shifted out of the BSM2 at TDO and into the B-S chain is the same B-S cell which has its previously captured response (if any) being shifted out of the B-S chain and into the BSM2, at TDI. For this reason, the TVI/TVO map that identifies the cell type and controls the value shifted into the selected/attached B-S chain, also identifies the cell type of the cell that is the origin of the bit that is being shifted out of the B-S chain and into the BSM2. Consequently, when an input cell is identified, as described above, the SAR is enabled and the bit value is taken as part of the data stream to be compressed. When the cell is identified as control or output, the SAR is disabled for that bit.

WARNING: When using ATPG, it is important to set autoincrementing on for both TVO and TVI. Otherwise, the first word of the maps in the two buffers will be used over and over as a map for the entire scan path. This may lead to undesirable changes of state in control cells along the B-S path with subsequent damage to the product.

When the BSM2 is used in normal (deterministic) scan operation with SAR as TDI destination, the output vectors, stored in TVO, are assumed to be correctly formatted so that no conflicts occur. Hence, the problem is limited to identifying the cells that have useful test information. When serial response vectors are to be compressed, TVI is used to store this information. A 1 in a location in TVI enables the SAR, and the information in the cell at the corresponding scan path location is compressed (Table 2). This feature can be used to identify the position of the input cells during interconnect test using the EXTEST instruction combined with signature analysis.

Note: The retimed delay function is not applicable to scan operation in which the SAR is the target for data scanned into TDI.

The table below defines the operation of the SSM and its interaction with SAR in this mode.

Table 2. Deterministic Mode with SSM Enabled: How i<sup>th</sup> Bit of TVI Encodes Source Cell in B-S Chain and Directs Operation of SAR

| Source of Test Stimulus | Receiving Test Output | TVI(i) | SAR     |

|-------------------------|-----------------------|--------|---------|

| TVO(i)                  | SAR                   | 1      | enable  |

| TVO(i)                  | SAR                   | 0      | disable |

#### **ATPG: Hardware Generation of Test Sequences**

This section describes the hardware support provided by the BSM2 for generating a set of commonly used test vector sequences. The BSM2 provides support for generating the following sequences in ATPG mode:

- Walking-ones (walking-zeros) sequence

- Upcount (downcount) sequence

- Pseudorandom sequence (and its complement)

- Constant 1 (or 0) output

#### Hardware Generation of Test Sequences (continued)

The complementary sequences are created by enabling ATPG with BSM2 output inversion also enabled (see under the heading TDO Inversion).

Throughout this section, N stands for the number of nets tested by means of a selected/attached B-S chain.

#### Walking Sequence ATPG

The walking-one (zero) sequence has special significance for interconnect test and is also useful for other purposes. Given *N* nets, the algorithm generates an *N* x *N* matrix with the diagonal of 1 (0). All other elements of the matrix are 0 (1). The hardware to generate this sequence is shown in Figure 3. It consists of two downcounters, NC (which is loaded via NCR) and LPC. Both NCR and LPC must be initialized to *N* by the user. After NC downcounts to zero, it is reloaded with the contents of NCR, and LPC is decremented. (SDR, as always, contains the length of the selected/attached B-S path.) NC and LPC are input to a comparator that outputs a 1 only when the two counters are equal. The sequence of bits produced from this output is the serialized test pattern.

The operation is as follows: The controlling processor initializes both NCR (and implicitly NC) and LPC to N. Since initially NC = LPC, a 1 is output and this is the first bit output from the test generator. After that, each time the ATPG is enabled by the SSM, the NC is decremented and the comparator output is shifted out as a bit of the test vector. After the test vector is generated (identified by SDC = NC = 0), LPC is decremented to N - 1, and NC is reinitialized to N by NCR. The operation repeats, except that now a 1 is output when NC = N - 1. This operation repeats until both counters are zero. This algorithm will generate N patterns, each of length N and the i<sup>th</sup> pattern has a 1 in location i, and 0 in all other locations. The SSM ensures that the test vector bits are correctly positioned in each serial test vector. This is the walking-one sequence. Note that the complementary sequence, walking zeros, can be trivially constructed by complementing the output.

5-6312 (F)

Figure 3. Walking Sequence Test Generator

5-6313 (F)

# Automatic Test Pattern Generation (ATPG), Scan Sequence Modification (SSM), and Signature Analysis (continued)

Hardware Generation of Test Sequences (continued)

#### **Counting Sequence ATPG**

Application of an ATPG counting sequence is done by assigning a unique sequential (serial) test vector (STV) to each net such that the set of STVs follows a counting sequence. The counting sequence test has a short test length O (log N), where N is the number of nets. It should be noted that there is no "zero<sup>th</sup>" net.

**Figure 4. Counting Sequence Test Generator**

Figure 4 shows the structure of the test generator. It uses the same counters as the walking sequence, NC (with the NCR) and LPC, but in a different configuration. The NCR is initialized to N, and the LPC is initialized to

$\lceil \log (N + 2) \rceil$ .

The outputs of NC are fed to a multiplexor. The outputs of LPC

$(\lceil \log \log (N + 2) \rceil \text{ bits})$

are the control inputs of the multiplexor which selects one of the

$\lceil \log (N + 2) \rceil$

outputs of NC as the test output. Since the all-zero STV is prohibited, an additional logic block (NC = 1 detector) is included to detect the state when NC = 1. When NC=1, NC is reinitialized to the initial count value from NCR, and LPC is decremented.

The operation is as follows: The test master initializes NC to N and LPC to

$\lceil \log (N+2) \rceil$ .

The least significant bit of NC is chosen by the multiplexor as the test vector source and, on demand from the SSM, NC is decremented and the column is shifted out as the serial test vector. When NC counts down to one, it is reinitialized to N, and LPC is decremented. Now the multiplexor selects the second least significant bit of NC to shift out as the test vector. This sequence repeats till both NC and LPC downcount to zero. During this operation, NC counts down from N to 1,

$\lceil \log (N + 2) \rceil$

times and each time one of the

$\lceil \log (N + 2) \rceil$

### Hardware Generation of Test Sequences (continued)

lines input to the multiplexor are selected as the test output. This generates the set of N-bit serial test vectors comprising the serialized counting sequence. As before, the complementary sequence can be constructed by inverting the output.

#### **Pseudorandom ATPG**

The third sequence that the SSM facilitates is the pseudorandom sequence. This can be applied to the interconnect and the response compressed to a signature to give a pass/fail indication. The techniques for designing a pseudorandom test generator are well known and are not described in this document. The BSM2 has a 32-bit PRPG, the seed of which can be programmed. This generator can prove especially useful for cluster test and for testing the internal logic of some devices that do not have BIST.

#### **Constant Output**

Another useful mode of the ATPG is that in which a constant 1 or constant 0 is shifted out via TDO. This would be used when the BYPASS (all 1) or EXTEST (all 0) instruction is being scanned into the IR of all the devices in a selected/attached B-S chain.

**Note:** While constant output ATPG is selected, the SSM function must be disabled.

#### **Programming ATPG and SSM Functions**

The selection of the source of test vectors and the destination of the test response is programmed in the CUTI register, bits TIOM[2:0]. The ATPG type that is to be selected is programmed in the configuration registers, bits AMD[1:0]. Enabling/disabling of the SSM is also controlled by the CUTI register, bit SSME. Finally, bit AC in CUTI controls whether or not the output of the ATPG is complemented. More details concerning these registers are provided in Appendix B—BSM2 Internal Register Descriptions.

The operation of the ATPG is synchronized with the TAP State Tracker. When the TAP State Tracker indicates that all the TAP controllers on the selected/attached B-S chain have entered the Shift-DR TAP

controller state, and the TDO source has been set as ATPG, the ATPG starts generating serialized algorithmic or pseudorandom test vectors. The response to the test sequences generated by the ATPG is compressed to a signature. The SAR is enabled only after the first test vector is scanned out of the selected/ attached B-S chain. This is important in ensuring that the unknown values that are scanned out when the first vector is scanned in do not corrupt the signature. Also, after the last ATPG vector is scanned in, another vector needs to be shifted in to scan out the last response. This housekeeping is performed automatically in the BSM2 and is transparent to the user. For the last vector, a constant value is scanned into the B-S chain to allow access to the last response. In the BSM2, this value is 1.

#### **Low Power Mode**

To minimize power dissipation from the BSM2 several approaches can be taken.

CMOS power dissipation is strongly dependent on input voltage levels. Maintaining logic levels within 0.5 V of VDD and Vss will minimize power dissipation in any mode of operation.

The output loads, particularly the TAP signals, are a large factor determining the power dissipation of the device. 3-stating or disabling these signals when they are not used will minimize power consumption.

To reduce power dissipation below 43 mW, four complimentary approaches can be used when the device is not executing a scan operation. To reduce power dissipation to <5 mW, the external master clock for the BSM2 should be disabled.

To achieve low (<43 mW) power dissipation,

- All TAP output signals should be 3-stated. (This is accomplished using the TOE\* pin and the TOEB bit in the 1215E and the TOEB bit alone in the 497AE.)

- CE\* should not become active.

- No internal registers should change state.