# 54HSC/T Series RADIATION HARD HIGH SPEED CMOS/SOS LOGIC

The CMOS/SOS HSC/T Series offer the combined benefits of low power, high speed CMOS with the inherent latch up immunity, Single Event Upset (SEU) immunity and the high level of radiation hardness of Silicon on Sapphire technology. The 54HSC/T Series of circuits are pin for pin compatible with the 54LS series range.

HSC and HST devices have CMOS and TTL compatible inputs/outputs respectively.

### **FEATURES**

- Radiation Hard to 1MRad (Si)

- High SEU Immunity, Latch Up Free

- Low Power CMOS/SOS Technology

- Plug In Replacement for 54/74LS, HC and HCT

54HSC/T00 Quadruple 2-input positive NAND gates

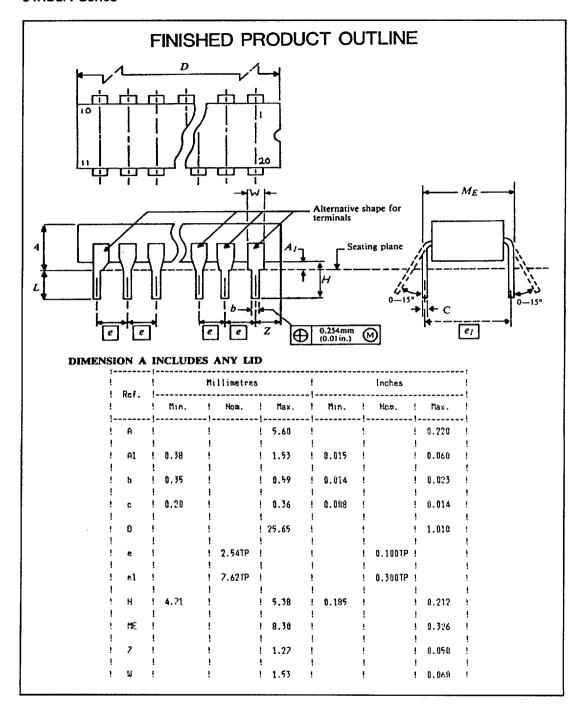

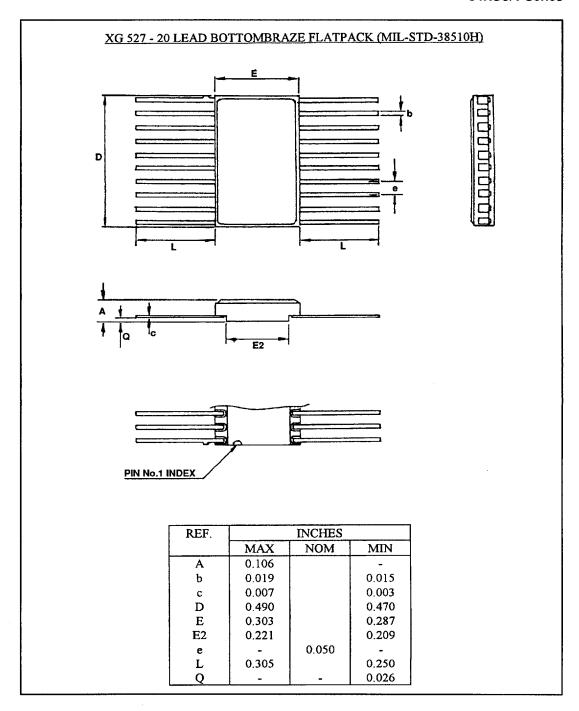

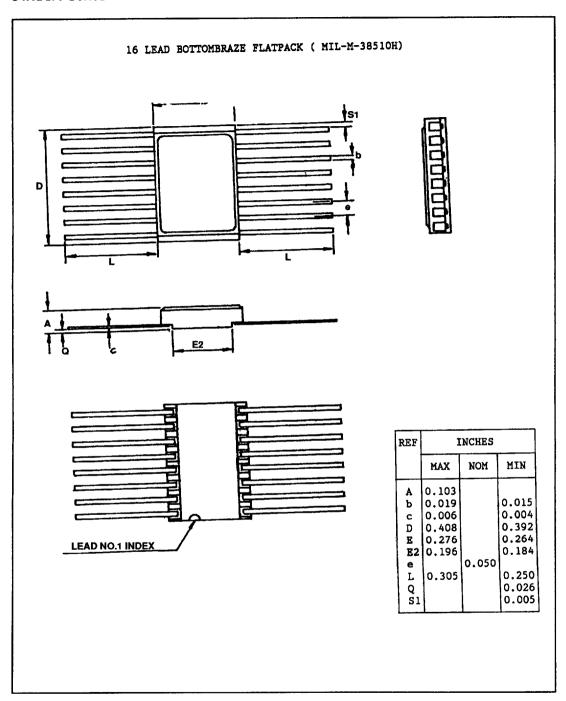

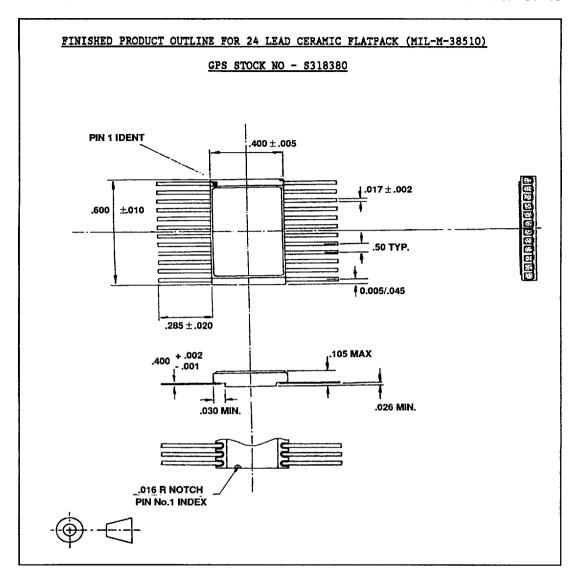

Dual In Line or Flatpack Packages

### **Gates and Buffers**

EALICOTTOO

| 54FISC/102 | Quadruple 2-input positive NOH gates              |

|------------|---------------------------------------------------|

| 54HSC/TO3  | Quadruple 2-input positive NAND gates with        |

|            | open collector outputs                            |

| 54HSC/T04  | Hex Inverters                                     |

| 54HSC/T08  | Quadruple 2-input positive AND gates              |

| 54HSC/T10  | Triple 3-input positive NAND gates                |

| 54HSC14    | Hex schmitt-trigger inverters                     |

| 54HSC/T21  | Dual 4-input positive AND gates                   |

| 54HSC/T27  | Triple 3-input positive NOR gates                 |

| 54HSC/T32  | Quadruple 2-input positive OR gates               |

| 54HSC/T86  | Quadruple 2-input Exclusive OR gates              |

| 54HSC/T125 | Quadruple bus buffer gates with tri-state outputs |

|            | (Active low enable)                               |

| 54HSC/T126 | Quadruple bus buffer gates with tri-state outputs |

|            |                                                   |

### Flip-Flops

| 54HSC/T74  | Dual D-type flip-flops with preset and clear |

|------------|----------------------------------------------|

| 54HSC/T109 | Dual J-KB flip-flop with preset and clear    |

| 54HSC/T273 | Octal D-type flip-flops                      |

| 54HSC/T374 | Octal D-type edge triggered flip-flops       |

| 54HSC/T574 | Octal D-type edge triggered flip-flops       |

(Active high enable)

#### Adders

54HSC/T283 4-bit binary full adders with fast carry

#### Counters

| 54HSC/T161 | 4-bit synchronous binary counter |

|------------|----------------------------------|

| 54HSC/T163 | Synchronous 4-bit counter        |

| 54HSC/T191 | Synchronous 4-bit counter        |

### Decoders/Demultiplexers

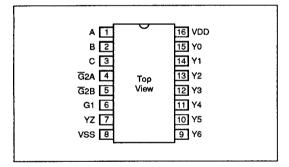

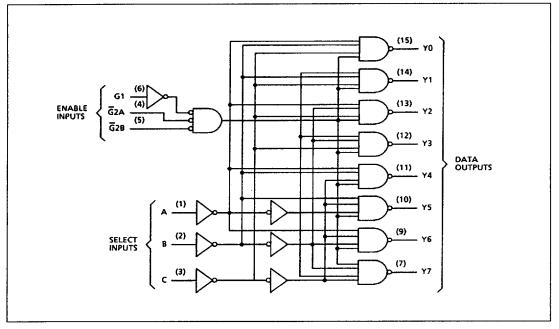

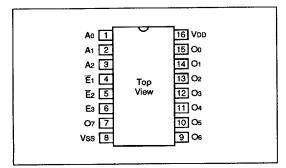

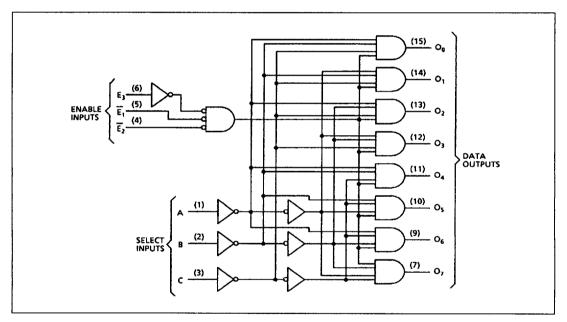

| 54HSC/1138 | 3-line to 8-line decoder/multiplexer     |

|------------|------------------------------------------|

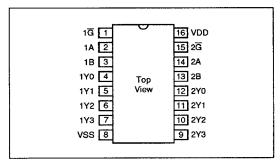

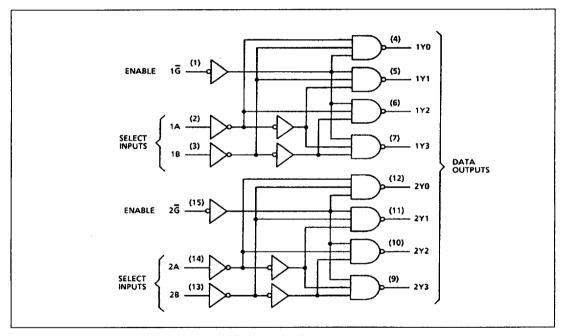

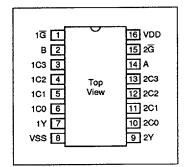

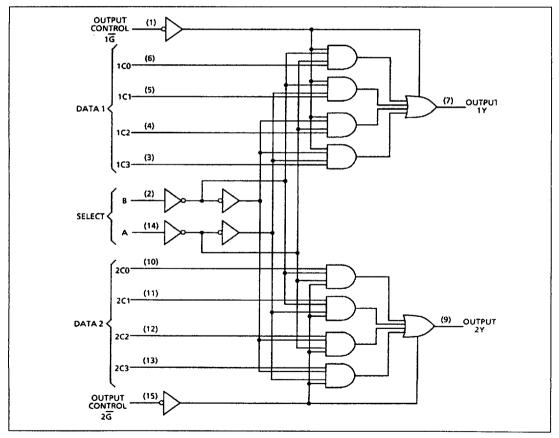

| 54HSC/T139 | Dual 2 to 4 decoders/multiplexers        |

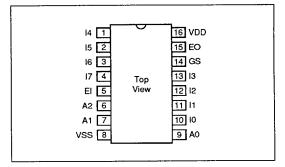

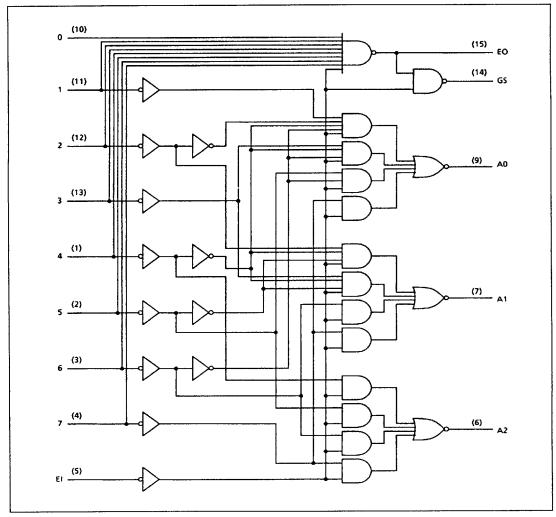

| 54HSC/T148 | 8-line to 3-line octal priority encoders |

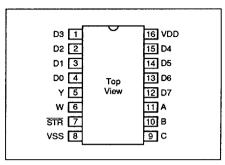

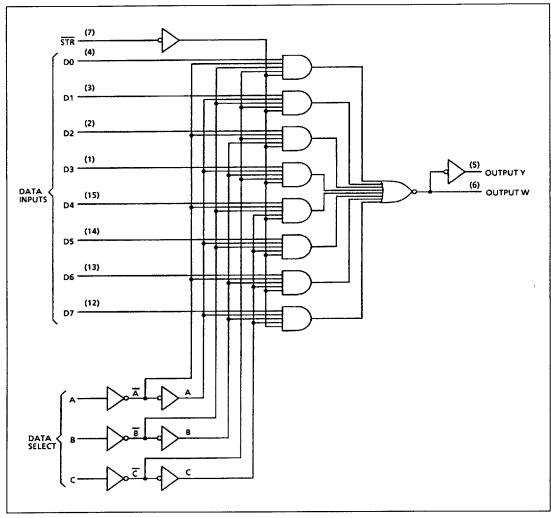

| 54HSC/T151 | 1 of 8 data selectors/multiplexers       |

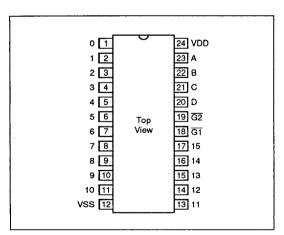

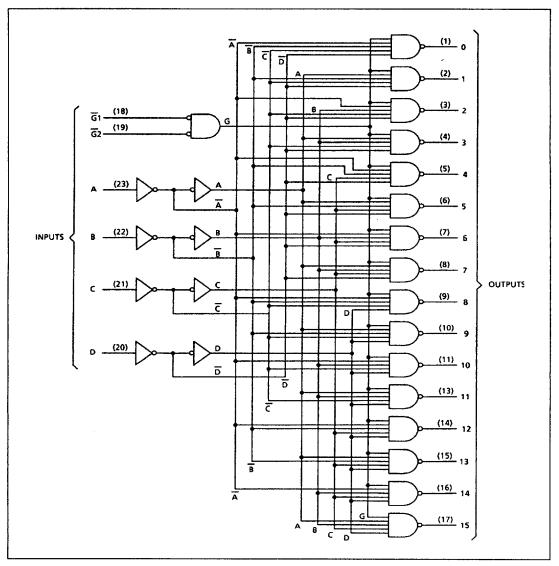

| 54HSC/T154 | 4 to 16-line decoders/demultiplexers     |

|            |                                          |

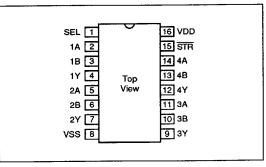

54HSC/T157 Quad 2-line to 1-line data selectors/multiplexers

54HSC/T238 3 to 8 decoder/demultiplexer

54HSC/T253 Dual 4 to 1 data selectors/multiplexers

#### Registers

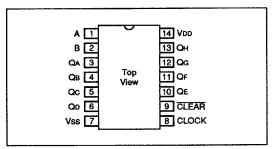

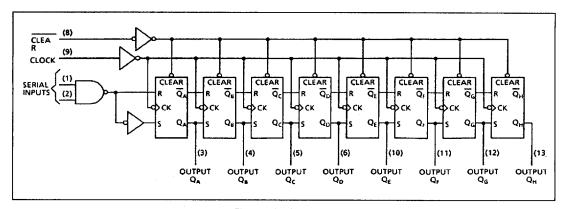

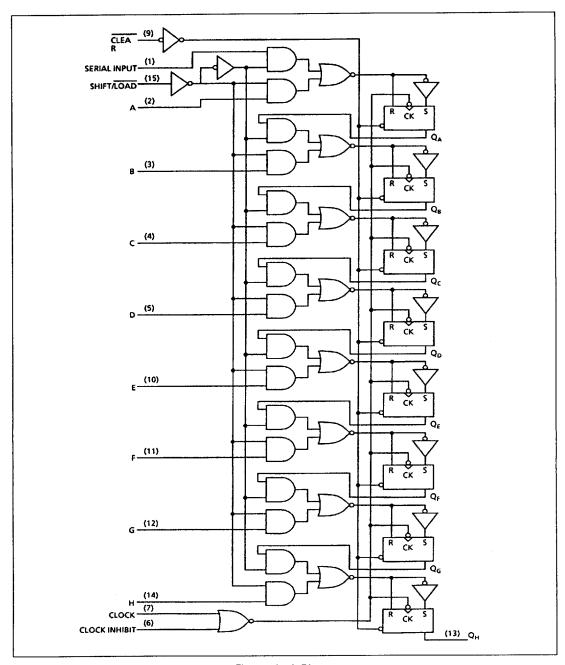

| 54HSC/T164 | 8-bit parallel output serial shift register |

|------------|---------------------------------------------|

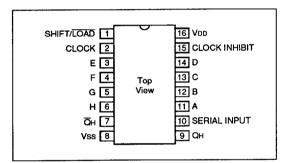

| 54HSC/T165 | Parallel load 8-bit shift register          |

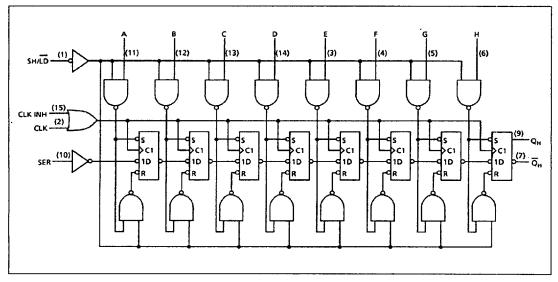

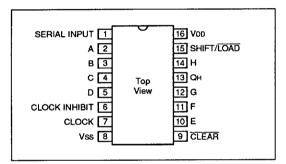

| 5/H5C/T166 | R-hit chift register                        |

### Comparators

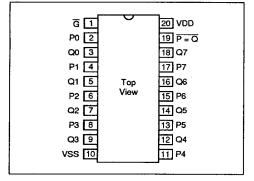

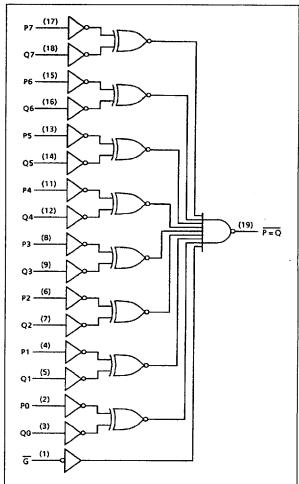

54HSC/T521 8-bit magnitude comparator

### Line Drivers

| 54HSC/T240 | Octal 3-state driver inverting            |

|------------|-------------------------------------------|

|            | Octal 3-state driver complementary enable |

| 54HSC/T244 | Octal 3-state driver                      |

| 54HSC/T540 | Octal 3-state driver/buffer inverting     |

| 54HSC/T541 | Octal 3-state driver/buffer               |

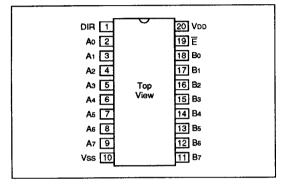

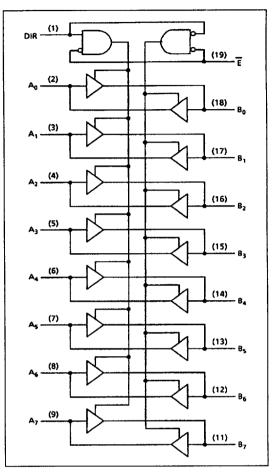

### **Transceivers**

54HSC/T245 Octal bus transceiver

### Latches

54HSC/T373 Octal transparent latch, 3-state outputs 54HSC/T573 Octal transparent latch, 3-state outputs

### Miscellaneous

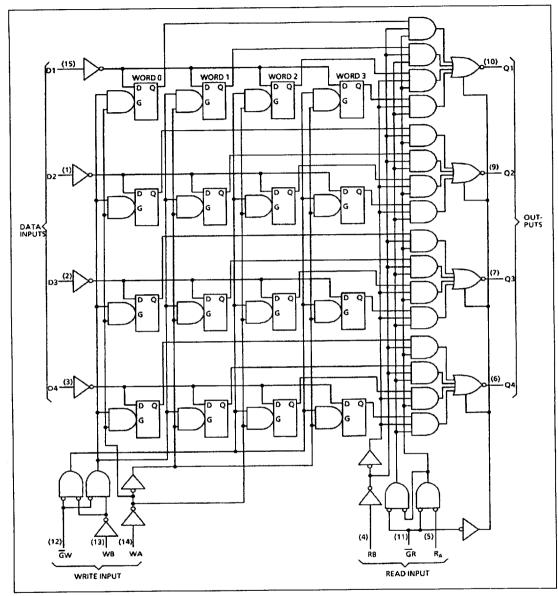

54HSC/T670 4 x 4 register files with tri-state outputs

### 54HSC/T Series

### DC CHARACTERISTICS AND RATINGS

| Parameter               | Min. | Max.                 | Units |

|-------------------------|------|----------------------|-------|

| Supply Voltage          | -0.5 | 10                   | ٧     |

| Input Voltage           | -0.3 | V <sub>DD</sub> +0.3 | ٧     |

| Current Through Any Pin | -25  | +25                  | mA    |

| Operating Temperature   | -55  | 125                  | °C    |

| Storage Temperature     | -65  | 150                  | °C    |

Figure 1: Absolute Maximum Ratings

Note: Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions, or at any other condition above those indicated in the operations section of this specification, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

|                  |                        |                                                                                                                  | Total do                           | se radia<br>ng 3x10 <sup>5</sup> |                   |        |

|------------------|------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------|-------------------|--------|

| Symbol           | Parameter              | Conditions                                                                                                       | Min.                               | Тур.                             | Max.              | Units  |

| V <sub>DD</sub>  | Supply Voltage         | -                                                                                                                | 4.5                                | 5.0                              | 5.5               | V      |

| V <sub>IH1</sub> | HST Input High Voltage | -                                                                                                                | 2.0                                | -                                | -                 | ٧      |

| V <sub>IL1</sub> | HST Input Low Voltage  | -                                                                                                                | -                                  | -                                | 0.8               | V      |

| V <sub>IH2</sub> | HSC Input High Voltage | -                                                                                                                | 3.5                                | -                                | -                 | ٧      |

| V <sub>IL2</sub> | HSC Input Low Voltage  | -                                                                                                                | -                                  | -                                | 1.5               | ٧      |

| V <sub>oH</sub>  | Output High Voltage    | $V_{IN} = V_{IH} \text{ or } V_{IL}$ $I_{OH} = -20\mu\text{A}^*$ $I_{OH} = 6\text{mA}^*$ $I_{OH} = -11\text{mA}$ | V <sub>DD</sub> -0.1<br>3.7<br>2.5 |                                  | -                 | ><br>> |

| V <sub>OL</sub>  | Output Low Voltage     | $V_{IN} = V_{IH} \text{ or } V_{IL}$ $I_{OL} = -20\mu\text{A}^*$ $I_{OL} = 6\text{mA}^*$ $I_{OL} = 9\text{mA}$   | -                                  | -<br>-<br>-                      | 0.1<br>0.2<br>0.4 | >>>    |

| I <sub>IL</sub>  | Input Leakage Current  | $V_{IN} = V_{DD}$ or $V_{SS}$<br>All inputs                                                                      | -                                  | 1                                | 5                 | μА     |

| l <sub>OL</sub>  | Output Leakage Current | V <sub>OUT</sub> = V <sub>DD</sub> or V <sub>SS</sub><br>Outputs disabled                                        | -                                  | 20                               | 50                | μА     |

| I <sub>DD</sub>  | Quiescent Current      | V <sub>IN</sub> = V <sub>DD</sub><br>Outputs unloaded                                                            | -                                  | †                                | †                 | μА     |

$V_{DD} = 5V\pm10\%$ , over full operating temperature range.

Figure 2: Electrical Characteristics

<sup>\*</sup> Guaranteed but not tested.

<sup>†</sup> Refer to individual device types (-55°C / +125°C).

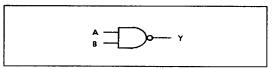

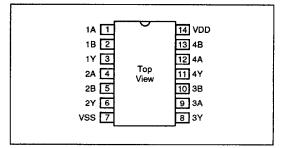

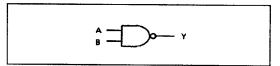

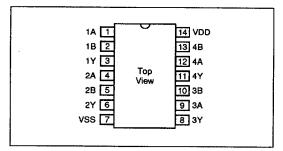

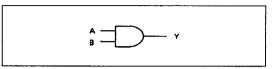

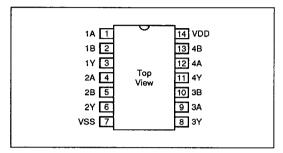

## 54HSC/T00: Quadruple 2-Input Positive NAND Gates

The 54HSC/T00 is a Quadruple 2-Input Positive NAND gate.

| Inp | uts | Outputs |

|-----|-----|---------|

| Α   | В   | Y       |

| L   | L   | Н       |

| L   | н   | н       |

| н   | L   | н       |

| Н   | н   | L       |

H = high level, L = low level

Figure 1: Function Table

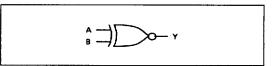

Figure 2: Logic Diagram

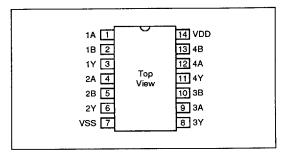

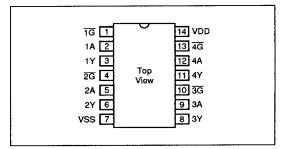

Figure 3: Pin Out

|                  |                                                  | +2   | +25°C |      | -55°C / +125°C |       |

|------------------|--------------------------------------------------|------|-------|------|----------------|-------|

| Symbol           | Parameter                                        | Тур. | Max.  | Тур. | Max.           | Units |

| t <sub>PLH</sub> | Propagation delay time, low to high level output | 11   | 20    | 17   | 22             | ns    |

| t <sub>PHL</sub> | Propagation delay time, high to low level output | 10   | 18    | 18   | 20             | ns    |

Figure 4: Switching Characteristics

|                  |                           |                                                      | Limits |      |         |        |       |

|------------------|---------------------------|------------------------------------------------------|--------|------|---------|--------|-------|

|                  |                           |                                                      | +2     | 5°C  | -55°C / | +125°C |       |

| Symbol           | Parameter                 | Test Conditions                                      | Min.   | Max. | Min.    | Мах.   | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub>              | -      | 10   | -       | 300    | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                                | -      | 0.4  | -       | 0.4    | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                              | 2.5    | -    | 2.5     | -      | V     |

| $V_{\rm IL1}$    | Voltage Input Low (CMOS)  |                                                      |        | 1.5  | -       | 1.5    | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                                    | 3.5    | -    | 3.5     | -      | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                                    | -      | 0.8  | - 1     | 0.8    | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                                    | 2.0    |      | 2.0     | -      | l v   |

| IN               | Input Leakage Current     | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> | -      | ±0.5 | -       | ±5.0   | μА    |

Figure 5: DC Characteristics

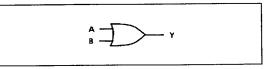

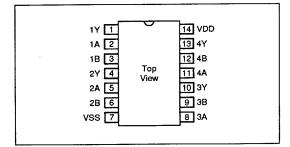

# 54HSC/T02: Quadruple 2-Input Positive NOR Gates

The 54HSC/T02 is a Quadruple 2-Input Positive NOR gate.

| Inp | uts | Outputs |

|-----|-----|---------|

| A   | В   | Y       |

| L   | L   | Н       |

| L   | н   | L       |

| н   | L   | L       |

| Н   | Н   | L       |

H = high level, L = low level

Figure 1: Function Table

Figure 2: Logic Diagram .

Figure 3: Pin Out

|                  |                                                  | +25°C -55°C |      | -55°C / | +125°C |       |

|------------------|--------------------------------------------------|-------------|------|---------|--------|-------|

| Symbol           | Parameter                                        | Тур.        | Max. | Тур.    | Max.   | Units |

| t <sub>PLH</sub> | Propagation delay time, low to high level output | 11          | 20   | 17      | 22     | ns    |

| t <sub>PHL</sub> | Propagation delay time, high to low level output | 10          | 18   | 18      | 20     | ns    |

Figure 4: Switching Characteristics

|                  |                           |                                                      |       |      | -    |                |       |

|------------------|---------------------------|------------------------------------------------------|-------|------|------|----------------|-------|

|                  |                           |                                                      | +25°C |      |      | -55°C / +125°C |       |

| Symbol           | Parameter                 | Test Conditions                                      | Min.  | Max. | Min. | Max.           | Units |

| 1 <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub>              | -     | 10   | -    | 300            | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                                | -     | 0.4  | -    | 0.4            | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                              | 2.5   | -    | 2.5  | -              | v     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                                    | -     | 1.5  | -    | 1.5            | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                                    | 3.5   | -    | 3.5  | -              | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                                    | -     | 0.8  | -    | 0.8            | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                                    | 2.0   | -    | 2.0  | -              | V     |

| I <sub>IN</sub>  | Input Leakage Current     | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> | -     | ±0.5 | -    | ±5.0           | μА    |

Figure 5: DC Characteristics

# 54HSC/T03: Quadruple 2-Input Positive NAND Gates With Open Collector Outputs

The 54HSC/T03 is a Quadruple 2-Input Positive NAND gate with open collector output.

| lnp | uts | Outputs |

|-----|-----|---------|

| A   | В   | Y       |

| L   | L   | н       |

| L   | н   | н       |

| н   | L   | н       |

| н   | н   | L       |

H = high level, L = low level

Figure 1: Function Table

Figure 2: Logic Diagram

Figure 3: Pin Out

|                  |                                                  | +2   | +25°C |      | -55°C / +125°C |       |

|------------------|--------------------------------------------------|------|-------|------|----------------|-------|

| Symbol           | Parameter                                        | Тур. | Max.  | Тур. | Max.           | Units |

| t <sub>PLH</sub> | Propagation delay time, low to high level output | 11   | 20    | 17   | 22             | ns    |

| t <sub>PHL</sub> | Propagation delay time, high to low level output | 10   | 18    | 18   | 20             | ns    |

Figure 4: Switching Characteristics

|                  |                           |                                                      | +25°C |      | -55°C / +125°C |      |       |

|------------------|---------------------------|------------------------------------------------------|-------|------|----------------|------|-------|

| Symbol           | Parameter                 | Test Conditions                                      | Min.  | Max. | Min.           | Max. | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub>              | -     | 10   | -              | 300  | μА    |

| Vol              | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                                | -     | 0.4  | -              | 0.4  | v     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                              | 2.5   | -    | 2.5            | -    | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  |                                                      |       | 1.5  | -              | 1.5  | l v   |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                                    | 3.5   | -    | 3.5            | _    | l v   |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                                    | -     | 0.8  | -              | 0.8  | l v   |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                                    | 2.0   | -    | 2.0            | -    | l v   |

| I <sub>iN</sub>  | Input Leakage Current     | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> | -     | ±0.5 | -              | ±0.5 | μΑ    |

Figure 5: DC Characteristics

### 54HSC/T Series

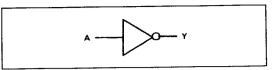

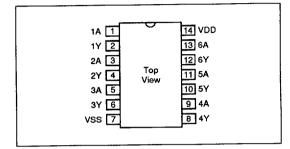

## 54HSC/T04: Hex Inverters

The 54HSC/T04 consists of six Hex Inverters.

| Inputs | Outputs |

|--------|---------|

| A      | Υ       |

| Н      | L       |

| L      | н       |

H = high level, L = low level

Figure 1: Function Table

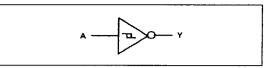

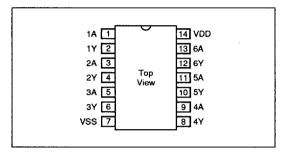

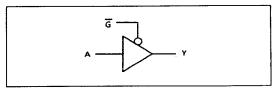

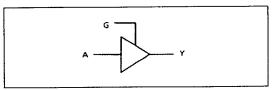

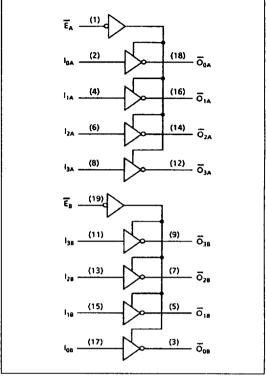

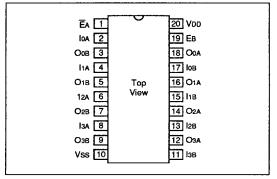

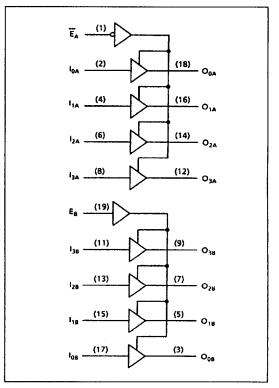

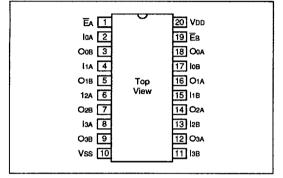

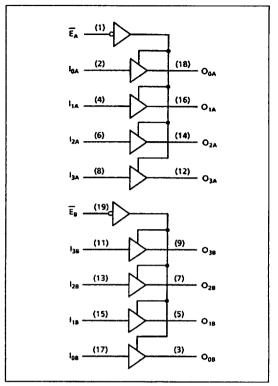

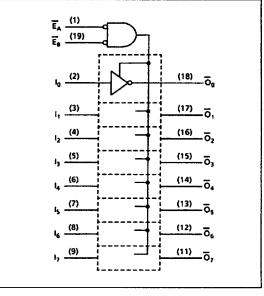

Figure 2: Logic Diagram

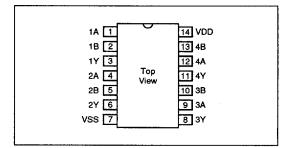

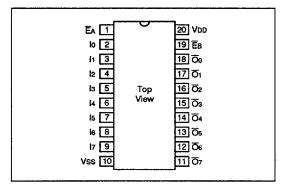

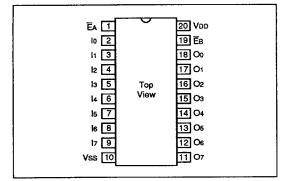

Figure 3: Pin Out

|                  |                                                                                                   | +25°C    |          | -55°C / +125°C |          |          |

|------------------|---------------------------------------------------------------------------------------------------|----------|----------|----------------|----------|----------|

| Symbol           | Parameter                                                                                         | Тур.     | Max.     | Тур.           | Max.     | Units    |

| t <sub>PLH</sub> | Propagation delay time, low to high level output Propagation delay time, high to low level output | 11<br>10 | 20<br>18 | 17<br>18       | 22<br>20 | ns<br>ns |

Figure 4: Switching Characteristics

|                  |                           |                                         | +25  |      | +25°C -55°C/ |      |       |

|------------------|---------------------------|-----------------------------------------|------|------|--------------|------|-------|

| Symbol           | Parameter                 | Test Conditions                         | Min. | Max. | Min.         | Max. | Units |

| l <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub> | -    | 10   | -            | 300  | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                   | -    | 0.4  | -            | 0.4  | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                 | 2.5  | -    | 2.5          | -    | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                       | -    | 1.5  | -            | 1.5  | v     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                       | 3.5  | -    | 3.5          | -    | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   |                                         | -    | 0.8  | -            | 0.8  | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                       | 2.0  | -    | 2.0          | -    | V     |

| i <sub>IN</sub>  | Input Leakage Current     | $V_{iN} = V_{DD}$ or $V_{SS}$           | -    | ±0.5 | -            | ±5.0 | μА    |

Figure 5: DC Characteristics

## 54HSC/T08: Quadruple 2-Input Positive AND Gates

The 54HSC/T08 is a Quadruple 2-Input Positive AND gate.

| lnp | uts | Outputs |

|-----|-----|---------|

| A   | В   | Υ       |

| L   | L   | L       |

| L   | н   | L       |

| Н   | L   | L       |

| Н   | н   | Н       |

H = high level, L = low level

Figure 1: Function Table

Figure 2: Logic Diagram

Figure 3: Pin Out

|                                      |                                                                                                      | +2       | +25°C    |          | -55°C / +125°C |          |

|--------------------------------------|------------------------------------------------------------------------------------------------------|----------|----------|----------|----------------|----------|

| Symbol                               | Parameter                                                                                            | Тур.     | Max.     | Тур.     | Max.           | Units    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay time, low to high level output<br>Propagation delay time, high to low level output | 11<br>10 | 20<br>18 | 17<br>18 | 22<br>20       | ns<br>ns |

Figure 4: Switching Characteristics

|                  |                           |                                                      |      | +25°C |      | +125°C |       |

|------------------|---------------------------|------------------------------------------------------|------|-------|------|--------|-------|

| Symbol           | Parameter                 | Test Conditions                                      | Min. | Max.  | Min. | Max.   | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub>              | -    | 10    | -    | 300    | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                                | -    | 0.4   | -    | 0.4    | v     |

| $V_{OH}$         | Output Voltage High Level | I <sub>OH</sub> = -11mA                              | 2.5  | -     | 2.5  |        | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  |                                                      | -    | 1.5   | -    | 1.5    | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                                    | 3.5  | -     | 3.5  | -      | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                                    | -    | 0.8   | -    | 0.8    | v     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                                    | 2.0  | -     | 2.0  | -      | v     |

| I <sub>IN</sub>  | Input Leakage Current     | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> | -    | ±0.5  | -    | ±5.0   | μА    |

Figure 5: DC Characteristics

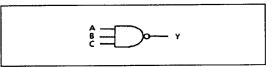

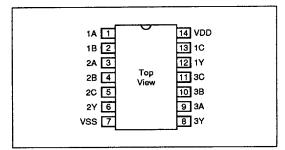

# 54HSC/T10 : Triple 3-Input Positive NAND Gates

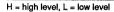

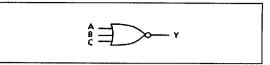

The 54HSC/T10 is a Triple 3-Input Positive NAND gate.

|   | Inputs | Outputs |   |

|---|--------|---------|---|

| Α | В      | С       | Υ |

| L | х      | х       | Н |

| X | L      | x       | н |

| X | х      | L       | н |

| Н | н      | н       | L |

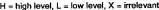

H = high level, L = low level, X = irrelevant

Figure 1: Function Table

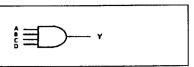

Figure 2: Logic Diagram

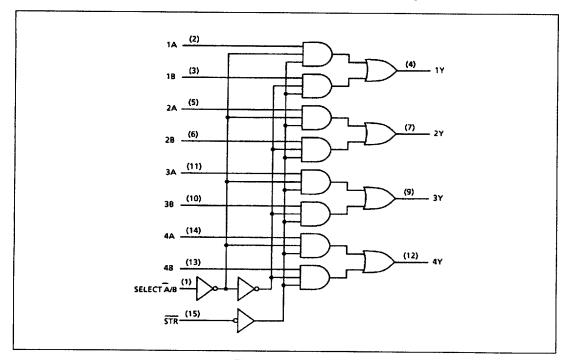

Figure 3: Pin Out

|                                      |                                                                                                      | +2       | 5°C      | -55°C /  |          |          |

|--------------------------------------|------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|

| Symbol                               | Parameter                                                                                            | Тур.     | Max.     | Тур.     | Max.     | Units    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay time, low to high level output<br>Propagation delay time, high to low level output | 11<br>10 | 20<br>18 | 17<br>18 | 22<br>20 | ns<br>ns |

Figure 4: Switching Characteristics

|                  |                           |                                         | +25°C |      | -55°C / +125°C |      |       |

|------------------|---------------------------|-----------------------------------------|-------|------|----------------|------|-------|

| Symbol           | Parameter                 | Test Conditions                         | Min.  | Max. | Min.           | Max. | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub> | -     | 10   | -              | 300  | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                   | -     | 0.4  | -              | 0.4  | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                 | 2.5   | -    | 2.5            | -    | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                       | -     | 1.5  | -              | 1.5  | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) |                                         | 3.5   | -    | 3.5            | -    | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                       | -     | 0.8  | -              | 0.8  | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  |                                         | 2.0   | -    | 2.0            | -    | V     |

| I                | Input Leakage Current     | $V_{IN} = V_{DD}$ or $V_{SS}$           | -     | ±0.5 | -              | ±5.0 | μА    |

Figure 5: DC Characteristics

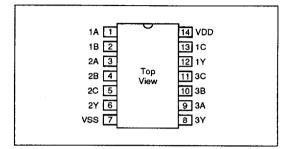

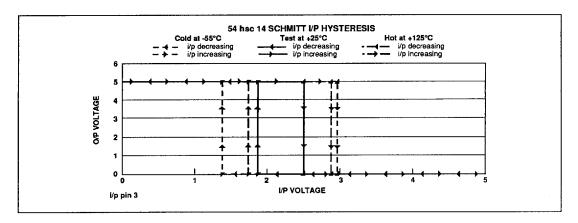

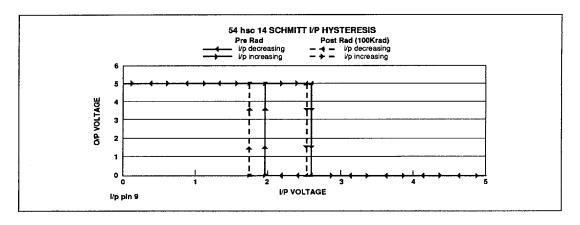

## 54HSC14: Hex Schmitt-Trigger Inverters

The 54HSC/T14 consists of six Hex Schmitt-Trigger Inverters.

| Inputs | Outputs |

|--------|---------|

| A      | Υ       |

| L      | Н       |

| Н      | L       |

H = high level, L = low level

Figure 1: Function Table

Figure 2: Logic Diagram

Figure 3: Pin Out

|                                      |                                                                                                      |          | +25°C -  |          |          |          |

|--------------------------------------|------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|

| Symbol                               | Parameter                                                                                            | Тур.     | Max.     | Тур.     | Max.     | Units    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay time, low to high level output<br>Propagation delay time, high to low level output | 11<br>10 | 20<br>18 | 17<br>18 | 22<br>20 | nş<br>ns |

Figure 4: Switching Characteristics

|                  |                           |                                                      | +2   | 5°C  | -55°C / | +125°C |       |

|------------------|---------------------------|------------------------------------------------------|------|------|---------|--------|-------|

| Symbol           | Parameter                 | Test Conditions                                      | Min. | Max. | Min.    | Max.   | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub>              | -    | 10   | -       | 300    | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                                | -    | 0.4  | -       | 0.4    | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                              | 2.5  | -    | 2.5     | -      | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                                    | -    | 1.5  | -       | 1.5    | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                                    | 3.5  | -    | 3.5     | -      | v     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                                    | -    | 0.8  | -       | 0.8    | l v   |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                                    | 2.0  | -    | 2.0     | ] -    | l v   |

| I <sub>IN</sub>  | Input Leakage Current     | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> | -    | ±0.5 | -       | ±5.0   | μΑ    |

Figure 5: DC Characteristics

## 54HSC/T21: Dual 4-Input Positive AND Gates

The 54HSC/T21 is a Dual 4-Input Positive AND gate.

|   | Inp    | uts |   | Outputs |

|---|--------|-----|---|---------|

| A | В      | С   | D | Y       |

| L | L      | L   | L | L       |

| L | L      | L   | Н | L       |

| L | L      | Н   | L | L       |

| L | L      | Н   | Н | L       |

| L | н      | L   | L | L       |

| L | н      | L   | Н | L       |

|   | н      | Н   | L | L       |

| L | Н      | Н   | н | L       |

| Н | L      | L   | L | L       |

| Н |        | L   | н | L       |

| Н | L<br>L | Н   | L | L       |

| Н | L      | Н   | Н | L       |

| Н | н      | L   | L | L       |

| Н | н      | L   | н | L       |

| Н | н      | Н   | L | L       |

| Н | Н      | Н   | н | Н       |

Figure 2: Logic Diagram

Figure 3: Pin Out

H = high level, L = low level

Figure 1: Function Table

|                  |                                                  | +25°C -55°C |      |      | 55°C / +125°C |       |

|------------------|--------------------------------------------------|-------------|------|------|---------------|-------|

| Symbol           | Parameter                                        | Тур.        | Max. | Тур. | Max.          | Units |

| t <sub>PLH</sub> | Propagation delay time, low to high level output | 11          | 20   | 17   | 22            | ns    |

| t <sub>PHL</sub> | Propagation delay time, high to low level output | 10          | 18   | 18   | 20            | ns    |

Figure 4: Switching Characteristics

|                  |                           |                                                      | +25°C |      | -55°C / +125°C |      |       |

|------------------|---------------------------|------------------------------------------------------|-------|------|----------------|------|-------|

| Symbol           | Parameter                 | Test Conditions                                      | Min.  | Max. | Min.           | Max. | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub>              | -     | 10   | -              | 300  | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                                | -     | 0.4  | -              | 0.4  | V     |

| VOH              | Output Voltage High Level | I <sub>OH</sub> = -11mA                              | 2.5   | -    | 2.5            | -    | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                                    | -     | 1.5  | -              | 1.5  | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                                    | 3.5   | -    | 3.5            | -    | v     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                                    | -     | 0.8  | -              | 0.8  | V     |

| V <sub>iH2</sub> | Voltage Input High (TTL)  | -                                                    | 2.0   | -    | 2.0            | -    | V     |

| I <sub>IN</sub>  | Input Leakage Current     | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> | -     | ±0.5 | -              | ±5.0 | μА    |

Figure 5: DC Characteristics

## 54HSC/T27: Triple 3-Input Positive NOR Gates

The 54HSC/T27 is a Triple 3-Input Positive NOR gate.

|   | Inputs |   | Outputs |

|---|--------|---|---------|

| Α | В      | С | Y       |

| L | L      | L | Н       |

| L | L      | н | L       |

| L | н      | L | L       |

| L | н      | н | L       |

| н | L      | L | L       |

| Н | L      | н | L       |

| н | Н      | L | L       |

| н | Н      | Н | Ľ       |

Figure 1: Function Table

Figure 2: Logic Diagram

Figure 3: Pin Out

|                                      |                                                                                                      | +25°C    |          | -55°C /  | -55°C / +125°C |          |

|--------------------------------------|------------------------------------------------------------------------------------------------------|----------|----------|----------|----------------|----------|

| Symbol                               | Parameter                                                                                            | Тур.     | Max.     | Тур.     | Max.           | Units    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay time, low to high level output<br>Propagation delay time, high to low level output | 11<br>10 | 20<br>18 | 17<br>18 | 22<br>20       | ns<br>ns |

Figure 4: Switching Characteristics

|                  |                           |                                                      | +25°C |      | -55°C/+125°C |      | 1     |

|------------------|---------------------------|------------------------------------------------------|-------|------|--------------|------|-------|

| Symbol           | Parameter                 | Test Conditions                                      | Min.  | Max. | Min.         | Max. | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub>              | -     | 10   |              | 300  | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                                |       | 0.4  | -            | 0.4  | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                              | 2.5   | -    | 2.5          | -    | V     |

| $V_{JL1}$        | Voltage Input Low (CMOS)  | -                                                    |       | 1.5  | -            | 1.5  | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                                    | 3.5   | -    | 3.5          | -    | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                                    | -     | 0.8  | -            | 0.8  | l v   |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                                    | 2.0   | -    | 2.0          |      | l v   |

| I <sub>IN</sub>  | Input Leakage Current     | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> | -     | ±0.5 | -            | ±5.0 | μА    |

Figure 5: DC Characteristics

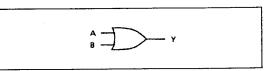

# 54HSC/T32: Quadruple 2-Input Positive OR Gates

The 54HSC/T32 is a Quadruple 2-Input Positive OR gate.

| Inp | uts | Outputs |

|-----|-----|---------|

| Α   | В   | Y       |

| L   | L   | L       |

| L   | н   | н       |

| Н   | L   | Н       |

| Н   | Н   | н       |

H = high level, L = low level

Figure 1: Function Table

Figure 2: Logic Diagram

Figure 3: Pin Out

|                  |                                                                                                      | +25°C -55°C / +125°C |          |          | +125°C   |          |

|------------------|------------------------------------------------------------------------------------------------------|----------------------|----------|----------|----------|----------|

| Symbol           | Parameter                                                                                            | Тур.                 | Max.     | Тур.     | Max.     | Units    |

| t <sub>PLH</sub> | Propagation delay time, low to high level output<br>Propagation delay time, high to low level output | 11<br>10             | 20<br>18 | 17<br>18 | 22<br>20 | ns<br>ns |

Figure 4: Switching Characteristics

|                  |                           |                                         |      | +25°C |      | +125°C |       |

|------------------|---------------------------|-----------------------------------------|------|-------|------|--------|-------|

| Symbol           | Parameter                 | Test Conditions                         | Min. | Max.  | Min. | Max.   | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub> | -    | 10    | -    | 300    | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                   | -    | 0.4   | -    | 0.4    | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                 | 2.5  | -     | 2.5  | -      | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                       | -    | 1.5   | -    | 1.5    | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                       | 3.5  | -     | 3.5  | -      | V     |

| V <sub>IL2</sub> | Voitage Input Low (TTL)   | -                                       | -    | 0.8   | -    | 0.8    | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  |                                         | 2.0  | -     | 2.0  | -      | V     |

| I <sub>IN</sub>  | Input Leakage Current     | $V_{IN} = V_{DD}$ or $V_{SS}$           | -    | ±0.5  | -    | ±5.0   | μА    |

Figure 5: DC Characteristics

## 54HSC/T86: Quadruple 2-Input Exclusive OR Gates

The 54HSC/T86 is a Quadruple 2-Input Exclusive OR gate.

| Inp | uts | Outputs |

|-----|-----|---------|

| A   | В   | Y       |

| L   | L   | L       |

| L   | н   | н       |

| н   | L   | Н       |

| н   | н   | L       |

H = high level, L = low level

Figure 1: Function Table

Figure 2: Logic Diagram

Figure 3: Pin Out

|                  |                                                  |      | +25°C |      |      |       |

|------------------|--------------------------------------------------|------|-------|------|------|-------|

| Symbol           | Parameter                                        | Тур. | Max.  | Тур. | Max. | Units |

| t <sub>plH</sub> | Propagation delay time, low to high level output | 11   | 20    | 17   | 22   | ns    |

| t <sub>PHL</sub> | Propagation delay time, high to low level output | 10   | 18    | 18   | 20   | ns    |

Figure 4: Switching Characteristics

|                  |                           |                                         | Limits |      |              |      |       |

|------------------|---------------------------|-----------------------------------------|--------|------|--------------|------|-------|

|                  |                           |                                         | +25°C  |      | -55°C/+125°C |      |       |

| Symbol           | Parameter                 | Test Conditions                         | Min.   | Max. | Min.         | Max. | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub> | -      | 10   | -            | 300  | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                   | -      | 0.4  | -            | 0.4  | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                 | 2.5    | -    | 2.5          | -    | V     |

| $V_{\rm IL1}$    | Voltage Input Low (CMOS)  | -                                       | -      | 1.5  | -            | 1.5  | l v   |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                       | 3.5    | -    | 3.5          | -    | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                       | -      | 0.8  | -            | 0.8  | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                       | 2.0    | -    | 2.0          | -    | V     |

| I <sub>IN</sub>  | Input Leakage Current     | $V_{IN} = V_{DD}$ or $V_{SS}$           | -      | ±0.5 | -            | ±5.0 | μА    |

Figure 5: DC Characteristics

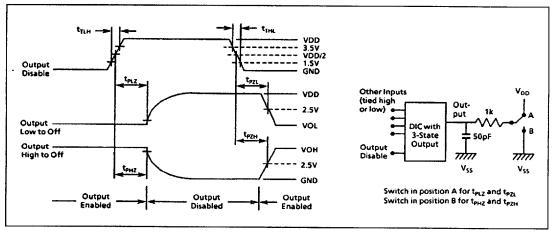

# 54HSC/T125: Quadruple Bus Buffer Gates with Tri-State Outputs (Active Low Enable)

The 54HSC/T125 is a Quadruple Bus Buffer Gate. When G is low the A input is transferred to the Y output. When G is high the output is in a high impedance state.

| Inp | uts | Outputs |

|-----|-----|---------|

| G   | A   | Y       |

| L   | L   |         |

| L   | н   | Н       |

| н   | L   | Z       |

| Н   | Н   | Z       |

H = high level, L = low level, Z = high impedance

Figure 1: Function Table

Figure 2: Logic Diagram

Figure 3: Pin Out

|                  |                                  |     | +25°C |      | -55°C / +125°C |      |       |

|------------------|----------------------------------|-----|-------|------|----------------|------|-------|

| Symbol           | Parameter                        | T   | ур.   | Max. | Тур.           | Мах. | Units |

| t <sub>PLH</sub> | Propagation delay A to Y         |     | 15    | 18   | 18             | 28   | ns    |

| t <sub>PHL</sub> | Propagation delay A to Y         |     | 15    | 20   | 18             | 28   | ns    |

| t <sub>PZH</sub> | Propagation delay G to Y         | •   | 12    | 25   | 15             | 28   | ns    |

| t <sub>PZL</sub> | Propagation delay G to Y         |     | 12    | 25   | 15             | 28   | ns    |

| t <sub>PHZ</sub> | Propagation delay Y to Tri-State | 1 - | 12    | 25   | 15             | 28   | ns    |

| t <sub>PLZ</sub> | Propagation delay Y to Tri-State |     | 12    | 25   | 15             | 28   | ns    |

Figure 4: Switching Characteristics

# 54HSC/T125 : Quadruple Bus Buffer Gates with Tri-State Outputs (Active Low Enable)

|                  |                           |                                         | Limits |      |              |      |       |

|------------------|---------------------------|-----------------------------------------|--------|------|--------------|------|-------|

|                  |                           |                                         | +25°C  |      | -55°C/+125°C |      | 1     |

| Symbol           | Parameter                 | Test Conditions                         | Min.   | Max. | Min.         | Max. | Units |

| 1 <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub> | -      | 10   | -            | 400  | μА    |

| $V_{OL}$         | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                   | -      | 0.4  | -            | 0.4  | l v   |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                 | 2.5    | -    | 2.5          | -    | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                       | -      | 1.5  | -            | 1.5  | l v   |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                       | 3.5    | -    | 3.5          | -    | v     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                       | -      | 0.8  | -            | 0.8  | v     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                       | 2.0    | -    | 2.0          | -    | V     |

| I <sub>IN</sub>  | Input Leakage Current     | $V_{IN} = V_{DD}$ or $V_{SS}$           | -      | ±0.5 | -            | ±5.0 | μА    |

Figure 5: DC Characteristics

# 54HSC/T126: Quadruple Bus Buffer Gates with Tri-State Outputs (Active High Enable)

The 54HSC/T126 is a Quadruple Bus Buffer Gate. When G is high the A input is transferred tp the Y output. When G is low the output is in a high impedance state.

| Inp | uts | Outputs |

|-----|-----|---------|

| G   | Α   | Υ       |

| Н   | L   | L       |

| Н   | Н   | Н       |

| L   | L   | Z       |

| L   | н   | Z       |

H = high level, L = low level, Z = high impedance

Figure 1: Function Table

Figure 2: Logic Diagram

Figure 3: Pin Out

|                  |                                  | +25°C |      | -55°C / +125°C |      |       |

|------------------|----------------------------------|-------|------|----------------|------|-------|

| Symbol           | Parameter                        | Тур.  | Max. | Тур.           | Max. | Units |

| t <sub>PLH</sub> | Propagation delay A to Y         | 14    | 25   | 17             | 28   | ns    |

| t <sub>PHL</sub> | Propagation delay A to Y         | 15    | 25   | 19             | 28   | ns    |

| t <sub>PZH</sub> | Propagation delay G to Y         | 15    | 25   | 18             | 28   | ns    |

| t <sub>PZL</sub> | Propagation delay G to Y         | 17    | 25   | 19             | 28   | ns    |

| t <sub>enz</sub> | Propagation delay Y to Tri-State | 17    | 25   | 20             | 28   | ns    |

| t <sub>PLZ</sub> | Propagation delay Y to Tri-State | 15    | 25   | 19             | 28   | ns    |

Figure 4: Switching Characteristics

# 54HSC/T126: Quadruple Bus Buffer Gates with Tri-State Outputs (Active High Enable)

|                  |                           |                                         | Limits |      |                |      |       |

|------------------|---------------------------|-----------------------------------------|--------|------|----------------|------|-------|

|                  |                           |                                         | +25°C  |      | -55°C / +125°C |      | ]     |

| Symbol           | Parameter                 | Test Conditions                         | Min.   | Max. | Min.           | Max. | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub> |        | 10   |                | 400  | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                   | -      | 0.4  | -              | 0.4  | v     |

| V <sub>OH</sub>  | Output Voltage High Level | l <sub>OH</sub> = -11mA                 | 2.5    | -    | 2.5            | -    | l v   |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                       | -      | 1.5  | -              | 1.5  | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                       | 3.5    | -    | 3.5            | _    | l v   |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                       | -      | 0.8  | -              | 0.8  | l v   |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                       | 2.0    | -    | 2.0            | -    | l v   |

| I <sub>IN</sub>  | Input Leakage Current     | $V_{IN} = V_{DD}$ or $V_{SS}$           | -      | ±0.5 | -              | ±5.0 | μА    |

Figure 5: DC Characteristics

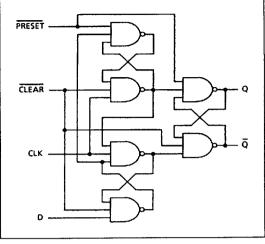

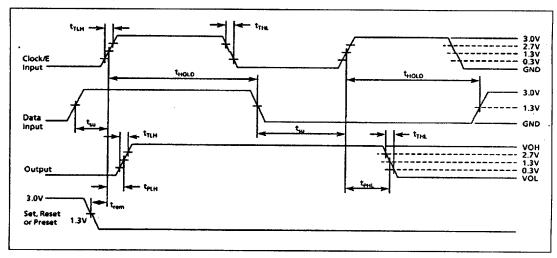

## 54HSC/T74: Dual D-Type Flip-Flops with Preset and Clear

The 54HSC/T74 is a Dual D-Type Flip-Flop. The D inputs are transferred to the Q outputs on the positive going edge of the clock pulse. The clear is active low.

|        | Inputs               |     |   |                |                    |  |

|--------|----------------------|-----|---|----------------|--------------------|--|

| PRESET | PRESET CLEAR CLOCK D |     |   |                |                    |  |

| L      | Н                    | Х   | Х | Н              | L                  |  |

| н      | L                    | x   | х | L              | Н                  |  |

| L      | L                    | x   | х | H*             | H⁺                 |  |

| н      | Н                    | L-H | н | н              | L                  |  |

| н      | н                    | L-H | L | L              | Н                  |  |

| н      | н                    | L   | Х | Q <sub>0</sub> | $\overline{Q}_{0}$ |  |

H = high level, L = low level, X = irrelevant, \* = unknown return state

Figure 1: Function Table

Figure 2: Logic Diagram

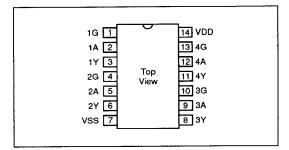

Figure 3: Pin Out

| Symbol           |                                                            | +2   | 5°C  | -55°C / | +125°C |       |

|------------------|------------------------------------------------------------|------|------|---------|--------|-------|

|                  | Parameter                                                  | Тур. | Max. | Тур.    | Max.   | Units |

| t <sub>PLH</sub> | Propagation delay. Preset to Q or Q.                       | 15   | 20   | 18      | 24     | ns    |

| PHL              | Propagation delay. Preset to Q or Q.                       | 16   | 20   | 10      | 24     | ns    |

| PLH              | Propagation delay. Clear to Q or Q.                        | 18   | 20   | 15      | 24     | ns    |

| PHL              | Propagation delay. Clear to Q or Q.                        | 15   | 20   | 15      | 24     | ns    |

| PLH              | Propagation delay. Clock to Q or Q.                        | 17   | 25   | 15      | 25     | ns    |

| PHL              | Propagation delay. Clock to Q or $\overline{\mathbf{Q}}$ . | 18   | 25   | 15      | 25     | ns    |

Figure 4: Switching Characteristics

## 54HSC/T74: Dual D-Type Flip-Flops with Preset and Clear

|                  |                           |                                                      |      | Lin  | nits    |        |       |

|------------------|---------------------------|------------------------------------------------------|------|------|---------|--------|-------|

|                  |                           |                                                      | +2!  | 5°C  | -55°C / | +125°C |       |

| Symbol           | Parameter                 | Test Conditions                                      | Min. | Max. | Min.    | Max.   | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub>              | -    | 10   | -       | 400    | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                                | -    | 0.4  | -       | 0.4    | v     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                              | 2.5  | -    | 2.5     |        | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                                    | -    | 1.5  | -       | 1.5    | ٧     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                                    | 3.5  | -    | 3.5     | -      | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                                    | -    | 0.8  | _       | 0.8    | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                                    | 2.0  | -    | 2.0     | -      | V     |

| I <sub>IN</sub>  | Input Leakage Current     | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> | -    | ±0.5 | -       | ±5.0   | μΑ    |

Figure 5: DC Characteristics

# 54HSC/T109: Dual J-KB Flip-Flops with Preset and Clear

The 54HSC/T109 is a Dual Positive-Edge-Triggered J-KB Flip-Flop with preset and clear.

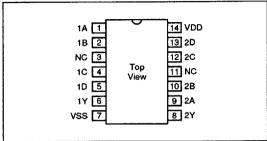

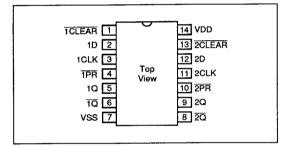

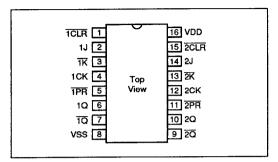

Figure 1: Pin Out

|        |       | Inputs |   |    | Out            | put    |

|--------|-------|--------|---|----|----------------|--------|

| PRESET | CLEAR | СГОСК  | J | КВ | Q              | ā      |

| L      | Н     | ×      | х | x  | Н              | L      |

| н      | L     | x      | х | x  | L              | н      |

| L      | L     | x      | х | x  | H*             | Н*     |

| н      | Н     | 1      | L | L  | L              | н      |

| н      | н     | 1      | Н | L  | Toggle         | Toggle |

| н      | н     | 1      | L | н  | Q <sub>0</sub> | ਕ੍ਰ    |

| н      | н     | 1      | н | н  | н              | L      |

| н      | Н     | L      | х | x  | Q <sub>o</sub> | a₀     |

H = high level, L = low level, X = irrelevant, \* = unknown return state

Figure 2: Function Table

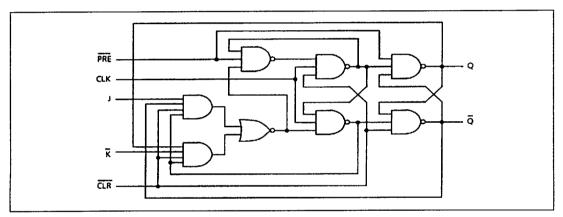

Figure 3: Logic Diagram

|                  |                                      | +25  | °C   | -55°C / | +125°C |       |

|------------------|--------------------------------------|------|------|---------|--------|-------|

| Symbol           | Parameter                            | Тур. | Max. | Тур.    | Мах.   | Units |

| t <sub>PLH</sub> | Propagation delay. Preset to Q or Q. | 15   | 19   | 17      | 19     | ns    |

| t <sub>PHL</sub> | Propagation delay. Preset to Q or Q. | 16   | 25   | 19      | 25     | ns    |

| t <sub>PLH</sub> | Propagation delay. Clear to Q or Q.  | 17   | 25   | 20      | 25     | ns    |

| t <sub>PHL</sub> | Propagation delay. Clear to Q or Q.  | 15   | 25   | 18      | 25     | ns    |

| t <sub>PLH</sub> | Propagation delay. Clock to Q or Q.  | 18   | 25   | 21      | 25     | ns    |

| t <sub>PHL</sub> | Propagation delay. Clock to Q or Q.  | 15   | 25   | 18      | 25     | ns    |

Figure 4: Switching Characteristics

## 54HSC/T109: Dual J-KB Flip-Flops with Preset and Clear

|                  |                           |                                         |      | Min.         Max.         Min.         Max           -         20         -         40           -         0.4         -         0           2.5         -         2.5         - |                |      |       |

|------------------|---------------------------|-----------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-------|

|                  |                           |                                         | +2   | 5°C                                                                                                                                                                              | -55°C / +125°C |      |       |

| Symbol           | Parameter                 | Test Conditions                         | Min. | Max.                                                                                                                                                                             | Min.           | Max. | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub> | -    | 20                                                                                                                                                                               | -              | 400  | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                   | -    | 0.4                                                                                                                                                                              | -              | 0.4  | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                 | 2.5  | -                                                                                                                                                                                | 2.5            | -    | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                       | -    | 1.5                                                                                                                                                                              | -              | 1.5  | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                       | 3.5  | -                                                                                                                                                                                | 3.5            | -    | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                       | -    | 0.8                                                                                                                                                                              | -              | 0.8  | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                       | 2.0  | -                                                                                                                                                                                | 2.0            | -    | V     |

| I                | Input Leakage Current     | $V_{IN} = V_{DD}$ or $V_{SS}$           | -    | ±0.5                                                                                                                                                                             | -              | ±5.0 | μΑ    |

Figure 5: DC Characteristics

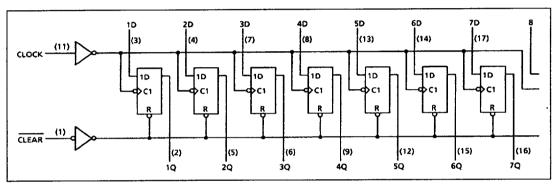

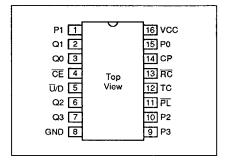

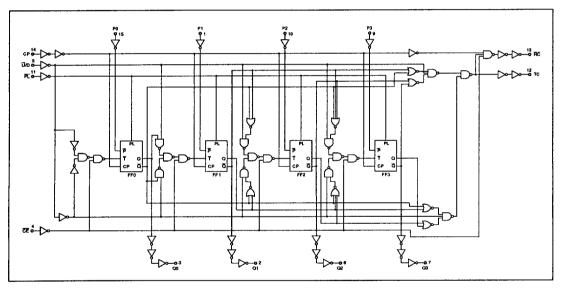

### 54HSC/T273: Octal D-Type Flip-Flops

The 54HSC/T273 is an Octal D-Type Flip-Flop with a direct active low clear. The D-Inputs are transferred to the Q-Outputs on the positive going edge of the clock pulse.

|       | Inputs |   |                |  |  |

|-------|--------|---|----------------|--|--|

| CLEAR | D      | Q |                |  |  |

| L     | х      | х | L              |  |  |

| н     | L-H    | н | н              |  |  |

| н     | L-H    | L | L              |  |  |

| н     | L      | х | a <sub>o</sub> |  |  |

Q<sub>0</sub> = level of Q before inputs were established H = high level, L = low level, X = irrelevant

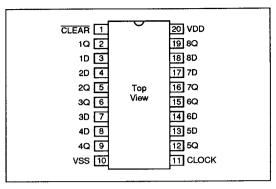

Figure 2: Pin Out

Figure 3: Logic Diagram

| Symbol Parame    |                                                            | +2   | 5°C  | -55°C / | +125°C |       |

|------------------|------------------------------------------------------------|------|------|---------|--------|-------|

|                  | Parameter                                                  | Тур. | Max. | Тур.    | Max.   | Units |

| t <sub>PLH</sub> | Propagation delay. Clear to Q or Q.                        | 14   | 25   | 17      | 28     | ns    |

| t <sub>PHL</sub> | Propagation delay. Clear to Q or Q.                        | 16   | 25   | 19      | 28     | กร    |

| t <sub>PLH</sub> | Propagation delay. Clock to Q or Q.                        | 15   | 25   | 18      | 28     | ns    |

| t <sub>PHL</sub> | Propagation delay. Clock to Q or $\overline{\mathbf{Q}}$ . | 17   | 25   | 20      | 28     | ns    |

Figure 4: Switching Characteristics

## 54HSC/T273 : Octal D-Type Flip-Flops

|                  |                           |                                                      | Limits       +25°C     -55°C / +125°C       Min.     Max.     Min.     Max.       -     20     -     600       -     0.4     -     0.4       2.5     -     2.5     - |      |        |      |       |

|------------------|---------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|-------|

|                  |                           |                                                      | +25°C -55°C / +125°C                                                                                                                                                 |      | +125°C |      |       |

| Symbol           | Parameter                 | Test Conditions                                      | Min.                                                                                                                                                                 | Max. | Min.   | Max. | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub>              | -                                                                                                                                                                    | 20   | -      | 600  | μА    |

| $V_{QL}$         | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                                | -                                                                                                                                                                    | 0.4  | -      | 0.4  | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                              | 2.5                                                                                                                                                                  | -    | 2.5    | -    | l v   |

| $V_{iL1}$        | Voltage Input Low (CMOS)  | -                                                    | -                                                                                                                                                                    | 1.5  | -      | 1.5  | l v   |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                                    | 3.5                                                                                                                                                                  | -    | 3.5    | -    | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                                    | -                                                                                                                                                                    | 0.8  | -      | 0.8  | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                                    | 2.0                                                                                                                                                                  | -    | 2.0    | -    | V     |

| i <sub>IN</sub>  | Input Leakage Current     | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> | -                                                                                                                                                                    | ±0.5 | -      | ±5.0 | μА    |

Figure 5: DC Characteristics

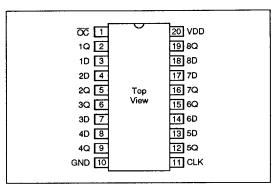

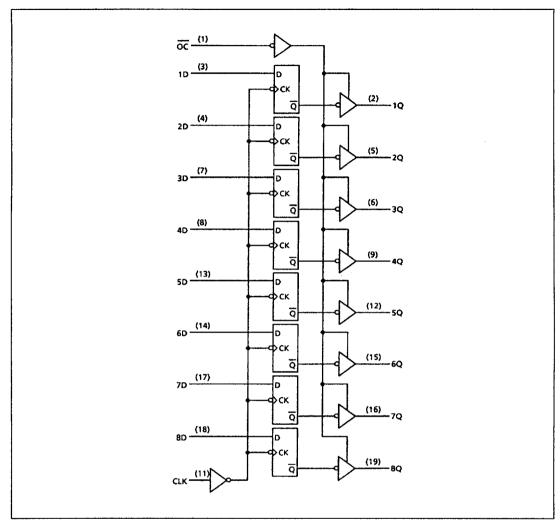

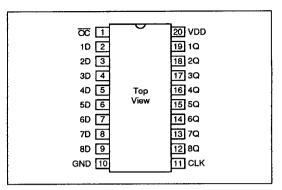

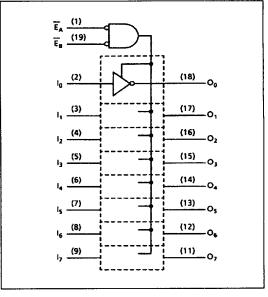

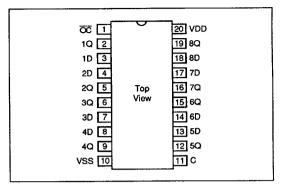

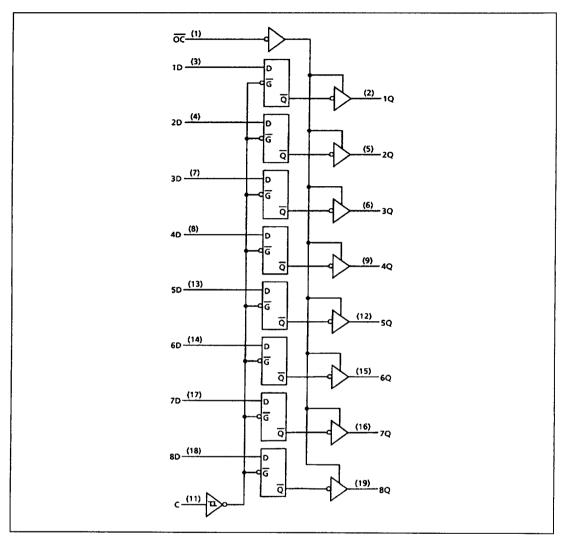

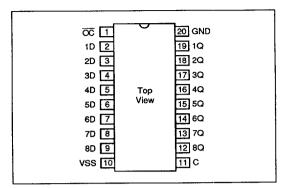

### 54HSC/T374: Octal D-Type Edge-Triggered Flip-Flops

The 54HSC/T374 consists of 8 Positive-Edge Triggered D-Type Flip-Flops with tri-state output.

|           | Inputs |   |                |  |  |

|-----------|--------|---|----------------|--|--|

| <u>oc</u> | CLOCK  | D | Q              |  |  |

| L         | 1      | Н | н              |  |  |

| L         | 1      | L | Ł              |  |  |

| L         | L      | × | Q <sub>o</sub> |  |  |

| Н         | х      | × | z              |  |  |

H = high level, L = low level, X = irrelevant, Z = high impedance

Figure 1: Function Table

Figure 2: Pin Out

| Symbol           |                                        |      | +25°C |      | -5:  | 5°C / +125 | °C   |       |

|------------------|----------------------------------------|------|-------|------|------|------------|------|-------|

|                  | Parameter                              | Min. | Тур.  | Max. | Min. | Тур.       | Max. | Units |

| t <sub>PLH</sub> | Propagation delay. Low to high output. | -    | 14    | 22   | -    | 17         | 25   | ns    |

| t <sub>PHL</sub> | Propagation delay. High to low output. | -    | 15    | 22   | -    | 16         | 25   | ns    |

| t <sub>PZL</sub> | Propagation delay. Enable to low.      | -    | 13    | 20   | -    | 16         | 25   | ns    |

| t <sub>PZH</sub> | Propagation delay. Enable to high.     | -    | 16    | 20   | -    | 18         | 23   | ns    |

| t <sub>PLZ</sub> | Propagation delay. Disable from low.   | -    | 14    | 20   | -    | 16         | 22   | ns    |

| t <sub>PHZ</sub> | Propagation delay. Disable from high.  | -    | 13    | 18   | -    | 15         | 20   | ns    |

Figure 3: Switching Characteristics

|                  |                           |                                         |      | Lin  | nits    |        |       |

|------------------|---------------------------|-----------------------------------------|------|------|---------|--------|-------|

|                  |                           |                                         | +2!  | 5°C  | -55°C / | +125°C |       |

| Symbol           | Parameter                 | Test Conditions                         | Min. | Max. | Min.    | Max.   | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub> | -    | 20   | -       | 600    | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                   | -    | 0.4  | -       | 0.4    | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                 | 2.5  | -    | 2.5     | -      | V     |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                       | -    | 1.5  | -       | 1.5    | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                       | 3.5  | -    | 3.5     | -      | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                       | -    | 0.8  | -       | 0.8    | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  |                                         | 2.0  |      | 2.0     | -      | V     |

| loz              | Tri-State Leakage         | $V_0 = 0V \text{ or } V_{DD}$           | -    | ±1   | -       | ±50    | μА    |

| I                | Input Leakage Current     | $V_{IN} = V_{DD}$ or $V_{SS}$           | -    | ±0.5 | -       | ±5.0   | μΑ    |

Figure 4: DC Characteristics

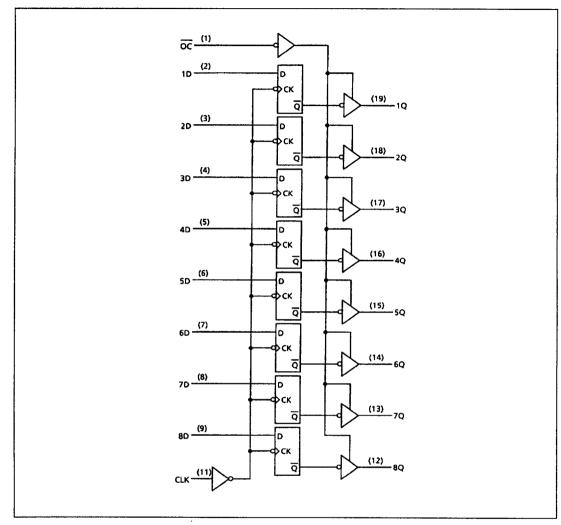

## 54HSC/T374: Octal D-Type Edge-Triggered Flip-Flops

Figure 5: Logic Diagram

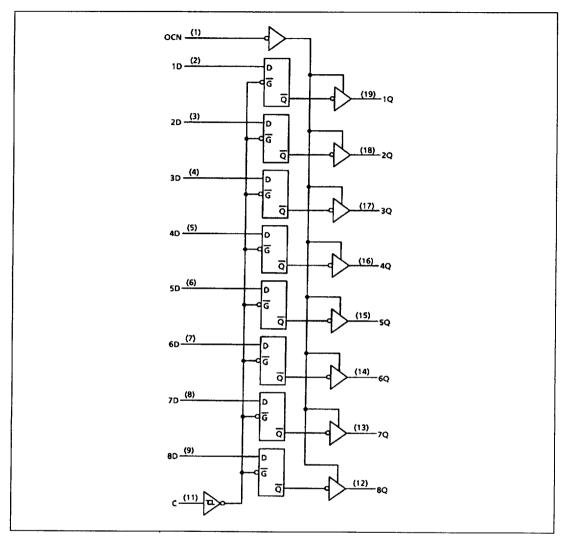

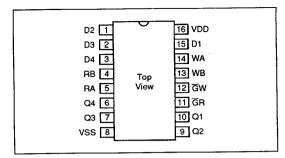

# 54HSC/T574 : Octal D-Type Edge-Triggered Flip-Flops

The 54HSC/T574 consists of 8 Positive-Edge Triggered D-Type Flip-Flops with tri-state output.

| Inputs |                | Outputs   |

|--------|----------------|-----------|

| CLOCK  | D              | Q         |

| 1      | Н              | н         |

| 1      | L              | L         |

| L.     | х              | Q₀        |

| x      | х              | z         |

|        | CLOCK  ↑  ↑  L | CLOCK   D |

H = high level, L = low level, X = irrelevant, Z = high impedance

Figure 1: Function Table

Figure 2: Pin Out

|                  |                                        | +25°C |      |      | -55°C / +125°C |      |      |       |

|------------------|----------------------------------------|-------|------|------|----------------|------|------|-------|

| Symbol           | Parameter                              | Min.  | Тур. | Max. | Min.           | Тур. | Max. | Units |

| t <sub>PLH</sub> | Propagation delay. Low to high output. | -     | 16   | 25   | -              | 19   | 28   | ns    |

| t <sub>PHL</sub> | Propagation delay. High to low output. | -     | 19   | 27   | -              | 22   | 30   | ns    |

| t <sub>PZL</sub> | Propagation delay. Enable to low.      | -     | 13   | 21   | -              | 16   | 24   | ns    |

| t <sub>PZH</sub> | Propagation delay. Enable to high.     | -     | 16   | 24   | -              | 19   | 27   | ns    |

| t <sub>PLZ</sub> | Propagation delay. Disable from low.   | -     | 14   | 22   | -              | 17   | 25   | ns    |

| t <sub>PHZ</sub> | Propagation delay. Disable from high.  | -     | 13   | 21   | -              | 16   | 24   | ns    |

Figure 3: Switching Characteristics

|                  |                           |                                         |       | Limits |                |      |       |  |

|------------------|---------------------------|-----------------------------------------|-------|--------|----------------|------|-------|--|

|                  |                           |                                         | +25°C |        | -55°C / +125°C |      | 1     |  |

| Symbol           | Parameter                 | Test Conditions                         | Min.  | Max.   | Min.           | Max. | Units |  |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub> | -     | 20     | -              | 600  | μА    |  |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                   | -     | 0.4    | -              | 0.4  | V     |  |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                 | 2.5   | -      | 2.5            | -    | V     |  |

| V <sub>IL1</sub> | Voltage Input Low (CMOS)  | -                                       | -     | 1.5    | -              | 1.5  | V     |  |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                       | 3.5   | -      | 3.5            | -    | V     |  |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   | -                                       | -     | 0.8    | -              | 0.8  | v     |  |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                       | 2.0   | -      | 2.0            | -    | V     |  |

| l <sub>oz</sub>  | Tri-State Leakage         | V <sub>O</sub> = 0V or V <sub>DD</sub>  | -     | ±1     | -              | ±50  | μΑ    |  |

| I <sub>IN</sub>  | Input Leakage Current     | $V_{IN} = V_{DD}$ or $V_{SS}$           | -     | ±0.5   | -              | ±5.0 | μΑ    |  |

Figure 4: DC Characteristics

## 54HSC/T574: Octal D-Type Edge-Triggered Flip-Flops

Figure 5: Logic Diagram

### 54HSC/T Series

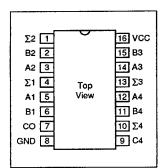

## 54HSC/T283: 4-Bit Binary Full Adders with Fast Carry

The 54HSC/T283 are 4-Bit Binary Full Adders with fast carry.

|       | Inp   | out   |       |        |           | Ou     | tput   |           |        |

|-------|-------|-------|-------|--------|-----------|--------|--------|-----------|--------|

|       |       |       |       | When C | O=L / Whe | n C2=L | When C | O≖H / Whe | n C2=H |

| A1/A3 | B1/B3 | A2/A4 | B2/B4 | Σ1/Σ3  | Σ2/Σ4     | C2/C4  | Σ1/Σ3  | Σ2/Σ4     | C2/C4  |

| L     | L     | L     | L     | L      | L         | L      | Н      | L,        | L      |

| н     | L     | L     | L     | н      | L         | L      | L      | н         | L      |

| L     | н     | L     | L     | н      | L         | L      | L      | н         | L      |

| н     | Н     | L     | L     | L      | н         | L      | Н      | н         | L      |

| L     | L     | н     | L     | L      | н         | L      | н      | н         | L      |

| н     | L     | н     | L     | н      | н         | L      | L      | L         | Н      |

| L     | Н     | н     | L     | н      | н         | L      | L      | L         | н      |

| н     | Н     | н     | L     | L      | L         | н      | Н      | L         | н      |

| L     | L     | L     | н     | L      | н         | L      | Н      | н         | L      |

| н     | L     | L     | н     | н      | н         | L      | L      | L         | н      |

| L     | н     | L     | н     | н      | н         | L      | L      | L         | н      |

| н     | н     | L     | н     | L      | L         | н      | н      | L         | н      |

| L     | L     | н     | н     | L      | L         | н      | Н      | L         | н      |

| н     | L     | н     | н     | н      | L         | н      | L      | н         | н      |

| L     | н     | н     | н     | н      | L         | н      | L      | н         | н      |

| н     | Н     | Н     | н     | L      | н         | н      | н      | н         | н      |

Figure 2: Pin Out

H = high level, L = low level

Figure 1: Function Table

|                  |                                    | +2   | 5°C  | -55°C / +125°C |      |       |

|------------------|------------------------------------|------|------|----------------|------|-------|

| Symbol           | Parameter                          | Тур. | Max. | Тур.           | Max. | Units |

| t <sub>PLH</sub> | Propagation delay. C0 to any ∑.    | 13   | 25   | 16             | 28   | ns    |

| t <sub>PHL</sub> | Propagation delay. C0 to any Σ.    | 12   | 25   | 15             | 28   | ns    |

| t <sub>PLH</sub> | Propagation delay. Ai or Bi to ∑i. | 14   | 25   | 17             | 28   | ns    |

| t <sub>PHL</sub> | Propagation delay. Ai or Bi to ∑i. | 12   | 25   | 15             | 28   | ns    |

| t <sub>PLH</sub> | Propagation delay. C0 to C4.       | 11   | 25   | 14             | 28   | ns    |

| PHL              | Propagation delay. C0 to C4.       | 16   | 25   | 19             | 28   | ns    |

| PLH              | Propagation delay. Ai or Bi to C4. | 15   | 25   | 19             | 28   | ns    |

| t <sub>PHL</sub> | Propagation delay. Ai or Bi to C4. | 14   | 25   | 17             | 28   | ns    |

Figure 3: Switching Characteristics

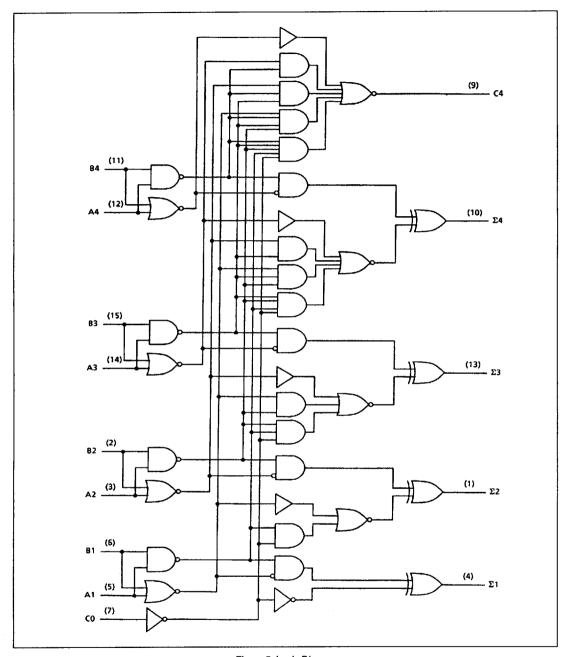

## 54HSC/T283: 4-Bit Binary Full Adders with Fast Carry

|                  |                           |                                         |       | Lin  |      |                |       |

|------------------|---------------------------|-----------------------------------------|-------|------|------|----------------|-------|

|                  |                           |                                         | +25°C |      |      | -55°C / +125°C |       |

| Symbol           | Parameter                 | Test Conditions                         | Min.  | Max. | Min. | Max.           | Units |

| I <sub>DD</sub>  | Quiescent Current         | V <sub>IN</sub> = 0V or V <sub>DD</sub> | -     | 20   | -    | 600            | μА    |

| V <sub>OL</sub>  | Output Voltage Low Level  | I <sub>OL</sub> = 9mA                   | -     | 0.4  | -    | 0.4            | V     |

| V <sub>OH</sub>  | Output Voltage High Level | I <sub>OH</sub> = -11mA                 | 2.5   | -    | 2.5  | -              | V     |

| $V_{IL1}$        | Voltage Input Low (CMOS)  | -                                       | -     | 1.5  | -    | 1.5            | V     |

| V <sub>IH1</sub> | Voltage Input High (CMOS) | -                                       | 3.5   | -    | 3.5  | -              | V     |

| V <sub>IL2</sub> | Voltage Input Low (TTL)   |                                         | -     | 0.8  | -    | 0.8            | V     |

| V <sub>IH2</sub> | Voltage Input High (TTL)  | -                                       | 2.0   | -    | 2.0  | -              | v     |

| I                | Input Leakage Current     | $V_{IN} = V_{DD}$ or $V_{SS}$           | -     | ±0.5 | -    | ±5.0           | μА    |

Figure 4: DC Characteristics

## 54HSC/T283: 4-Bit Binary Full Adders with Fast Carry

Figure 5: Logic Diagram

828

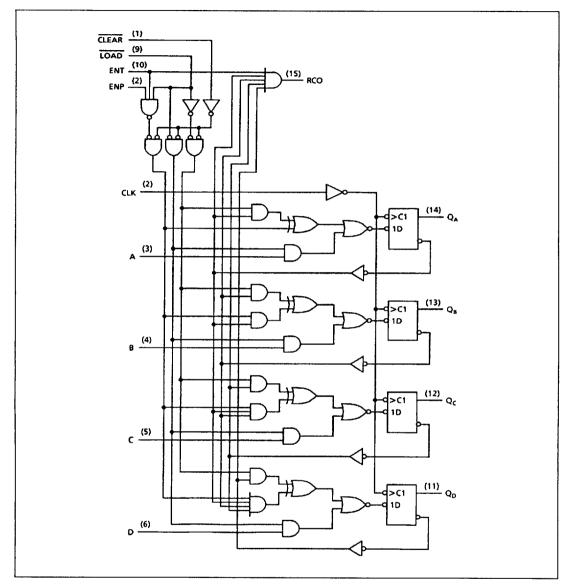

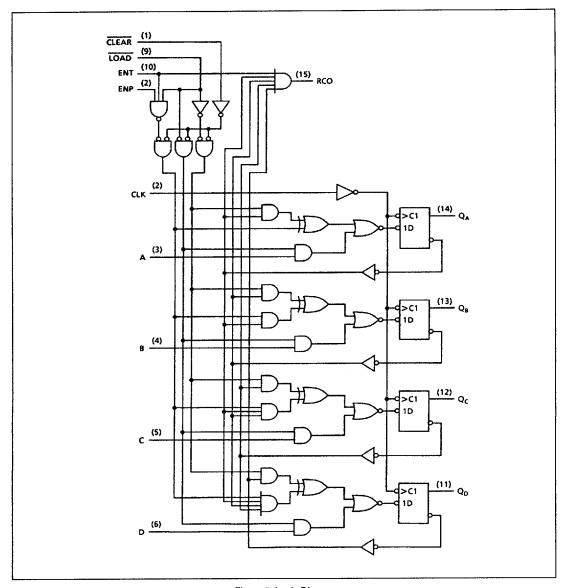

## 54HSC/T161: 4-Bit Synchronous Binary Counter

The 54HSC/T161 is a Synchronous 4-Bit Binary Counter which features direct clear and an internal carry look-ahead.

|       |          | Inp      | uts |      |       | Output                |

|-------|----------|----------|-----|------|-------|-----------------------|

| Clear | Enable P | Enable T | A→D | Load | Clock | $Q_A \rightarrow Q_D$ |

| L     | х        | х        | х   | х    | х     | 0                     |

| н     | L        | х        | х   | н    | х     | Inhibit               |

| н     | x        | L        | х   | н    | x     | Inhibit               |

| н     | ×        | x        | Qn  | L    | 1     | Q <sub>n</sub>        |

| Н     | х        | x        | Х   | x    | L     | Q <sub>o</sub>        |

| н     | х        | x        | X   | ×    | н     | $Q_0$                 |

| н     | н        | н        | х   | н    | 1     | Count                 |

CARRY = H when  $Q_A \rightarrow Q_D$  = H,  $Q_0$  = previous level of Q H = high level, L = low level, X = irrelevant

Figure 1: Function Table

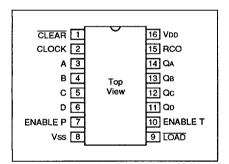

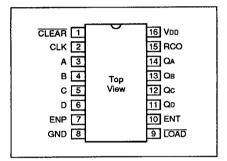

Figure 2: Pin Out

|                  |                         |              | +2   | 5°C  | -55°C / +125°C |      |       |

|------------------|-------------------------|--------------|------|------|----------------|------|-------|

| Symbol           | From (Input)            | To (Output)  | Тур. | Max. | Тур.           | Max. | Units |

| t <sub>PLH</sub> | CLOCK                   | RIPPLE CARRY | 20   | 25   | 23             | 28   | ns    |

| t <sub>PHL</sub> | CLOCK                   | RIPPLE CARRY | 19   | 25   | 22             | 28   | лѕ    |

| t <sub>PLH</sub> | CLOCK (Load Input HIGH) | Any Q Output | 16   | 25   | 19             | 28   | ns    |

| t <sub>PHL</sub> | CLOCK (Load Input HIGH) | Any Q Output | 15   | 25   | 18             | 28   | ns    |

| t <sub>PLH</sub> | CLOCK (Load Input LOW)  | Any Q Output | 15   | 25   | 18             | 28   | ns    |