# Military Low Power FIFOs 64x4 64x5 Memory

12 MHz (Standalone) 57L401D 57L402D

57L4013D

Conforms to Mil-Std-883, Class B

#### Features/Benefits

- · High-speed 12 MHz shift-in/shift-out data rates

- · Low power consumption

- · Choice of 4-bit or 5-bit data width

- · TTL inputs and outputs

- · Readily expandable in word width

- Structured pinouts. Outputs pins directly opposite corresponding input pins

- · High-drive capability

- · Asynchronous operation

- Dose rate (transient upset) junction-isolated bipolar process 2x10<sup>10</sup> RADs (Si)/s recovery time of 50 to 70 µs from a 1 µs pulse

- Neutron fluence (permanent damage): 1x10<sup>13</sup> N/cm<sup>2</sup>

#### **Description**

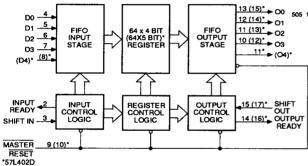

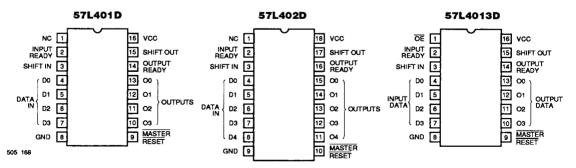

The 57L401D/2D and 574013D are "fall-through" high-speed First-In First-Out (FIFO) memories organized 64 words by 4 bits and 64 words by 5 bits. These FIFOs are expandable in word width. The FIFOs are attractive for many applications such as disk controllers, communication buffers, rate buffers, etc. They feature high-drive (I<sub>OL</sub> = 12 mA) outputs. The 57L4013D features three-state outputs.

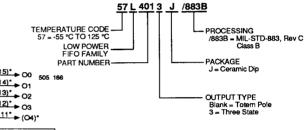

#### **Ordering Information**

### **Block Diagram**

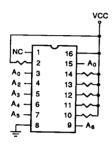

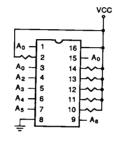

#### **Device Pinouts**

505 167

May 1988

## **Absolute Maximum Ratings\***

| Complement V                   |                    |

|--------------------------------|--------------------|

| Supply voltage, V <sub>∞</sub> |                    |

| Input voltage range            | -0.5 V to to 5.5 V |

| Off-state output voltage       | -65°C to +150°C    |

| Storage temperature            |                    |

\*Note:

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

#### **Operating Conditions**

| SYMBOL               | PARAMETER                                | FIGURE | MIN | MAX | UNIT |

|----------------------|------------------------------------------|--------|-----|-----|------|

| V <sub>cc</sub>      | Supply voltage                           |        | 4.5 | 5.5 | ٧    |

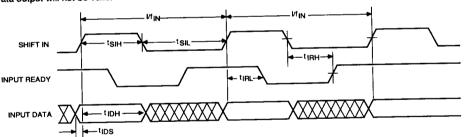

| t <sub>siH</sub> †   | Shift in HIGH time                       | 1      | 30  | _   | ns   |

| t <sub>siL</sub> †   | Shift in LOW time                        | 1      | 15  |     | ns   |

| t <sub>ios</sub>     | Input data setup to SI (Shift In)        | 1      | 0   |     | ns   |

| t <sub>ion</sub>     | Input data hold time to SI (Shift In)    | 1      | 35  |     | ns   |

| t <sub>RIDS</sub>    | Input data setup to IR (Input Ready)     | 3      | 0   |     | ns   |

| t <sub>AIDH</sub>    | Input data hold time to IR (Input Ready) | 3      | 35  |     | ns   |

| f <sub>in</sub>      | Shift in rate                            | 1      |     | 12  | MHz  |

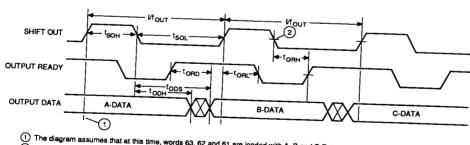

| f <sub>out</sub>     | Shift out rate                           | 4      |     | 12  | MHz  |

| t <sub>soh</sub> †   | Shift out HIGH time                      | 4      | 28  |     | ns   |

| t <sub>sol</sub> †   | Shift out LOW time                       | 4      | 18  |     | ns   |

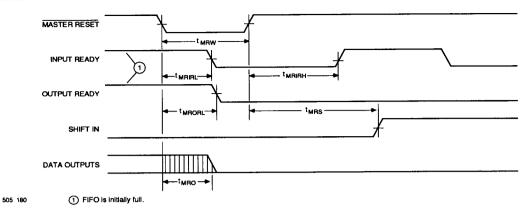

| t <sub>MRW</sub> **  | Master Reset pulse                       | 8      | 40  |     | ns   |

| t <sub>MRS</sub> *** | Master Reset to SI                       | 8      | 45  |     | ns   |

| V <sub>IL</sub> *    | Low level input voltage                  |        |     | 8.0 | ٧    |

| V <sub>H</sub> *     | High level input voltage                 |        | 2.0 |     | V    |

| T,                   | Operating free-air temperature           |        | -55 |     | °C   |

|                      | Operating instant-on case temperature    |        |     | 125 | °C   |

These are absolute voltages with respect to the ground pin on the device and include all overshoots due to system and/or tester noise.

Do not attempt to test these values without suitable equipment.

<sup>\*\*</sup> If the FIFO is not full (IR HIGH) MR LOW forces IR LOW, followed by IR returning high when MR goes high.

<sup>\*\*\*</sup> t<sub>MRS</sub> is measured on initial characterization lots only and is not directly tested in production.

See AC test and high-speed application note.

## **Electrical Characteristics** Over Operating Conditions

| SYMBOL            | PARAMETER                                 |           | TEST CONDITIONS              |                             | MIN | MAX  | UNIT |

|-------------------|-------------------------------------------|-----------|------------------------------|-----------------------------|-----|------|------|

| V <sub>IC</sub>   | Input clamp voltage                       |           | V <sub>cc</sub> = MIN        | I <sub>,</sub> = -18 mA     |     | -1.5 | V    |

| I <sub>IL</sub>   | Low-level input current                   | A Avr     | V <sub>cc</sub> = MAX        | V <sub>1</sub> = 0.45 V     |     | -250 | μА   |

| I <sub>M</sub>    | High-level input current                  |           | V <sub>cc</sub> = MAX        | V, = 2.4 V                  |     | 50   | μА   |

| l,                | Maximum input current                     |           | V <sub>cc</sub> = MAX        | V, = 5.5 V                  |     | 1    | mA   |

|                   |                                           | Ouput, O  | V <sub>cc</sub> = MIN        | I <sub>oL</sub> = 12 mA     | -   | 0.5  | v    |

| V <sub>o.</sub>   | Low-level output voltage                  | IR, OR    |                              | I <sub>oL</sub> = 8 ma      |     |      |      |

|                   |                                           | Output, O | I <sub>oH</sub> = -3.0 mA    |                             |     |      |      |

| V <sub>OH</sub>   | V <sub>oH</sub> High-level output voltage | IR, OR    | V <sub>cc</sub> = MIN        | I <sub>oH</sub> = -0.9 mA   | 2.4 |      | V    |

| l <sub>os</sub> † | Output short-circuit current              |           | V <sub>cc</sub> = MAX        | V <sub>o</sub> = 0 V        | -20 | -90  | mA   |

| l <sub>oz</sub>   | Off-state output current (57L4013D only)  |           |                              | V <sub>o</sub> = 0.4 V      |     | -50  |      |

| l <sub>ozh</sub>  |                                           |           | V <sub>cc</sub> = MAX        | V <sub>o</sub> = 2.4 V      |     | +50  | μА   |

| I <sub>cc</sub>   | Supply current                            |           | V <sub>cc</sub> = MAX All in | puts low. All outputs open. |     | 120  | mA   |

<sup>†</sup> Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

505028

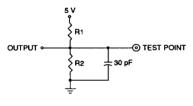

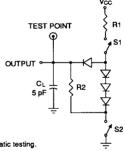

## Standard Test Load\*

## **Three State Test Load\***

Input Pulse Amplitude = 3 V Input Rise and Fall Time (10% Measurements made at 1.5 V

505 107

\*Equivalent test loads may be used for automatic testing.

| l <sub>oL</sub> | R1    | R2     |

|-----------------|-------|--------|

| 12 mA           | 390 Ω | 760 Ω  |

| 8 mA            | 600 Ω | 1200 Ω |

505028A

## Switching Characteristics Over Operating Conditions

| SYMBOL               | PARAMETER FIGURE                      |      | MIN | MAX | UNIT |  |

|----------------------|---------------------------------------|------|-----|-----|------|--|

| t <sub>iRL</sub> †   | Shift In ↑ to Input Ready LOW         | 1    |     | 50  | ns   |  |

| t <sub>iRH</sub> †   | Shift In ↓ to Input Ready HIGH        | 1    |     | 30  | ns   |  |

| t <sub>orl</sub> †   | Shift Out ↑ to Output Ready LOW       | 4    |     | 55  | ns   |  |

| t <sub>orn</sub> †   | Shift Out ↓ Output Ready HIGH         | 4    |     | 55  | ns   |  |

| t <sub>oph</sub> t   | Output Data Hold (previous word)      | 4    | 10  |     | ns   |  |

| t <sub>ops</sub>     | Output Data Shift (next word)         | 4    |     | 50  | ns   |  |

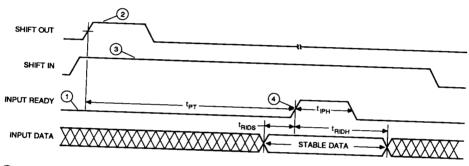

| t <sub>et</sub>      | Data throughput                       | 3, 6 |     | 2.0 | μs   |  |

| t <sub>MRORL</sub>   | Master Reset ↓ to Output Ready LOW    | 8    |     | 65  | ns   |  |

| t <sub>MRIRH</sub> * | Master Reset ↑ to Input Ready HIGH    | 8    |     | 35  | ns   |  |

| t <sub>MRIRL</sub> * | Master Reset ↓ to Input Ready LOW     | 8    |     | 55  | ns   |  |

| t <sub>MRO</sub>     | Master Reset ↓ to Output LOW          | 8    |     | 75  | ns   |  |

| t <sub>IPH</sub>     | Input ready pulse HIGH                | 3    | 15  |     | ns   |  |

| t <sub>oph</sub>     | Output ready pulse HIGH               | 6    | 20  |     | ns   |  |

| t <sub>orid</sub>    | Output ready ↑ to Data Valid          | 4    |     | 0   | ns   |  |

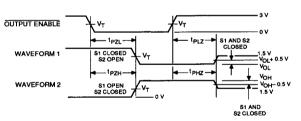

| t <sub>PHZ</sub> **  | Output disable delay (57L4013D only)  | A    |     | 35  | ns   |  |

| t <sub>PL2</sub> **  | Culput disable delay (5/L40/30 offis) |      |     | 35  | 113  |  |

| t <sub>PZL</sub>     | Outsid English Delay (57) 4012D anish | A    |     | 35  | ns   |  |

| t <sub>ezh</sub>     | Output Enable Delay (57L4013D only)   |      |     | 45  | 113  |  |

- See AC test and high-speed application note.

- \* If the FIFO is not full (IR HIGH), MR LOW forces IR LOW, followed by IR returning high when MR goes high.

- \*\* Actual test limits may be different to compensate for ATE.

505029

Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

Figure A. Enable and Disable (57L4013D Only)

## **Military Case Outlines**

| PACKAGE OUTLINE<br>LETTER | CONFORMS TO<br>MIL-M-38510<br>APPENDIX C<br>CASE |  |

|---------------------------|--------------------------------------------------|--|

| 16J                       | D-2                                              |  |

| 18J                       | D-6                                              |  |

505029B

#### **Burn-In Circuitry** Dynamic Burn-In

57L401D

57L4013D

57L402D

505 172

T<sub>ambient</sub> = 125°C V<sub>cc</sub> = 5.25 ± 0.25 V

Square wave pulses on A0 to A8 are:

- 1.  $50\% \pm 15\%$  duty cycle

- 2. Logic "0" = -1 V to 0.7 V

- 3. Logic "1" = 2.4 V to V<sub>cc</sub>

4. Frequency of each address is to be one-half of each preceding input, with A0 beginning at 100 kHZ.

- e.g. A0 = 100 kHz

A1 = 50 kHz ± 10%

A2 = 25 kHz ± 10%

$An = 1/2 An - 1 \pm 10\%$ , etc.

## **Functional Description**

#### **Data Input**

After power up the Master Reset is pulsed low (Figure 8) to prepare the FIFO to accept data in the first location. Master reset must be applied prior to use to ensure proper operation. When Input Ready (IR) is HIGH the first location is ready to accept data from the D\_inputs. Data then present at the data inputs is entered into the first location when the Shift-In (SI) is brought HIGH. An SI HIGH signal causes the IR to go LOW. Once data is entered into the first cell, the transfer of data from any full cell to the adjacent (downstream) empty cell is automatic, activated by an on-chip control. Thus data will stack up at the end of the device while empty locations will "bubble" to the front. t<sub>pr</sub> defines the time required for the first data to travel from input to the output of a previously empty device. When SI is brought LOW and the FIFO is not full, IR will go HIGH, indicating more room is available. If the memory is full, IR will remain LOW. The FIFO should always be cleared by using master reset.

## **Data Output**

Data is read from the Ox outputs. When data is shifted to the output stage, Output Ready (OR) goes HIGH, indicating the presence of valid data. When the OR is HIGH, data may be shifted out by bringing the Shift Out (SO) HIGH. A HIGH signal at SO causes the OR to go LOW. Valid data is maintained while the SO is HIGH. When SO is brought LOW the upstream data, provided the upstream stage has valid data, is shifted to the output stage, OR goes HIGH. If the FIFO is emptied, OR stays LOW and Data output will not be valid.

Input Ready and Output Ready may also be used as status signals indicating that the FIFO is completely full (Input Ready stays LOW for at least  $t_{\rm pr}$ ) or completely empty (Output Ready stays LOW for at least  $t_{\rm pr}$ ).

# AC Test and High-Speed App. Notes

Since the FIFO is a very-high-speed device, care must be exercised in the design of the hardware and the timing utilized within the design. The internal shift rate of the FIFO typically exceeds 20 MHz operation. Device grounding and decoupling is crucial to correct operation as the FIFO will respond to very small glitches due to long reflective lines, high capacitances and/or poor supply decoupling and grounding. We recommend a monolithic ceramic capacitor 0.1  $\mu F$  directly between  $V_{cc}$  and GND with very short lead length. In addition, care must be exercised in how the timing is set up and how the parameters are measured. For example, since an AND gate function is associated with both the Shift-In-Input-Ready combination, as well as the Shift-Out-Output-Ready combination, timing measurements may be misleading, i.e., rising edge of the Shift-In pulse is not recognized until Input Ready is HIGH. If Input Ready is not high due to (a) too high a frequency, or (b) FIFO being full or effected by Master Reset, the Shift-In activity will be ignored. This will affect the device from a functional standpoint, and will also cause the "effective" timing of Input Data Hold time (Tidh) and the next activity of Input Ready (T<sub>IRI</sub>) to be extended relative to Shift-In going HIGH.This same type of situation occurs with  $\rm T_{\rm opl}$  and  $\rm T_{\rm oph}$  as related to Shift-Out. For high-speed applications, proper grounding technique is essential.

505 174

Flaure 1. Input Timing

- 1 Input Ready HIGH indicates space is available and a Shift-In pulse may be applied.

- input Data is loaded into the first word. The Data from the first word is released for "fall through" to second word.

- 3 Input Ready goes LOW indicating the first word is full.

- Shift-in going LOW allows input Ready to sense the status of the first word. The first word is now empty as indicated by input Ready HiGH.

- (5) If the second word is already full then the data remains at the first word. Since the FIFO is now full input Ready remains low.

- Note: Shift-in pulses applied while input Ready is LOW will be ignored (See Figure 3). 505 154

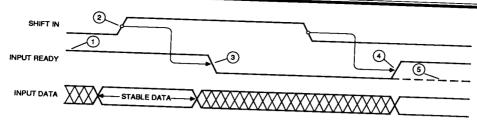

Figure 2. The Mechanism of Shifting Data Into the FIFO

- FIFO is initially full.

- Shift Out pulse is applied. An empty location starts "bubbling" to the front.

- 3 Shift in is held HIGH.

505 176

As soon as Input Ready becomes HIGH the Input Data is loaded into the first word. 505 175

Figure 3. Data is Shifted in Whenever Shift in and Input Ready Are Both HIGH

- ① The diagram assumes that at this time, words 63, 62 and 61 are loaded with A, B and C Data, respectively.

- Output data changes on the falling edge of SO after a valid Shift-Out Sequence, i.e., OR and SO ar both high together.

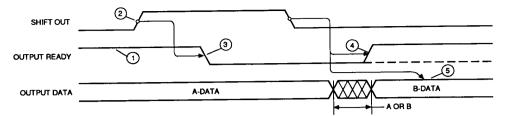

Figure 4. Output Timing

505 177

505 178

505 179

- 1) Ouput Ready HIGH indicates that data is available and a Shift-Out pulse may be applied.

- Shift-Out goes HKGH causing the contents of word 62 (B-DATA) to be released for fall through to word 63. Output data remains as valid A-Data while Shift-Out is HIGH.

- 3 Output Ready goes LOW.

- Shift-out goes LOW causing Output Ready to go HIGH and new data (B) to appear at the data outputs.

- (S) If the FIFO has only one word loaded (A-Data) then Output Ready stays LOW and the output data becomes invalid.

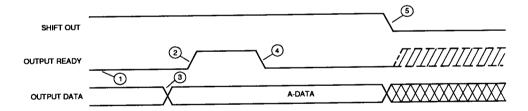

Figure 5. The Mechanism of Shifting Data Out of the FIFO

P.y

2 Shift Out held HIGH.

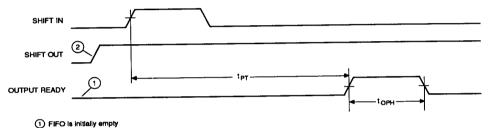

Figure 6.  $t_{\rm pT}$  and  $t_{\rm oph}$  Specification

- 1) Word 63 is empty.

- Output Ready goes HIGH indicating arrival of the new data.

- 3 New data (A) arrives at the outputs (word 63).

- Since Shift Out is held HIGH, Output Ready goes immediately LOW.

- S As soon as Shift Out goes LOW the Output Data is subject to change. Output Ready will go HIGH or LOW depending on whether there are any additional upstream words in the FIFO.

Figure 7. Data is Shifted Out Whenever Shift Out and Output Ready Are Both HIGH

Figure 8. Master Reset Timing