|                           |        |        |    |              | · · · · · · |            |       | RE     | EVISI   | ONS                                                                                                              |                                   |   |      |     |        |      |      |               |      |    |

|---------------------------|--------|--------|----|--------------|-------------|------------|-------|--------|---------|------------------------------------------------------------------------------------------------------------------|-----------------------------------|---|------|-----|--------|------|------|---------------|------|----|

| LTR                       |        |        |    |              | D           | ESCRI      | LPTIC |        |         |                                                                                                                  |                                   |   | D    | ATE | (YR-MO | -DA) |      | APPRO         | OVED |    |

|                           | i      |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      | 1  |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      | 1  |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

| REV                       |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

| SHEET                     |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

| REV                       |        |        |    |              |             |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

| SHEET                     | 15     | 16     | 17 | 18           | 19          | 20         | 21    | 22     | 23      |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

| REV STATE                 |        |        |    | RE           | v           |            |       |        |         |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

| OF SHEETS                 | 3      |        |    | SH           | IEET        |            | 1     | 2      | 3       | 4                                                                                                                | 5                                 | 6 | 7    | 8   | 9      | 10   | 11   | 12            | 13   | 14 |

| PMIC N/A                  |        | 7.1.4  |    |              | PARED E     | sy<br>La C |       | Nicaci | lows    | DI                                                                                                               | DEFENSE ELECTRONICS SUPPLY CENTER |   |      |     |        |      |      |               |      |    |

| STAND                     | ARD]   | (ZED   |    | <del> </del> | KED BY      | <u> </u>   |       |        |         | DAYTON, OHIO 45444                                                                                               |                                   |   |      |     |        |      |      |               |      |    |

|                           | ITAF   |        |    | ~            | lm          | u          | H.    | 10     | oh      | DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444  MICROCIRCUITS, DIGITAL, CMOS, PROCESSOR INTERFACE CIRCUIT, |                                   |   |      |     |        |      |      |               |      |    |

| DRA                       | MIN    | G      |    | APPR         | ROVED E     |            |       |        | 1       |                                                                                                                  |                                   |   |      |     |        |      |      |               |      |    |

| THIS DRAWING FOR USE BY A | ALL DE | PARTME |    | 1            | <u> </u>    |            | Ĺĸ    | lf     | <u></u> | MONOLITHIC SILICON                                                                                               |                                   |   |      |     | :      |      |      |               |      |    |

| AND AGEN<br>DEPARTMEN     |        |        | Ē  | DRAW         |             | PPROVAL    |       |        |         |                                                                                                                  |                                   |   |      |     | T      |      |      |               |      |    |

| AMSC N/A                  |        |        |    |              |             | 3-10       |       |        |         | SIZ<br><b>A</b>                                                                                                  | E                                 |   | E CO |     |        | 59   | 962- | 88 <b>6</b> 4 | 12   |    |

| AHSC N/A                  |        |        |    | KFAT         | SION L      | -EVEL      |       |        |         | <del></del>                                                                                                      | _                                 | ` | 1120 |     | 1      |      |      |               |      |    |

|                           |        |        |    |              |             |            |       |        |         | SHI                                                                                                              | ET                                |   |      |     |        |      |      |               | 1    |    |

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

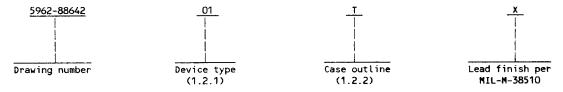

- 1.2 Part or Identifying Number (PIN). The complete PIN shall be as shown in the following example:

1.2.1 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>                              | Clock speed |

|-------------|----------------|------------------------------------------------------|-------------|

| 01          | P1754          | Processor interface with system configuration inputs | 20 MHz      |

| 02          | P1754          | Processor interface with system configuration inputs | 30 MHz      |

| 03          | P1754          | Processor interface with system configuration inputs | 40 MHz      |

| 04          | P1754          | Processor interface                                  | 20 MHz      |

| 05          | P1754          | Processor interface                                  | 30 MHz      |

| 06          | P1754          | Processor interface                                  | 40 MHz      |

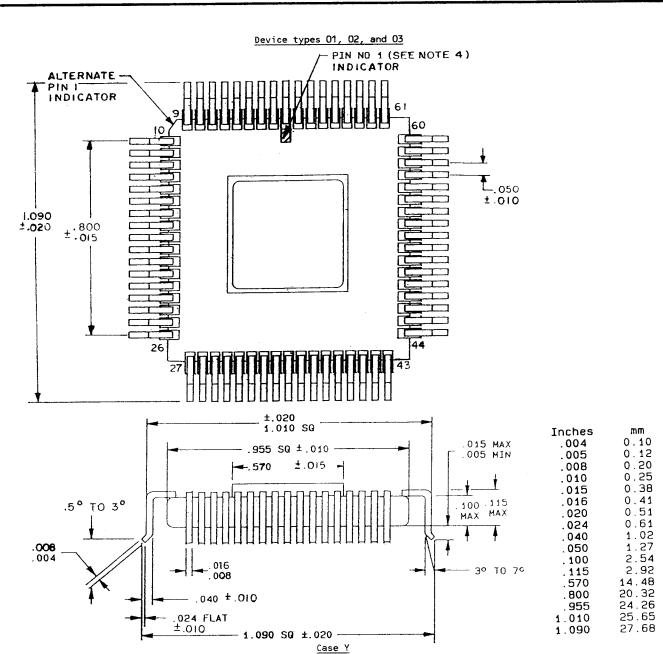

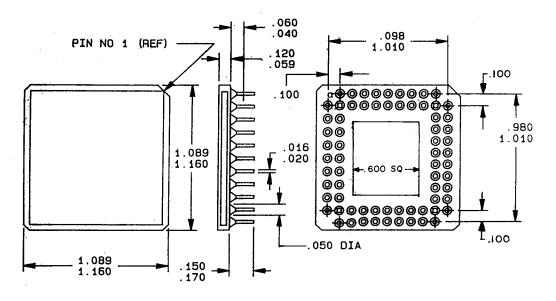

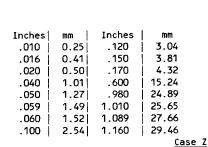

1.2.2 <u>Case outline(s)</u>. The case outline(s) shall be as designated in appendix C of MIL-M-38510, and as follows:

| Outline letter | <u>Case outline</u>                                                                                     |

|----------------|---------------------------------------------------------------------------------------------------------|

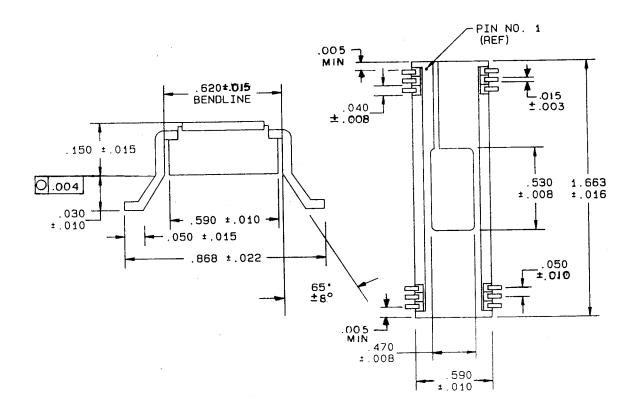

| T              | See figure 2 (64-lead, 1.665" $\times$ .630" $\times$ .190"), dual-in-line package with gull-wing leads |

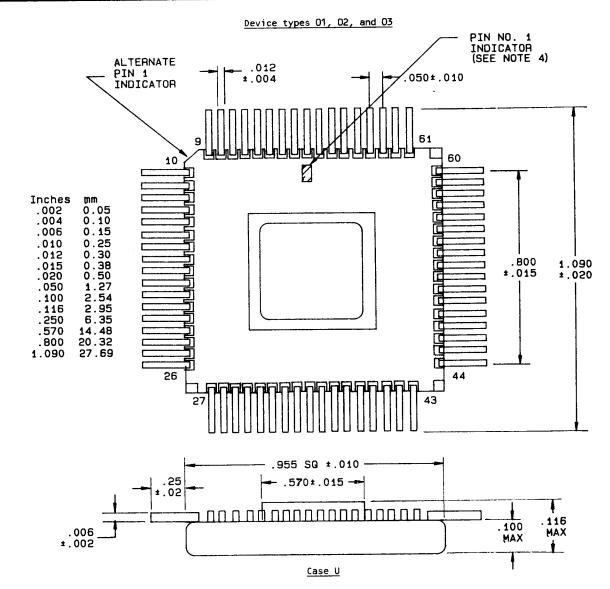

| U              | See figure 2 (68-terminal, .955" x .955" x .115"), leaded chip carrier package with straight leads      |

| X              | See figure 2 (64-lead, 1.665" x .630" x .190"), dual-in-line package                                    |

| Υ              | See figure 2 (68-terminal, .955" x .955" x .115"), leaded chip carrier package with gull-wing leads     |

| Z              | See figure 2 (68-pin, 1.160" x 1.160" x .290"), pin grid array package                                  |

## 1.3 Absolute maximum ratings.

| Supply voltage range, V <sub>CC</sub>                | -0.5 V dc to +7.0 V dc               |

|------------------------------------------------------|--------------------------------------|

| Input voltage range                                  | -0.5 V dc to V <sub>cc</sub> + 0.5 V |

| Storage temperature range                            | -65°C to +150°Č                      |

| Input current range                                  | -30 mA to +5 mA                      |

| Current applied to any output                        | 150 mA                               |

| Maximum power dissipation ( $P_D$ ) $\underline{1}/$ | 1.5 W                                |

| Lead temperature range (soldering 10 seconds)        | <b>300°</b> C                        |

| Thermal resistance, $\Theta_{\mathrm{jC}}$ :         |                                      |

| Cases X and T                                        |                                      |

| Cases Y and U                                        | 5°C/W                                |

| Case Z                                               | 6°C/W                                |

1/ Must withstand the added P<sub>D</sub> due to short circuit test; e.g., I<sub>OS</sub>.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-88642 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 2    |

| 1.4 | Recommended | operating | conditions. |

|-----|-------------|-----------|-------------|

|     |             |           |             |

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standard, and bulletin</u>. Unless otherwise specified, the following specification, standard, and bulletin of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

SPECIFICATION

MILITARY

MIL-M-38510

Microcircuits, General Specification for.

STANDARD

MILITARY

MIL-STD-883

- Test Methods and Procedures for Microelectronics.

BULLETIN

MILITARY

MIL-BUL-103

List of Standardized Military Drawings (SMD's).

(Copies of the specification, standard, and bulletin required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

## 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

- 3.2.1 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

- 3.2.2 (ase outline(s). The case outline(s) shall be as specified on figure 2.

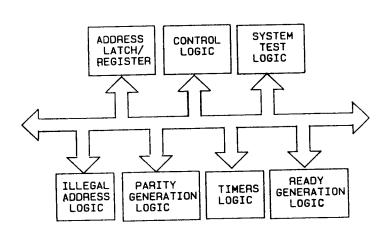

- 3.2.3 Functional block diagram. The functional block diagram shall be as specified on figure 3.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full (case or ambient) operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962- იგნ42 |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHELT<br>3  |

| Test                                                                                                                                                                                | Symbol          |                                                                 | nditions<br>T <sub>C</sub> ≤ +125°C<br>V <sub>CC</sub> ≤ 5.5 V | Group A<br>subgroups | Device<br>type | · · · · · · · · · · · · · · · · · · · |                       | Unit             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------|----------------------------------------------------------------|----------------------|----------------|---------------------------------------|-----------------------|------------------|

|                                                                                                                                                                                     |                 | 4.5 V ≤<br>unless other                                         | $V_{CC} \le 5.5 \text{ V}$ wise specified $1/$                 |                      |                | Min                                   | Max                   | 1                |

| Input high voltage                                                                                                                                                                  | ν <sub>IH</sub> |                                                                 |                                                                | 1,2,3                | All            | 2.0                                   | v <sub>cc</sub> + 0.5 | ٧                |

| Input low voltage                                                                                                                                                                   | VIL             |                                                                 |                                                                | 1,2,3                | All            | -0.5                                  | 0.8                   | ٧                |

| Input clamp diode<br>voltage                                                                                                                                                        | v <sub>CD</sub> | V <sub>CC</sub> = 4.5 V,<br>I <sub>IN</sub> = -18 mA            |                                                                | 1,2,3                | ALL            |                                       | -1.2                  | V                |

| Output high voltage                                                                                                                                                                 | v <sub>OH</sub> | V <sub>CC</sub> = 4.5 V                                         | I <sub>OH</sub> = -8.0 mA                                      | 1,2,3                | ALL            | 2.4                                   |                       | ٧                |

|                                                                                                                                                                                     |                 | V <sub>IN</sub> = 2.0 V,<br>0.8 V                               | $I_{OH} = -300 \mu A$                                          | 1                    | !<br>          | v <sub>cc</sub> -                     |                       | ٧                |

| Output low voltage,                                                                                                                                                                 | V <sub>OL</sub> | V <sub>CC</sub> = 4.5 V<br>V <sub>IN</sub> = 2.0 V,             | I <sub>OL</sub> = 8.0 mA                                       | 1,2,3                | ALL            |                                       | 0.5                   | V                |

| except A <sub>0</sub> - A <sub>15</sub>                                                                                                                                             |                 | V <sub>IN</sub> = 2.0 V,                                        | I <sub>OL</sub> = 300 μA                                       | 1                    |                |                                       | 0.2                   | ٧                |

| Output low voltage,                                                                                                                                                                 | V <sub>OL</sub> | V <sub>CC</sub> = 4.5 V<br>V <sub>IN</sub> = 2.0 V,             | I <sub>OL</sub> = 20 mA                                        | 1,2,3                | ALL            |                                       | 0.5                   | V                |

| A <sub>0</sub> - A <sub>15</sub>                                                                                                                                                    |                 | 0.8 V                                                           | I <sub>OL</sub> = 300 μA                                       |                      |                |                                       | 0.2                   | V                |

| Input high current, except IB <sub>O</sub> - IB <sub>15</sub> , parity/IB <sub>16</sub> , SING ERR, A <sub>O</sub> /EXT AD <sub>O</sub> A <sub>1</sub> /EXT AD <sub>1</sub> , STRBA | IIH             | V <sub>IN</sub> = V <sub>CC</sub> '<br>V <sub>CC</sub> = 5.5' V |                                                                | 1,2,3                | ALL            |                                       | 10                    | µA<br> <br> <br> |

| Input high current, IB <sub>O</sub> -IB <sub>15</sub> , parity/IB <sub>16</sub> , A <sub>O</sub> /EXT AD <sub>O</sub> , A <sub>1</sub> /EXT AD <sub>1</sub>                         | IIH             |                                                                 |                                                                | 1,2,3<br> <br> <br>  | ALL            |                                       | 50<br> <br>           | μA<br> <br> <br> |

| Input high<br>current, STRBA,<br>SING ERR                                                                                                                                           | IIH             | V <sub>IN</sub> = V <sub>CC</sub> '<br> V <sub>CC</sub> = 5.5 V |                                                                | 1,2,3                | All            |                                       | 500                   | μΑ               |

| Input low current, except IB <sub>0</sub> - IB <sub>15</sub> , parity/IB <sub>16</sub> , SING ERR, A <sub>0</sub> /EXT_AD <sub>0</sub> A <sub>1</sub> /EXT AD <sub>1</sub> , STRBD, | IIL             | V <sub>IN</sub> = GND,<br>V <sub>CC</sub> = 5.5 V               |                                                                | 1,2,3                | ALL            |                                       | -10<br>               | ДА               |

| TEST ON                                                                                                                                                                             |                 | -                                                               |                                                                |                      | <br>           |                                       | <del> </del>          | -                |

| Input low current, IBO-IB <sub>15</sub> , parity/IB <sub>16</sub> , SING ERR, A <sub>O</sub> /EXT AD <sub>O</sub> , A <sub>1</sub> /EXT AD <sub>1</sub>                             | IIL             |                                                                 |                                                                | 1,2,3                | ALL            |                                       | <b>-50</b>            | μA<br> <br> <br> |

| Input low current,<br>STRBD, TEST ON                                                                                                                                                | IIL             |                                                                 |                                                                | 1,2,3                | ALL            |                                       | -500                  | μА               |

| See footnotes at end of table                                                                                                                                                       | l               |                                                                 |                                                                |                      |                |                                       |                       | •                |

| STANDAR<br>MILITARY                                                                                                                                                                 | DRAWING         |                                                                 | SIZE<br>A                                                      |                      |                |                                       | 5962-€                | 38642            |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444                                                                                                                                |                 |                                                                 |                                                                | REVISI               | ONIES          | 191                                   | SHEET                 |                  |

| Test                                                     | Symbol                |                                                                                             | Group A<br>subgroups | Device  <br>  type |     |     | Unit |

|----------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------|----------------------|--------------------|-----|-----|------|

|                                                          |                       | unless otherwise specified 1/                                                               |                      | ļ                  | Min | Max |      |

| Output 3-state current                                   | I <sub>OZH</sub>      | V <sub>OUT</sub> = 2.4 V,<br>V <sub>CC</sub> = 5.5 V                                        | 1,2,3                | All                |     | 50  | μΑ   |

| Output 3-state current                                   | IozL                  | V <sub>OUT</sub> = 0.5 V,<br>V <sub>CC</sub> = 5.5 V                                        | 1,2,3                | All                |     | -50 | μA   |

| Quiescent power<br>supply current<br>(CMOS input levels) | Iccqc                 | $V_{IN} < 0.2 \text{ V or } > V_{CC}$ -0.2 V, f = 0 MHz, outputs open, $V_{CC}$ = 5.5 V     | 1,2,3                | All                |     | 10  | mA   |

| Quiescent power<br>supply current<br>(TTL input levels)  | IccQT                 | V <sub>IN</sub> = 3.4 V, f = 0 MHz,<br>all inputs, outputs open,<br>V <sub>CC</sub> = 5.5 V | 1,2,3                | ALL                |     | 50  | mA   |

| Dynamic power supply                                     | ICCD                  | V <sub>IN</sub> = 0 V to V <sub>CC</sub> ,<br>tr = tf = 2.5 ns typically,                   | 1,2,3                | 01,04              |     | 40  | mA   |

| current                                                  |                       | outputs open,                                                                               |                      | 02,05              |     | 50  | mA   |

|                                                          |                       | v <sub>CC</sub> = 5.5 v                                                                     |                      | 03,06              |     | 60  | mA   |

| Output short circuit current <u>2</u> /                  | Ios                   | V <sub>OUT</sub> = GND,<br>V <sub>CC</sub> = 5.5 V                                          | 1,2,3                | ALL                | -25 |     | mA   |

| Input capacitance                                        | CIN                   | See 4.3.1c, inputs only                                                                     | 4                    | All                |     | 10  | pF   |

| Output/bi-directional capacitance                        | C <sub>OUT</sub>      | See 4.3.1c,<br>outputs,<br>(including I/O buffers)                                          | 4                    | ALL                |     | 15  | pF   |

| Functional tests                                         |                       | See 4.3.1d, V <sub>CC</sub> = 4.5 V, 5.5 V                                                  | 7,8                  | ALL                |     |     |      |

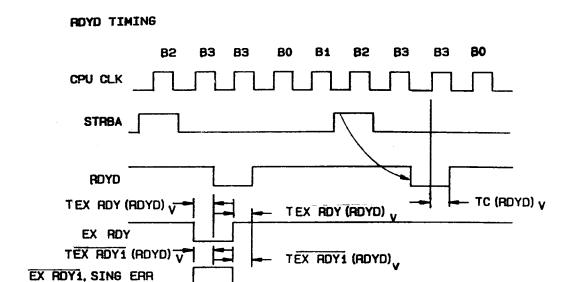

| Time from external                                       | TEX RDY-              | See figure 4, V <sub>CC</sub> = 4.5 V                                                       | 9,10,11              | 01,04              |     | 16  | ns   |

| ready to ready data<br>valid                             | (RDYD) <sub>V</sub>   | <u>3</u> /                                                                                  |                      | 02,05              |     | 14  | ns   |

|                                                          |                       |                                                                                             |                      | 03,06              |     | 12  | ns   |

| Time from clock                                          | TC-                   |                                                                                             | 9,10,11              | 01,04              |     | 28  | ns   |

| read to ready data<br>valid                              | (RDYD) <sub>V</sub>   |                                                                                             |                      | 02,05              |     | 22  | ns   |

|                                                          |                       |                                                                                             | ļ<br>                | 03,06              |     | 16  | ns   |

| Time from strobe                                         | TSTRBA <sub>H</sub> - |                                                                                             | 9,10,11              | 01,04              |     | 29  | ns   |

| address high to<br>address bus valid                     | (A) (                 |                                                                                             |                      | 02,05              |     | 21  | ns   |

|                                                          |                       | ,                                                                                           |                      | 03,06              |     | 19  | ns   |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-0.042 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEF1<br>5 |

| Test                                 | Symbol                       | Symbol Conditions $-55^{\circ}C \le T_{C} \le +125^{\circ}C$                                                    |         | Device  <br>type | Limits |     | Unit |

|--------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------|---------|------------------|--------|-----|------|

|                                      |                              | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>  4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V<br>  unless otherwise specified <u>1</u> / | ļ       |                  | Min    | Max | 1    |

| ime from                             | TIBA <sub>V</sub> -          | See figure 4, V <sub>CC</sub> = 4.5 V                                                                           | 9,10,11 | 01,04            |        | 31  | ns   |

| information bus<br>address to        | (A) <sub>V</sub>             | <u>3</u> /                                                                                                      |         | 02,05            |        | 22  | ns   |

| address bus<br>valid                 |                              |                                                                                                                 |         | 03,06            |        | 20  | ns   |

| ime from falling                     | TFC(R)                       | 1                                                                                                               | 9,10,11 | 01,04            |        | 24  | ns   |

| clock to read low                    |                              |                                                                                                                 |         | 02,05            |        | 18  | ns   |

|                                      |                              |                                                                                                                 |         | 03,06            |        | 12  | ns   |

| ime from strobe                      | TSTRBD <sub>H</sub> -        | 1                                                                                                               | 9,10,11 | 01,04            |        | 24  | ns   |

| data high to read<br>high            | (K)H                         | <br>                                                                                                            |         | 02,05            |        | 18  | ns   |

|                                      |                              | <br>                                                                                                            |         | 03,06            |        | 12  | ns   |

| ime from strobe<br>data low to write | TSTRBD                       |                                                                                                                 | 9,10,11 | 01,04            |        | 26  | ns   |

| low                                  | (W)                          |                                                                                                                 |         | 02,05            |        | 20  | ns   |

|                                      |                              |                                                                                                                 |         | 03,06            |        | 15  | ns   |

| ime from strobe                      | TSTRBD <sub>H</sub> -        |                                                                                                                 |         | 01,04            |        | 26  | ns   |

| data high to write<br>high           | \w/H                         |                                                                                                                 |         | 02,05            |        | 20  | ns   |

|                                      |                              |                                                                                                                 |         | 03,06            |        | 15  | ns   |

| ime from infor-                      | TIBD <sub>IN</sub> -         |                                                                                                                 | 9,10,11 | 01,04            |        | 22  | ns   |

| mation bus data in to memory         | (ME PA ER)                   |                                                                                                                 |         | 02,05            |        | 17  | ns   |

| parity error low                     |                              |                                                                                                                 |         | 03,06            |        | 12  | ns   |

| Time from infor-                     | TIBAIN-                      | <del>-</del><br> <br>                                                                                           | 9,10,11 | 01,04            |        | 30  | ns   |

| mation bus<br>address in to          | (EX AD ER)                   |                                                                                                                 |         | 02,05            |        | 25  | ns   |

| external address<br>error            |                              |                                                                                                                 |         | 03,06            |        | 20  | ns   |

| ime from strobe                      | TSTRBD                       | 1<br>!                                                                                                          | 9,10,11 | 01,04            |        | 26  | ns   |

| data low to<br>start-up run          | (STRT ROM̄) <sub>V</sub><br> | /  <br>                                                                                                         |         | 02,05            |        | 20  | ns   |

| valid                                | valid                        |                                                                                                                 | 03,06   |                  | 15     | ns  |      |

See footnotes at end of table.

| STANDARDIZED  MILITARY DRAWING                       | SIZE<br>A |                | 5962-88642 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>6 |

| Test                                   | Symbol                | Conditions<br>$-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$                                                      |         | Device<br>type | Limits |     | Unit |

|----------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------|---------|----------------|--------|-----|------|

|                                        |                       | $-55^{\circ}C \le T_C \le +125^{\circ}C$<br>$4.5 \ V \le V_{CC} \le 5.5 \ V$<br>unless otherwise specified $1/$ |         |                | Min    | Max |      |

| Time from falling                      | TFC-                  | 0 4: / 2 - / 5 2                                                                                                | 9,10,11 | 01,04          |        | 30  | ns   |

| clock to infor-<br>mation bus valid    | (IB OUT)              | See figure 4, $V_{CC} = 4.5 \text{ V}$                                                                          |         | 02,05          |        | 25  | ns   |

|                                        |                       |                                                                                                                 |         | 03,06          |        | 25  | ns   |

| Time from rising                       | TC-                   |                                                                                                                 | 9,10,11 | 01,04          |        | 30  | ns   |

| edge of clock<br>to timer clock        | (TIMER<br>  CLK)      |                                                                                                                 |         | 02,05          |        | 25  | ns   |

|                                        |                       |                                                                                                                 |         | 03,06          |        | 20  | ns   |

| Time from infor-                       |                       | 1                                                                                                               | 9,10,11 | 01,04          |        | 25  | ns   |

| mation bus data (IB16) to parity valid | (IB16)                | 6)                                                                                                              |         | 02,05          |        | 20  | ns   |

|                                        |                       |                                                                                                                 |         | 03,06          |        | 18  | ns   |

| · · · · · · · · · · · · · · · · · · ·  | TEXT AD               |                                                                                                                 | 9,10,11 | 01,04          | 10     |     | ns   |

| setup time                             | (CLKB3)               | )                                                                                                               |         | 02,05          | 10     |     | ns   |

|                                        |                       |                                                                                                                 |         | 03,06          | 10     |     | ns   |

| Time from external                     | TEX RDY1-             | 1                                                                                                               | 9,10,11 | 01,04          |        | 28  | ns   |

| ready data to<br>ready data            | (RDYD) <sub>V</sub>   |                                                                                                                 |         | 02,05          |        | 24  | ns   |

| valid                                  |                       |                                                                                                                 |         | 03,06          |        | 21  | ns   |

| Time from falling                      | TFC-                  | -                                                                                                               | 9,10,11 | 01,04          |        | 30  | ns   |

| clock to SCR<br>SCR enable;            | (SCR EN)              |                                                                                                                 |         | 02,05          |        | 24  | ns   |

| case types T<br>and X only             |                       |                                                                                                                 |         | 03,06          |        | 24  | ns   |

| Time from STRBD                        | TSTRBD <sub>H</sub> - | 1                                                                                                               | 9,10,11 | 01,04          |        | 30  | ns   |

| high to<br>SCR enable; case            | (SCR EN)              |                                                                                                                 |         | 02,05          |        | 24  | ns   |

| types T and<br>X only                  |                       |                                                                                                                 | 1       | 03,06          |        | 24  | ns   |

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-იია42 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 7    |

<sup>1/2</sup> Unless otherwise specified, all testing shall be conducted under worst-case conditions. 1/2 Only one output may be shorted at a time. 1/2 All measurements of delay times on active signals are related to the 1.5 V levels.

| Device types 04, 05, 06 |                                      |                    |                                        |                    |                                                        |                    |                                     |

|-------------------------|--------------------------------------|--------------------|----------------------------------------|--------------------|--------------------------------------------------------|--------------------|-------------------------------------|

| Case o                  | utlines                              | T and X            |                                        |                    |                                                        |                    |                                     |

| Terminal<br>number      | Terminal<br>symbol                   | Terminal<br>number | Terminal<br>symbol                     | Terminal<br>number | Terminal<br>  symbol                                   | Terminal<br>number | Terminal<br>symbol                  |

| 1 2                     | GND<br>SCR EN                        | 17<br>18           | IB <sub>8</sub>                        | 33<br>34           | A <sub>15</sub><br>A <sub>14</sub>                     | 49<br>50           | A <sub>O</sub> /EXT AD <sub>O</sub> |

| 3 4                     | TEST ON                              | 19<br>20           | GND<br>IB                              | 35<br>36           | A <sub>13</sub><br>A <sub>12</sub>                     | 51<br>52           | CPU CLK<br>STRBA                    |

| 5                       | RESET<br>TEST END                    | 21<br>22           | IB <sub>11</sub><br>IB <sub>12</sub>   | 37<br>38           | A <sub>11</sub><br>A <sub>10</sub>                     | 53<br>54           | STRBD<br>STRB EN                    |

| 7                       | TIMER CLK<br>EX RDY1                 | 23<br>24           | IB <sub>13</sub><br>IB <sub>14</sub>   | 39<br>40           | A <sub>9</sub> A <sub>8</sub>                          | 55<br>56           | EX RDY<br>RDYD                      |

| 9<br>10                 | IB <sub>O</sub><br>  IB <sub>1</sub> | 25<br>26           | IB <sub>15</sub><br>  IB <sub>16</sub> | 41<br>42           | A <sub>7</sub><br> A <sub>6</sub>                      | 57                 | R/W<br>GND                          |

| 11<br>12                | IB <sub>2</sub> IB <sub>3</sub>      | 27<br>28           | ME PA ER/RAM DIS<br>EX AD ER/SING ERR  | 43<br>44           | A <sub>5</sub>                                         | 59<br>60           | M/IO<br> MEMW                       |

| 13<br>14                | IB <sub>4</sub><br>  IB <sub>5</sub> | 29<br>30           | INTA<br>STRT ROM                       | 45<br>46           | A <sub>3</sub><br> GND                                 | 61<br>62           | MEMR<br>IOW                         |

| 15<br>16                | IB <sub>6</sub><br>  IB <sub>7</sub> | 31 32              | V <sub>CC</sub><br> GND                | 47<br>48           | A <sub>2</sub><br> A <sub>1</sub> /EXT AD <sub>1</sub> | 63<br>64           | IOR<br>V <sub>CC</sub>              |

FIGURE 1. <u>Terminal connections</u>.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-88642 |

|---------------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                             |           | REVISION LEVEL | SHEET<br>8 |

| Device             | types                                |                    | 01, 02, 03                             |                    |                                                        |                    |                                     |  |  |

|--------------------|--------------------------------------|--------------------|----------------------------------------|--------------------|--------------------------------------------------------|--------------------|-------------------------------------|--|--|

| Case o             | utlines                              |                    | U and Y                                |                    |                                                        |                    |                                     |  |  |

| Terminal<br>number | Terminal<br>symbol                   | Terminal<br>number | Terminal<br>symbol                     | Terminal<br>number | Terminal<br>  symbol                                   | Terminal<br>number | Terminal<br>symbol                  |  |  |

| 1<br>2             | GND<br>SC <sub>O</sub>               | 18                 | EX RDY1                                | 35<br>36           | A <sub>15</sub><br>A <sub>14</sub>                     | 52<br>53           | sc <sub>4</sub><br> sc <sub>3</sub> |  |  |

| 3                  | sc <sub>1</sub>                      | 20                 | IB <sub>9</sub>                        | 37                 | A <sub>13</sub>                                        | 54                 | тс                                  |  |  |

| 4                  | TEST ON                              | 21                 | GND                                    | 38                 | A <sub>12</sub>                                        | 55                 | CPU CLK                             |  |  |

| 5<br>6             | RESET<br>TEST END                    | 22 23              | IB <sub>10</sub><br>  IB <sub>11</sub> | 39<br>40           | A <sub>11</sub><br>A <sub>10</sub>                     | 56<br>57           | STRBA<br> STRBD                     |  |  |

| 7<br>8             | TIMER CLK                            | 24                 | IB <sub>12</sub><br>  IB <sub>13</sub> | 41<br>42           | A <sub>9</sub>                                         | 58<br>59           | STRB EN<br>EX RDY                   |  |  |

| 9<br>10            | IBO<br>CC                            | 26<br>27           | IB <sub>14</sub><br>  IB <sub>15</sub> | 43<br>  44         | A <sub>7</sub> A <sub>6</sub>                          | 60<br>61           | RD <u>Y</u> D<br> R/W               |  |  |

| 11<br>12           | IB <sub>1</sub>                      | 28<br>29           | PARITY/IB<br>ME PA ER/RAM DIS          | 45<br>46           | A <sub>5</sub><br>  A <sub>4</sub>                     | 62                 | GN <u>D</u><br>M/IO                 |  |  |

| 13<br>14           | IB <sub>3</sub><br>  IB <sub>4</sub> | 30<br>31           | EX AD ER/SING ERR                      | 47<br>48           | A <sub>3</sub><br> GND                                 | 64                 | MEMW<br>MEMR                        |  |  |

| 15<br>16           | IB <sub>5</sub><br>  IB <sub>6</sub> | 32<br>33           | STRT ROM                               | 49<br>50           | A <sub>2</sub><br> A <sub>1</sub> /EXT AD <sub>1</sub> | 66<br>67           | IOW<br>IOR                          |  |  |

| 17                 | IB <sub>7</sub>                      | 34                 | GND                                    | 51                 | A <sub>O</sub> /EXT AD <sub>O</sub>                    | 68                 | v <sub>cc</sub>                     |  |  |

FIGURE 1. Terminal connections - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-88642 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 9    |

| Devi | ce types         |     | 01, 02, 03      |     |                                     |     |                          |  |

|------|------------------|-----|-----------------|-----|-------------------------------------|-----|--------------------------|--|

| Case | outline          |     |                 |     | Z                                   |     |                          |  |

| Pin  | Pin Name         | Pin | Pin Name        | Pin | Pin Name                            | Pin | Pin Name                 |  |

| B1   | V <sub>CC</sub>  | L2  | GND             | K11 | EX RDY                              | A10 | GND                      |  |

| B2   |                  | K2  | SC <sub>2</sub> | K10 | STRB EN                             | B10 | A <sub>8</sub>           |  |

| C1   | IB <sub>13</sub> | L3  | TIMER CLK       | J11 | STRBD                               | A9  | A <sub>9</sub>           |  |

| C2   | IB <sub>12</sub> | K3  | TEST END        | J10 | STRBA                               | B9  | A <sub>10</sub>          |  |

| D1   | IB <sub>11</sub> | L4  | RESET           | H11 | CPU CLK                             | A8  | A <sub>11</sub>          |  |

| D2   | IB <sub>10</sub> | K4  | TEST ON         | H10 |                                     | B8  | A <sub>12</sub>          |  |

| E1   | IB <sub>9</sub>  | L5  | sc <sub>1</sub> | G11 | sc <sub>3</sub>                     | A7  | A <sub>13</sub>          |  |

| E2   |                  | K5  | sc <sub>0</sub> | G10 | sc <sub>4</sub>                     | B7  | A <sub>14</sub>          |  |

| F1   | EX RDY1          | L6  | V <sub>CC</sub> | F11 | A <sub>O</sub> /EXT AD <sub>O</sub> | A6  | A <sub>15</sub>          |  |

| F2   |                  | K6  | IOR             | F10 | A <sub>1</sub> /EXT AD <sub>1</sub> | B6  | GND                      |  |

| G1   | IB <sub>6</sub>  | L7  | IOW             | E11 | A <sub>2</sub>                      | A5  | V <sub>CC</sub>          |  |

| G2   |                  | K7  | MEMR            | E10 | GND                                 | B5  | STRT ROM                 |  |

| H1   | 1B <sub>4</sub>  | L8  | ME <u>MW</u>    | D11 | A <sub>3</sub>                      | A4  | INTA                     |  |

| H2   | 1B <sub>3</sub>  | K8  | M/IO            | D10 | A <sub>4</sub>                      | B4  | EX AD ER                 |  |

| J1   | IB <sub>2</sub>  | L9  | GN <u>D</u>     | c11 | A <sub>5</sub>                      | A3  | ME PA ER                 |  |

| J2   |                  | K9  | R/W             | c10 | A <sub>6</sub>                      | B3  | IB <sub>16</sub> /PARITY |  |

| к1   | IB <sub>O</sub>  | L10 | RDYD            | B11 | A <sub>7</sub>                      | A2  | IB <sub>15</sub>         |  |

FIGURE 1. <u>Terminal connections</u> - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-88642  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>10 |

## Device types 04, 05, and 06

| Inches | mm   | Inches | mm    |

|--------|------|--------|-------|

| .003   | 0.08 | .040   | 1.01  |

| .004   | 0.10 | .050   | 1.27  |

| .005   | 0.13 | .150   | 3.81  |

| .008   | 0.20 | .470   | 11.93 |

| .010   | 0.25 | .530   | 13.46 |

| .015   | 0.38 | .590   | 14.98 |

| .016   | 0.41 | .620   | 15.74 |

| .022   | 0.55 | .868   | 22.04 |

| .030   | 0.76 | 1.663  | 42.24 |

# Case T

- 1. Dimensions are in inches.

- 2. Metric equivalents are given for general information only.

- 3. Unless otherwise specified, tolerances are .02 (0.51 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

FIGURE 2. Case outlines.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-88642  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>11 |

- 1. Dimensions are in inches.

- Metric equivalents are given for general information only.

- 3. Unless otherwise specified, tolerances are .02 (0.51 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

- 4. Pin 1: Indicator can be either rectangle, dot, or triangle at specified location or referenced to the uniquely beveled corner.

- 5. Corners indicated as notched may be either notched or square (with radius).

FIGURE 2. Case outlines - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-88642 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 12   |

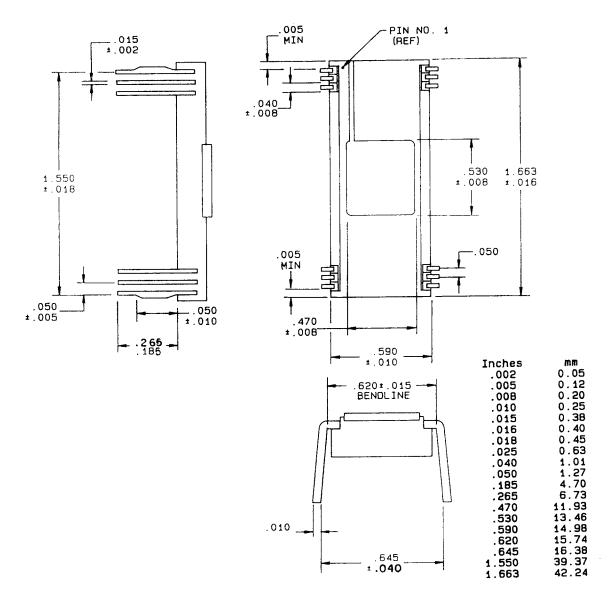

## Device types 04, 05, and 06

# Case X

- 1. Dimensions are in inches.

- 2. Metric equivalents are given for general information only.

- Unless otherwise specified, tolerances are .02 (0.51 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

FIGURE 2. <u>Case outlines</u> - Continued.

| STANDARDIZED  MILITARY DRAWING  DEFENSE ELECTRONICS SUPPLY CENTER  DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-88642 |

|---------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                       |           | REVISION LEVEL | SHEET      |

- 1. Dimensions are in inches.

- 2. Metric equivalents are given for general information only.

- Unless otherwise specified, tolerances are .02 (0.51 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

- 4. Pin 1: Indicator can be either rectangle, dot, or triangle at specified location or referenced to the uniquely beveled corner.

- 5. Corners indicated as notched may be either notched or square (with radius).

FIGURE 2. Case outlines - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-88642  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>14 |

### Device types 01, 02, and 03

- Dimensions are in inches.

- 2. Metric equivalents are given for general information only.

- 3. Unless otherwise specified, tolerances are .02 (0.51 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

- 4. Pin 1: Indicator can be either rectangle, dot, or triangle at specified location or referenced to the uniquely beveled corner.

FIGURE 2. <u>Case outlines</u> - Continued.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-88642  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>15 |

FIGURE 3. Functional block diagram.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-88642  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>16 |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-88642 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET      |

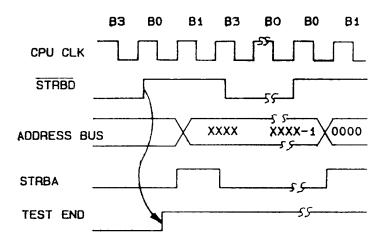

TEST END TIMING (NOTE 1)

- 1. The last two inst<u>ructions</u> executed during system test are: XIO RA, 1F44, 0 and JC 7, 0000 hex, 0. After execution of the IOW bus cycle, the XIO proceeds by filling the instruction pipe with two memory <u>read</u> bus cycles where the opcode 7070 hex and 0000 hex are entered to the processor. As from the end of STRBD in the second cycle, TEST END is asserted. At this point, the execution of IC starts by first issuing two fetch cycles from the "old PC" (from addresses XXXX & XXXX+1). The data will be taken from system memory (because TEST END is asserted) but both the address and data are irrelevant. Following that, IC will start filling the pipe from address 0000 hex and 0001 hex, now from the system memory to start user's program execution.

- 2. All timing measurements on active signals relate to 1.5  $\rm V$  levels.

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE |                | 5962-88642  |

|------------------------------------------------------|------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |      | REVISION LEVEL | SHEET<br>18 |

- 3.5 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103 (see 6.6 herein).

- 3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.6 herein). The certificate of compliance submitted to DESC-ECC prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change</u>. Notification of change to DESC-ECC shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.9 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

## 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition D using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

TABLE II. Electrical test requirements.

| MIL-STD-883 test requirements                                      | Subgroups<br>(per method<br>5005, table I) |

|--------------------------------------------------------------------|--------------------------------------------|

| Interim electrical parameters (method 5004)                        | 1, 2, 7, 8A                                |

| Final electrical test parameters (method 5004)                     | 1*, 2, 3, 7*,<br>8, 9, 10, 11              |

| Group A test requirements (method 5005)                            | 1, 2, 3, 4, 7,<br>8, 9, 10, 11             |

| Groups C and D end-point<br>electrical parameters<br>(method 5005) | 1, 2, 3, 7, 8,<br>9, 10, 11                |

| Additional electrical subgroups for group C periodic inspections   |                                            |

<sup>\*</sup> PDA applies to subgroups 1 and 7.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-88642  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>20 |

4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

#### 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 ( $c_{\rm IN}$  and  $c_{\rm OUT}$  measurements) shall be measured only for the initial test and after process or design changes which may affect input capacitance. A minimum sample size of five devices with zero rejects shall be required.

- d. Subgroups 7 and 8 shall consist of verifying the functionality of the device. These tests form a part of the vendors test tape and shall be maintained and available from the approved sources of supply.

#### 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition D using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_{\Delta} = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

#### PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

#### 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-481 using DD Form 1693, Engineering Change Proposal (Short Form).

- 6.4 Record of users. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronics devices (FSC 5962) should contact DESC-ECT, telephone (513) 296-6022.

- 6.5 Pin descriptions. See table III.

- 6.6 <u>Comments</u>. Comments on this drawing should be directed to DESC-ECC, Dayton, Ohio 45444, or telephone (513) 296-8526.

- 6.7 Approved sources of supply. Approved sources of supply are listed in MIL-BUL-103. The vendors listed in MIL-BUL-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DESC-ECC.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-88642  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>21 |

TABLE III. Pin descriptions.

| Mnemonic                           | Name                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU CLK                            | CPU Clock                         | A single phase input clock signal (0-40 MHz, 40% to 60% duty cycle).                                                                                                                                                                                                                                                                                                                                                                                                     |

| STRBA                              | Strobe Address                    | An active high input which latches the contents of IB(0:15) into the address latches.                                                                                                                                                                                                                                                                                                                                                                                    |

| STRBD                              | Strobe Data                       | An active low input which is used for writing or reading data to or from the device and also to produce the external memory and I/O strobes.                                                                                                                                                                                                                                                                                                                             |

| TIMER CLK                          | Timer Clock                       | A 100 kHz output (fixed frequency) based on the programmed operating frequency of the CPU clock.                                                                                                                                                                                                                                                                                                                                                                         |

| MEMW                               | Memory Write Strobe               | An active low output produced in memory write cycles.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MEMR                               | Memory Read Strobe                | An active low output produced in memory read cycles.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IOW                                | I/O Write Strobe                  | An active low output produced in output write cycles.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| IOR                                | I/O Read Strobe                   | An active low output produced in input read cycles.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INTA                               | Interrupt Acknowledge<br>  Strobe | An active low output produced after any interrupt, corresponding to an output write to address 1000 (Hex).                                                                                                                                                                                                                                                                                                                                                               |

| SCR EN                             | System Configuration              | An active low output (in 64 pin only) produced any time an input read from address 8410 (Hex), read system configuration is executed.                                                                                                                                                                                                                                                                                                                                    |