|                       |                      |                  |     |      |                |                |       | RE           | EVISI    | ONS      |       |    |                                       |     |        |             |              |                                       |      |             |

|-----------------------|----------------------|------------------|-----|------|----------------|----------------|-------|--------------|----------|----------|-------|----|---------------------------------------|-----|--------|-------------|--------------|---------------------------------------|------|-------------|

| LTR                   |                      |                  |     |      | D:             | ESCR           | LPTIC | ON           |          |          |       |    | D                                     | ATE | (YR-MO | -DA)        |              | APPR                                  | OVED | )           |

| LTR                   |                      |                  |     |      | D              | ESCR           | IPTIC | ON .         |          |          |       |    | D                                     | ATE | (YR-MO | -DA)        |              | ΑΥΥΚ                                  | ΟVΕD |             |

| REV                   |                      |                  |     |      |                |                |       |              | <u> </u> |          |       |    |                                       |     |        |             |              |                                       |      |             |

| SHEET                 |                      |                  |     |      |                |                |       |              |          |          |       |    |                                       |     |        |             |              |                                       | ļ    |             |

| REV                   |                      |                  |     |      |                |                |       |              |          |          |       |    |                                       |     |        |             |              |                                       |      |             |

| SHEET                 | 15                   | 16               | 17  | 18   | 19             | 20             | 21    | 22           | 23       | 24       | 25    | 26 | 27                                    | 28  | 29     |             |              |                                       |      |             |

| REV STAT              | US                   |                  |     | RE   | v              |                |       |              |          |          |       |    |                                       |     |        |             |              |                                       |      |             |

| OF SHEET              | S                    |                  |     | SH   | ŒET            |                | 1     | 2            | 3        | 4        | 5     | 6  | 7                                     | 8   | 9      | 10          | 11           | 12                                    | 13   | 14          |

| PMIC N/A              |                      |                  |     | PREP | ARED E         | nie (          | ar    | Care         | _        | Di       | EFENS |    |                                       |     |        | PPLY<br>454 | CEN'         | rer                                   |      |             |

|                       | ARDI<br>ITAI<br>AWIN | RY               | 1   | CHEC | KED B          |                | Pm    | ./km         |          |          |       |    |                                       |     |        |             |              | · · · · · · · · · · · · · · · · · · · |      | <del></del> |

| THIS DRAWIN           | IG IS A              | VAILAI<br>PARTME | NTS | APPR | OVED           | 3Y<br><u>~</u> |       | self<br>self | <u>/</u> |          |       |    |                                       |     |        |             | GRAN<br>SILI |                                       |      | DMA         |

| AND AGEN<br>DEPARTMEN |                      |                  |     | DRAW |                | PROVAL         |       |              |          |          |       | I  | · · · · · · · · · · · · · · · · · · · |     | Ι      |             |              |                                       |      |             |

| AMSC N/A              | 1                    |                  |     | REVI | 92-0<br>SION I | 09-29<br>LEVEL | 1     | <del> </del> |          | SIZ<br>A | E     |    | E CO                                  |     |        | 59          | 962-         | 9054                                  | 43   | ,           |

|                       |                      |                  |     |      |                |                |       |              |          | SHI      | EET   | 1  |                                       |     | OF     |             | 29           | •                                     |      | 1           |

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes B, Q, and M) and space application (device classes S and V), and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of radiation hardness assurance (RHA) levels are reflected in the PIN.

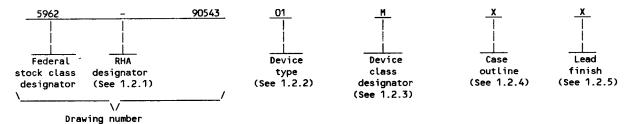

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>Radiation hardness assurance (RHA) designator</u>. Device classes M, B, and S RHA marked devices shall meet the MIL-M-38510 specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>              |

|-------------|----------------|--------------------------------------|

| 01          | 82c37A-5       | 5 MHz programmable DMA controller    |

| 02          | 82c37A         | 8 MHz programmable DMA controller    |

| 03          | 82c37A-12      | 12.5 MHz programmable DMA controller |

| 04          | 82c237         | 8 MHz programmable DMA controller    |

| 05          | 82c237-12      | 12.5 MHz programmable DMA controller |

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

| Device class | Device requirements documentation                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------|

| М            | Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883 |

| B or \$      | Certification and qualification to MIL-M-38510                                                                          |

| Q or V       | Certification and qualification to MIL-I-38535                                                                          |

1.2.4 Case outline. The case outlines shall be designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style                |

|----------------|------------------------|------------------|------------------------------|

| Q              | GDIP1-T40              | 40               | Dual-in-line                 |

| X              | CQCC1-N44              | 44               | Square leadless chip carrier |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-M-38510 for classes M, B, and S or MIL-I-38535 for classes Q and V. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90543 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>2 |

| 1.3            | Absolute maximum rat                                                                                                                 | ings                                        | •                                                                                        |                                      |                                                                                  |                                       |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|

|                | Input, output, or I/O<br>Storage temperature r<br>Power dissipation (P <sub>n</sub><br>Lead temperature (sol<br>Junction temperature | vol<br>ange<br>) <u>1</u> /<br>deri<br>(T,) | d to ground) tage applied range ng, 10 seconds) ion-to-case ( $\Theta_{JC}$ )            |                                      | GND -0.5 V dc to V<br>65°C to +150°C<br>1.0 W maximum<br>275°C<br>+150°C maximum | / <sub>CC</sub> +0.5 V dc             |

| 1.4            | Recommended operation                                                                                                                | g co                                        | nditions.                                                                                |                                      |                                                                                  |                                       |

|                | Case operating temper<br>Supply voltage range                                                                                        | atur<br>(V <sub>CC</sub>                    | e range                                                                                  |                                      | 55°C to +125°C<br>+4.5 V dc to +5.5                                              | V dc                                  |

| 1.5            | Digital testing for                                                                                                                  | <u>dev i</u>                                | ce classes Q and V.                                                                      |                                      |                                                                                  |                                       |

|                | Fault coverage measur<br>logic tests (MIL-STD-                                                                                       | emen<br>883,                                | t of manufacturing<br>test method 5012)                                                  |                                      | XX percent <u>2</u> /                                                            |                                       |

| 2.             | APPLICABLE DOCUMENTS                                                                                                                 |                                             |                                                                                          |                                      |                                                                                  |                                       |

| specia         | fications, standards,<br>ecifications and Stand                                                                                      | bull                                        | s, standards, bulletin, and<br>etin, and handbook of the i<br>specified in the solicitat | ssue listed in th                    | at issue of the Departmen                                                        | t of perense index                    |

| SPI            | ECIFICATIONS                                                                                                                         |                                             |                                                                                          |                                      |                                                                                  |                                       |

| 1              | MILITARY                                                                                                                             |                                             |                                                                                          |                                      |                                                                                  |                                       |

|                | MIL-M-38510<br>MIL-I-38535                                                                                                           | -<br>-                                      | Microcircuits, General Spe<br>Integrated Circuits, Manuf                                 | cification for.<br>acturing, General | Specification for.                                                               |                                       |

| ST             | ANDARDS                                                                                                                              |                                             |                                                                                          |                                      |                                                                                  |                                       |

|                | MILITARY                                                                                                                             |                                             |                                                                                          |                                      |                                                                                  |                                       |

|                | MIL-STD-480<br>MIL-STD-883<br>MIL-STD-1835                                                                                           | -                                           | Configuration Control-Engi<br>Test Methods and Procedure<br>Microcircuit Case Outlines   | s for Microelectr                    | Deviations and Waivers.<br>onics.                                                |                                       |

| BU             | LLETIN                                                                                                                               |                                             |                                                                                          |                                      |                                                                                  |                                       |

|                | MILITARY                                                                                                                             |                                             |                                                                                          |                                      |                                                                                  |                                       |

|                | MIL-BUL-103                                                                                                                          | -                                           | List of Standardized Milit                                                               | ary Drawings (SMD                    | )'s).                                                                            |                                       |

| НА             | NDBOOK                                                                                                                               |                                             |                                                                                          |                                      |                                                                                  |                                       |

|                | MILITARY                                                                                                                             |                                             |                                                                                          |                                      |                                                                                  |                                       |

|                | MIL-HDBK-780                                                                                                                         | -                                           | Standardized Military Draw                                                               | ings.                                |                                                                                  |                                       |

| (Copi<br>acqui | es of the specifications shou                                                                                                        | ons,<br>ld be                               | standards, bulletin, and ha<br>obtained from the contract                                | ndbook required b                    | by manufacturers in connects directed by the contract                            | tion with specific<br>ting activity.) |

| 2.2<br>herei   | Order of precedence<br>n, the text of this d                                                                                         | . I<br>rawi                                 | n the event of a conflict be<br>ng shall take precedence.                                | tween the text of                    | this drawing and the ref                                                         | erences cited                         |

|                |                                                                                                                                      |                                             |                                                                                          |                                      |                                                                                  |                                       |

| 1/ P<br>2/ V   | ower dissipation base<br>alues will be added w                                                                                       | d on<br>hen                                 | package heat transfer limit<br>hey become available.                                     | ations, not devic                    | ce power consumption.                                                            |                                       |

|                | MILITA                                                                                                                               | RY !                                        |                                                                                          | SIZE<br>A                            |                                                                                  | 5962-90543                            |

|                | DEFENSE ELECTRO<br>DAYTON,                                                                                                           |                                             | S SUPPLY CENTER<br>O 45444                                                               |                                      | REVISION LEVEL                                                                   | SHEET 3                               |

|                |                                                                                                                                      |                                             |                                                                                          | l ,                                  | <u> </u>                                                                         |                                       |

## 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes B and S shall be in accordance with MIL-M-38510 and as specified herein. For device classes B and S, a full electrical characterization table for each device type shall be included in this SMD when a qualified source exists. The individual item requirements for device classes Q and V shall be in accordance with MIL-I-38535 and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 for device classes M, B, and S and MIL-I-38535 for device classes Q and V and herein.

- 3.2.1 Case outlines. The case outlines shall be in accordance with 1.2.4 herein.

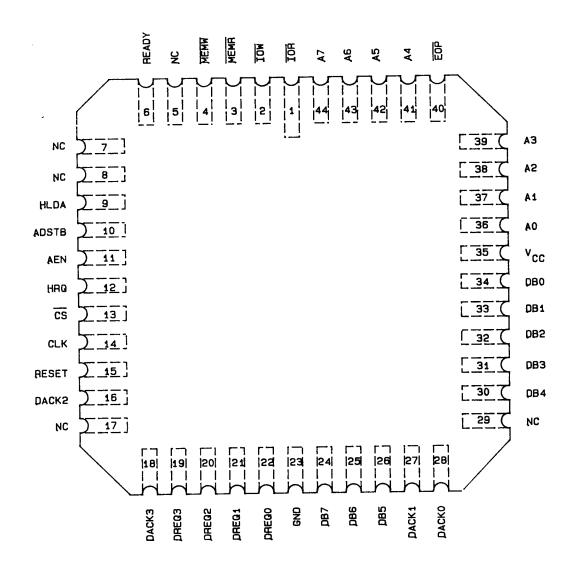

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 1.

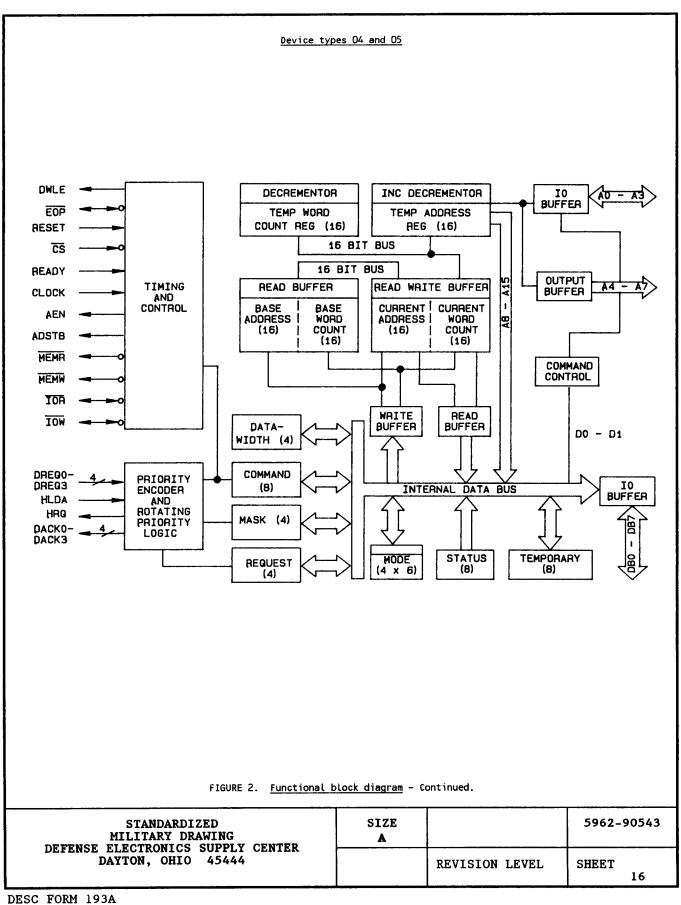

- 3.2.3 Functional block diagram. The functional block diagram shall be as specified on figure 2.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes B and S shall be in accordance with MIL-M-38510. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes B and S shall be a "J" or "JAN" as required in MIL-M-38510. The certification mark for device classes Q and V shall be a "QML" as required in MIL-I-38535.

- 3.6 <u>Certificate of compliance</u>. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.3 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.2 herein). The certificate of compliance submitted to DESC-ECC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M, the requirements of MIL-STD-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-I-38535 and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or device classes B and S in MIL-M-38510 or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M</u>. For device class M, notification to DESC-ECC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-480.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DESC, DESC's agent and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device classes M, B, and S</u>. Device classes M, B, and S devices covered by this drawing shall be in microcircuit group number 105 (see MIL-M-38510, appendix E).

- 3.11 <u>Serialization for device class S</u>. All device class S devices shall be serialized in accordance with MIL-M-38510.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-90543 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>4 |

#### TABLE I. <u>Electrical performance characteristics</u>. Limits Unit Group A Device Conditions Symbol Test $-55^{\circ}$ C $\leq$ T<sub>C</sub> $\leq$ +125 $^{\circ}$ C $\frac{1}{2}$ unless otherwise specified subgroups type Min Max 2.2 ٧ ALL 1,2,3 | v<sub>cc</sub> = 5.5 v VIH Input high voltage 0.8 $v_{cc} = 4.5 \text{ V}$ ٧<sub>IL</sub> Input low voltage $V_{CC} = 4.5 \text{ V, } \frac{2}{4}$ $I_{OH} = -2.5 \text{ mA}$ 3.0 High level output VOH voltage V<sub>CC</sub> -0.4 $v_{CC} = 4.5 \text{ V}, \frac{2}{4}$ $I_{OH} = -100 \mu\text{A}$ $|V_{CC}| = 4.5 \text{ V}, \underline{2}/$ $|I_{OL}| = 3.2 \text{ mA for EOP}$ $|I_{OL}| = 2.5 \text{ mA for all other}$ 0.40 $v_{\rm OL}$ Low level output voltage output pins -1.0 +1.0 $V_{CC} = 5.5 V$ $V_{IN} = V_{CC}$ or GND μA Input leakage I current +10 V<sub>CC</sub> = 5.5 V V<sub>OUT</sub> = V<sub>CC</sub> or GND -10 I/O and output Io leakage current $|V_{CC}| = 5.5 \text{ V}$ $|V_{IN}| = V_{CC} \text{ or GND, outputs open}$ 10 Standby supply Iccsb current $|V_{CC}| = 5.5 \text{ V, f} = \text{maximum}$ $|V_{IN}| = V_{CC} \text{ or GND, outputs open}$ 2 mA/MHz Operating supply ICCOP current 25 f = 1 MHz, T<sub>C</sub> = 25°C, |All measurements are рF Input capacitance $^{\mathsf{c}}^{\mathsf{I}}$ referenced to device ground. See 4.4.1c. 40 Output capacitance $c_{o}$ 25 I/O capacitance C1/0 $V_{CC} = 4.5 \text{ V and 5.5 V, } \frac{3}{4}$ | see 4.4.1d. 7,8 Functional test See footnotes at end of table.

SIZE

A

REVISION LEVEL

5962-90543

5

SHEET

STANDARDIZED MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

| Test                                                  | Symbol      | <br>  Conditions                                                       | <br> Group A   | Device               | Limit                              | ts                         | Unit                  |

|-------------------------------------------------------|-------------|------------------------------------------------------------------------|----------------|----------------------|------------------------------------|----------------------------|-----------------------|

|                                                       |             | -55°C ≤ T <sub>C</sub> ≤ +125°C <u>1</u> /<br>unless otherwise specifi | subgroup<br>ed | s   type             | Min                                | Max                        |                       |

| EN high from CLK<br>low (S1) delay time               | 1           | <br> DMA master mode<br>  See figure 3                                 | 9,10,11        | 01<br>02,04<br>03,05 |                                    | <br>  175<br>  105<br>  50 | ns                    |

| AEN low from CLK<br>high (S1) delay time              | 2           | <br>                                                                   |                | 01<br>02,04<br>03,05 |                                    | 130<br>  80<br>  50        | <br>                  |

| ADR active to float <u>4</u> /<br>delay from CLK high | 3           | <br> <br> <br>                                                         | 1              | 01<br>02,04<br>03,05 |                                    | 90<br>55<br>55             | <u> </u>              |

| READ or WRITE float <u>4</u> /<br>delay from CLK high | <br>  4<br> | <br>                                                                   |                | 01<br>02,04<br>03,05 |                                    | <br>  120<br>  75<br>  50  | <u> </u><br>          |

| DB active to float 4/ delay from CLK high             | 5           |                                                                        |                | 01<br>02,04<br>03,05 |                                    | <br>  170<br>  135<br>  90 |                       |

| ADR from READ high<br>hold time                       | 6           | <br> <br> <br> <br>                                                    | <br>           | 01<br>02,04<br>03,05 | <br> TCY-100<br> TCY-75<br> TCY-65 |                            | <br> <br>             |

| DB from ADSTB low<br>hold time                        | <br>  7<br> |                                                                        |                | ALL                  | <br> TCL-18<br>                    |                            | <br> <br><del> </del> |

| ADR from WRITE high<br>hold time                      | <br>  8<br> | \                                                                      |                | 01<br>02,04<br>03,05 | TCY-65<br> TCY-65<br> TCY-50       |                            | <br>                  |

| DACK valid from CLK<br>low delay time                 | <br>  9<br> |                                                                        |                | 01<br>02,04<br>03,05 | <br> <br>                          | 170<br>  105<br>  69       | <br> <br> <br>        |

| EOP high from CLK<br>high delay time                  | 9           |                                                                        |                | 01<br>02,04<br>03,05 |                                    | 170<br>  105<br>  90       | <br> <br> <br>        |

| EOP low from CLK<br>high delay time                   | 9           | †<br> <br> -<br>                                                       |                | 01<br>02,04<br>03,05 |                                    | 100<br>60<br>35            | <br>                  |

| ADR stable from<br>CLK high                           | 10          | †<br> <br>                                                             |                | 01<br>02,04<br>03,05 |                                    | <br>  110<br>  60<br>  50  | <br> <br> <br>        |

| DB to ADSTB low setup time                            | 11          | †<br>                                                                  |                | ALL                  | <br> TCH-20                        | <br> <br>                  | <u> </u>              |

| Clock high time<br>(transitions 10 ns)                | 12          |                                                                        |                | 01<br>02,04<br>03,05 | 70<br>55<br>30                     |                            |                       |

| See footnotes at end of ta                            | able.       |                                                                        |                |                      |                                    |                            |                       |

| MILITA                                                | DARDIZE     | JING                                                                   | SIZE           |                      |                                    | 5962                       | -9054                 |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444  |             |                                                                        |                | REVISIO              | N LEVEL                            | SHEET                      | 6                     |

6

| Test                                                                                        | <br>  Symbol | Conditions                                                               | Group A        | Device                          | Limi             | ts                  | ⊥ Unit                                             |

|---------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------|----------------|---------------------------------|------------------|---------------------|----------------------------------------------------|

|                                                                                             | <br>         | -55°C ≤ T <sub>C</sub> ≤ +125°C <u>1</u> /<br>unless otherwise specified | subgroups      | type                            | Min              | Max                 |                                                    |

| Clock low time<br>(transitions 10 ns)                                                       | 13           | <br> DMA master mode<br>  See figure 3                                   | 9,10,11        | 01<br>02,04<br>03,05            | 50<br>43<br>30   | <br> <br>           | ns                                                 |

| CLK cycle time                                                                              | 14           |                                                                          |                | 01<br>02,04<br>03,05            | 200<br>125<br>80 |                     |                                                    |

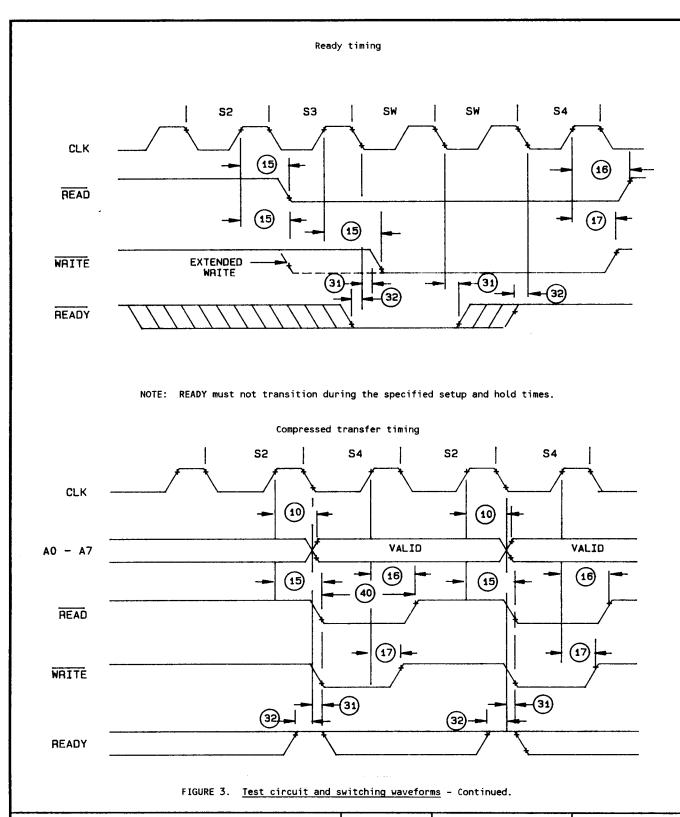

| CLK high to READ<br>or WRITE low delay                                                      | 15           |                                                                          |                | 01<br>02,04<br>03,05            |                  | 190<br>130<br>120   |                                                    |

| READ high from CLK<br>high (S4) delay time                                                  | 16           |                                                                          |                | 01<br>02,04<br>03,05            |                  | 190<br>1115<br>80   | <u> </u>                                           |

| WRITE high from CLK<br>high (S4) delay time                                                 | 17           | <br>                                                                     | <br> -<br> -   | 01<br>02,04<br>03,05            |                  | 130<br>80<br>70     | <br>                                               |

| HRQ valid from CLK<br>high delay time                                                       | 18           |                                                                          | <br> <br> <br> | 01<br>02,04<br>03,05            |                  | 120<br>  75<br>  30 | <br>                                               |

| EOP hold time from<br>CLK low (S2)                                                          | 19           |                                                                          | <br> <br>      | 01<br>02,04<br>03,05            | 90<br>90<br>50   |                     | 1                                                  |

| EOP low to CLK low<br>setup time                                                            | 20           |                                                                          |                | 01<br>02,04<br>03,05            | 40<br>25<br>0    |                     | <br> <br> -                                        |

| EOP pulse width<br>high delay time                                                          | 21           |                                                                          |                | 01 220<br>02,04 135<br>03,05 50 | 135              |                     | 60  <br>50  <br>50  <br>90  <br>50  <br>10  <br>60 |

| ADR valid delay from<br>CLK high                                                            | 22           |                                                                          |                | <br>  01<br>  02,04<br>  03,05  | <br>             | 110<br>60<br>50     |                                                    |

| READ or WRITE active<br>from CLK high                                                       | 23           |                                                                          |                | 01<br>02,04<br>03,05            |                  | 150<br>90<br>50     |                                                    |

| DB valid delay from<br>CLK high                                                             | 24           |                                                                          |                | 01 02,04 03,05                  |                  | 110<br>60<br>45     |                                                    |

| HLDA valid to CLK<br>high setup time                                                        | 25           |                                                                          |                | 01<br>02,04<br>03,05            | 75<br>45<br>10   | 45                  | <br>                                               |

| Input data from MEMR<br>high hold time                                                      | 26           | <br> <br>                                                                |                | All                             | 0                |                     |                                                    |

| See footnotes at end of                                                                     | table.       |                                                                          |                |                                 |                  |                     |                                                    |

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |              | ING                                                                      | IZE<br>A       |                                 |                  | 5962                | -9054                                              |

|                                                                                             |              | UPPLY CENTER<br>45444                                                    | 1              | REVISION                        | LEVEL            | SHEET               | 7                                                  |

| Test                                  | Symbol       | Conditions                                                               | Group A   | Device<br>type                 | Limit                                 | Unit             |                |

|---------------------------------------|--------------|--------------------------------------------------------------------------|-----------|--------------------------------|---------------------------------------|------------------|----------------|

|                                       |              | -55°C ≤ T <sub>C</sub> ≤ +125°C <u>1</u> /<br>unless otherwise specified | subgroups |                                | Min                                   | Max              | <u> </u>       |

| Input data to MEMR high setup time    | <br>  27<br> | <br> DMA master mode<br>  See figure 3<br>                               | 9,10,11   | 01<br>02,04<br>03,05           | 155<br>90<br>45                       |                  | ns             |

| Output data from MEMW high hold time  | 28           | <br> <br> <br>                                                           |           | <br>  01<br>  02,04<br>  03,05 | 15<br>  15<br> TCY-50                 |                  |                |

| Output data valid to MEMW high        | 29           | <br> <br> <br>                                                           |           | 01<br>02,04<br>03,05           | <br> TCY-35<br> TCY-35<br> TCY-10     |                  |                |

| DREQ to CLK low (S1,S4) setup time    | 30           |                                                                          |           | All                            | 0                                     |                  | <u> </u><br>   |

| CLK to READY low<br>hold time         | 31           | <br>                                                                     |           | 01<br>02,04<br>03,05           | 20<br>20<br>10                        |                  | <br>           |

| READY to CLK low<br>setup time        | <br>  32<br> | <br>                                                                     |           | 01<br>02,04<br>03,05           | 60<br>35<br>15                        |                  | <br> <br> <br> |

| ADSTB high from CLK<br>low delay time | 33           | <br> <br> <br>                                                           |           | 01<br>02,04<br>03,05           |                                       | 80<br>70<br>70   | <br> <br> <br> |

| ADSTB low from CLK<br>low delay time  | 34           | <br>                                                                     |           | 01<br>02,04<br>03,05           |                                       | 120<br>120<br>60 | <br> <br> <br> |

| READ high delay from<br>WRITE high    | <br>  35<br> | <br> <br> <br>                                                           |           | 01<br>02,04<br>03,05           | 0<br>0<br>0<br>5                      |                  |                |

| READ pulse width,<br>normal timing    | 36           | <br> <br> <br>                                                           |           | <br>  01<br>  02,04<br>  03,05 | <br> 2TCY-60<br> 2TCY-60<br> 2TCY-55  |                  | <br> <br> <br> |

| ADSTB pulse width                     | 37           | <br> <br> <br>                                                           |           | 01<br>02,04<br>03,05           | <br> TCY-80<br> TCY-50<br> TCY-35     |                  | <br> <br> <br> |

| Extended WRITE pulse width            | <br>  38<br> | <br>                                                                     |           | 01<br>02,04<br>03,05           | <br> 2TCY-100<br> 2TCY-85<br> 2TCY-80 |                  | <br> <br> <br> |

| WRITE pulse width                     | 39           | 1                                                                        |           | 01<br>02,04<br>03,05           | <br> TCY-100<br> TCY-85<br> TCY-80    |                  |                |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90543 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 8    |

| Test                                        | Symbol       | Conditions                                                               | Group A<br>subgroups | Device<br>type       | Limit                               | ⊥ Unit         |                |

|---------------------------------------------|--------------|--------------------------------------------------------------------------|----------------------|----------------------|-------------------------------------|----------------|----------------|

| 1030                                        |              | -55°C ≤ T <sub>C</sub> ≤ +125°C <u>1</u> /<br>unless otherwise specified |                      |                      | Min                                 | Max            |                |

| READ pulse width,<br>compressed             | 40           | DMA master mode See figure 3                                             | 9,10,11              | 01<br>02,04<br>03,05 | TCY-60  <br>  TCY-60  <br>  TCY-55  |                | ns             |

| DB float delay from <u>4</u> /<br>READ high | 47           |                                                                          | <br>                 | 01<br>02,04<br>03,05 | 5<br>5<br>5                         | 85<br>85<br>55 |                |

| ADR valid to READ low                       | 56           |                                                                          |                      | ALL                  | 17                                  |                | <u> </u>       |

| ADR valid to WRITE low                      | 57           | <br>                                                                     |                      | All                  | 7                                   |                |                |

| READ high to AEN low                        | 58           | <del> </del><br> -<br> -                                                 | <br>                 | ALL                  | 15                                  |                | <u> </u>       |

| READ high to ADSTB high                     | 59           | †<br> <br> -                                                             |                      | All                  | 13                                  |                | <br> <br> -    |

| WRITE high to ADSTB high                    | 60           | <br>                                                                     |                      | ALL                  | 15                                  |                |                |

| DACK valid to READ low                      | 61           | <del> </del><br> -<br> -                                                 |                      | ALL                  | 25                                  |                | <br> <br>      |

| DACK valid to WRITE low                     | 62           |                                                                          |                      | ALL                  | 25                                  |                | <br> <br>      |

| READ high to DACK inactive                  | 63           | <br> <br> -<br> -                                                        |                      | ALL                  | 12                                  |                |                |

| ADR float to READ low <u>4</u> /            | 64           |                                                                          |                      | ALL                  | - 2.5                               |                |                |

| Output enable valid<br>before WRITE high    | 65           | <br>                                                                     |                      | 01<br>02,03<br>04,05 | 5/<br>5/<br>Tcy+20                  |                | <br> <br> <br> |

| Output enable hold<br>time from WRITE high  | <br>  66<br> |                                                                          |                      | 01<br>02,03<br>04,05 | <u>5</u> /<br><u>5</u> /<br> TCY-50 |                | <u> </u><br>   |

| ADR valid or CS low<br>to READ low          | 41           | <br> Peripheral slave mode<br>  See figure 3                             | 9,10,11              | 01<br>02,04<br>03,05 | 10<br>10<br>0                       |                |                |

| ADR valid to WRITE<br>low setup time        | 42           |                                                                          |                      | ALL                  | 0                                   |                |                |

See footnotes at end of table.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-90543 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 9    |

| Test Symbol                            | Symbol | Conditions                                                               | Group A   | Device               | Limit            | s                | i Unit       |

|----------------------------------------|--------|--------------------------------------------------------------------------|-----------|----------------------|------------------|------------------|--------------|

|                                        | ļ      | -55°C ≤ T <sub>C</sub> ≤ +125°C <u>1</u> /<br>unless otherwise specified | subgroups | type                 | Min              | Max              |              |

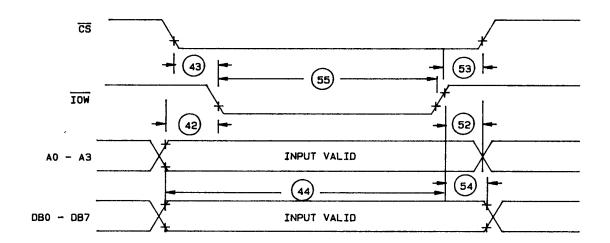

| CS low to WRITE low setup time         | 43     | <br> Peripheral slave mode<br>  See figure 3                             | 9,10,11   | ALL                  | 0                |                  | ns           |

| Data valid to WRITE<br>high setup time | 44     |                                                                          | <br> <br> | 01<br>02,04<br>03,05 | 150<br>100<br>60 |                  | <br> <br>    |

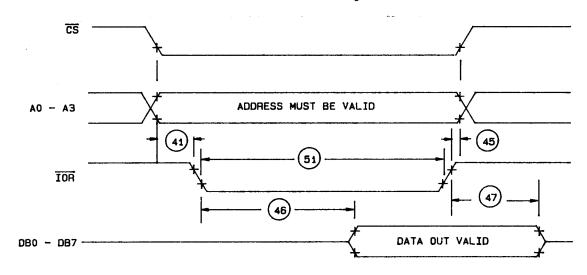

| ADR or CS hold from<br>READ high       | 45     | <br> Peripheral slave mode<br>  See figure 3                             | 9,10,11   | ALL                  | 0                |                  | 1            |

| Data access from READ                  | 46     |                                                                          |           | 01<br>02,04<br>03,05 |                  | 140<br>120<br>80 | <br> <br>    |

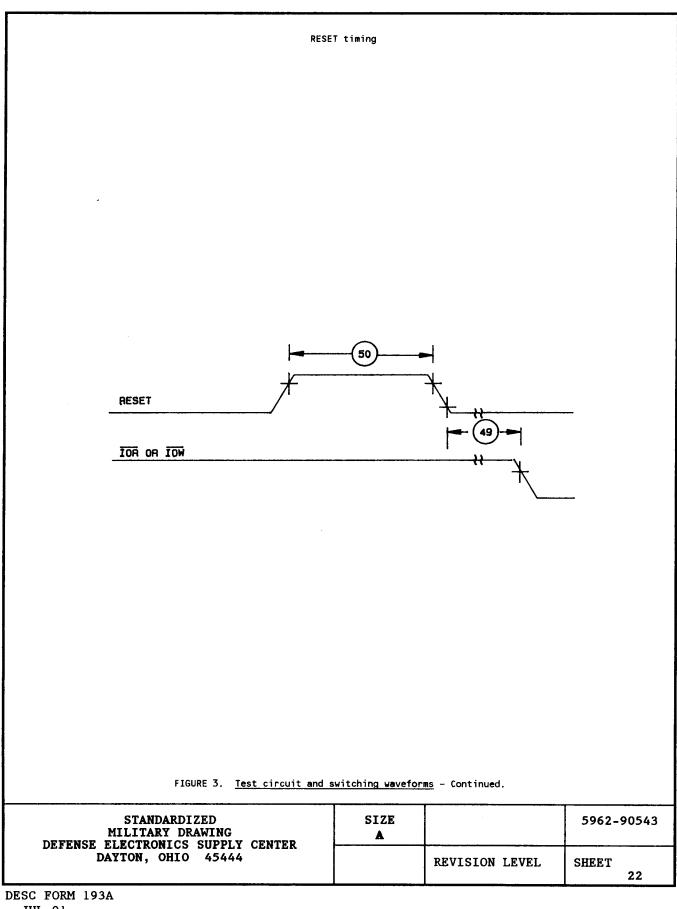

| RESET to first IOR or                  | 49     | -<br> <br> -                                                             |           | All                  | <br> 2TCY        |                  | <u> </u><br> |

| RESET pulse width                      | 50     |                                                                          |           | All                  | 300              |                  |              |

| READ pulse width<br>high setup time    | 51     |                                                                          |           | 01<br>02,04<br>03,05 | 200<br>155<br>85 |                  |              |

| ADR from WRITE high<br>hold time       | 52     | <br>                                                                     |           | ALL                  | 0                |                  | _            |

| CS high from WRITE high hold time      | 53     | <u> </u><br>                                                             |           | ALL                  | 0                |                  | <u> </u>     |

| Data from WRITE high<br>hold time      | 54     | 1                                                                        |           | All                  | 10               |                  | <u> </u>     |

| WRITE pulse width                      | 55     |                                                                          |           | 01<br>02,04<br>03,05 | 150<br>100<br>45 |                  |              |

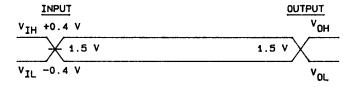

<sup>1/</sup> The following pins are active low: IOR, IOW, MEMR(READ), MEMW(WRITE), CS and EOP. Unless otherwise specified, all test conditions shall be worst case condition. Unless otherwise specified, ac parameters are specified, all test conditions shall be worst case condition. Unless otherwise specified, ac parameters are tested as follows: V<sub>CC</sub> of 4.5 V and 5.5 V, inputs are driven at 1 ns/V, and must switch between V<sub>IH</sub> + 0.4 V and V<sub>IL</sub> - 0.4 V. Input and output timing reference levels are 1.5 V.

2/ Interchanging of force and sense conditions is permitted.

3/ Tested as follows: V<sub>CC</sub> of 4.5 V and 5.5 V, frequency = 2.5 MHz, inputs are driven at 1 ns/V, and must switch between V<sub>IH</sub> + 0.4 V and V<sub>IL</sub> - 0.4 V.

4/ Guaranteed if not tested to the limits specified in table I.

5/ These test conditions only specified for device types 04 and 05. These limits are not specified for device.

These test conditions only specified for device types 04 and 05. These limits are not specified for device types 01, 02 or 03.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-90543  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>10 |

#### Device types 01, 02 and 03 Case Q Top view Α7 40 TOR A6 39 2 IOW A5 38 MEMA 3 37 A4 MEMW 36 EOP NC 5 EΑ 35 6 READY 34 **A2** 7 HLDA 33 A1 ADSTB 8 ΑO 35 9 AEN v<sub>cc</sub> 31 HAG 10 DB0 30 CS 11 DB1 29 12 CLK DB2 28 13 RESET DACK5 27 DB3 14 **DB4** 15 26 **DACK3** 25 **DACKO** DREQ3 16 DACK1 24 DREQ2 17 23 **DB5** 18 DREG1 55 **DB6 DREGO** 19 D87 (GND) V<sub>SS</sub> 21 20 FIGURE 1. Terminal connections. 5962-90543 SIZE **STANDARDIZED** MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER A DAYTON, OHIO 45444 REVISION LEVEL SHEET

11

#### Device types 04 and 05 Case Q Top view TOR 40 1 Α7 2 A6 39 IOW MEMR 3 38 A5 MEMW 37 A4 DWLE 5 36 EOP READY 6 35 EΑ HLDA 7 **A2** 34 **ADSTB** 8 33 A1 ΑO AEN 32 31 HRQ Vcc 10 CS 11 30 DB0 CLK 12 59 DB1 RESET 13 28 DB2 DACK2 27 14 **DB3 DACK3** DB4 15 26 **DREG3** 16 25 **DACKO** DREQ2 17 24 DACK1 DREG1 23 18 DB5 **DREGO** 19 55 D86 (GND) V<sub>SS</sub> DB7 20 21 FIGURE 1. <u>Terminal connections</u> - Continued. SIZE 5962-90543 STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER A DAYTON, OHIO 45444 REVISION LEVEL SHEET 12

# Device types 01, 02 and 03

Çase X

Top view

FIGURE 1. Terminal connections - Continued.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-90543  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>13 |

### Device types 04 and 05 Case X Top view DWLE IOR 입 7\_] 39 ΑЗ NC 8 } 38 82 NC 37 A1 HLDA \_9\_ j ADSTB 10 ] 36 ΑO v<sub>cc</sub> 35 11] AEN 34 DB0 HAG 12 33 cs QB1 <u>13</u> j **DB2** 35 14 CLK <u>15</u>] 31 **DB3** RESET 30 16 DB4 DACK2 NC <u> 17</u> ] 29 NC |23| 21 153 24 |26 19 120 25 DACKO DACK3 DREG3 DRE02 DREGO <u>S</u> **DB6** DACK1 DREG1 **DB**7

FIGURE 1. Terminal connections - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90543  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>14 |

#### Device types 01, 02 and 03 DECREMENTOR INC DECREMENTOR 10 EA - 0A EOP BUFFER TEMP WORD TEMP ADDRESS COUNT REG (16) RESET REG (16) 16 BIT BUS CS READY 16 BIT BUS OUTPUT TIMING READ BUFFER READ WRITE BUFFER CLOCK BUFFER A4 AND CONTROL BASE BASE CURRENT | CURRENT AEN ADDRESS | ADDRESS | WORD WORD (16)COUNT (16) COUNT ADSTB (16)(16) MEMA COMMAND MEMW CONTROL TOR WRITE READ IOW BUFFER BUFFER D0 - D1 DREGO-COMMAND PRIORITY DRE03 (8) INTERNAL DATA BUS ENCODER HLDA BUFFER AND ROTATING HRG -PRIORITY MASK (4) DACKO- 4 DACK3 LOGIC 1 <u>8</u> MODE **STATUS** TEMPORARY REQUEST (8) (4 x 6) (8) (4) FIGURE 2. Functional block diagram. STANDARDIZED SIZE 5962-90543 MILITARY DRAWING A DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 REVISION LEVEL SHEET 15 DESC FORM 193A

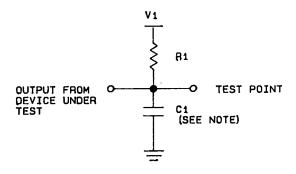

### AC test circuit

NOTE: Includes STRAY and FIXTURE capacitance.

Test condition definition table

| PINS                   | V1              | R1     | c1     |

|------------------------|-----------------|--------|--------|

| All outputs except EOP | 1.7 V           | 520Ω   | 100 pF |

| EOP                    | v <sub>cc</sub> | 1.6 kΩ | 50 pF  |

AC testing input, output waveforms

## NOTES:

- This specification applies only to valid-to-3-state outputs of recommended operation conditions: TAFAB(3), TAFC(4), TAFDB(5), TRDF(47), and TAZRL(64). Number in parentheses refers to ac parameter in figure 3.

- 2. AC testing: All ac parameters tested in accordance with test circuits, input RISE and FALL times are driven at 1 ns/V.

FIGURE 3. Test circuit and switching waveforms.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90543  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>17 |

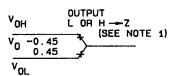

NOTE: For devices 04 and 05 only: In 8-bit mode, this signal is always high impedance 3-stated. Waveform shown is for an 8-bit transfer with the devices programmed in 16-bit mode. For a 16-bit transfer, DWLE will go low at least (CLK high time - 20 ns) before the falling edge of ADSTB in S2, and remain low for the entire transfer.

FIGURE 3. Test circuit and switching waveforms - Continued.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-90543  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>18 |

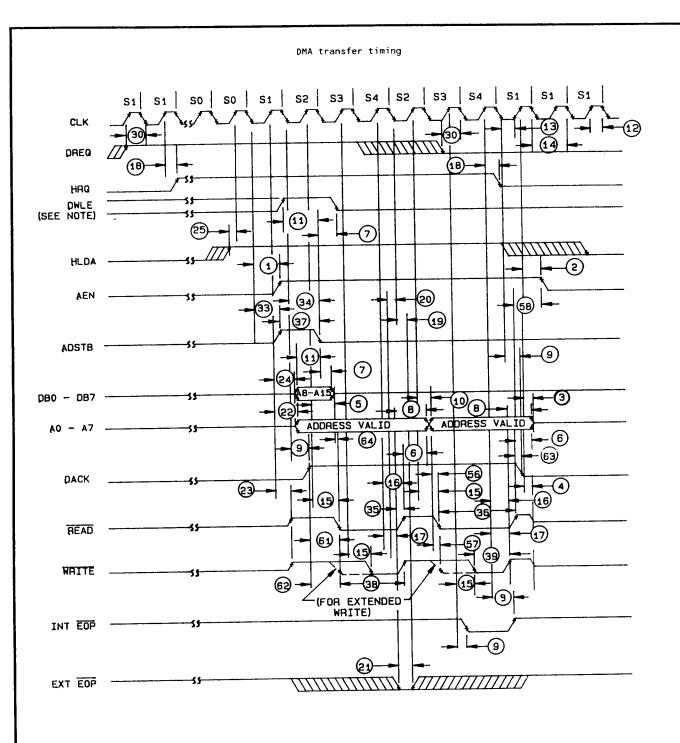

NOTE: For 16-bit mode, devices 04 and 05 only. In 8-bit mode, this signal is always high impedance 3-stated. Waveform shown is for a 16-bit memory-to-memory transfer. For an 8-bit transfer in 16-bit mode, DWLE will go high at least (CLK high time - 20 ns) before the falling edge of ADSTB in S2, then low (CLK low time - 18 ns) after the falling edge of ADSTB, and will remain low until the next ADSTB where the cycle is repeated.

FIGURE 3. Test circuit and switching waveforms - Continued.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90543  |

|-----------------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                                    |           | REVISION LEVEL | SHEET<br>19 |

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

REVISION LEVEL SHEET

20

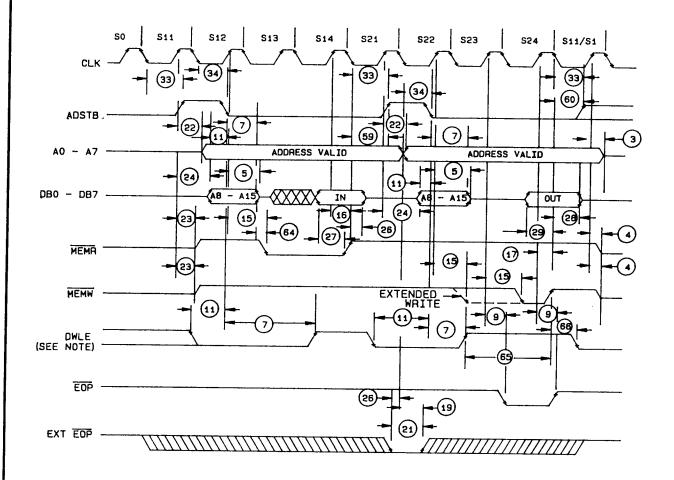

## Slave mode write timing

NOTE: Successive WRITE accesses to the devices must allow at least a CLK cycle time as reco<u>very</u> time between <u>acce</u>sses. A CLK cycle time recovery time must be allowed before executing a WRITE access after a READ access.

## Slave mode read timing

NOTE: Successive READ accesses to the devices must allow at least a CLK cycle time <u>as recovery time between</u> accesses. A CLK cycle time recovery time must be allowed before executing a WRITE access after a READ access.

FIGURE 3. Test circuit and switching waveforms - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90543 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 21   |

#### 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. For device class M, sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein). For device classes B and S, sampling and inspection procedures shall be in accordance with MIL-M-38510 and method 5005 of MIL-STD-883, except as modified herein. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-I-38535.

- 4.2 <u>Screening</u>. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. For device classes B and S, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to qualification and quality conformance inspection. For device classes Q and V, screening shall be in accordance with MIL-I-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection. The following additional criteria shall apply.

# 4.2.1 Additional criteria for device classes M, B, and S.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. For device class M, the test circuit shall be submitted to DESC-ECC for review with the certificate of compliance. For device classes B and S, the test circuit shall be submitted to the qualifying activity. For device classes Q and V, the test circuit shall be submitted to DESC-ECC with the certificate of compliance and under the control of the device manufacturer's technical review board (TRB) in accordance with MIL-I-38535.

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

# 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The burn-in test circuit shall be submitted to DESC-ECC with the certificate of compliance and shall be under the control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-I-38535.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in appendix B of MIL-I-38535 and as detailed in table IIB herein.

# 4.3 Qualification inspection.

- 4.3.1 <u>Qualification inspection for device classes B and S.</u> Qualification inspection for device classes B and S shall be in accordance with MIL-M-38510. Inspections to be performed shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5).

- 4.3.2 <u>Qualification inspection for device classes Q and V.</u> Qualification inspection for device classes Q and V shall be in accordance with MIL-I-38535. Inspections to be performed shall be those specified in MIL-I-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5).

- 4.4 <u>Conformance inspection</u>. Quality conformance inspection for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein) and as specified herein. Quality conformance inspection for device classes B and S shall be in accordance with MIL-M-38510 and as specified herein. Inspections to be performed for device classes M, B, and S shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5). Technology conformance inspection for classes Q and V shall be in accordance with MIL-I-38535 including groups A, B, C, D, and E inspections and as specified herein.

# 4.4.1 Group A inspection.

- a. Tests shall be as specified in table IIA herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90543 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 23   |

- c. Subgroup 4 ( $C_I$ ,  $C_0$  and  $C_{I/0}$  measurement) shall be measured only for the initial test and after process or design changes which may affect capacitance. Sample size is 15 devices with no failures, and all input and output terminals tested.

- d. Subgroups 7 and 8 functional test shall include verification of programming set.

- 4.4.2 <u>Group B inspection.</u> The group B inspection end-point electrical parameters shall be as specified in table IIA herein.

TABLE IIA. Electrical test requirements.

| Test requirements                                 |                                              | Subgroups<br>hod 5005, ta                | Subgroups<br>(per MIL-I-38535,<br>table III) |                                              |                                                  |

|---------------------------------------------------|----------------------------------------------|------------------------------------------|----------------------------------------------|----------------------------------------------|--------------------------------------------------|

|                                                   | Device<br>class<br>M                         | Device<br>class<br>B                     | Device<br>class<br>S                         | Device<br>class<br>Q                         | Device<br>class<br>V                             |

| Interim electrical parameters (see 4.2)           |                                              | <br>                                     | 1,7                                          | <br>                                         | 1,7                                              |

| <br>  Final electrical<br>  parameters (see 4.2)  | 1,2,3, <u>1</u> /<br>  5,6,7,8,<br>  9,10,11 | 1,2,3, <u>1</u> /<br>5,6,7,8,<br>9,10,11 | 1,2,3, <u>2</u> /<br>  5,6,7,8,<br>  9,10,11 | 1,2,3, <u>1</u> /<br>  5,6,7,8,<br>  9,10,11 | 1,2,3, <u>2</u> /  <br>  5,6,7,8,  <br>  9,10,11 |

| Group A test requirements (see 4.4)               | 1,2,3,4,<br>7,8,9,<br>10,11                  | 1,2,3,4,<br>7,8,9,<br>10,11              | 1,2,3,4,<br>7,8,9,<br>10,11                  | 1,2,3,4,<br>  7,8,9,<br>  10,11              | 1,2,3,4,<br>7,8,9,<br>10,11                      |

| Group B end-point electrical parameters (see 4.4) |                                              | <br> <br>                                |                                              |                                              |                                                  |

| Group C end-point electrical parameters (see 4.4) | 2,5,8,10                                     | 2,5,8,10                                 | <br> <br>                                    | 2,5,8,10                                     | 2,5,7,8,10                                       |

| Group D end-point electrical parameters (see 4.4) | 2,5,8,10                                     | 2,5,8,10                                 | 2,5,7,8,10                                   | 2,5,8,10                                     | 2,5,7,8,10                                       |

| Group E end-point electrical parameters (see 4.4) | 2,5,8,10                                     | 2,5,8,10                                 | 2,5,8,10                                     | 2,5,8,10                                     | 2,5,8,10                                         |

- 1/ PDA applies to subgroup 1.

- 2/ PDA applies to subgroups 1 and 7.

- 4.4.3 <u>Group C inspection</u>. The group C inspection end-point electrical parameters shall be as specified in table IIA here in.

- 4.4.3.1 Additional criteria for device classes M, B, and S. Steady-state life test conditions, method 1005 of MIL-STD-883:

- a. Steady-state life test conditions, method 1005 of MIL-STD-883:

- (1) Test condition A, B, C or D. For device class M, the test circuit shall be submitted to DESC-ECC for review with the certificate of compliance. For device classes B and S, the test circuit shall be submitted to the qualifying activity. For device classes Q and V, the test circuit shall be submitted to DESC-ECC with the certificate of compliance and under the control of the device manufacturer's technical review board (TRB) in accordance with MIL-I-38535.

- b.  $T_A = +125$ °C, minimum.

- c. Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-90543 |

|---------------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                             |           | REVISION LEVEL | SHEET 24   |

- 4.4.3.2 <u>Additional criteria for device classes Q and V</u>. The steady-state life test duration, test condition and test temperature or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The steady-state life test circuit shall be submitted to DESC-ECS with the certificate of compliance and shall be under the control of the device manufacturer's TRB in accordance with MIL-I-38535.

- 4.4.4 <u>Group D inspection</u>. For group D inspection end-point electrical parameters shall be as specified in table IIA herein.

- 4.4.5 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein). RHA levels for device classes B and S shall be M, D, R, and H and for device class M shall be M and D. RHA quality conformance inspection sample tests shall be performed at the level specified in the acquisition document. RHA tests for device classes Q and V shall be performed in accordance with MIL-I-38535 and 1.2.1 herein.

TABLE IIB. Additional screening for device class V.

|                                    | 1                                            |                   |

|------------------------------------|----------------------------------------------|-------------------|

| Test                               | MIL-STD-883, test method                     | Lot requirement   |

| Particle impact<br>noise detection | 2020                                         | 100 percent       |

| Internal visual                    | 2010, condition A or approved alternate      | 100 percent       |

| Nondestructive<br>bond pull        | 2023 or approved alternate                   | 100 percent<br>   |

| Reverse bias burn-in               | 1015                                         | <br>  100 percent |

| Burn-in<br>parameters              | <br>  1015, total of 240 hrs.<br>  at +125°C | <br>  100 percent |

| Radiographic                       | 2012                                         | 100 percent       |

- a. RHA tests for device classes B and S for levels M, D, R, and H or for device class M for levels M and D shall be performed through each level to determine at what levels the devices meet the RHA requirements. These RHA tests shall be performed for initial qualification and after design or process changes which may affect the RHA performance of the device.

- b. End-point electrical parameters shall be as specified in table IIA herein.

- c. Prior to total dose irradiation, each selected sample shall be assembled in its qualified package. It shall pass the specified group A electrical parameters in table I for subgroups specified in table IIA herein.

- d. For device classes M, B, and S, the devices shall be subjected to radiation hardness assured tests as specified in MIL-M-38510 for RHA level being tested, and meet the postirradiation end-point electrical parameter limits as defined in table I at  $T_A = 25^{\circ}\text{C} \pm 5$  percent, after exposure.

- e. Prior to and during total dose irradiation testing, the devices shall be biased to establish a worst case condition as specified in the radiation exposure circuit.

- (1) Inputs tested high,  $V_{CC}$  = volts dc,  $R_{CC}$  =  $\Omega$  +5 percent,  $V_{IN}$  = volts dc,  $R_{IN}$  =  $\Omega$  +20 percent, and all outputs are open.

- (2) Inputs tested low  $V_{CC}$  = volts dc,  $R_{CC}$  =  $\Omega$  +5 percent,  $V_{IN}$  = 0.0 V dc, and all outputs are open.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90543  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>25 |

- f. For device classes M, B, and S, subgroups 1 and 2 in table V, method 5005 of MIL-STD-883 shall be tested as appropriate for device construction.

- g. When specified in the purchase order or contract, a copy of the RHA delta limits shall be supplied.

#### 5. PACKAGING

5.1 <u>Packaging requirements</u>. The requirements for packaging shall be in accordance with MIL-M-38510 for device classes M, B, and S, and MIL-I-38535 for device classes Q and V.

#### 6 NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.1.1 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.1.2 Substitutability. Device classes B and Q devices will replace device class M devices.

- 6.2 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-481 using DD Form 1693, Engineering Change Proposal (Short Form).

- 6.3 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and which SMD's are applicable to that system. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DESC-ECS, telephone (513) 296-6022.

- 6.4 <u>Comments</u>. Comments on this drawing should be directed to DESC-ECC, Dayton, OH 45444, or telephone (513) 296-8525.

- 6.5 Symbols, definitions and functional descriptions.

| <br>  Symbol<br> | <br>  Type<br> | <br>  Functional description                                                                                                                                                                                                                                                                                                                                             |

|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>  |                | <br> +5 V power supply pin. A 0.1 $\mu$ F capacitor between pins 31 and 20 is recommended<br> for decoupling.                                                                                                                                                                                                                                                            |

| GND              |                | Ground.                                                                                                                                                                                                                                                                                                                                                                  |

| CLK              | I              | Clock input: The clock input is used to generate the timing signals which control the devices operations. This input may be driven from dc to 12.5 MHz for devices 03 and 05. The clock may be stopped in either state for standby operation.                                                                                                                            |

| cs               | I              | Chip select: Chip select is an active low input used to enable the controller onto the data bus for CPU communications.                                                                                                                                                                                                                                                  |

| RESET            | I              | Reset: This is an active high input which clears the command, status, request, and temporary registers, the first/last flip-flop, and the mode register counter. The mask register is set to ignore requests. The data-width register is set to perform 8-bit transfers on all channels (devices 04 and 05 only). Following a reset, the controller is in an idle cycle. |