|     | REVISIONS                                    |                 |               |

|-----|----------------------------------------------|-----------------|---------------|

| LTR | DESCRIPTION                                  | DATE (YR-MO-DA) | APPROVED      |

| Α   | Changes in accordance with NOR 5962-R144-93. | 93-06-15        | M.L. Poelking |

| В   | Add device 03. Editorial changes throughout. | 94-04-18        | M.L. Poelking |

| С   | Add device 04. Editorial changes throughout. | 95-03-25        | M.L. Poelking |

| REV                   |         |        |            |       |         |        |         |          |      |      |       |                      |       |          |      |      |        |             |    |             |

|-----------------------|---------|--------|------------|-------|---------|--------|---------|----------|------|------|-------|----------------------|-------|----------|------|------|--------|-------------|----|-------------|

| SHEET                 |         |        |            |       |         |        |         |          |      |      |       |                      |       |          |      |      |        |             |    | $\vdash$    |

| REV                   | С       | С      | С          | С     | С       | С      | С       | С        | С    | С    | С     | С                    | С     | С        |      |      |        |             |    |             |

| SHEET                 | 35      | 36     | 37         | 38    | 39      | 40     | 41      | 42       | 43   | 44   | 45    | 46                   | 47    | 48       |      |      |        |             |    |             |

| REV                   | С       | С      | С          | С     | С       | С      | С       | С        | С    | С    | С     | С                    | С     | С        | С    | С    | С      | С           | С  | c           |

| SHEET                 | 15      | 16     | 17         | 18    | 19      | 20     | 21      | 22       | 23   | 24   | 25    | 26                   | 27    | 28       | 29   | 30   | 31     | 32          | 33 | 34          |

| REV STAT              |         |        |            | RE    | ٧       |        | С       | С        | С    | С    | С     | C                    | С     | С        | С    | С    | С      | С           | С  | С           |

| OF SHEET              | <u></u> |        |            | SH    | EET     |        | 1       | 2        | 3    | 4    | 5     | 6                    | 7     | 8        | 9    | 10   | 11     | 12          | 13 | 14          |

| PMIC N/A              |         | ·····  |            | PREP  | ARED B  | Y Tho  | omas M. | . Hess   |      | DE   | FENS  |                      |       |          |      |      | CENT   | ΓER         |    | <del></del> |

|                       | ITAR    | RY     |            | CHEC  | KED BY  | Tim    | H.Noh   |          |      |      |       |                      | AYT0  | N, U     | H10  | 4544 | 44<br> | <del></del> |    |             |

| THIS DRAWIN           | G IS A  | VAILAB | ILE<br>ure | APPR  | OVED B  | Y Mon  | ica L.  | Poell    | king | GRA  | PHI   | IRCU<br>CS S<br>THIC | SYST  | EM I     | PROC |      | CMOS   | *           |    |             |

| AND AGEN<br>DEPARTMEN | CIES O  | F THE  |            | DRAW) | ING API | PROVAL | DATE    |          |      | 1101 | .0.01 | 1111                 | , 51  | <u> </u> | ) [N |      |        |             |    |             |

| AMSC N/A              |         |        |            |       | SION L  | EVEL   |         | <u>-</u> |      | SIZ  | Ē     |                      | E COI | 1        |      | 59   | 62-    | 9162        | 13 |             |

|                       |         |        |            |       | С       |        |         |          |      | SHE  | ΕT    |                      | 1     |          | 0F   | 48   | 3      |             |    |             |

|                       |         |        |            |       |         |        |         |          |      |      |       |                      |       |          |      |      |        |             |    |             |

DESC FORM 193

JUL 91

<u>DISTRIBUTION STATEMENT A</u>. Approved for public release; distribution is unlimited.

■ 9004708 0004995 OT2 ■

5962-E136-95

## 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes Q and M) and space application (device class V), and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

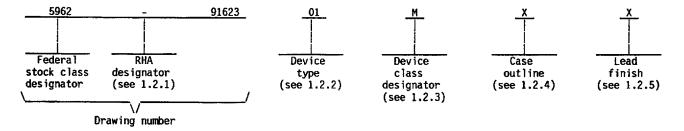

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>RHA designator</u>. Device class M RHA marked devices shall meet the MIL-I-38535 appendix A specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 Device type(s). The device type(s) shall identify the circuit function as follows:

| <u>Device type</u> | Generic number | <u>Circuit function</u>   |

|--------------------|----------------|---------------------------|

| 01                 | 34020-28       | Graphics system processor |

| 02                 | 34020-30       | Graphics system processor |

| 03                 | 34020A-32      | Graphics system processor |

| 04                 | 34020A-40      | Graphics system processor |

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

М

Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883

Q or V

Certification and qualification to MIL-I-38535

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | <u>Descriptive designator</u> | <u>Terminals</u> | Package style       |

|----------------|-------------------------------|------------------|---------------------|

| X              | CMGA7-P145                    | 145              | Pin grid array      |

| Y              | CQCC1-F132                    | 132              | Leaded chip carrier |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-STD-883 (see 3.1 herein) for class M or MIL-I-38535 for classes Q and V. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET 2    |

1.3 Absolute maximum ratings. 1/ 7.0 V dc -0.3 V dc to 7.0 V dc -2.0 V dc to 7.0 V dc -55°C to +125°C -65°C to +150°C +260°C See MIL-M-38510, appendix C +175°C 1.375 W 1.4 <u>Recommended operating conditions.</u> Supply voltage range ( $v_{CC}$ ): Device 01, 03 - - - - - Device 02, 04 - - - - - -4.5 V dc to 5.5 V dc 4.75 V dc to 5.25 V dc 0 V dc 400 µA 2 mA -55°C to +125°C 1.5 Digital logic testing for device classes Q and V. Fault coverage measurement of manufacturing logic tests (MIL-STD-883, test method 5012) . . . . . . XX percent 2/

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET 3    |

$<sup>\</sup>underline{1}$ / Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

$<sup>\</sup>frac{2}{3}$ / All voltage values are with respect to  $V_{SS}$ .  $\frac{3}{2}$ / Take care to provide a minimum inductance path between the  $V_{SS}$  pins and system ground in order to miminize noise on  $V_{SS}$ .

4/ Values will be added when they become available.

## 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, bulletin, and handbook</u>. Unless otherwise specified, the following specification, standards, bulletin, and handbook of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

MILITARY

MIL-I-38535 - Integrated Circuits, Manufacturing, General Specification for.

**STANDARDS**

MILITARY

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-973 - Configuration Management.

MIL-STD-1835 - Microcircuit Case Outlines.

BULLETIN

MILITARY

MIL-BUL-103 - List of Standardized Military Drawings (SMD's).

**HANDBOOK**

**MILITARY**

MIL-HDBK-780 - Standardized Military Drawings.

(Copies of the specification, standards, bulletin, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

## 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes Q and V shall be in accordance with MIL-1-38535, the device manufacturer's Quality Management (QM) plan, and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-STD-883 (see 3.1 herein) for device class M and MIL-I-38535 for device classes Q and V and herein.

- 3.2.1 <u>Case outline(s)</u>. The case outline(s) shall be in accordance with 1.2.4 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

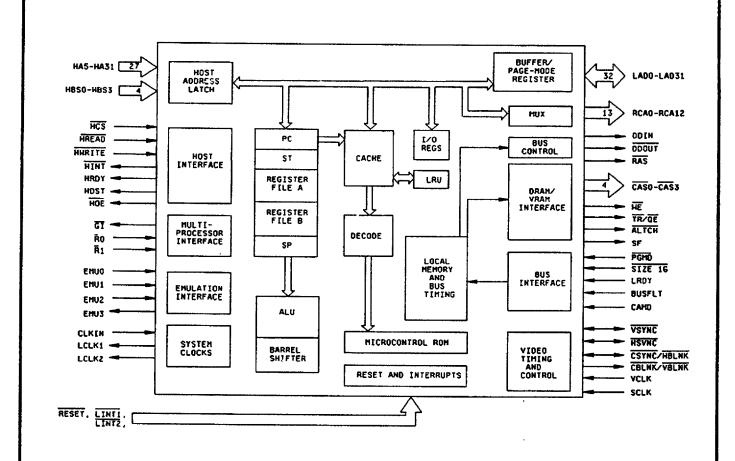

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 2.

- 3.2.5 Radiation exposure circuit. The radiation exposure circuit shall be specified when available.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET 4    |

- 3.5 Marking. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-I-38535.

- 3.6 <u>Certificate of compliance</u>. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.2 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.1 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M, the requirements of MIL-SID-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-1-38535 and the requirements herein.

- 3.7 Certificate of conformance. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change for device class M. For device class M, notification to DESC-EC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-973.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 105 (see MIL-I-38535, appendix A).

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. For device class M, sampling and inspection procedures shall be in accordance with MIL-STD-883 (see 3.1 herein). For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-I-38535 and the device manufacturer's QM plan.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET 5    |

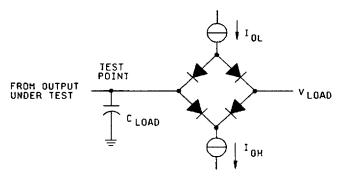

| Test                            | Symbol            |                                                    |                                                    | Group A      | Device          | <u>L</u> | imits                | _ Unit           |

|---------------------------------|-------------------|----------------------------------------------------|----------------------------------------------------|--------------|-----------------|----------|----------------------|------------------|

|                                 |                   | -55°C ≤ T                                          | r ≤ +125°C<br>n to max 1/2/                        | subgroups    | type            |          |                      |                  |

|                                 |                   | unless otherw                                      | n to max <u>1</u> / <u>2</u> /<br>ise specified    | j            |                 | Min      | Max                  | <u>i .</u>       |

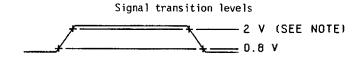

| High level input<br>voltage     | ν <sub>IH</sub> . |                                                    | BUSFLT, LRDY, VCLK, PGMD, SIZE16                   | 1,2,3        | All             | 2.3      | V <sub>CC</sub> +0.3 | V                |

|                                 |                   |                                                    | CLKIN only                                         |              |                 | 3.0      | V <sub>CC</sub> +0.3 |                  |

|                                 |                   | HWRITE, HREAD,<br>HA5-HA31, HCS,<br>HBSO-HBS3      | CSYNC,<br>HSYNC,<br>VSYNC                          |              | <br> <br> -<br> | 2.3      | v <sub>CC</sub> +0.3 | <br> <br> -      |

|                                 |                   |                                                    | All other input pins                               |              |                 | 2.0      | v <sub>CC</sub> +0.3 |                  |

| Low level input voltage         | VIL               |                                                    | нсѕ                                                | 1,2,3        | All             | -0.3     | 0.7                  |                  |

|                                 |                   |                                                    | All other                                          | 1,2,3        | All             | -0.3     | 0.8                  |                  |

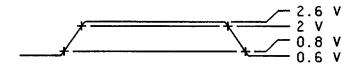

| High level output<br>voltage    | v <sub>OH</sub>   | V <sub>CC</sub> = min,<br>I <sub>OH</sub> = 400 μA |                                                    | 1,2,3        | All             | 2.6      |                      |                  |

| Low level output<br>voltage     | v <sub>oL</sub>   | V <sub>CC</sub> = max,<br>I <sub>OL</sub> = 2 mA   | DDIN, HINT,<br>HRDY, RO, R1,<br>EMU3               | 1,2,3        | All             |          | 0.8                  |                  |

|                                 |                   |                                                    | HSYNC, VSYNC                                       | <u> </u><br> |                 | <br>     | 0.8                  |                  |

|                                 |                   |                                                    | All other<br>output pins                           |              |                 |          | 0.6                  |                  |

| Output leakage<br>current (high | Io                | V <sub>CC</sub> = max                              | V <sub>0</sub> = 2.8 V                             | 1,2,3        | A11             |          | 20                   | <br>  μ <b>λ</b> |

| impedance)                      |                   |                                                    | V <sub>0</sub> = 0.6 V                             |              |                 |          | -20                  | <br> <br>        |

| Input current                   | ıı                | V <sub>I</sub> = V <sub>SS</sub>                   | 3/ All input pins except EMUO- EMU2, HREAD, HWRITE | 1,2,3        | A11<br>         |          | ±20                  |                  |

| Supply current                  | Icc               | V <sub>CC</sub> = max, freq                        | = max                                              | 1,2,3        | 01-03<br>04     |          | 265<br>280           | mA               |

| Input capacitance               | c <sub>I</sub>    | See 4.4.1.b                                        | •                                                  | 4            | ALL             |          | 18                   | pF               |

| Output capacitance              | co                | See 4.4.1.b                                        |                                                    | 4            | ALL             |          | 25                   | İ                |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON ONTO 65444 | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                                                |           | REVISION LEVEL<br>C | SHEET 6    |

| TABLE | Ι. | Electrical performance | characteristics | - | Continued. |

|-------|----|------------------------|-----------------|---|------------|

|-------|----|------------------------|-----------------|---|------------|

| Test                                                                                 | Symbol 1         | -55°C ≤ T <sub>c</sub>                | Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$ |           |                      | <u></u>                 | imits                | _ Unit |

|--------------------------------------------------------------------------------------|------------------|---------------------------------------|---------------------------------------------------------|-----------|----------------------|-------------------------|----------------------|--------|

|                                                                                      |                  | V <sub>CC</sub> = min                 | ito max <u>1</u> / <u>2</u> /<br>ise specified          | subgroups | type                 | Min                     | Max                  |        |

| Functional test                                                                      |                  | See 4.4.1.c                           |                                                         | 7,8       | ALL                  | ,                       |                      | ns     |

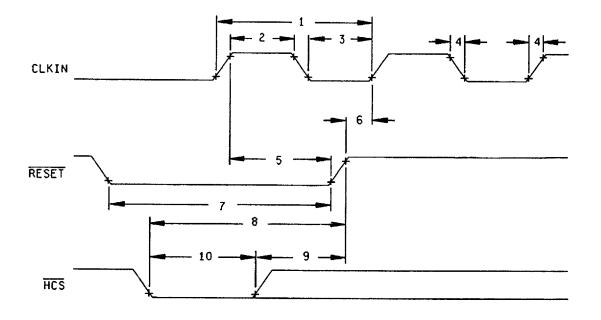

| Period, CLKIN (t <sub>Q</sub> )                                                      | tcl              | See figure 3 (1                       | )                                                       | 9,10,11   | 01<br>02<br>03<br>04 | 35<br>33<br>31.25<br>25 | 50<br>50<br>50<br>50 |        |

| Pulse duration,<br>CLKIN high                                                        | t <sub>w1</sub>  | See figure 3 (2                       | ·)                                                      | 9,10,11   | 01-03                | 10 8                    |                      | -      |

| Pulse duration,<br>CLKIN low                                                         | t <sub>w2</sub>  | See figure 3 (3                       | )                                                       | 9,10,11   | 01-03                | 10                      |                      | -      |

| Transition time,<br>CLKIN                                                            | t <sub>t1</sub>  | See figure 3 (4<br>  <u>4</u> /       | )                                                       | 9,10,11   | A11                  | 2                       | 5                    |        |

| Hold time, RESET<br>low after CLKIN<br>high                                          | t <sub>h1</sub>  | See figure 3 (5<br>  <u>5</u> /       | )                                                       | 9,10,11   | 01-03<br>04          | 15                      |                      |        |

| Setup time, RESET<br>high to CLKIN<br>going high                                     | t <sub>su1</sub> | See figure 3 (6<br>  <u>5</u> /       | )                                                       | 9,10,11   | 01-03                | 10                      |                      |        |

| Pulse width, RESET<br>low                                                            | t <sub>w3</sub>  | See figure 3<br>  (7)<br>  <u>6</u> / | <br>  Initial reset<br>  during<br>  powerup            | 9,10,11   | All                  | 160t <sub>0</sub>       |                      |        |

|                                                                                      |                  |                                       | Reset during active operation                           |           |                      | 16t <sub>Q</sub>        |                      |        |

| Setup <u>time</u> , HCS low<br>to RESET high to<br>configure self-<br>bootstrap mode | <sup>t</sup> su2 | See figure 3 (8                       | )                                                       | 9,10,11   | A11                  | 8t <sub>Q</sub> +55     |                      |        |

| Delay time, HCS going high to RESET high to configure self- bootstrap mode           | t <sub>d1</sub>  | See figure 3 (9)<br>  <u>7</u> /      | )                                                       | 9,10,11   | A11                  |                         | 4t <sub>Q</sub> -50  |        |

| Pulse width, HCS<br>low to configure<br>GSP in self-<br>bootstrap mode               | t <sub>w4</sub>  | See figure 3 (10                      | ))                                                      | 9,10,11   | All                  | 4t <sub>Q</sub> +55     |                      |        |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444            |           | REVISION LEVEL<br>C | SHEET 7    |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  - Continued.

| Test                                              | Symbol           | $ \begin{array}{c c} \text{Symbol} & \text{Conditions} \\ -55^{\circ}\text{C} \leq \text{T}_{\text{C}} \leq +125^{\circ}\text{C} \\ & \text{V}_{\text{CC}} = \text{min to max}  \underline{1}/ \ \underline{2}/ \\ & \text{unless otherwise specified} \\ \end{array} $ | Group A   | Device      | · · · · · · · · · · · · · · · · · · ·                     |            | Unit           |

|---------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|-----------------------------------------------------------|------------|----------------|

|                                                   |                  |                                                                                                                                                                                                                                                                         | subgroups | type<br>    | Min                                                       | Max        |                |

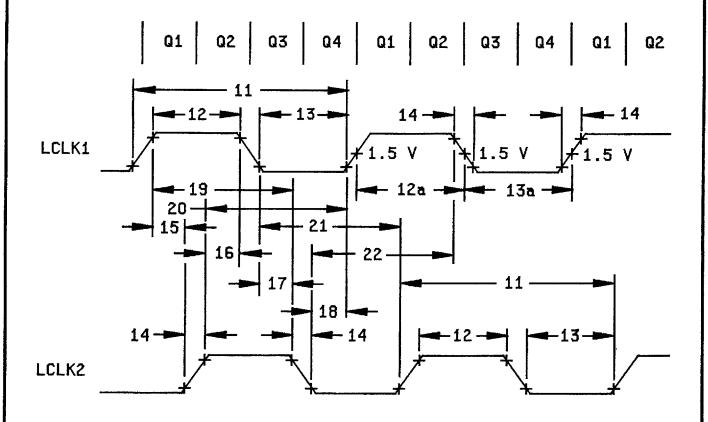

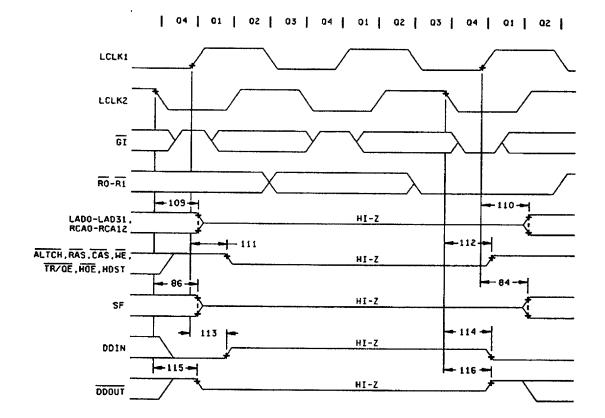

| Period of local<br>clocks LCLK1,<br>LCLK2         | t <sub>c2</sub>  | See figure 3 (11)   8/                                                                                                                                                                                                                                                  | 9,10,11   | All         | 4t <sub>c1</sub> +s                                       |            | ns             |

| Pulse width, local<br>clock high                  | t <sub>w5</sub>  | See figure 3 (12)                                                                                                                                                                                                                                                       | 9,10,11   | 01-03       | 2t <sub>Q</sub> -15<br>2t <sub>Q</sub><br>-13.5           |            | <br> <br> <br> |

| Pulse width, LCLK1<br>high (measured<br>at 1.5 V) | t <sub>w6</sub>  | See figure 3 (12a)                                                                                                                                                                                                                                                      | 9,10,11   | 01-03       | 2t <sub>Q</sub> -10                                       |            |                |

| Pulse width, local<br>clock low                   | t <sub>w7</sub>  | See figure 3 (13)                                                                                                                                                                                                                                                       | 9,10,11   | 01-03       | 2t <sub>0</sub> -15+S<br>2t <sub>0</sub> -<br>13.5+S      |            | -              |

| Pulse width, LCLK1<br>low (measured<br>at 1.5 V)  | t <sub>w8</sub>  | See figure 3 (13a)                                                                                                                                                                                                                                                      | 9,10,11   | 01-03<br>04 | 2t <sub>Q</sub> -10<br>+S<br>2t <sub>Q</sub> -7<br>+S     |            |                |

| Transition time,<br>LCLK1 or LCLK2                | t <sub>t2</sub>  | See figure 3 (14)                                                                                                                                                                                                                                                       | 9,10,11   | 01-03<br>04 | ,                                                         | 15<br>13.5 | <br>  <br>     |

| Hold time, LCLK2<br>low after LCLK1<br>high       | t <sub>h2</sub>  | See figure 3 (15)                                                                                                                                                                                                                                                       | 9,10,11   | 01-03       | t <sub>Q</sub> -15<br>t <sub>Q</sub> -13.5                |            |                |

| Hold time, LCLK1<br>high after LCLK2<br>high      | t <sub>h</sub> 3 | See figure 3 (16)                                                                                                                                                                                                                                                       | 9,10,11   | 01-03<br>04 | t <sub>Q</sub> -15<br> t <sub>Q</sub> -13.5               | ******     | <br> <br> <br> |

| Hold time, LCLK2<br>high after LCLK1<br>low       | t <sub>h4</sub>  | See figure 3 (17)                                                                                                                                                                                                                                                       | 9,10,11   | 01-03<br>04 | t <sub>Q</sub> -15<br>t <sub>Q</sub> -13.5                |            | . <br>. <br>.  |

| Hold time, LCLK1<br>low after LCLK2<br>low        | t <sub>h5</sub>  | See figure 3 (18)                                                                                                                                                                                                                                                       | 9,10,11   | 01-03<br>04 | t <sub>Q</sub> -15+S<br>t <sub>Q</sub> -13.5<br>+S        |            |                |

| Hold time, LCLK2<br>high after LCLK1<br>high      | t <sub>h6</sub>  | See figure 3 (19)                                                                                                                                                                                                                                                       | 9,10,11   | 01-03       | 3t <sub>Q</sub> -15<br>3t <sub>Q</sub><br>-13.5           |            |                |

| Hold time, LCLK1<br>low after LCLK2<br>high       | t <sub>h7</sub>  | See figure 3 (20)                                                                                                                                                                                                                                                       | 9,10,11   | 01-03<br>04 | 3t <sub>0</sub> -15+S<br>3t <sub>0</sub><br>-13.5+S       |            |                |

| Hold time, LCLK2<br>low after LCLK1<br>low        | t <sub>h8</sub>  | <br>  See figure 3 (21)                                                                                                                                                                                                                                                 | 9,10,11   | 01-03<br>04 | 3t <sub>Q</sub> -15<br>+S<br> 3t <sub>Q</sub><br> -13.5+S |            |                |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET<br>8 |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  - Continued.

| Test Symbol                                                  | Symbol           | Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$                                              | Group A | Device<br>type | <u>Li</u>                                               | mits<br>            | _  Unit           |

|--------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------|---------|----------------|---------------------------------------------------------|---------------------|-------------------|

|                                                              |                  | $V_{CC}$ = min to max $\frac{1}{2}$ / unless otherwise specified                                     |         |                | <br>  Min                                               | Max                 | j                 |

| Hold time, LCLK1<br>high after LCLK2<br>low                  | t <sub>h9</sub>  | See figure 3 (22)                                                                                    | 9,10,11 | 01-03          | 3t <sub>Q</sub> -15<br>+S<br>3t <sub>Q</sub><br>-13.5+S |                     | ns                |

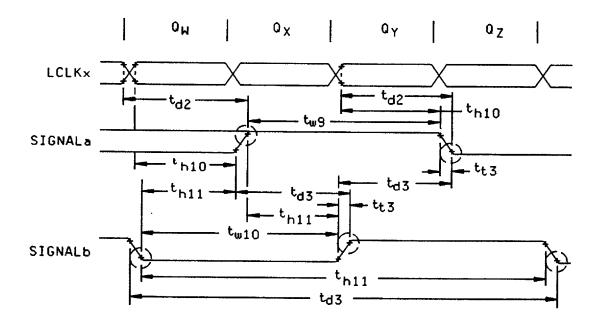

| Hold time, LCLKx <u>9/</u><br>to output signal<br>nct valid  | t <sub>h10</sub> | ·                                                                                                    | 9,10,11 | All            | t <sub>Q</sub> -15                                      |                     |                   |

| Delay time, LCLKx<br>start of transi-<br>tion to output      | t <sub>d2</sub>  | Fast: RAS, CAS, ALTCH, TR/QE, DDOUT, DDIN, EMU3, HOE, RO, RI, HDST, WE                               | 9,10,11 | A11            |                                                         | t <sub>Q</sub> +15  |                   |

| signal valid <u>9</u> /                                      |                  | Slow: LAD, RCA, SF                                                                                   |         |                |                                                         | t <sub>Q</sub> +22  |                   |

| Hold time, output signal valid to output signal not valid 9/ | t <sub>h11</sub> | Fa <u>st: RAS, CAS, ALTCH, TR/QE,</u> DDOUT, DDIN, EMU3, HOE, RO, RI, HOST, WE                       | 9,10,11 | All            | nt <sub>Q</sub> -16                                     |                     |                   |

|                                                              |                  | Slow: LAD, RCA, SF                                                                                   |         | <br> <br>      | nt <sub>Q</sub> -22                                     | <br> <br>           |                   |

| Delay time, output<br>signal started<br>transition to        | t <sub>d3</sub>  | Fa <u>st: RAS, CAS, ALTCH, TR/QE,</u><br><u>DD</u> OUT, DDIN, EMU3, HOE, RO,<br>RI, HDST, WE         | 9,10,11 | All            |                                                         | nt <sub>Q</sub> +15 | -<br> <br> <br> - |

| output signal<br>valid <u>9</u> /                            |                  | Slow: LAD, RCA, SF                                                                                   |         |                |                                                         | nt <sub>Q</sub> +22 |                   |

| Transition time, output signal                               | t <sub>t3</sub>  | Fa <u>st: RAS, CAS, ALTCH, TR/QE,</u><br><u>DD</u> OUT, DDI <u>N,</u> EMU3, HOE, RO,<br>RI, HOST, WE | 9,10,11 | <br>  A11<br>  |                                                         | 15                  |                   |

| <u>9</u> /                                                   |                  | Slow: LAD, RCA, SF                                                                                   |         |                |                                                         | 22                  |                   |

| Pulse width, toutput signal high 9/                          | t <sub>w</sub> 9 | Fa <u>st: RAS, CAS, ALTCH, TR/QE,</u><br>DDOUT, DDIN, EMU3, HOE, RO,<br>RI, HDST, WE                 | 9,10,11 | All            | nt <sub>Q</sub> -15                                     |                     |                   |

|                                                              |                  | Slow: LAD, RCA, SF                                                                                   |         | <br> <br>      | nt <sub>Q</sub> -22                                     |                     |                   |

| Pulse width,<br>output signal<br>low <u>9</u> /              | <sup>t</sup> w10 | Fa <u>st: RAS, CAS, ALTCH, TR/QE,</u> DDOUT, DDIN, EMU3, HOE, RO, R1, HDST, WE                       | 9,10,11 | <br>  All      | nt <sub>Q</sub> -15                                     |                     |                   |

|                                                              |                  | Slow: LAD, RCA, SF                                                                                   |         |                | nt <sub>0</sub> -22                                     |                     |                   |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET<br>9 |

TABLE I.  $\underline{\text{Electrical performance characteristics}} \text{ - Continued.}$

| Test                                                                  | Symbol            | Conditions                                                                                                                                                                     | Group A   | Device      | <u>Li</u> | mits | Uni             |

|-----------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|-----------|------|-----------------|

|                                                                       |                   | $\begin{array}{c c} -55^{\circ}C \leq T_{C} \leq +125^{\circ}C \\ V_{CC} = \min \text{ to max } \underline{1}/\underline{2}/\\ unless \text{ otherwise specified} \end{array}$ | subgroups | type<br>    | Min       | Max  |                 |

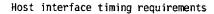

| Setup time, <u>ad</u> dress<br>prior to HCS<br>going low              | t <sub>su3</sub>  | See figure 3 (23)                                                                                                                                                              | 9,10,11   | 01-03       | 12        |      | ns              |

| Hold tim <u>e,</u> address<br>after HCS low                           | t <sub>h12</sub>  | See figure 3 (24)                                                                                                                                                              | 9,10,11   | 01-03<br>04 | 12<br>10  |      | _               |

| Pulse width, HCS<br>high                                              | t <sub>wll</sub>  | See figure 3 (25)                                                                                                                                                              | 9,10,11   | 01-03       | 28<br>25  |      | _               |

| Pulse width, HREAD high                                               | t <sub>w12</sub>  | See figure 3 (26)                                                                                                                                                              | 9,10,11   | 01-03       | 28<br>25  |      | _               |

| Pulse width,<br>HWRITE high                                           | t <sub>w13</sub>  | See figure 3 (27)                                                                                                                                                              | 9,10,11   | 01-03       | 28<br>25  |      |                 |

| Setup time, HREAD<br>high to HWRITE<br>going low                      | t <sub>su4</sub>  | See figure 3 (28)                                                                                                                                                              | 9,10,11   | 01-03       | 28<br>25  |      | -               |

| Setup time, HWRITE<br>high to HREAD<br>going low                      | t <sub>su5</sub>  | See figure 3 (29)                                                                                                                                                              | 9,10,11   | 01-03       | 28<br>25  |      | _               |

| Pulse width, HREAD low                                                | t <sub>w14</sub>  | See figure 3 (30)                                                                                                                                                              | 9,10,11   | 01-03       | 18<br>15  |      | _               |

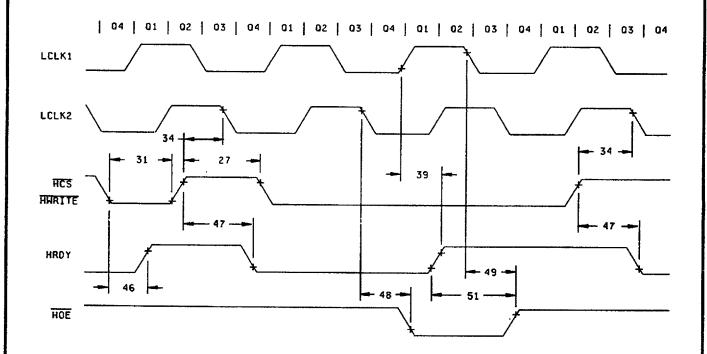

| Pu <u>lse wi</u> dth,<br>HWRITE low                                   | t <sub>w15</sub>  | See figure 3 (31)                                                                                                                                                              | 9,10,11   | 01-03       | 18<br>15  |      | _  <br>_        |

| Setup time, HCS<br>low to HWRITE<br>going high                        | t <sub>su6</sub>  | See figure 3 (32)                                                                                                                                                              | 9,10,11   | 01-03       | 18<br>15  |      | _               |

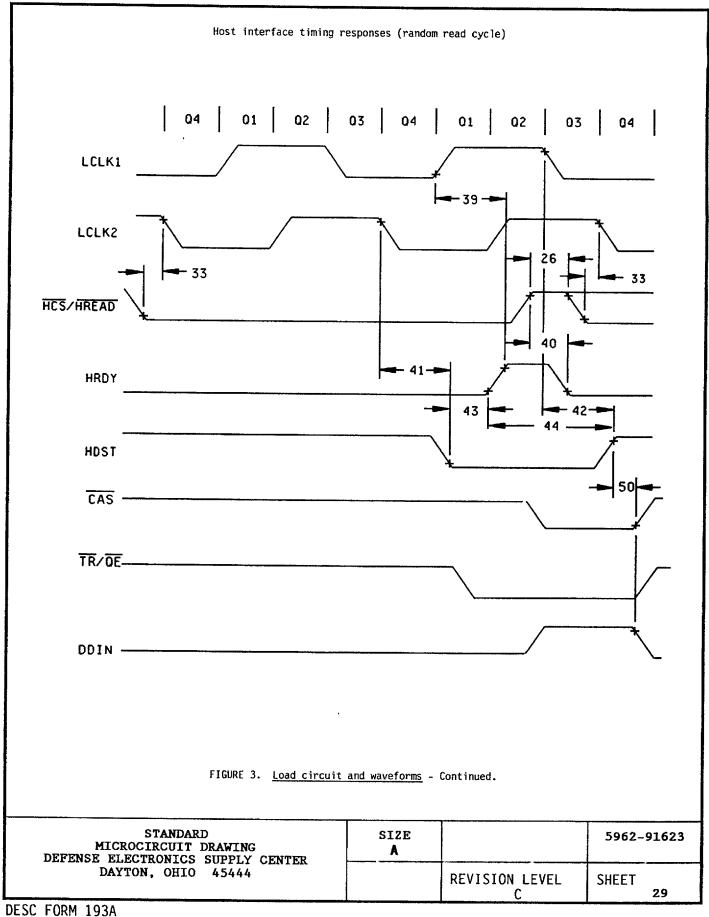

| Setup_time, later<br>of HCS low or<br>HREAD low to<br>LCLK2 going low | t <sub>su</sub> 7 | See figure 3 (33)<br>  <u>10</u> /                                                                                                                                             | 9,10,11   | 01-03       | 30<br>25  |      | -<br> <br> <br> |

| Setup time, later of HWRITE high or HCS high to LCLK2 going low       | t <sub>su8</sub>  | See figure 3 (34)<br>  <u>10</u> /                                                                                                                                             | 9,10,11   | 01-03       | 30<br>25  |      |                 |

| Hold time, HREAD<br>high after LCLK2<br>going low                     | t <sub>h13</sub>  | See figure 3 (35)<br>  <u>11</u> /                                                                                                                                             | 9,10,11   | All         | 0         |      | _               |

| Hold time, HWRITE<br>low after LCLK2<br>going low                     | t <sub>h14</sub>  | See figure 3 (36)   11/                                                                                                                                                        | 9,10,11   | All         | 0         |      |                 |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET<br>10 |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  - Continued.

| Test   Symbol                                                                  | Symbol            | Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$                                         | Group A<br>subgroups | Device<br>type | Li                                         | mits                                               | Unit         |

|--------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------|----------------------|----------------|--------------------------------------------|----------------------------------------------------|--------------|

|                                                                                | <u> </u>          | $V_{CC} = \min_{n=1}^{\infty} to \max_{n=1}^{\infty} \frac{1}{2}$<br>unless otherwise specified |                      |                | Min                                        | Max                                                | <u> </u><br> |

| Setup time, HREAD<br>high to LCLK2<br>going low,<br>prefetch read<br>mode      | t <sub>su9</sub>  | See figure 3 (37)<br>10/ 12/                                                                    | 9,10,11              | 01-03          | 30 25                                      |                                                    | ns           |

| Setur time, HCS<br>low to HREAD<br>going high                                  | t <sub>sul0</sub> | See figure 3 (38)                                                                               | 9,10,11              | 01-03          | 18<br>15                                   |                                                    |              |

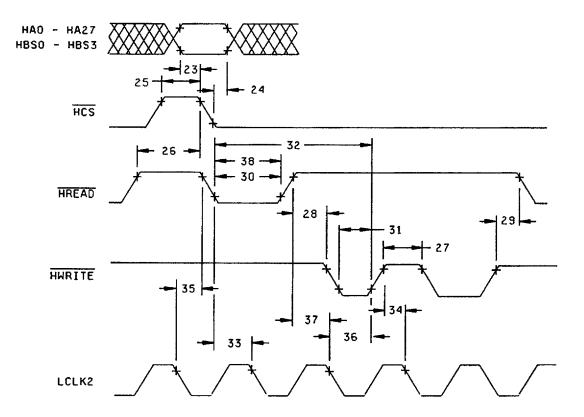

| Delay time, from<br>LCLK1 going high<br>to HRDY high<br>(end of read<br>cycle) | t <sub>d4</sub>   | See figure 3 (39)                                                                               | 9,10,11              | 01-03<br>04    |                                            | t <sub>Q</sub> +20<br>t <sub>Q</sub> +18           |              |

| Delay time, from<br>earlier of HREAD<br>or HCS high to<br>HRDY low             | t <sub>d5</sub>   | See figure 3 (40)                                                                               | 9,10,11              | 01-03          |                                            | 20                                                 |              |

| Delay time, from<br>LCLK2 going low<br>to HDST low                             | <sup>t</sup> d6   | See figure 3 (41)                                                                               | 9,10,11              | 01-03<br>04    |                                            | t <sub>0</sub> +15+S<br>t <sub>0</sub> +13.5<br>+S |              |

| Delay time, from<br>LCLK1 going low<br>to HDST high                            | t <sub>d7</sub>   | See figure 3 (42)                                                                               | 9,10,11              | 01-03          |                                            | t <sub>Q</sub> +15<br>t <sub>Q</sub> +13.5         |              |

| Setup time, HDST<br>low to HRDY<br>going high                                  | t <sub>su12</sub> | See figure 3 (43)                                                                               | 9,10,11              | 01-03<br>04    | t <sub>Q</sub> -15<br>t <sub>Q</sub> -13.5 |                                                    |              |

| Delay time, from<br>HRDY going high<br>to HDST high                            | t <sub>d8</sub>   | See figure 3 (44)                                                                               | 9,10,11              | 01-03          |                                            | 2t <sub>Q</sub> +15<br>2t <sub>Q</sub> +13.5       |              |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-91623 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET      |

${\sf TABLE\ I.\ \underline{Electrical\ performance\ characteristics}\ - Continued.}$

| Test                                                                               | Symbol                                                                   | Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$ | Group A | Device<br>type | <u>L</u> | imits<br>                                          | Unit           |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------|---------|----------------|----------|----------------------------------------------------|----------------|

|                                                                                    | $V_{CC} = min \text{ to max } \frac{1}{2}$<br>unless otherwise specified | Jabgi caps                                              | 10,50   | Min            | Max      | <u> </u>                                           |                |

| Delay time, from<br>later of HREAD<br>or HCS low to<br>HRDY high after<br>prefetch | t <sub>d14</sub>                                                         | See figure 3 (45)                                       | 9,10,11 | 01-03          |          | 25                                                 | ns             |

| Delay time, from later of HCS or HWRITE low to HRDY high (device ready)            | <sup>t</sup> d15                                                         | See figure 3 (46)                                       | 9,10,11 | 01-03<br>04    |          | 25 20                                              |                |

| Delay time, from earlier of HCS or HWRITE high to HRDY low (end of write)          | t <sub>d16</sub>                                                         | See figure 3 (47)                                       | 9,10,11 | 01-03          |          | 25<br>20                                           |                |

| Delay time, from<br>LCL <u>K2 g</u> oing low<br>to HOE low                         | <sup>t</sup> d17                                                         | See figure 3 (48)                                       | 9,10,11 | 01-03<br>04    |          | t <sub>Q</sub> +15+S<br>t <sub>Q</sub> +13.5<br>+S |                |

| Delay time, from<br>LCL <u>K1 g</u> oing low<br>to HOE high                        | <sup>t</sup> d18                                                         | See figure 3 (49)                                       | 9,10,11 | 01-03          |          | t <sub>Q</sub> +15<br>t <sub>Q</sub> +13.5         | <br> <br> <br> |

| Hold time CAS, TR/QE,<br>DDIN valid after<br>HDST high                             | t <sub>h31</sub>                                                         | See figure 3 (50)                                       | 9,10,11 | 03             | -2<br>-2 |                                                    |                |

| Delay time, from<br>HRD <u>Y g</u> oing high<br>to HOE high                        | <sup>t</sup> d20                                                         | See figure 3 (51)                                       | 9,10,11 | 01-03          |          | 2t <sub>Q</sub> +15<br>2t <sub>Q</sub> +13.5       |                |

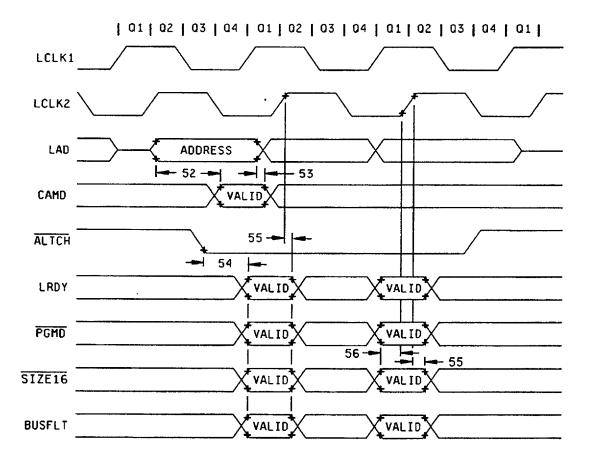

| Access time, CAMD<br>valid after<br>address valid on<br>LAD                        | t <sub>a1</sub>                                                          | See figure 3 (52)                                       | 9,10,11 | 01-03<br>04    |          | 3t <sub>Q</sub> -45<br>3t <sub>Q</sub> -37         |                |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET 12   |

TABLE I. <u>Electrical performance characteristics</u> - Continued.

| Test                                                                                                                     | Symbol             | Conditions<br>-55°C ≤ Y <sub>C</sub> ≤ +125°C                  | Group A<br>subgroups | Device<br>type     | L:                                            | imits<br>                                  | Uni      |

|--------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------|----------------------|--------------------|-----------------------------------------------|--------------------------------------------|----------|

|                                                                                                                          |                    | $V_{CC}$ = min to max $\frac{1}{2}$ unless otherwise specified |                      |                    | Min                                           | Max                                        | <u> </u> |

| Hold time, CAMD<br>valid after<br>address no longer<br>valid on LAD                                                      | t <sub>h15</sub> . | See figure 3 (53)                                              | 9,10,11              | All                | 0                                             |                                            | ns       |

| Access time,<br>control_valid<br>(LRDY, PGMD,                                                                            | ta2                | See figure 3 (54)                                              | 9,10,11              | 01-03              |                                               | 3t <sub>Q</sub> -35+S                      |          |

| SIZE1 <u>6, BU</u> SFLT)<br>after ALTCH low                                                                              |                    |                                                                |                      | 04                 |                                               | 3t <sub>Q</sub> -27+\$                     |          |

| Hold time <u>, co</u> ntrol<br>( <u>LRDY, PGMD</u> ,<br>SIZE16, BUSFLT)<br>valid after<br>LCLK2 high                     | t <sub>h16</sub>   | See figure 3 (55)                                              | 9,10,11              | All                | 0                                             |                                            |          |

| Se <u>tup</u> time, LRDY,<br><u>PGMD,</u> BUSFLT,<br>SIZE16 valid                                                        | t <sub>sul5</sub>  | See figure 3 (56)                                              | 9,10,11              | 01-03              | 20                                            |                                            |          |

| before LCLK2<br>going high                                                                                               |                    |                                                                |                      | 04                 | 15                                            |                                            |          |

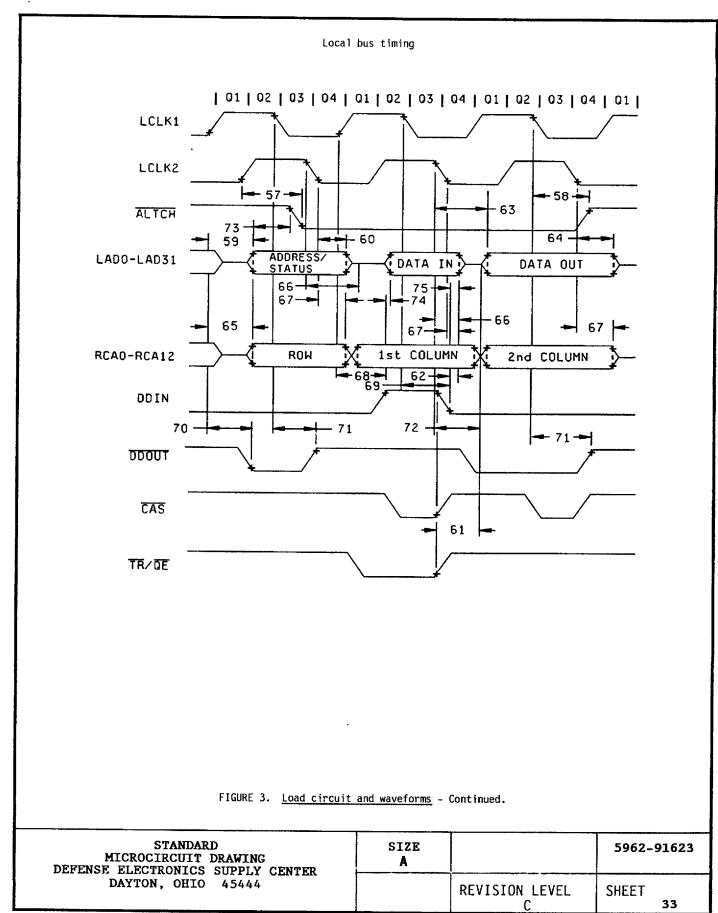

| Delay time, ALTCH<br>low after LCLK2<br>going high                                                                       | t <sub>d21</sub>   | See figure 3 (57)                                              | 9,10,11              | 01-03              |                                               | t <sub>Q</sub> +15<br>t <sub>Q</sub> +13.5 |          |

| Delay time, ALTCH<br>high after LCLK1<br>going low                                                                       | <sup>t</sup> d22   | See figure 3 (58)                                              | 9,10,11              | 01-03<br>04        |                                               | t <sub>Q</sub> +15<br>t <sub>Q</sub> +13.5 |          |

| Delay time, LADO-<br>LAD31 address<br>valid after LCLK1<br>going high                                                    | t <sub>d23</sub>   | See figure 3 (59)                                              | 9,10,11              | 01-03              |                                               | t <sub>Q</sub> +22<br>t <sub>Q</sub> +20   |          |

| old time, LADO-<br>LAD31 address<br>valid after<br>LCL <sup>P2</sup> low                                                 | t <sub>h17</sub>   | See figure 3 (60)                                              | 9,10,11              | 01-03              | t <sub>Q</sub> -15+S<br> t <sub>Q</sub> -12+S |                                            |          |

| elay time, LADO-<br>LAD31 driven                                                                                         | t <sub>d24</sub>   | See figure 3 (61)                                              | 9,10,11              | 01-03              | t <sub>Q</sub> -5+S                           |                                            |          |

| after earlier of DDIN going low or CAS going high or TR/QE going high                                                    |                    |                                                                |                      | 04                 | t <sub>Q</sub> -5+S                           |                                            |          |

| old time, LADO-<br>LAD31 read data<br>valid after<br>earlier of <u>DDIN</u><br>low <u>or RAS</u> , CAS,<br>or TR/QE high | t <sub>h18</sub>   | See figure 3 (62)                                              | 9,10,11              | <br>  A11<br> <br> | 3.5                                           |                                            |          |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET 13   |

| Test                                                                           | Symbol           | Conditions                                                                                                                                                                       | Group A   | Device      | <u>Li</u>          | mits                                                 | Unit      |

|--------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|--------------------|------------------------------------------------------|-----------|

|                                                                                |                  | $ \begin{array}{c c} -55^{\circ}C \leq T_{C} \leq +125^{\circ}C \\ V_{CC} = \min \text{ to max } \underline{1}/\underline{2}/\\ unless \text{ otherwise specified} \end{array} $ | subgroups | type        | Min                | Max                                                  | <br> <br> |

| Delay time, LADO-<br>LAD31 data valid<br>after LCLK2<br>going low<br>(write)   | <sup>t</sup> d25 | See figure 3 (63)                                                                                                                                                                | 9,10,11   | 01-03<br>04 |                    | t <sub>Q</sub> +22+S                                 | ns        |

| Hold time, LADO-<br>LAD31 data valid<br>after LCLK2 low                        | t <sub>h19</sub> | See figure 3 (64)                                                                                                                                                                | 9,10,11   | 01-03       | t <sub>Q</sub> -15 |                                                      |           |

| (write)  Delay time, RCAO- RCA12 row address valid after LCLK1 going high      | td26             | See figure 3 (65)                                                                                                                                                                | 9,10,11   | All         |                    | t <sub>Q</sub> +22                                   |           |

| Delay time, LADO-<br>LAD31 column<br>address valid<br>after LCLK2<br>going low | t <sub>d27</sub> | See figure 3 (66)                                                                                                                                                                | 9,10,11   | 01-03       |                    | t <sub>Q</sub> +22+S<br>t <sub>Q</sub> +20+S         |           |

| Hold time, RCAO-<br>RCA12 address<br>valid after<br>LCLK2 low                  | t <sub>h20</sub> | See figure 3 (67)                                                                                                                                                                | 9,10,11   | 01-03<br>04 | t <sub>Q</sub> -15 |                                                      |           |

| Delay time, DDIN<br>high after LCLK1<br>going high                             | t <sub>d28</sub> | See figure 3 (68)                                                                                                                                                                | 9,10,11   | 01-03       |                    | t <sub>Q</sub> +15<br>t <sub>Q</sub> +13.5           |           |

| Delay time, DDIN<br>low after LCLK1<br>going low                               | t <sub>d29</sub> | See figure 3 (69)                                                                                                                                                                | 9,10,11   | 01-03       |                    | t <sub>0</sub> +15<br> t <sub>0</sub> +13.5          |           |

| Delay time, DDOUT<br>low after LCLK1<br>going high                             | t <sub>d30</sub> | See figure 3 (70)                                                                                                                                                                | 9,10,11   | 01-03<br>04 |                    | t <sub>Q</sub> +15<br>t <sub>Q</sub> +13.5           |           |

| Delay time, DDOUT<br>high after LCLK1<br>going low                             | t <sub>d31</sub> | See figure 3 (71)                                                                                                                                                                | 9,10,11   | 01-03       |                    | t <sub>Q</sub> +15<br>t <sub>Q</sub> +13.5           |           |

| elay time, DDOUT<br>low after LCLK2<br>going low                               | t <sub>d32</sub> | See figure 3 (72)                                                                                                                                                                | 9,10,11   | 01-03       |                    | t <sub>Q</sub> +15+S<br> t <sub>Q</sub> +13.5<br> +S |           |

| Setup time, LADO-<br>LAD31 d <u>ata v</u> alid<br>before ALTCH<br>going low    | tsu16            | See figure 3 (73)                                                                                                                                                                | 9,10,11   | 01-03       | t <sub>Q</sub> -16 |                                                      |           |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91623 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET 14   |

| Test                                                         | Symbo1               | Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$              | Group A | <br> Device<br> s  type |            | imits                                              | Unit  |

|--------------------------------------------------------------|----------------------|----------------------------------------------------------------------|---------|-------------------------|------------|----------------------------------------------------|-------|

|                                                              |                      | V <sub>CC</sub> = min to max <u>1/</u><br>unless otherwise specified | 2/      | - Lype                  | Min        | Max                                                |       |

| Enable time, data<br>valid after DDIN<br>high                | ten1                 | See figure 3 (74)<br>13/                                             | 9,10,11 | 01-03<br>04             | <br>  <br> | 2t <sub>Q</sub> -20<br>2t <sub>Q</sub> -17         | ns    |

| Disable time, data<br>high-impedance<br>after DDIN low       | <sup>t</sup> dis1    | See figure 3 (75)<br>13/4/                                           | 9,10,11 | 01-03                   | <u> </u>   | t <sub>Q</sub> -12+S<br>t <sub>Q</sub> -10+S       |       |

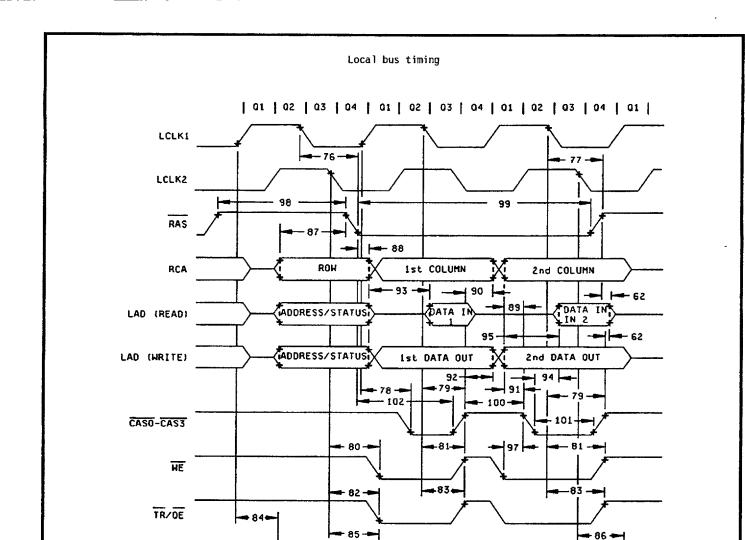

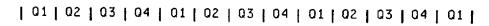

| Delay time, RAS<br>low after LCLK1<br>going low              | t <sub>d33</sub>     | See figure 3 (76)                                                    | 9,10,11 | 01-03<br>04             |            | t <sub>Q</sub> +12+S<br>t <sub>Q</sub> +10+S       |       |

| Delay time, RAS<br>high after LCLK1<br>going low             | t <sub>d34</sub>     | See figure 3 (77)                                                    | 9,10,11 | 01-03<br>04             |            | t <sub>Q</sub> +12<br>t <sub>Q</sub> +10           |       |

| Delay time, CAS<br>low after LCLK1<br>going high             | t <sub>d35</sub>     | See figure 3 (78)                                                    | 9,10,11 | 01-03<br>04             |            | t <sub>Q</sub> +12<br>t <sub>Q</sub> +10           |       |

| Delay time, CAS<br>high after LCLK1<br>going low             | t <sub>d36</sub>     | See figure 3 (79)                                                    | 9,10,11 | 01-03                   |            | t <sub>Q</sub> +12<br>t <sub>Q</sub> +10           |       |

| Delay time, WE low<br>after LCLK2<br>going low               | t <sub>d37</sub>     | See figure 3 (80)                                                    | 9,10,11 | 01-03                   |            | t <sub>0</sub> +15+S<br>t <sub>0</sub> +13.5<br>+S |       |

| Delay time, WE high after LCLK1 going low                    | t <sub>d38</sub>     | See figure 3 (81)                                                    | 9,10,11 | All                     |            | t <sub>Q</sub> +15                                 |       |

| Delay time, TR/QE<br>low after LCLK2<br>going low            | t <sub>d39</sub>     | See figure 3 (82)                                                    | 9,10,11 | 01-03<br>04             |            | t <sub>Q</sub> +15+5                               |       |

| Delay time, TR/QE<br>high after LCLK1<br>going low           | t <sub>d40</sub>     | See figure 3 (83)                                                    | 9,10,11 | 01-03<br>04             |            | t <sub>Q</sub> +15<br>t <sub>Q</sub> +13.5         |       |

| Delay time, SF<br>valid after<br>LCLK1 going high            | t <sub>d41</sub>     | See figure 3 (84)                                                    | 9,10,11 | 01-03<br>04             |            | t <sub>Q</sub> +22<br>t <sub>Q</sub> +20           |       |

| Delay time, SF<br>valid after<br><u>LCLK2 going</u> low      | t <sub>d42</sub>     | See figure 3 (85)                                                    | 9,10,11 | 01-03                   |            | t <sub>Q</sub> +22+S<br>t <sub>Q</sub> +20+S       |       |

| Delay time, SF<br>high-impedance<br>after LCLK2<br>going low | t <sub>d43</sub>     | See figure 3 (86)<br>4/                                              | 9,10,11 | 01-03                   |            | t <sub>Q</sub> +22<br>t <sub>Q</sub> +20           |       |

| ee footnotes at end o                                        | of table.            |                                                                      |         | <u>'</u>                |            | 4                                                  |       |

|                                                              | STANDAE<br>CIRCUIT   | DRAWING                                                              | SIZE    |                         |            | 596                                                | 2-916 |

|                                                              | CTRONICS<br>ON, OHIO | SUPPLY CENTER 45444                                                  |         | REVISION                | LEVEL      | SHEE                                               | <br>Т |

REVISION LEVEL C

15

| Test                                                                                    | Symbol              | Conditions $-55^{\circ}C \leq T_{C} \leq +125$        | Group A S°C   subgroups | Device<br>type | <u>Li</u>                                               | mits                                          | Unit                                  |

|-----------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------|-------------------------|----------------|---------------------------------------------------------|-----------------------------------------------|---------------------------------------|

|                                                                                         |                     | V <sub>CC</sub> = min to max<br>unless otherwise spec | < <u>1</u> / <u>2</u> / | type           | Min                                                     | Max                                           |                                       |

| Setup time, row address valid                                                           | t <sub>su17</sub>   | See figure 3 (87)   14/                               | 9,10,11                 | 01-03          | 2t <sub>Q</sub> -22                                     |                                               | ns                                    |

| before RAS going<br>low                                                                 |                     |                                                       |                         | 04             | 2t <sub>Q</sub> -20                                     |                                               | <u>.</u><br>!                         |

| Hold time, row<br>addres <u>s v</u> alid<br>after RAS low                               | t <sub>h22</sub>    | See figure 3 (88)<br>  <u>14</u> /                    | 9,10,11                 | 01-03<br>04    | t <sub>Q</sub> -5+S                                     |                                               |                                       |

| Setup time, column<br>address valid<br>before CAS going<br>low                          | t <sub>su18</sub>   | See figure 3 (89)                                     | 9,10,11                 | 01-03<br>04    | t <sub>Q</sub> -22<br>t <sub>Q</sub> -20                |                                               |                                       |

| Hold time, column<br>address valid<br>after CAS high                                    | t <sub>h23</sub>    | See figure 3 (90)                                     | 9,10,11                 | 01-03<br>04    | t <sub>Q</sub> -15<br>t <sub>Q</sub> -13.5              |                                               |                                       |

| Setup time, write<br>data va <u>lid</u><br>before CAS going<br>low                      | t <sub>su19</sub>   | See figure 3 (91)                                     | 9,10,11                 | 01-03          | t <sub>Q</sub> -22                                      |                                               |                                       |

| Hold time, write<br><u>dat</u> a valid after<br>CAS high                                | t <sub>h24</sub>    | See figure 3 (92)                                     | 9,10,11                 | 01-03<br>04    | t <sub>Q</sub> -15<br> t <sub>Q</sub> -13.5             |                                               |                                       |

| Access time, data-<br>in valid after<br>RAS low (assuming<br>maximum<br>transition time | t <sub>a3</sub>     | See figure 3 (93)                                     | 9,10,11                 | 01-03          |                                                         | 4t <sub>Q</sub> -8+S<br> 4t <sub>Q</sub> -8+S |                                       |

| Access time, data-<br>in valid after<br>CAS going low                                   | t <sub>a4</sub>     | See figure 3 (94)                                     | 9,10,11                 | All            |                                                         | 2t <sub>Q</sub> -8                            |                                       |

| Access time, data-<br>in valid after                                                    | t <sub>a5</sub>     | See figure 3 (95)                                     | 9,10,11                 | 01-03          |                                                         | 3t <sub>Q</sub> -20                           |                                       |

| column address valid Setup time, write                                                  | t <sub>su20</sub>   | See figure 3 (97)                                     | 9,10,11                 | 04             | t <sub>0</sub> -15                                      | 3t <sub>Q</sub> -12                           |                                       |

| low before CAS<br>going low (on<br>write cycles)                                        | Suzo                |                                                       |                         | 04             | t <sub>Q</sub> -13.5                                    |                                               |                                       |

| Pu <u>lse</u> width,<br>RAS high                                                        | t <sub>w16</sub>    | See figure 3 (98)                                     | 9,10,11                 | 01-03<br>04    | 4t <sub>Q</sub> -12<br>+S<br> 4t <sub>Q</sub> -10<br>+S |                                               |                                       |

| Pu <u>lse</u> width,<br>RAS low                                                         | t <sub>w17</sub>    | See figure 3 (99)<br>  <u>15</u> /                    | 9,10,11                 | 01-03          | 4nt <sub>Q</sub> -12<br>+S'                             |                                               |                                       |

| ee footnotes at end o                                                                   | of table.           |                                                       |                         |                | 1 73 ]                                                  |                                               | · · · · · · · · · · · · · · · · · · · |

|                                                                                         |                     | DRAWING                                               | SIZE                    |                |                                                         | 596                                           | 2-9162                                |

|                                                                                         | TRONICS<br>ON, OHIO | SUPPLY CENTER 45444                                   | <del> </del>            | EVISION        |                                                         | SHEE                                          | т                                     |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  - Continued.

| Test                                                                   | Symbol            | Conditions $-55^{\circ}C \leq T_C \leq +125^{\circ}C$           | Group A subgroups | Device<br>type | <u>Li</u>                                                | mits<br>                                         | Unit         |