# **630AG Receive Converter**

#### **Features**

- Data loopback mode

- Automatic output shutdown

- Dual-rail PCM output

- Internal phase-locked loop

- Unipolar clock output

- TTL-compatible output

## **Description**

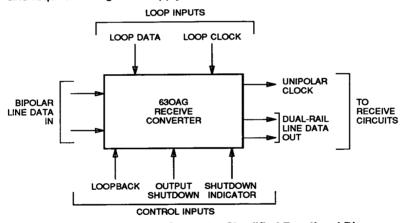

The 630AG Receive Converter hybrid integrated circuit (HIC) extracts clock and PCM information from the incoming bipolar digital line and regenerates unipolar clock and dual-rail PCM signals at its output for DS1 applications. A data loopback capability and an automatic output shutdown mechanism are provided. The 630AG Receive Converter is available in a 20-pin ceramic HIC DIP and requires a single 5 V supply.

Figure 1. Receive Converter Simplified Functional Diagram

# **User Information**

## **Pin Descriptions**

| TO 19 | ₫ | 1  |        | 20 |   | NC      |

|-------|---|----|--------|----|---|---------|

| NC    | 4 | 2  |        | 19 | P | TO1     |

| NC    | ᅥ | 3  |        | 18 | Þ | ASDCTRL |

| NC    | Ь | 4  | 63OAG  | 17 | Þ | PCMIN2  |

| GND   | ᅥ | 5  | 000/12 | 16 | Þ | PCMIN1  |

| SDOUT | Ь | 6  |        | 15 | Þ | LPCM2   |

| VDD   | Ь | 7  |        | 14 | þ | PCM2    |

| CLK   | П | 8  |        | 13 | þ | LCTRL   |

| PCM1  | П | 9  |        | 12 | Þ | LCLK    |

| LPCM1 | Ц | 10 |        | 11 | þ | SDCTRL  |

|       |   |    |        |    |   |         |

| Symbol  | Pin        | Symbol      | Pin |

|---------|------------|-------------|-----|

| ASDCTRL | 18         | PCM1        | 9   |

| CLK     | 8          | PCM2        | 14  |

| GND     | 5          | PCMIN1      | 16  |

| LCLK    | 12         | PCMIN2      | 17  |

| LCTRL   | 13         | SDCTRL      | 11  |

| LPCM1   | 10         | SDOUT       | 6   |

| LPCM2   | 15         | TO1         | 19  |

| NC      | 24,        | TO19        | 1   |

|         | 2—4,<br>20 | <b>V</b> DD | 7   |

Figure 2. Pin Function Diagram and Alphabetical Listing of Symbols

Table 1. Pin Descriptions

| Pin         | Symbol | Туре | Name/Function                                                                                                                                                              |

|-------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | TO19   | _    | Connect to Pin 19.                                                                                                                                                         |

| 2<br>3<br>4 | NC     | _    | No Connection.                                                                                                                                                             |

| 5           | GND    | _    | Ground.                                                                                                                                                                    |

| 6           | SDOUT  | 0    | Shutdown Output. When high, indicates output shutdown.                                                                                                                     |

| 7           | VDD    | _    | 5 V Supply.                                                                                                                                                                |

| 8           | CLK    | 0    | Recovered Clock. 1.544-MHz square-wave clock output.                                                                                                                       |

| 9           | PCM1   | 0    | Line Data Output 1. In conjunction with PCM2 (pin 14), provides dual-rail output.                                                                                          |

| 10          | LPCM1  | 1    | Loop Line Data 1. When high, input for data loopback mode is looped back to the input via LPCM1 and LPCM2 (pin 15).                                                        |

| 11          | SDCTRL | ı    | Shutdown Control. When tied to ASDCTRL (pin 18), turns off the clock and PCM outputs if there is a loss of incoming signal. This feature is disabled by tying SDCTRL high. |

| 12          | LCLK   | ı    | Loop Clock. Clock signal used in loopback mode.                                                                                                                            |

| 13          | LCTRL  | 1    | Loop Control. When low, inputs LPCM1 and LPCM2 are inverted and looped back to outputs PCM1 and PCM2.                                                                      |

| Table 1. Pin Descriptions (Continue | ed) | Continue | S | on | pt | scri | De | 2in | . F | e 1 | Tab |

|-------------------------------------|-----|----------|---|----|----|------|----|-----|-----|-----|-----|

|-------------------------------------|-----|----------|---|----|----|------|----|-----|-----|-----|-----|

| Pin | Symbol  | Туре | Name/Function                                                                                                                               |

|-----|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | PCM2    | 0    | Line Data Output 2. In conjunction with PCM1 (pin 9), provides dual-rail output.                                                            |

| 15  | LPCM2   | I    | Loop Line Data Input 2. When high, input for data loopback mode is looped back to the input via LPCM2 and LPCM1 (pin 10).                   |

| 16  | PCMIN1  | 1    | Line Data Input 1. Bipolar line data input from the digital line.                                                                           |

| 17  | PCMIN2  | 1    | Line Data Input 2. Bipolar line data input from the digital line.                                                                           |

| 18  | ASDCTRL | 0    | Automatic Shutdown Control. Active when tied to SDCTRL (pin 11). Turns off the clock and PCM outputs if there is a loss of incoming signal. |

| 19  | TO1     | _    | Connect to Pin 1.                                                                                                                           |

| 20  | NC      |      | No Connection.                                                                                                                              |

#### Operation

The primary functions of the 630AG Receive Converter (RCV) are to extract clock and PCM information from the incoming 1.544-MHz bipolar digital line and to regenerate unipolar clock and dual-rail PCM signals.

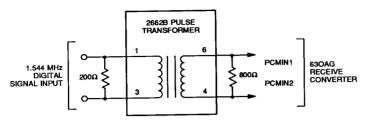

The incoming signal is applied to the RCV at PCMIN1 and PCMIN2. A transformer and resistor network is needed to provide the proper impedance match to the  $100-\Omega$  twisted-pair line (see Figure 3). The RCV converts this bipolar signal to a dual-rail, 100% duty cycle, TTL-compatible signal. The dual-rail output is required to detect bipolar violations. The nominal bipolar signal measured at pins 16 and 17 is 6 Vpp, with the minimum and maximum values at 2 Vpp and 12 Vpp, respectively.

The RCV contains a phase-locked loop (PLL) to extract the clock from the line signal. The extracted clock appears at CLK. The PLL free-running frequency is preadjusted to 1.544 MHz. In order for the RCV to lock onto the incoming signal, there must be a minimum density of at least one 1 every 16 bits (i.e., a maximum of fifteen 0s in a row).

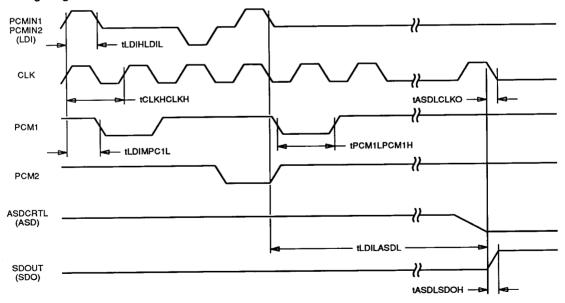

Timing for the dual rail signal is shown in Figure 4. If the incoming PCM bit is a 0, both rails are high. Incoming 1s are represented by a low pulse on one rail only, with the low pulse alternating between the two rails for successive incoming data bits that are equal to 1. Two successive low pulses on the same rail represents a bipolar violation. Data is accepted on the falling edge of the 1.544-MHz clock.

An automatic output shutdown mechanism is incorporated to turn off the clock and PCM outputs if there is a loss of incoming signal. This feature is enabled by tying SDCTRL to ASDCTRL and is disabled by tying SDCTRL high.

Approximately 400  $\mu$ s after the last 1 has been received, the voltage level on ASDCRTL is 0. If the automatic output shutdown mechanism is being used (SDCTRL tied to ASDCTRL), the clock stops and SDOUT goes high, indicating that a shutdown condition exists.

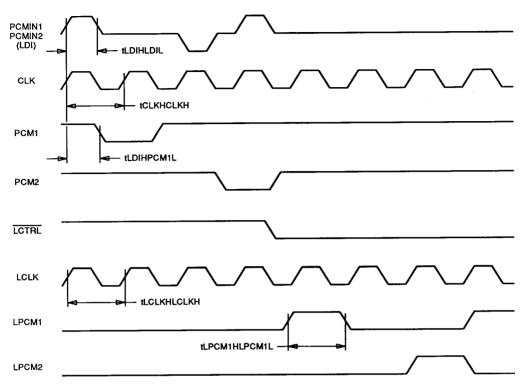

For maintenance purposes, a data loopback feature is provided. A low at the LCTRL input puts the 630AG in loopback mode. When the receive converter is in the loopback mode, the clock signal is taken from LCLK and is not extracted from the incoming data. The data entered via LPCM1 and LPCM2 is the inverse of the data output on PCM1 and PCM2. The automatic output shutdown feature is not available in the loopback mode.

Figure 3. Transformer and Resistor Network

### **Characteristics**

#### Clocks

Recovered clock: 1.544 MHz Loop clock: 1.544 MHz

## **Electrical Characteristics**

TA = 0 to 85 °C,  $VDD = 5 V \pm 0.5 V$ , GND = 0 V

| Parameter                      | Symbol     | Min      | Max        | Unit     |

|--------------------------------|------------|----------|------------|----------|

| Supply current                 | IDD        |          | 80         | mA       |

| Input current:<br>high<br>low  | liH<br>liL | _        | 40<br>–1.6 | μA<br>mA |

| Output current:<br>high<br>low | IOH<br>IOL | <u></u>  | -0.4<br>3  | mA<br>mA |

| Input voltage:<br>high<br>low  | VIH<br>VIL | 2.2      | VDD<br>0.8 | V        |

| Output voltage:<br>high<br>low | Voh<br>Vol | 2.4      | VDD<br>0.6 | V<br>V   |

| Power dissipation              | PD         | <u> </u> | 400        | mW       |

### **Maximum Ratings**

| Vallage range on any nin with respect to ground  |               |

|--------------------------------------------------|---------------|

| Voltage range off any pin with respect to ground | 0 to 85 °C    |

| Ambient operating temperature (TA) range         | _40 to +90 °C |

| Storage temperature (Tstg) range                 |               |

| Power dissination (PD)                           | 400 mW        |

Maximum ratings are the limiting conditions that can be applied under all variations of circuit and environmental conditions without the occurrence of permanent damage.

The external leads can be bonded or soldered safely at temperatures up to 300 °C.

# **Timing Characteristics and Requirements**

Table 2. Normal Mode I/O Format (See Figure 4)

| Symbol       | Description                 | Min | Тур | Max | Unit |  |  |  |

|--------------|-----------------------------|-----|-----|-----|------|--|--|--|

| Requirements |                             |     |     |     |      |  |  |  |

| tLDIHLDIL    | Line data input high        | 294 | 324 | 354 | ns   |  |  |  |

| tCLKHCLKH    | CLK period*                 | 647 | 647 | 648 | ns   |  |  |  |

|              | Characteristics             |     |     |     |      |  |  |  |

| tASDLCLKO    | ASDCTRL low to CLK off      |     | 0_  | _   | μS   |  |  |  |

| tLDIHPCM1L   | LDI high to PCM1 low        | _   | 324 | _   | ns   |  |  |  |

| tPCMPW       | PCM1 pulse width            | 647 | 647 | 648 | ns   |  |  |  |

| tASDLSDOH    | ASD low to SDOUT high       |     | 0   | _   | μS   |  |  |  |

| tLDILASDL    | Input data zero to ASDL low | _   | 400 |     | μS   |  |  |  |

<sup>\*</sup> This corresponds to a line frequency of 1.544 MHz  $\pm$  50 ppm.

Table 3. Loopback Mode I/O Format (See Figure 5)

| Symbol        | Description     | Min | Тур | Max | Unit |  |  |

|---------------|-----------------|-----|-----|-----|------|--|--|

| Requirements  |                 |     |     |     |      |  |  |

| tLCLKHLCLKH   | Loop CLK period | 647 | 647 | 648 | ns   |  |  |

| tLPCM1HLPCM1L | LPCM1 high      | 647 | 647 | 648 | ns   |  |  |

### **Timing Diagrams**

Figure 4. Normal Mode I/O Format

Figure 5. Loopback Mode I/O Format