## 67417

Serializing First-In First-Out (FIFO) 64 x 8/9 Memory

#### Features/Benefits

- High-speed 28-MHz serial shift-in/shift-out rate

- 10-MHz parallel shift-in/shift-out rate

- Three-state outputs with Hi-current drive

- · Cascadable at parallel port only

- Half-full flag (32 or more)

- Selectable 64x8 or 64x9 FIFO configuration thus providing "freme mark bit"

#### **Typical Applications**

- LAN equipment

- Data communication

- Office automation

- Microcomputers

- Minicomputers

- Disk/tape controllers

#### **Description**

The 67417 is a serializing/deserializing FIFO. This FIFO, the first one of its type in the industry, is organized 64 words x 8/9 bits wide. Like traditional Monolithic Memories' FIFOs it is cascadable, but only at the parallel port.

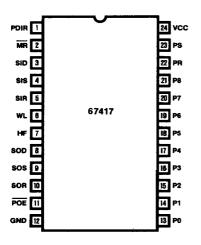

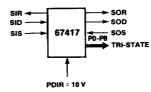

### **Pin Configuration**

#### **Ordering Information**

| Part<br>Number | Package | Temp | Description |  |

|----------------|---------|------|-------------|--|

| 67417          | CD 024  | Com  | 64x8/9      |  |

In addition, the device has the ability to connect directly to a system bus. These features make it a complete "sub-system on a chip."

The FIFO basically has three modes of operation;

- 1. Serial in to parallel out

- 2. Parallel in to serial out

- Serial in to serial out (requires non-standard logic level on PDIR).

In the first mode, serial data can be accepted at up to 28 MHz and the FIFO outputs parallel data at up to 10 MHz. Similarly, in the alternate mode parallel data can be transformed into serial data. Please refer to appendix for detailed description.

#### Pin Names

| P0-P8 | Parallel Data               |  |  |

|-------|-----------------------------|--|--|

| PS    | Parallel Shift In/Out       |  |  |

| PR    | Parallel Input/Output Ready |  |  |

| POE   | Parallel Output Enable      |  |  |

| SID   | Serial Input Data           |  |  |

| SIS   | Serial Input Shift          |  |  |

| SIR   | Serial Input Ready          |  |  |

| SOD   | Serial Output Data          |  |  |

| SOS   | Serial Output Shift         |  |  |

| SOR   | Serial Output Ready         |  |  |

| PDIR  | Parallel Port Direction     |  |  |

| WL    | Word Length                 |  |  |

| MR    | Master Reset                |  |  |

| HF    | Half Full Flag              |  |  |

| VCC   | VCC                         |  |  |

| GND   | Ground                      |  |  |

Publication # Rev. Amendment 67417 A /0 Issue Date: May 1988

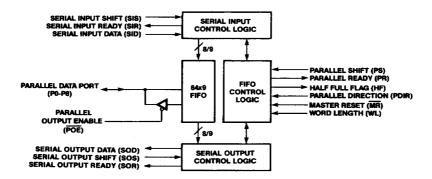

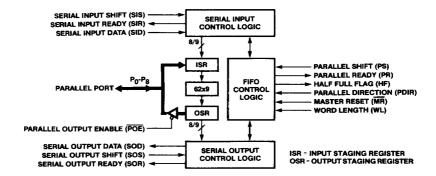

## **Block Diagram**

## **Absolute Maximum Ratings**

| Supply voltage V <sub>CC</sub> | 0.5 V to 7 V   |

|--------------------------------|----------------|

| Input voltage                  | 1.5 V to 7 V   |

| Off-state output voltage       | 0.5 V to 5.5 V |

| Storage temperature            | -65° to +150°C |

## **Operating Conditions**

| SYMBOL              | PARAMETER                                                     | FIGURE | COMMERCIAL |     |      | UNIT |

|---------------------|---------------------------------------------------------------|--------|------------|-----|------|------|

| STMBUL              | PARAMETER                                                     | FIGURE | MIN        | TYP | MAX  | UNI  |

| v <sub>CC</sub>     | Voltage                                                       |        | 4.75       | 5   | 5.25 | V    |

| T <sub>A</sub>      | Operating free-air temperature                                |        | 0          |     | 75   | °C   |

|                     | SERIAL INPUT PARAMETERS                                       |        |            | _   |      |      |

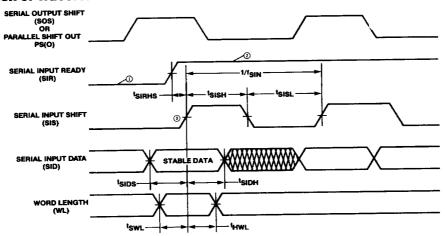

| fSIN                | Max. Serial Shift-In Rate                                     | 1      |            |     | 28   | MH   |

| tsish .             | Serial Shift-In HIGH time                                     | 1      | 23         |     |      | ns   |

| tsisl               | Serial Shift-In LOW time                                      | 1      | 12         |     |      | ns   |

| tSIDS               | Serial Input Data Setup time                                  | 1      | 14         |     |      | ns   |

| tSIDH               | Serial Input Data Hold time                                   | 1      | 0          |     |      | ns   |

| <sup>t</sup> SIRHS  | Recovery Time Serial Input Ready 1 to<br>Serial Input Shift 1 | 1      | 0          |     |      | ns   |

|                     | SERIAL OUTPUT PARAMETERS                                      |        |            |     |      |      |

| fsout               | Max. Serial Shift-Out Rate                                    | 1      |            |     | 28   | MH   |

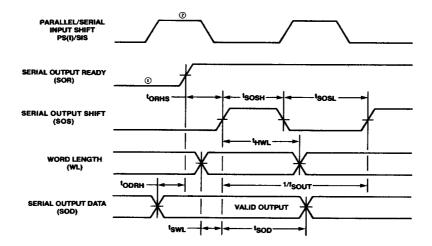

| tsosh               | Serial Shift-Out HIGH time                                    | 3      | 15         |     |      | ns   |

| tsosl               | Serial Shift-Out LOW time                                     | 3      | 15         | • . |      | ns   |

| <sup>t</sup> ORHS   | Recovery time Serial Output Ready † to Serial Output Shift †  | 3      | 5          |     |      | ns   |

|                     | WORD LENGTH PARAMETERS                                        |        |            |     |      |      |

| <sup>t</sup> swL    | Setup SIS, SOS                                                | 1,3    | 18         |     |      | ns   |

| <sup>t</sup> HWL    | Hold SIS, SOS                                                 | 1,3    | 3          |     |      | ns   |

|                     | PARALLEL PORT PARAMETERS                                      |        |            |     |      | 1    |

| fp                  | Parallel shift-in/shift-out rate                              | 8      |            |     | 10   | MHz  |

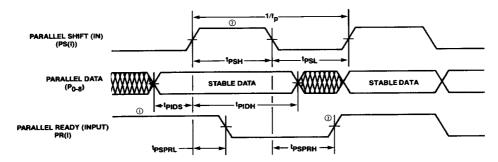

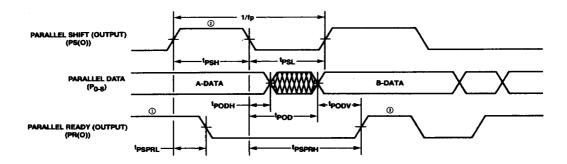

| <sup>t</sup> PSH    | Parallel Shift-In/Out HIGH time                               | 5/8    | 30         |     |      | ns   |

| t <sub>PSL</sub>    | Parallel Shift-In/Out LOW time                                | 5/8    | 30         |     |      | ns   |

| t <sub>PIDS</sub>   | Parallel Input Data Setup time                                | 5      | -5         |     |      | ns   |

| <sup>t</sup> PIDH   | Parallel Input Data hold time                                 | 5      | 35         |     |      | ns   |

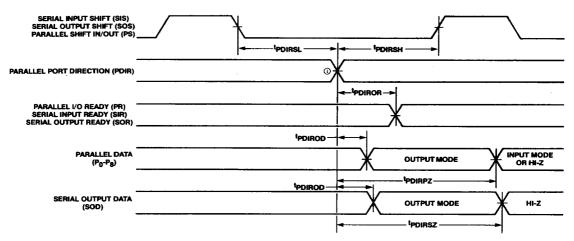

| <sup>t</sup> PDIRSL | Shift LOW to parallel direction transition                    | 14     | 50         |     |      | ns   |

| <sup>t</sup> PDIRSH | Parallel direction transition to Shift HIGH                   | 14     | 50         |     |      | ns   |

| <sup>t</sup> PRHS   | Parallel Ready † to Parallel Shift Low                        | 10/11  | 30         |     |      | ns   |

|                     | MASTER RESET PARAMETER                                        |        |            |     |      |      |

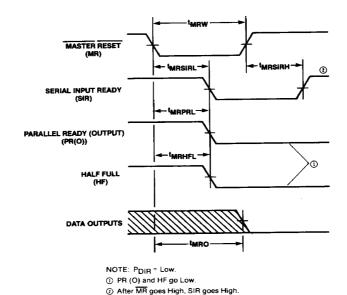

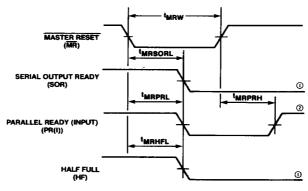

| <sup>t</sup> MRW    | Master Reset LOW time                                         | 12/13  | 40         |     |      | ns   |

**2-130** 67417

## Switching Characteristics Over Operating Conditions

|                     |                                                        |             |                           | UNIT |            |    |

|---------------------|--------------------------------------------------------|-------------|---------------------------|------|------------|----|

| SYMBOL              | PARAMETER                                              | FIGURE      | COMMERCIAL<br>MIN TYP MAX |      |            |    |

|                     | SERIAL INPUT PARAMETERS                                |             |                           |      |            |    |

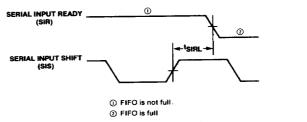

| tSIRL               | Serial Input Shift 1 to Serial Input Ready LOW         | 2           |                           |      | 23         | ns |

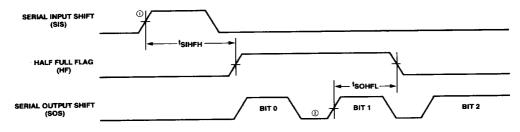

| tSIHFH              | Serial Input Shift ! to Half-Full Flag HIGH            | 7           |                           |      | 1.3        | μS |

|                     | SERIAL OUTPUT PARAMETERS                               |             |                           |      |            |    |

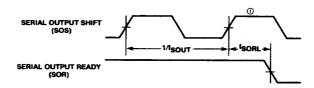

| tsorl .             | Serial Output Shift † to Serial Output Ready LOW       | 4           |                           |      | 23         | ns |

| tSOD                | Serial Output Shift † to Serial Output data            | 3           |                           |      | 23         | ns |

| <sup>t</sup> ODRH   | Serial Output Data valid to Serial Output Ready HIGH   | 3           | 0                         | 25   |            | ns |

| <sup>t</sup> SOHFL  | Serial Output Shift † to Half-Full LOW                 | 7           |                           |      | 1.3        | μS |

|                     | PARALLEL INPUT/OUTPUT PARAMETERS                       |             | -                         |      |            |    |

| t <sub>PSPRL</sub>  | Parallel Shift 1 to Parallel Ready LOW                 | 5/8         |                           |      | <b>6</b> 5 | ns |

| <sup>t</sup> PSPRH  | Parallel Shift I to Parallel Ready HIGH                | 5/8/10      |                           |      | 80         | ns |

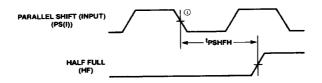

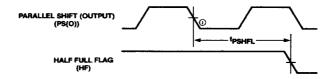

| <sup>t</sup> PSHFH  | Parallel Shift-In I to Half-Full HIGH                  | 6           |                           |      | 1.3        | μS |

| <sup>t</sup> PSHFL  | Parallel Shift-Out I to Half-Full LOW                  | 9           |                           |      | 1.3        | μS |

|                     | PARALLEL OUTPUT PARAMETERS                             |             |                           |      |            |    |

| <sup>t</sup> PODH   | H Minimum Parallel Shift ↓ to Ouput data               |             | 20                        |      |            | ns |

| t <sub>POD</sub>    | Maximum Parallel Shift I to Output data                | 8           |                           |      | 60         | ns |

| <sup>t</sup> PODV   | Minimum Output data valid to parallel ready HIGH       |             | 0                         | 15   |            | ns |

|                     | OTHER PARAMETERS                                       |             |                           |      |            |    |

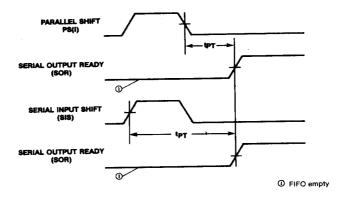

| t <sub>PT</sub>     | Fall-through time                                      | 10/11/16/17 |                           |      | 2.6        | μ8 |

| tIPH                | Parallel Input Ready pulse HIGH                        | 11          | 30                        |      |            | ns |

| <sup>t</sup> OPH    | Parallel Output Ready pulse HIGH                       | 10          | 30                        |      |            | ns |

| <sup>t</sup> MRO    | Master Reset ↓ to Data Out LOW                         | 12          |                           |      | 65         | ns |

| <sup>t</sup> MRSIRL | Master Reset ↓ to Serial Input Ready LOW               | 12          |                           |      | 40         | ns |

| <sup>t</sup> MRSIRH | Master Reset 1 to Serial Input Ready HIGH              | 12          |                           |      | 40         | ns |

| <sup>t</sup> MRPRL  | Master Reset ↓ to Parallel Ready LOW                   | 12/13       |                           |      | 40         | ns |

| <sup>t</sup> MRPRH  | Master Reset 1 to Parallel Ready HIGH                  | 13          |                           |      | 30         | ns |

| <sup>t</sup> MRSORL | Master Reset I to Serial Output Ready LOW              | 13          |                           |      | 40         | ns |

| <sup>t</sup> MRHFL  | Master Reset I to Half-Full LOW                        | 12/13       |                           |      | 60         | ns |

| <sup>t</sup> PDIROR | Parallel Direction change to new Output Ready          | 14          |                           |      | 60         | ns |

| <sup>t</sup> PDIROD | Parallel Direction change to Output data valid         | 14          |                           |      | 60         | ns |

| <sup>t</sup> PDIRPZ | Parallel Direction change to Parallel Output data Hi-Z | 14          |                           |      | 35         | ns |

| <sup>t</sup> PDIRSZ | Parallel Direction changes to Serial Output-data Hi-Z  | 14          |                           |      | 80         | ns |

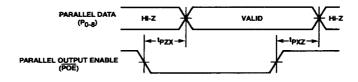

| <sup>t</sup> PZX    | Output enable time POE to P0-8                         | 15          |                           |      | 30         | ns |

| t <sub>PXZ</sub>    | Output disable time POE to P0-8                        | 15          |                           |      | 35         | ns |

## **Electrical Characteristics** Over Operating Conditions

| SYMBOL          | PARAMETER                              |                     | TEST CONDITIONS       |                            |                         |           | OM<br>YP MAX | UNIT |    |

|-----------------|----------------------------------------|---------------------|-----------------------|----------------------------|-------------------------|-----------|--------------|------|----|

| VIL             | Low-level input vo                     | ltage               |                       |                            |                         |           |              | 0.8† | ٧  |

| VIH             | High-level input vo                    | oltage              |                       |                            |                         |           | 2†           |      | ٧  |

| V <sub>IC</sub> | Input clamp voltag                     | je                  | V <sub>CC</sub> = MIN | I <sub>I</sub> = -18 mA    |                         |           |              | -1.5 | ٧  |

| IL.             | Low-level input cu                     | rrent               | V <sub>CC</sub> = MAX | V <sub>I</sub> = 0.4 V     |                         |           |              | -0.4 | mA |

| ΊΗ              | High-level input current               |                     | V <sub>CC</sub> = MAX | V <sub>I</sub> = 2.4 V     |                         |           |              | 0.1  | mA |

| l <sub>l</sub>  | Maximum input current                  |                     | V <sub>CC</sub> = MAX | V <sub>I</sub> = 5.5 V     |                         |           | 0.4          | mA   |    |

|                 | Voi Low-level output voltage           |                     |                       |                            | 1 24 mA                 | 0° C-75°C |              | 0.58 |    |

|                 |                                        |                     | V MINI                | Data Outputs<br>P0-P8, SOD | I <sub>OL</sub> ≖24 mA  | 25°C      |              | 0.55 | v  |

| VOL             | Low-level output                       | ever output voltage | V <sub>CC</sub> = MIN |                            | I <sub>OL</sub> = 16 mA | 0° C-75°C |              | 0.5  | *  |

|                 |                                        |                     |                       | All other outputs          | I <sub>OL</sub> =8 mA   |           |              | 0.5  |    |

| Vон             | High-level output voltage              |                     | V <sub>CC</sub> = MIN | I <sub>OH</sub> = -3 mA    |                         |           | 2.4          |      | ٧  |

| los             | Output short-circuit current*          |                     | V <sub>CC</sub> = MAX | V <sub>O</sub> = 0 V       |                         |           | -20          | -90  | mA |

| l <sub>LZ</sub> | Off-state SOD output current* P0 to P8 |                     | V - 144V              | V <sub>O</sub> = 0.4 V     |                         |           |              | -100 | μА |

| <sup>I</sup> HZ |                                        |                     | V <sub>CC</sub> = MAX | V <sub>O</sub> = 2.4 V     |                         |           |              | 100  | mA |

| 'cc             | Supply current                         |                     | V <sub>CC</sub> = MAX | ×                          |                         |           |              | 350  | mA |

| o <sub>V</sub>  | PDIR non-standard over voltage         |                     | Serial-In, Sei        | rial-Out                   |                         |           | 10           | 16   | ٧  |

<sup>\*</sup> Not more than one output should be shorted at a time and duration of the short circuit not exceed one second.

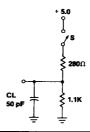

#### **Test Waveforms**

| TEST                | S = OPEN         | S = CLOSED          | OUTPUT WAVEFORM-MEAS-LEVEL                                 |

|---------------------|------------------|---------------------|------------------------------------------------------------|

| All t <sub>PD</sub> |                  | All t <sub>PD</sub> | V <sub>OH</sub> 1.5 V                                      |

| tPXZ                | <sup>t</sup> PHZ | <sup>t</sup> PLZ    | V <sub>OH</sub> 0.5 V 2.8 V<br>V <sub>OL</sub> 0.5 V 0.0 V |

| t <sub>PZX</sub>    | <sup>t</sup> PZH | <sup>t</sup> PZL    | 2.5 V V <sub>OH</sub>                                      |

**2-132** 67417

<sup>†</sup> This is an absolute voltage with respect to device GND (pin 12) and includes all overshoots due to test equipment.

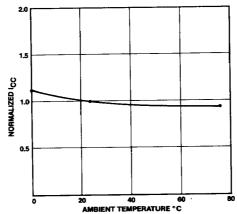

## **ICC VS Temperature**

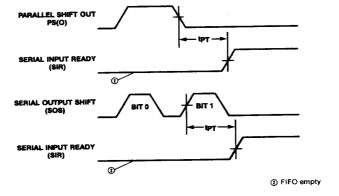

#### **Definition of Waveforms**

- ① FIFO is tult.

- 3 Shift-out (serial or parallel) is asserted, SIR goes High.

- $\ensuremath{\mathfrak{G}}$  SIS can be asserted t\_SIRHS after serial input ready changes from low-to-high.

Figure 1. Serial input Timing

Figure 2. FIFO Full Specification (ISIRL)

2-133

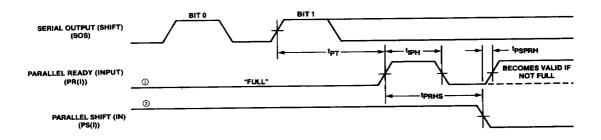

- ① FIFO is empty, output ready remains Low and shift-out cannot be applied.

- ① After a word is shifted in, output ready goes High and shift-out can be applied.

- 3 The first serial bit is P0.

Figure 3. Serial Output Timing

① After the last shift-out, output ready goes Low indicating FIFO is empty.

Figure 4. FIFO Empty Specifications (t<sub>SORL</sub>),

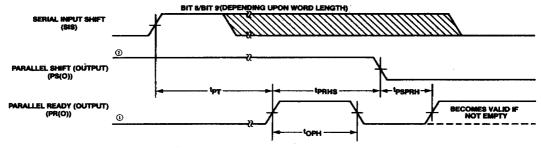

NOTE: PDIR = High for the mode parallel-in to serial-out. Parallel ready is an output flag from the FIFO indicating that a word can be loaded into the FIFO.

- ① FIFO is not full and ready for input.

- PS (In) is asserted, shifting in parallel data P0-8.

PR (In) goes Low indicating parallel port is in use and no longer ready.

PR (In) will remain Low as long as PS (In) remains High.

- PS (In) has gone Low, allowing recent word to propagate through FIFO, PR (In) returns High when ready for more input.

Figure 5. Parallel Input Shift Timing

for P<sub>DIR</sub> = High, the direction is parallel-in to serial-out. After the 32nd shift-in, the half-full flag is set to High, and remains High, indicating the presence of 32 or more words.

Figure 6. Half-full Flag Specifications on Parallel (tpshfh)

- When there are 31 words in the FIFO, the next shift-in on the 32nd word sets the half-full flag (HF) High indicating that there are 32 or more words.

- 3 As soon as one word is partially shifted out, HF goes Low indicating there are less than 32 words.

Figure 7. Half-full Flag Specification on Serial Operation (tSIHFH, tSOHFL)

NOTE: For above conditions  $P_{DIR} = Low$  indicating that the direction is from serial-in to parallel-out. Thus parallel ready indicates the output status.

- ① FIFO is not empty and at least one word is valid and ready at P0-8 outputs.

- ② PS (Out) is asserted, shifting out parallel data. Data remains valid, but:

- PR (Out) goes Low to indicate parallel port is in use and no longer ready.

- PR (Out) will remain Low as long as PS (Out) remains High.

- ① PS (Out) has gone Low, allowing data word to be shifted out. Next data word appears at output and PR (Out) is asserted to indicate valid data ready.

Figure 8. Serial-in to Parallel-out Specifications (tpOD, tpODH, tODV)

NOTE: For PDIR = Low the direction is serial-in to parallel-out.

① When a word is shifted out and the half-full flag goes Low, 31 words or less are in the FIFO.

Figure 9. Half-full Flag Specification on Parallel Shift-out (tpsHFL)

NOTE: PDIR = Low indicating serial-in to parallel-out.

- FIFO initially empty.

- ② PS (Out) held High.

Figure 10. tpSpRH, tpT, tpOH Specifications (Serial Input Mode)

NOTE: PDIR = High (parallel-in to serial-out).

- ① FIFO is full.

- ② PS (I) held High.

Figure 11. Fall-through Specifications

Figure 12. Master Reset Timing Serial-in to Parallel-out

NOTE: PDIR = High.

- ① SOR and HF go Low.

- ② Affter MR goes High, PR(I) goes High.

Figure 13. Master Reset Timing (Parallel-in to Serial-out)

NOTE: When the FIFO is used as a stack, change the port direction before the FIFO is full; otherwise, data may be lost.

Figure 14. PDIR Transition Parameters

Figure 15. Parallel Port Enable and Disable Timing

Figure 16. tpT Specification (Shift-in to Serial Output Ready)

Figure 17. 1pT Specification (Shift-in to Serial Input Ready)

# Appendix Detailed Functional/Description for 67417

The 67417 is a serializing FIFO intended as a one-chip solution for data buffering and serializing/deserializing. It can be successfully used for interfacing parallel-format computing equipment to serial-format data communications and mass-memory equipment. The 67417 is a word-oriented device. It is meant to function with complete 8- or 9-bit words of data.

#### **Parallel Port**

This is a fully bidirectional port, and it operates at a more conservative data rate of 10 MHz. The input-staging register (ISR) internally controls the parallel input data port bus signals. Likewise the OSR internally controls the parallel output data port. The ISR data outputs drive the parallel data inputs to the cell array, and the OSR inputs are likewise driven by the final parallel data stage of the cell array

Basically the major internal subsystems of the 67417 are:

- (i) The serial input port

- (ii) The serial output port

- (iii) The parallel port

- (iv) The FIFO control logic and

- (v) The cell array

## **Modes of Operation**

There are three modes in which the 67417 can operate

- (i) Parallel-in to serial-out

- (ii) Serial-in to parallel-out and

- (iii) Serial-in to serial-out.

67401/2

In the parallel-in to serial-out mode, PDIR = HIGH. Thus Parallel Shift (PS) acts as a Shift In (SI) and similarly, Parallel Ready (PR) as Input Ready (IR). The first bit shifted out of the serial port will be bit 0 of the parallel word input.

disabled (during Master Reset) and PDIR = Low. The parallel port is controlled by Parallel Shift (PS) input and Parallel Direc-

tion Input (PDIR). Parallel Ready (PR) is the handshake/status

output. At the Parallel Port PS and PR do accomplish a hand-

shake with the outside world as SI, IR, SO and OR on the

Similarly for serial-in to parallel-out mode, PDIR = LOW, and Parallel Shift (PS) acts as a Shift Out(SO) and Parallel Ready (PR) as Output Ready (OR). The first bit shifted into the serial port will be bit 0 of the parallel word output.

If the direction mode for a particular application of the 67417 is not intended to change during system operation, the PDIR input should be strapped to a logic LOW or HGH.

In the serial-in to serial-out mode, PDIR = 10 V minimum.

The parallel port does not function during this mode and is three-stated. The direction operating mode should not be changed if the FIFO is FULL otherwise stored data will be lost.

#### **Cell Array**

The 67417 cell array can function either as a 64x8 FIFO (with the 9th bit padded to a zero) or as a 64x9 FIFO, according to the setting of the word length (WL) control input. Like the PDIR

#### **Serial Port**

The two serial ports (input and output) are entirely separate which allows a high-speed data rate of 28 MHz. These serial ports do not share data pins, control pins, or internal circuits. However, since the serial output data is a three-state output, the serial data ports could be connected together in the normal serial-parallel operation mode with separate SOR and SIR status signals.

The serial input port interface consists of the Serial Input Ready (SIR) output, Serial Input Data (SID) input, and the Serial Input Shift (SIS) clock input. Unlike the analogous SI and IR signals on the 67401/2, SIS and SIR do not accomplish a "handshake" with the rest of the logic of the system which incorporates the 67417; rather SIR is asserted whenever the 67417 is still capable of receiving at least one more bit. SIS is a positive edge-triggered input which sequences the serial input control logic. This logic in turn controls SIR and the 8/9-bit Input Staging Register (ISR).

The serial output port interface is the dual of the above, with a Serial Output Data (SOD) output, a Serial Output Shift (SOS) clock input, and a Serial Output Ready (SOR) status output. SOR is asserted whenever at least one more bit is available at the output. SOS is a positive edge-triggered input which sequences the 8/9-bit Output Staging Register (OSR). Serial Output Data is automatically three-stated whenever the serial output port is

control input, WL can be switched at electronic speeds during system operations; but if the word length of a particular 67417 is never to change during system operation, WL for that part can be strapped to ground or  $V_{CC}$ .

It is a permissible 67417 mode of operation to almost fill the FIFO (there should be at least two empty locations) with WL set to 8-bit operation, then switch WL to 9-bit operation (WL = HIGH) to load one more word plus a frame marker in the last bit, and then switch PDIR and unload the 67417 in a 9-bit mode. This sequence of operations has the effect of providing a "frame marker bit" in the ninth bit of the last word loaded. The corresponding 9th bits will have been zeroed by the 67417 internal logic for all the other words in the frame since they were loaded while the 67417 was operating as an 8-bit device.

It is, however, the system designer's responsibility to avoid changing PDIR inputs when only part of an 8- or 9-bit word has been received or transmitted. In general, if such a change occurs, the part in general will try to add zero bits to pad out the impacted word to assume full length.

### Half-Full Flag

This status output indicates when the 67417 statically contains 32 words or more. This provides an indication to send in more data if the device is operated in a mostly-empty mode or send out more data if the 67417 is operated in a mostly-full mode.

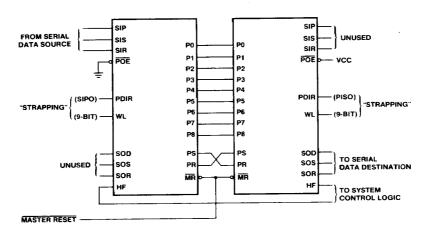

#### Cascading

The 67417 is designed to be cascaded at the parallel port only, due to very high data transfer rates at the serial ports. Cascading two 67417's is accomplished by connecting Parallel Input/Output Ready (PR) of each part to control the Parallel Shift In/Out (PS) of the other part, with one FIFO in serial-in to parallel-out mode, and the other FIFO in parallel-in to serial-out mode. The combined effect of this is a reversible 128x8 or 128x9 serial-in serial-out FIFO. The 67417 can not be cascaded at the serial ports because SIR and SOR are not acknowledged signals but rather status signals only.

#### **Applications**

NOTE: It can shift in data serially in the multiples of 8- or 9-bit according to WL.

Figure 18, 512/576x1 Serial-in to Serial-out Mode

- \* SIPO = Serial-in to Parallel-out.

- \* PISO = Parallel-in to Serial-out

Figure 19. Cascading of Two 'S417s for Serial-in to Serial-out Operation as a 128x9 (1152x1) FIFO

67417 2-141

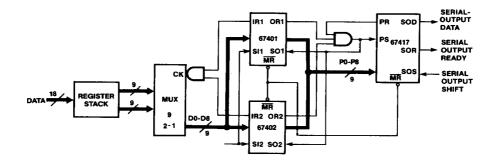

Figure 20. An Example of an Expansion Scheme for a 64x18 Parallel-to-Serial FIFO

An 18-bit data word is multiplexed into the two 67401/2 FIFOs. Since the 67417 FIFO is cascadable at the parallel port only, two

67401/2 FIFOs were used along with the 67417 to obtain the appropriate organization.

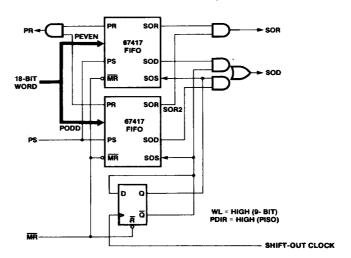

Figure 21. Another Example of an Expansion Scheme for a 64x18 Parallel-in to Serial-out FIFO Two 67417 FIFOs Are Used to Implement a 64x18 Parallel-in to Serial-out FIFO

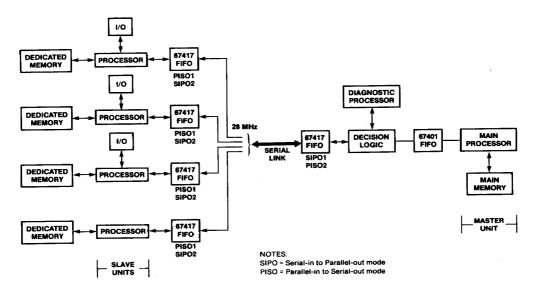

Figure 22. A Multiprocessing System

Each processor unit on the left has its own communication interface which consists of a serializing FIFO. The serial data link can operate in either direction 1 or direction 2 which is decided by the Decision logic. In direction 1 either of the slave units send the data to the master over the serial link, with its respective 67417 operating in parallel-in to serial-out mode (PISO1). While

the 67417 for the master unit operates in serial-in to parallel-out mode (SIPO1). The direction 2 has the FIFOs (67417) operating in the reverse direction from the above case. Decision logic determines the priority of the slave processors to use the serial link