# CGS64/74B2529 500 ps 2 to 10 Minimum Skew Clock Driver

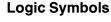

CLKO

CLK1

#### **General Description**

This minimum skew clock driver is designed for Clock Generation and Support (CGS) applications operating from 33 MHz to 80 MHz. The devices guarantee minimum output skew across the outputs of a given device.

Skew parameters are also provided as a means to measure duty cycle requirements as those found in high speed clocking systems. The '2529 is a minimum skew clock driver with two selectable inputs driving ten outputs.

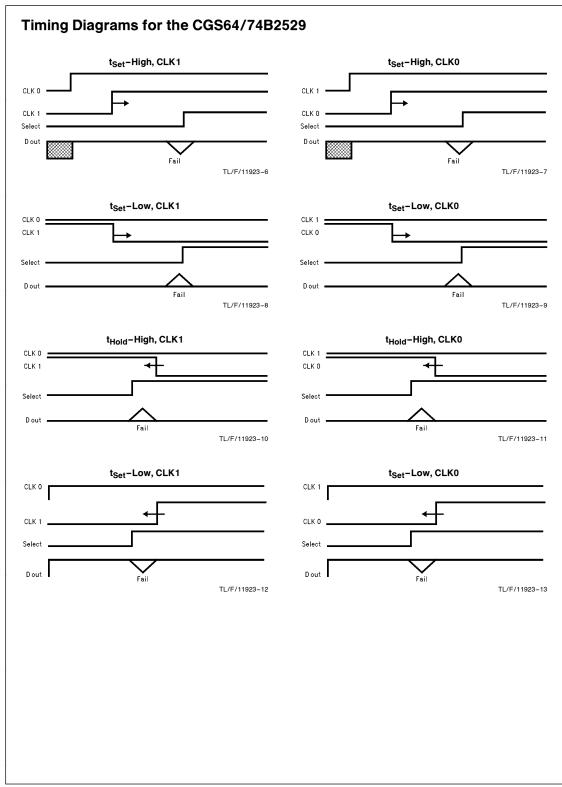

The SEL pin is used to determine which CLKn will have an active effect on the outputs of the circuit. When SEL = 1, the CLK1 input is selected and when SEL = 0, the CLK0 input is selected. The non-selected CLKn input will not have any effect on the logical output level of the circuit. The output pins act as a single entity and will follow the state of the CLK inputs.

#### **Features**

- Clock Generation and Support (CGS) devices

- Ideal for high frequency signal generation or clock distribution applications

- CGS74B version features National's Advanced Bipolar FAST® LSI process

- 2-to-10 low skew clock distribution

- 500 ps pin-to-pin output skew (V package)

- Specification for transition skew to meet duty cycle requirements

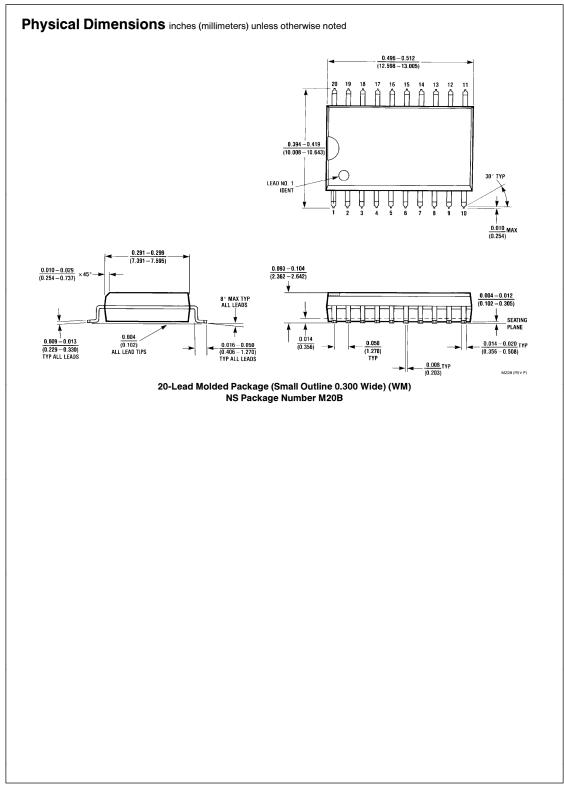

- $\blacksquare$  20-center pin V\_{CC} and GND configuration or PLCC to minimize high speed switching noise

- Current sourcing 48 mA and current sinking of 64 mA

- Low dynamic power consumption above 20 MHz

- Guaranteed 4 kV ESD protection

#### **Pin Description**

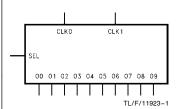

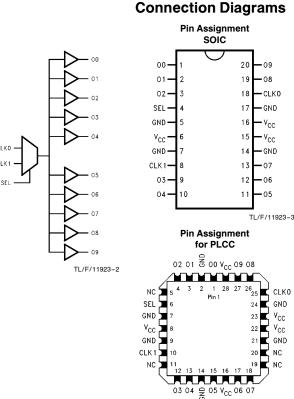

| Pin<br>Names | Description  |

|--------------|--------------|

| CLK0, CLK1   | Clock Input  |

| 00-09        | Outputs      |

| SEL          | Clock Select |

| Inputs |      |     | Outputs |

|--------|------|-----|---------|

| CLK0   | CLK1 | SEL | 00-09   |

| L      | Х    | L   | L       |

| н      | X    | L   | н       |

| Х      | L    | н   | L       |

| Х      | н    | н   | н       |

ogic Leve H = High Logic Level

X = Immateria

RRD-B30M106/Printed in U. S. A.

http://www.national.com

TL/F/11923-4

۷<sub>CC</sub>

Vcc

CGS64/74B2529 500 ps 2 to 10 Minimum Skew Clock Driver

September 1995

© 1996 National Semiconductor Corporation TL/F/11923

FAST® is a registered trademark of National Semiconductor Corporation

## Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage        | (V <sub>CC</sub> ) |    |          | 7.0V    |

|-----------------------|--------------------|----|----------|---------|

| Input Voltage (\      | /1)                |    |          | 7.0V    |

| Operating Tem         | perature           |    |          |         |

| 64 Grade              |                    |    | -40°C t  | o +85°C |

| 74 Grade              |                    |    | 0°C t    | o +70°C |

| Storage Tempe         | rature Range       |    | -65°C to | +150°C  |

| Typical $\theta_{JA}$ | Airflow            | М  | v        |         |

|                       | 0 LFM              | 89 | 64       | °C/W    |

|                       | 225 LFM            | 71 | 52       | °C/W    |

|                       | 500 LFM            | 63 | 45       | °C/W    |

# Recommended Operating Conditions

| Supply Voltage (V <sub>CC</sub> )                                              | 4.5V to 5.5V   |

|--------------------------------------------------------------------------------|----------------|

| Input Rise and Fall Times<br>(0.8V to 2.0V)                                    | 9.6 ns max     |

| Free Air Operating Temperature (T <sub>A</sub> )                               |                |

| 64 Grade                                                                       | -40°C to +85°C |

| 74 Grade                                                                       | 0°C to +70°C   |

| Note: The Absolule Maximum Ratings a<br>yond which the safety of the device ca |                |

yond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the DC and AC Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The Recommended Operating Conditions will define the conditions for actual device operation.

## **DC Electrical Characteristics**

Over recommended operating conditions unless specified otherwise. All typical values are measured at  $V_{CC}$  = 5V,  $T_A$  = 25°C

| Symbol          | Parameter                            | Cond                                                   | litions                | Min | Тур  | Max   | Units |

|-----------------|--------------------------------------|--------------------------------------------------------|------------------------|-----|------|-------|-------|

| V <sub>IK</sub> | Input Clamp Voltage                  | $V_{CC} = 4.5V, I_{I}$                                 | = -18 mA               |     |      | -1.2  | V     |

| $V_{\text{IH}}$ | Minimum Input<br>High Level Voltage  |                                                        |                        | 2.0 |      |       | v     |

| V <sub>IL</sub> | Maximum Input<br>Low Level Voltage   |                                                        |                        |     |      | 0.8   | v     |

| V <sub>OH</sub> | High Level Output Voltage            | $I_{OH} = -3 \text{ mA},$                              | $V_{CC} = 4.5V$        | 2.4 |      |       | v     |

|                 |                                      | I <sub>OH</sub> = 48 mA, V                             | / <sub>CC</sub> = 4.5V | 2.0 |      |       | v     |

| V <sub>OL</sub> | Low Level Output Voltage             | $V_{CC} = 4.5V, I_C$                                   | <sub>L</sub> = 64 mA   |     | 0.35 | 0.5   | V     |

| lj –            | Input Current @ Max<br>Input Voltage | $V_{CC} = 5.5V, V_{IH} = 7V$                           |                        |     |      | 0.1   | mA    |

| IIH             | High Level Input Current             | $V_{CC} = 5.5V, V_{IH} = 2.7V$                         |                        |     |      | 20    | μΑ    |

| IIL             | Low Level Input Current              | $V_{\text{CC}}=5.5\text{V}, V_{\text{IL}}=0.4\text{V}$ |                        |     | -0.5 | -0.75 | mA    |

| I <sub>O</sub>  | Output Drive Current                 | $V_{CC} = 5.5V, V_{O} = 2.25V$                         |                        | -50 |      | - 150 | mA    |

| ICC             | Supply Current                       | $V_{CC} = 5.5V$                                        | Outputs High           |     | 24   | 35    | mA    |

|                 | '2529                                |                                                        | Outputs Low            |     | 45   | 65    | mA    |

| C <sub>IN</sub> | Input Capacitance                    | $V_{CC} = 5.5V$                                        |                        |     | 5    |       | pF    |

| Symbol                                             | Parameter                                                                                                                                                                                                                                                                                                                                                               |                                              | V <sub>C</sub>                           | $V_{CC} = 4.5V \text{ to } 5.5V$ $C_L = 50 \text{ pF}$ $R_L = 500\Omega$ |                                             |                |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------|----------------|

|                                                    |                                                                                                                                                                                                                                                                                                                                                                         | Min                                          | Тур                                      | Max                                                                      |                                             |                |

| f <sub>MAX</sub>                                   | Frequency Maximum                                                                                                                                                                                                                                                                                                                                                       |                                              |                                          | 80                                                                       |                                             | MHz            |

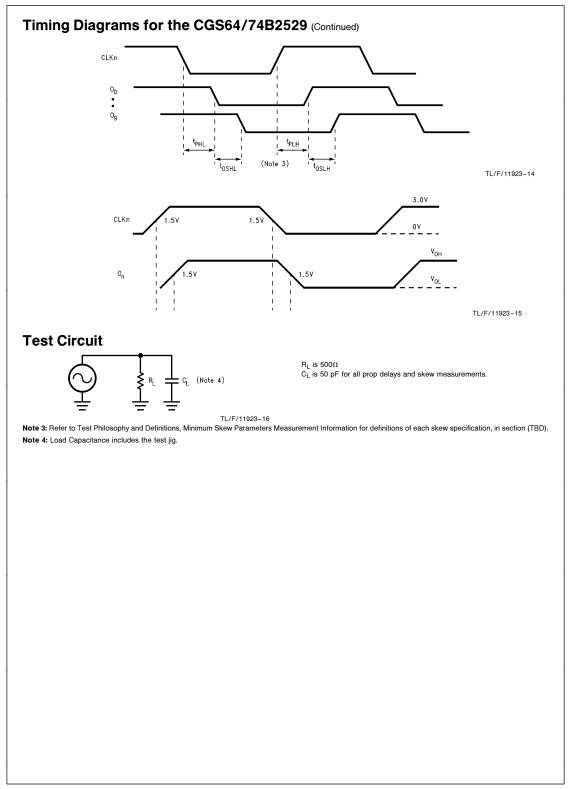

| t <sub>PLH</sub>                                   | Low-to-High Propagation Delay CLK0,1                                                                                                                                                                                                                                                                                                                                    | to O <sub>n</sub> M                          | 3.0                                      | 5.5                                                                      | 7.0                                         |                |

|                                                    | Low-to-High Propagation Delay CLK0,1                                                                                                                                                                                                                                                                                                                                    | to O <sub>n</sub> V                          | 2.5                                      | 5.5                                                                      | 6.0                                         | ns             |

| t <sub>PHL</sub>                                   | High-to-Low Propagation Delay CLK0,1                                                                                                                                                                                                                                                                                                                                    | High-to-Low Propagation Delay CLK0,1 to On M |                                          | 5.5                                                                      | 7.0                                         |                |

|                                                    | High-to-Low Propagation Delay CLK0,1                                                                                                                                                                                                                                                                                                                                    | to O <sub>n</sub> V                          | 2.5                                      | 5.5                                                                      | 6.0                                         | ns             |

| 0                                                  | Demonstern                                                                                                                                                                                                                                                                                                                                                              | Dealasas                                     |                                          | ; = 4.5V to <del>{</del><br>C <sub>L</sub> = 50 pF                       |                                             |                |

| Symbol                                             | Parameter                                                                                                                                                                                                                                                                                                                                                               | Package                                      |                                          | $C_L = 50 pF$<br>$R_L = 500\Omega$                                       |                                             | Units          |

| Symbol                                             | Parameter                                                                                                                                                                                                                                                                                                                                                               | Package                                      |                                          | C <sub>L</sub> = 50 pF                                                   |                                             | Units          |

| Symbol                                             | Parameter<br>Maximum Skew Common Edge<br>Output-to-Output Variation (Note 1)                                                                                                                                                                                                                                                                                            | Package<br>M<br>V                            |                                          | $C_L = 50 pF$<br>$R_L = 500\Omega$                                       | 1                                           | Units          |

|                                                    | Maximum Skew Common Edge                                                                                                                                                                                                                                                                                                                                                | M                                            |                                          | $C_L = 50 pF$<br>$R_L = 500\Omega$                                       | <b>Max</b><br>500                           | -              |

| toshl                                              | Maximum Skew Common Edge<br>Output-to-Output Variation (Note 1)<br>Maximum Skew Common Edge                                                                                                                                                                                                                                                                             | M<br>V<br>M                                  |                                          | $C_L = 50 pF$<br>$R_L = 500\Omega$                                       | Max<br>500<br>500<br>500                    | ps             |

| toshl<br>toslh                                     | Maximum Skew Common Edge<br>Output-to-Output Variation (Note 1)<br>Maximum Skew Common Edge<br>Output-to-Output Variation (Note 1)<br>Maximum Skew Pin                                                                                                                                                                                                                  | M<br>V<br>M<br>V<br>M                        |                                          | $C_L = 50 pF$<br>$R_L = 500\Omega$                                       | Max     500     500     500     500     750 | ps<br>ps       |

| toshl<br>toslh<br>tps<br>tset                      | Maximum Skew Common Edge<br>Output-to-Output Variation (Note 1)<br>Maximum Skew Common Edge<br>Output-to-Output Variation (Note 1)<br>Maximum Skew Pin<br>(Signal) Transition Variation (Note 1)<br>Setup Time High Select to CLK0 or 1                                                                                                                                 | M<br>V<br>M<br>V<br>M<br>V                   | Min<br>—                                 | $C_L = 50 pF$<br>$R_L = 500\Omega$                                       | Max     500     500     500     500     750 | ps<br>ps<br>ps |

| tOSHL<br>tOSLH<br>tPS<br>tSet<br>(Note 2)<br>tHold | Maximum Skew Common Edge<br>Output-to-Output Variation (Note 1)<br>Maximum Skew Common Edge<br>Output-to-Output Variation (Note 1)<br>Maximum Skew Pin<br>(Signal) Transition Variation (Note 1)<br>Setup Time High Select to CLK0 or 1<br>Setup Time High Select to CLK0 or 1<br>Hold Time High Sel to CLK0<br>Hold Time High Sel to CLK1<br>Hold Time Low Sel to CLK0 | M<br>V<br>M<br>V<br>M<br>V                   | Min<br>-2.0<br>-2.0<br>5.0<br>5.0<br>8.0 | $C_L = 50 pF$<br>$R_L = 500\Omega$                                       | Max     500     500     500     500     750 | ps<br>ps<br>ns |

Note 1:  $t_{OSHL}$  and  $t_{OSLH}$  are characterized and guaranteed by design @1 MHz.

Note 2: A negative setup time indicates that the correct logic levels may be initiated sometimes after the active transition of the timing pulse.

http://www.national.com

http://www.national.com

4

http://www.national.com

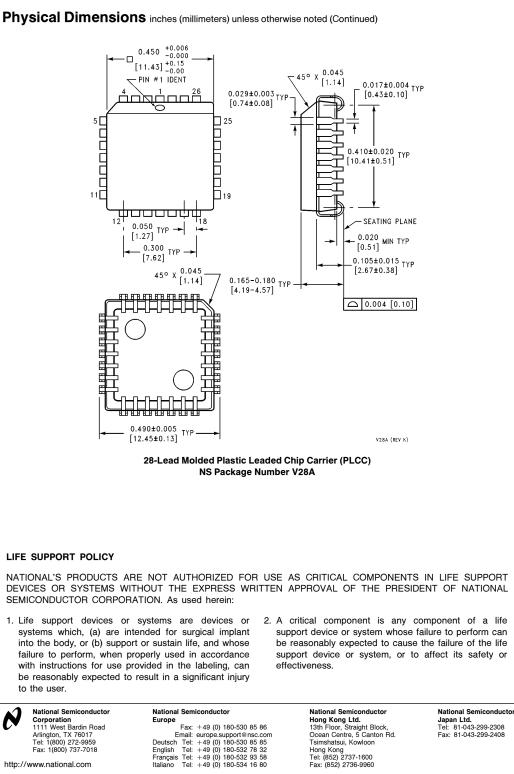

| Family Contact NSG   Family Clock Generation and Support   Operating Temperature Range 74   74 Commercial   54 Military/Aerospace   Technology B   B Biplolar | CMarketing for specifi | - Packaging<br>WM = JEDEC SOIC<br>V = PCC<br>DWF = Die Wafer Form<br>- Device Type<br>2528<br>2529 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------|

|                                                                                                                                                               |                        |                                                                                                    |

|                                                                                                                                                               |                        |                                                                                                    |

|                                                                                                                                                               |                        |                                                                                                    |

|                                                                                                                                                               |                        |                                                                                                    |

|                                                                                                                                                               |                        |                                                                                                    |

|                                                                                                                                                               |                        |                                                                                                    |

http://www.national.com

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications