# 74F583 4-Bit BCD Adder

# **General Description**

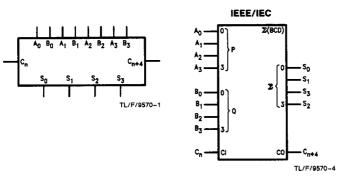

The 'F583 high-speed 4-bit, BCD full adder with internal carry lookahead accepts two 4-bit decimal numbers  $(A_0-A_3,\,B_0-B_3)$  and a Carry Input  $(C_n).$  It generates the decimal sum outputs  $(S_0-S_3),\,$  and a Carry Output  $(C_{n+4})$  if the sum is greater than 9. The 'F583 is the functional equivalent of the 82S83.

#### **Features**

- Adds two decimal numbers

- Full internal lookahead

- Fast ripple carry for economical expansion

- Sum output delay time 16.5 ns max

Ripple carry delay time 8.5 ns max

- Input to ripple delay time 8.5 ns max

Input to ripple delay time 14.0 ns max

- Supply current 60 mA max

- Available in SOIC, (300 mil only)

## Ordering Code: See Section 11

| Commercial | Package Number | Package Description                               |

|------------|----------------|---------------------------------------------------|

| 74F583PC   | N16E           | 16-Lead (0.300" Wide) Molded Dual-In-Line         |

| 74F583SC   | M16A           | 16-Lead (0.150" Wide) Molded Small Outline, JEDEC |

# **Logic Symbols**

# Connection Diagram

Pin Assignment for

#### Unit Loading/Fan Out: See Section 2 for U.L. Definitions

|                                |                  | 74F              |                                                                                   |  |  |

|--------------------------------|------------------|------------------|-----------------------------------------------------------------------------------|--|--|

| Pin Names                      | Description      | U.L.<br>HIGH/LOW | Input I <sub>IH</sub> /I <sub>IL</sub><br>Output I <sub>OH</sub> /I <sub>OL</sub> |  |  |

| A <sub>0</sub> -A <sub>3</sub> | A Operand inputs | 1.0/2.0          | 20 μA/-1.2 mA                                                                     |  |  |

| B <sub>0</sub> -B <sub>3</sub> | B Operand Inputs | 1.0/2.0          | 20 μA/ – 1.2 mA                                                                   |  |  |

| C <sub>n</sub>                 | Carry input      | 1.0/1.0          | 20 μA/ – 0.6 mA                                                                   |  |  |

| S <sub>0</sub> -S <sub>3</sub> | Sum Outputs      | 50/33.3          | -1 mA/20 mA                                                                       |  |  |

| Cn+4                           | Carry Output     | 50/33.3          | -1 mA/20 mA                                                                       |  |  |

7-439

## **Functional Description**

The 'F583 4-bit binary coded (BCD) full adder performs the addition of two decimal numbers (A<sub>0</sub>-A<sub>3</sub>, B<sub>0</sub>-B<sub>3</sub>). The look-ahead generates the BCD carry terms internally, allowing the 'F583 to then do BCD addition correctly. For BCD numbers 0 through 9 at A and B inputs, the BCD sum forms at the output. In the addition of two BCD numbers totalling a number greater than 9, a valid BCD number and a carry will result

For input values larger than 9, the number is converted from binary to BCD. Binary to BCD conversion occurs by grounding one set of inputs,  $A_n$  or  $B_n$ , and applying any 4-bit binary number to the other set of inputs. If the input is between 0 and 9, a BCD number occurs at the output. If the binary input falls between 10 and 15, a carry term is generated. Both the carry term and the sum are the BCD equivalent of the binary input. Converting binary numbers greater than 16 may be achieved through cascading 'F583s.

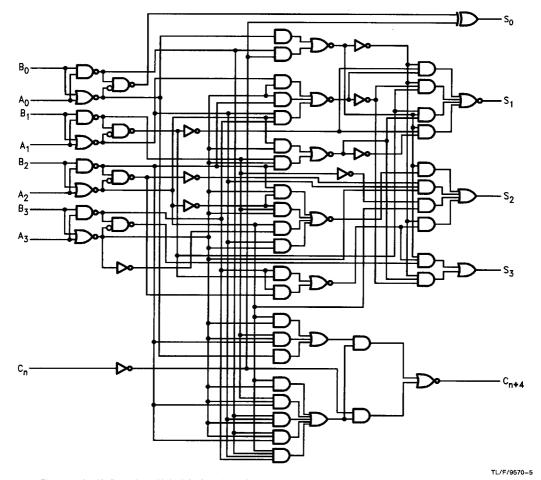

# **Logic Diagram**

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

#### **Absolute Maximum Ratings** (Note 1)

Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$

Ambient Temperature under Bias -55°C to +125°C

Junction Temperature under Bias -55°C to +175°C

Plastic -55°C to +150°C

V<sub>CC</sub> Pin Potential to

Ground Pin -0.5V to +7.0V Input Voltage (Note 2) -0.5V to +7.0V

Input Current (Note 2) -30 mA to +5.0 mA

Voltage Applied to Output

in HIGH State (with  $V_{CC} = 0V$ )

Standard Output

−0.5V to V<sub>CC</sub>

TRI-STATE® Output

−0.5V to +5.5V

Current Applied to Output

in LOW State (Max) twice the rated I<sub>OL</sub> (mA)

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

# Recommended Operating Conditions

Free Air Ambient Temperature

Commercial 0°C to +70°C

Supply Voltage Commercial

+ 4.5V to + 5.5V

#### **DC Electrical Characteristics**

|                  | Parameter                                                             | 74F        |     |              | Units  | Vcc | Conditions                                           |  |

|------------------|-----------------------------------------------------------------------|------------|-----|--------------|--------|-----|------------------------------------------------------|--|

| Symbol           | Parameter                                                             | Min        | Тур | Max          | Oilles | •66 | Oonariono                                            |  |

| V <sub>IH</sub>  | Input HIGH Voltage                                                    | 2.0        |     |              | ٧      |     | Recognized as a HIGH Signal                          |  |

| V <sub>IL</sub>  | Input LOW Voltage                                                     |            |     | 8.0          | ٧      |     | Recognized as a LOW Signal                           |  |

| V <sub>CD</sub>  | Input Clamp Diode Voltage                                             |            |     | -1.2         | V      | Min | $I_{\text{IN}} = -18 \text{ mA}$                     |  |

| V <sub>OH</sub>  | Output HIGH 74F 10% V <sub>CC</sub><br>Voltage 74F 5% V <sub>CC</sub> | 2.5<br>2.7 |     |              | ٧      | Min | $l_{OH} = -1 \text{ mA}$<br>$l_{OH} = -1 \text{ mA}$ |  |

| V <sub>OL</sub>  | Output LOW 74F 10% V <sub>CC</sub><br>Voltage                         |            |     | 0.5          | V      | Min | I <sub>OL</sub> = 20 mA                              |  |

| łн               | Input HIGH Current                                                    |            |     | 20           | μΑ     | Max | V <sub>IN</sub> = 2.7V                               |  |

| I <sub>BVI</sub> | Input HIGH Current<br>Breakdown Test                                  |            |     | 100          | μΑ     | Max | V <sub>IN</sub> = 7.0V                               |  |

| IIL              | Input LOW Current                                                     |            |     | -0.6<br>-1.2 | mA     | Max | $V_{1N} = 0.5V (C_n)$<br>$V_{1N} = 0.5V (A_n, B_n)$  |  |

| los              | Output Short-Circuit Current                                          | -60        |     | - 150        | mA     | Max | V <sub>OUT</sub> = 0V                                |  |

| I <sub>CEX</sub> | Output HIGH Leakage Current                                           |            |     | 250          | μΑ     | Max | V <sub>OUT</sub> = V <sub>CC</sub>                   |  |

| ICCL             | Power Supply Current                                                  |            | 40  | 60           | mA     | Max | $V_O = LOW$                                          |  |

| Symbol           | Parameter                                          | 74F  T <sub>A</sub> = +25°C  V <sub>CC</sub> = +5.0V  C <sub>L</sub> = 50 pF |                   |      | 74F  T <sub>A</sub> , V <sub>CC</sub> = Com C <sub>L</sub> = 50 pF |      | Units | Fig.<br>No. |

|------------------|----------------------------------------------------|------------------------------------------------------------------------------|-------------------|------|--------------------------------------------------------------------|------|-------|-------------|

|                  |                                                    |                                                                              |                   |      |                                                                    |      |       |             |

|                  |                                                    | t <sub>PLH</sub>                                                             | Propagation Delay | 2.5  | 13.0                                                               | 16.5 | 2.5   | 17.5        |

| t <sub>PHL</sub> | A <sub>n</sub> or B <sub>n</sub> to S <sub>n</sub> | 2.5                                                                          | 11.0              | 14.0 | 2.5                                                                | 15.0 |       |             |

| t <sub>PLH</sub> | Propagation Delay                                  | 2.5                                                                          | 6.5               | 8.5  | 2.5                                                                | 9.5  | ns    | 2-3         |

| t <sub>PHL</sub> | C <sub>n</sub> to C <sub>n+4</sub>                 | 2.5                                                                          | 5.0               | 6.5  | 2.5                                                                | 7.5  |       |             |

| tpLH             | Propagation Delay                                  | 4.0                                                                          | 11.0              | 14.0 | 4.0                                                                | 15.0 |       | 2-3         |

| t <sub>PHL</sub> | An or Bn to Cn + 4                                 | 4.0                                                                          | 8.0               | 10.5 | 4.0                                                                | 11.5 | ns    |             |