20 STERN AVE. SPRINGFIELD, NEW JERSEY 07081 U.S.A.

TELEPHONE: (973) 376-2922

(212) 227-6005

FAX: (973) 376-8960

## **Silicon Controlled Switch**

The General Electric Type 3N86 is a PLANAR PNPN silicon controlled switch (SCS) offering outstanding circuit design flexibility by providing leads to all four semiconductor regions. Unique fabrication processes based on planar oxide passivation have resulted in high rehability and uniformity atlow cost. The SCS is thoroughly characterized at temperature extremes to permit worst case circuit design. The 3N86 can be considered an integrated PNP-NPN transistor pair in a positive feedback configuration. As such it offers fewer connections, fewer parts, lower cost and better characterization than is available from two separate transistors. Its characterization permits it to be used as an extremely sensitive SCR, as a complementary SCR, or as a "transistor" with "latching" capabilities. Type 3N86 is intended for applications requiring extremely low holding current, high triggering sensitivity at either gate and high

## FEATURES:

- Completely eliminates rate effect problems

- Dynamic and static breakover voltages are identical

- Extremely high triggering sensitivity at both gates

- Low holding current

- High turn-off gain

- Design parameters specified at worst-case temperatures Characterized for SCR and complementary SCR type applications

- Characterized as PNPN and also as transistor integrated pair

- All planar, completely oxide passivated

- Leads to all four semiconductor regions

## absolute maximum ratings (25°C) (unless otherwise specified)

| Voltage Anode to cathode forward and reverse Anode gate to anode reverse Cathode gate to cathode reverse                    | 65<br>65<br>5                           | volts<br>volts<br>volts | DIMENSIONS WITHIN<br>JEDEC OUTLINE TO-18<br>EXCEPT FOR<br>LEAD CONFIGURATION                                                 | .230<br>.209<br>             |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Total Current Continuous DC forward <sup>(2)</sup> Peak recurrent forward $(T_A = 100^{\circ}\text{C}, 100 \mu\text{sec.})$ | 200                                     | ma                      | NOTE 1: Lead diameter is controlled in the zone between .050 and .250 from the seating plane. Between .250 and end of lead a | .030<br>MAX                  |

| pulse width, 1% duty cycle)                                                                                                 | 1.0                                     | amps                    | max. of .021 is held.                                                                                                        | 1) 11 77 4                   |

| Peak non-recurrent forward (10 µsec. pulse width)                                                                           | 5.0                                     | amps                    | NOTE 2: Leads having maximum diameter<br>(.019) measured in gaging plane .054 + .001                                         |                              |

| Gate Current (Forward Bias)                                                                                                 | • • • • • • • • • • • • • • • • • • • • |                         | <ul> <li>.000 below the seating plane of the device<br/>shall be within .007 of true position rela-</li> </ul>               | معدا الالا                   |

| Continuous DC anode gate <sup>(2)</sup>                                                                                     | 100                                     | ma                      | tive to a maximum width tab.                                                                                                 | n n n \ www                  |

| Peak anode gate ( $T_A = 100^{\circ}$ C, 100 $\mu$ sec.                                                                     | 200                                     | ma                      | NOTE 3: Measured from mex. diameter of<br>the actual device.  PNP EMITTER 9 4                                                | 100 SEATING PLANE            |

| Peak cathode gate ( $T_A = 100^{\circ}$ C, 100 $\mu$ sec. pulse width, 1% duty cycle Continuous DC cathode gate             | 500<br>20                               | ma<br>ma                | PNP BASE NPN COLLECTOR                                                                                                       | 4 LEADS<br>.017 1002         |

| Continuous DC cathode gate                                                                                                  | 20                                      | IIIa                    | NPN BASE                                                                                                                     | //\/\\ (NETE I)              |

| Dissipation Total power <sup>(2)</sup>                                                                                      | 400<br>100                              | mw                      | (A) 04 ANOXE                                                                                                                 | COMMECTED INTERNALLY TO DASE |

| Cathode gate power <sup>(2)</sup>                                                                                           | 100                                     | mw                      | (Ge) ( ) 3 ANODE GATE                                                                                                        |                              |

| Temperature Operating junction                                                                                              | -65 to +150                             | °C                      | GATE 2 (C) 61 CATHODE                                                                                                        | 048                          |

| Storage                                                                                                                     | -65  to  +200                           | °C                      | ALL DIMEN IN INCHES AND ARE<br>REFERENCE UNLESS TOLERANCED                                                                   | (NOTE 3) 45°                 |

NOTE 1: Symbols and nomenclature are defined below.

NOTE 2: Derate currents and power linearly to 150°C, the maximum rated temperature. The absolute maximum rating at any given temperature shall be in terms of the more conservative of the two parameters, i.e., current or power.

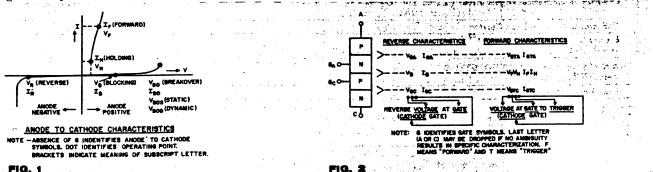

DEFINITION OF TERMS USED IN SCS SPECIFICATIONS

PNPN devices available at present do not have a common nomenclature. In part, this is due to their different construction and varied applications. SCS nomenclature permits the reverse characteristics of all three junctions to be specified. The anode forward characteristic and gate triggering characteristics can also be specified fully. The principles used in assigning symbols are illustrated below and with outline drawing above.

electrical characteristics.

3N86

1.0

20

μa max

μa max

μa max

μa max

μa max

μa max

V max

V max

V max

ma max

ma max

ma max

ma max

V max

V max

ua max

ua max

μa max

V max

V max

V min

V min

V max

V min

ma max

ma max

V max

V max

V min

V min

μs max

μs max

μs max

us max

pf

NPN1

Min. Max

65

5

20

75

₩<u>a</u>

IK

TURN ON TIME TEST SET

2N58

50Ω

CONNECT POWER SUPPLY

BEFORE INPUT PULSE

FIG. 4

3N86

μsec max

μsec max

2

0.9

20

20

20

15

V/μsec max

volts

volts

volts

volts

μ8.

$\mu$ 8

μ8.

рſ

mc

Temp.

@ 150°C

@ 25°C

Symbol<sup>(1)</sup>

IB max

3N86

CUTOFF CHARACTERISTICS

Forward Blocking Current

**Quality Semi-Conductors**

IN4148 DEVICE UNDER TEST

RECOVERY TEST SET