. : :

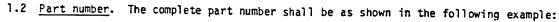

1.2.1 Device type. The device type shall identify the circuit function as follows:

| Device type | Generic number | Circuit                                |

|-------------|----------------|----------------------------------------|

| 01          | A0808          | 8 bit fixed instruction microprocessor |

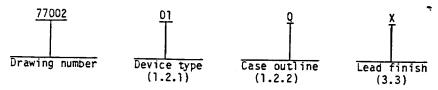

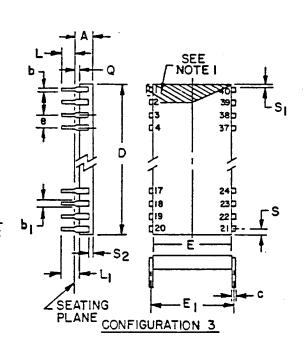

1.2.2 <u>Case outline</u>. The case outline shall be as shown in figure 2.

Outline letter

Q (40 Pin Ceramic dual-in-line pack)

1.3 Absolute maximum ratings.

| V <sub>CC</sub> Supply Voltage                                                                                                                    | WITH _                                                                                        |                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------|

| <b>V<sub>DD</sub></b> Supply Voltage                                                                                                              | RESPECT /                                                                                     |                 |

| V <sub>SS</sub> Supply Voltage                                                                                                                    | то {                                                                                          | -0.3 to +20 Vdc |

| Input and Output Voltage                                                                                                                          | ر ۱۹۳                                                                                         |                 |

| Storage Temperature Range<br>Power Dissipation<br>Lead Temperature (Soldering 5<br>Maximum Junction Temperature<br>Thermal Resistance Junction to | -65 to +150°C<br>1.7 W<br>270°C<br>T <sub>J</sub> = (150°C)<br>(\text{\theta}_{J-C} = 50°C/W) |                 |

|                                                                                                                                                   |                                                                                               | J-L             |

1.4 Recommended Operating Conditions

| Supply Voltage | V <sub>BB</sub><br>V <sub>CC</sub><br>V <sub>DD</sub> | -4.5 V to -5.5 V<br>+4.5 V to +5.5 V<br>+10.8 V to +13.2 V              |

|----------------|-------------------------------------------------------|-------------------------------------------------------------------------|

|                | Output voltage                                        | 0 Y 3.0 Y 8.5 V 0.8 V 3.7 V 0.45 V 0.5 MHz to 2.083 MHz -55° to + 125°C |

DEFENSE ELECTRONICS SUPPLY CENTER A 14933 77002

REV A PAGE 2

•

## 2. APPLICABLE DOCUMENTS

2.1 The following documents, of the issue in effect on date of invitation for bids or request for proposal, form a part of this drawing to the extent specified herein.

SPECIFICATION

**MILITARY**

MIL-M-38510 - Microcircuits, General Specification for.

STANDARD

**MILITARY**

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

(Copies of specifications, standards, drawings, and publications required by suppliers in connection with specific procurement functions should be obtained from the procuring activity or as directed by the contracting officer.)

- 3. REQUIREMENTS

- 3.1 Detail specifications. The individual item requirements shall be in accordance with MIL-M-38510, and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

- 3.2.1 <u>Design documentation</u>. The design documentation shall be in accordance with MIL-M-38510 and, unless otherwise specified in the contract or purchase order, shall be retained by the manufacturer but be available for review by the procuring activity or contractor upon request.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

- 3.2.3 Case outline. The case outline shall be in accordance with 1.2.2.

- 3.3 Lead material and finish. Lead material and finish shall be in accordance with MIL-M-38510.

- 3.4 Electrical performance characteristics. The electrical performance characteristics are as specified in table I and apply over the full recommended ambient operating temperature range, unless otherwise specified.

- 3.5 Marking. Marking shall be in accordance with MIL-M-38510 except the part number shall be in accordance with 1.2 herein. The M38510/XXX part number, and the "JAN" or "J" mark shall not be used.

- 3.6 <u>Product assurance requirements</u>. Microcircuits furnished under this drawing shall have been subjected to, and passed all the requirements, tests, and inspections detailed herein including screening, and quality conformance inspection requirements.

DEFENSE ELECTRONICS SUPPLY CENTER A 14933 77002

DAYTON, OHIO REV PAGE 3

Powered by ICminer.com Electronic-Library Service CopyRight 2003

|   | 1 |

|---|---|

| 1 | , |

| M                                                                                                               | Characterist      |                                                                                                                                                                                          | Device  | Lir     | nits |            |

|-----------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|------|------------|

| Test                                                                                                            | Symbol            | Conditions                                                                                                                                                                               | type    | Min     | Max  | Units      |

| High Level Output Voltage<br>All Outputs                                                                        | Vон               | $V_{DD}$ = +10.8 V<br>$I_{OH}$ = -150 $\mu$ A<br>$V_{BB}$ = -5.5 V, $V_{CC}$ = +4.5                                                                                                      | v 01    | 3.7     |      | Volts      |

| Low Level Output Voltage<br>All Outputs                                                                         | V <sub>OL</sub>   | $V_{DD}$ = +10.8 V<br>$I_{OL}$ = 1.9 mA<br>$V_{BB}$ = -5.5 V, $V_{CC}$ = 4.5 V                                                                                                           | 01      |         | 0.45 | Volts      |

| High Level High Impedance<br>Output Current<br>D <sub>O</sub> -D <sub>7</sub> , A <sub>O</sub> -A <sub>15</sub> | I <sub>ZH</sub> 1 | V <sub>O</sub> = +5.5 V<br>T <sub>A</sub> = +125°C, +25°C<br>V <sub>BB</sub> = -5.5 V, V <sub>CC</sub> = +5.5 V<br>V <sub>DD</sub> = +10.8 V                                             | 01      |         | 10   | μ <b>Α</b> |

| Low Level High Impedance<br>Output Current<br>D <sub>O</sub> -D <sub>7</sub> , A <sub>O</sub> -A <sub>15</sub>  | I <sub>ZL</sub> 1 | V <sub>O</sub> = 0.45 V<br>T <sub>A</sub> = +125°C, +25°C<br>V <sub>BB</sub> = -4.5 V, V <sub>CC</sub> = +5.5 V<br>V <sub>DD</sub> = 13.2 V                                              | 01      | -10     | -100 | μA         |

| High Level Input current;<br>For Clock Inputs, Reset,<br>Hold, Int, and Ready                                   | I IHI             | Logic Clock<br>V <sub>IN</sub> = 5.5 V 13.2 V<br>V <sub>BB</sub> = -5.5 V -5.5 V<br>V <sub>CC</sub> = +5.5 V +4.5 V<br>V <sub>DD</sub> = 10.8 V 13.2 V<br>T <sub>A</sub> = +125°C, +25°C | 01      |         | 10   | μ <b>Α</b> |

| Low Level Input Current:<br>For Clock Inputs, Reset,<br>Hold, Int, and Ready                                    | IILI              | V <sub>IN</sub> = 0 V<br>V <sub>BB</sub> = -4.5 V<br>V <sub>DD</sub> = +13.2 V<br>T <sub>A</sub> = +125°C, +25°C                                                                         | 01      |         | -10  | μΑ         |

| High Level Input Current;<br>Data Bus in input mode<br><sup>D</sup> O <sup>- D</sup> 7                          | I <sub>IH2</sub>  | V <sub>IN</sub> = 3.7 V<br>V <sub>BB</sub> = -4.5 V, V <sub>CC</sub> = +5.5 V<br>V <sub>DD</sub> = +13.2 V<br>T <sub>A</sub> = +125°C, +25°C                                             | 01      | 4       | -1.2 | mA         |

| Low Level Input Current;<br>Data Bus in input mode<br>00 - D7                                                   | I <sub>IL2</sub>  | V <sub>IN</sub> = 0 V<br>V <sub>BB</sub> = -4.5V, V <sub>CC</sub> = +5.5 V<br>V <sub>DD</sub> = +13.2 V<br>T <sub>A</sub> = +125°C, +25°C                                                | 01      | -10     | -100 | μΑ         |

| EFENSE ELECTRONICS SUPPLY DAYTON, OHIO                                                                          | CENTER            | SIZE CODE IDENT. NO. 14933                                                                                                                                                               | DWG NO. | • 77002 |      |            |

الاستان والأراب المعاولة المنافعة المنافعة والمنافعة وال

ගු

| 1 | Test                                                                                        | Q                 |                                                                                          | <u> </u>     | ****                            | Devic | e   | Lin           | nits |       |

|---|---------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------|--------------|---------------------------------|-------|-----|---------------|------|-------|

| l | rest                                                                                        | Symbol            |                                                                                          | Cond         | itions                          | type  |     | Min           | Max  | Units |

|   | High Level Input Current<br>Data Bus in Input Mode<br>D <sub>0</sub> D <sub>7</sub>         | IIH3              | $V_{BB} = -4.5$ $V_{DD} = 13.2$ $V_{IN} = 5.0$ $T_{A} = 125^{\circ}$                     | 2 V<br>V,    | V <sub>CC</sub> = +5.5 V        | 01    |     | -10           | -100 | MA    |

|   | Input High Threshold:<br>All Inputs Except Clock                                            | Y <sub>ІН</sub>   | V <sub>BB</sub> = -4.5<br>V <sub>CC</sub> = +4.5<br>V <sub>DD</sub> = 10.8               | 5γ,          | 5.5 Y                           | 01    |     | 3.0           |      | Volts |

|   | Input Low Threshold;<br>All Inputs Including Clocks                                         | YILI              |                                                                                          |              |                                 | 01    |     |               | 0.8  | Volts |

|   | Input High Threshold;<br>Clock Inputs                                                       | V <sub>IH2</sub>  |                                                                                          |              | ·                               | 01    |     | 8.5           |      | Volts |

|   | Negative 5 Y Power Supply<br>Current •                                                      | I <sub>BB</sub>   | f = 2.0 MH<br>V <sub>BB</sub> = -5.5<br>V <sub>CC</sub> = +5.5<br>V <sub>DD</sub> = +13. | 5 Y          |                                 | 01    |     | .01           | 1.0  | πA    |

| 1 | Positive 5 V Power Supply<br>Current                                                        | <sup>I</sup> cc   |                                                                                          |              | •                               | 01    |     | jo            | 100  | mÀ    |

|   | Positive 12 V Power Supply<br>Current                                                       | I <sub>DD</sub>   |                                                                                          |              |                                 | 01.   |     | 10            | 80   | mA    |

|   | Input Capacitance                                                                           | c <sub>i</sub>    | F = 1 MHz<br>From Input<br>other pins                                                    | pins         | T <sub>A</sub> = 25°C<br>to all | 01    |     | 17            | 25   | pF    |

|   | Input Capacitance Ready,<br>Hold, int, D <sub>O</sub> -D <sub>7</sub> , Reset               | ci                |                                                                                          |              | •                               | 01    |     | 6             | 10   | pF    |

|   | Output Capacitance A <sub>O</sub> -A <sub>15</sub> ,<br>Sync, DBIN, WAIT, WR, HLDA,<br>INTE | c <sub>o</sub>    |                                                                                          |              |                                 | 01    |     | 10            | 20   | pF    |

|   | Clock Pulse Width Ø1                                                                        | <sup>‡</sup> wн1  | V <sub>BB</sub> = -5V<br>V <sub>CC</sub> = +5V<br>V <sub>DD</sub> = +12                  | <u>+</u> 10% | 6                               | 01    |     | 60 -          |      | ns    |

|   | Clock Pulse Width Ø2                                                                        | t <sub>wH2</sub>  |                                                                                          |              |                                 | 01    |     | 220           |      | ns    |

|   | Delay Ø1 to Ø2 Leading Edges                                                                | t <sub>SLH7</sub> |                                                                                          |              |                                 | 01    |     | 80            |      | ns    |

|   | Delay Ø1 to Ø2                                                                              | T <sub>SLH6</sub> |                                                                                          |              |                                 | 01    | - 1 | 0             |      | ns    |

|   | Delay 02 to 01                                                                              | t <sub>SHL8</sub> |                                                                                          |              |                                 | 01    |     | 70            |      | ns    |

| - | DEFENSE ELECTRONICS SUPPLY<br>DAYTON, OHIO                                                  | CENTER            | SIZE (                                                                                   |              | IDENT. NO. D                    | WG NO | PA( | 77002<br>SE 5 |      |       |

USGOVERN

| TA                                                                                               | BLE I. E            | <u>lectrical Characteristics</u> - Con                                                                             |                | •          | **          | ·     |     |

|--------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------|----------------|------------|-------------|-------|-----|

| Test                                                                                             | Symbol              | Conditions                                                                                                         | Device<br>type | Lin<br>Min | nits<br>Max | Units |     |

| Ready Setup Time to Ø2                                                                           | · t <sub>SLH1</sub> | V <sub>BB</sub> = -5 V <u>+</u> 10%<br>V <sub>CC</sub> = +5 V <u>+</u> 10%<br>V <sub>DD</sub> = +12 V <u>+</u> 10% | 01             | 120        |             | ns    |     |

|                                                                                                  | t <sub>SHL1</sub>   | <b>–</b>                                                                                                           | 01             | 120        |             | ns    |     |

| Data Setup Time to Clock Øl                                                                      | t <sub>SLH2</sub>   | ·                                                                                                                  | 01             | 30         |             | ns    |     |

|                                                                                                  | t <sub>SHL2</sub>   |                                                                                                                    | 01             | 30         |             | ns    | į   |

| Data Setup Time to Clock Ø2                                                                      | t <sub>SLH3</sub>   |                                                                                                                    | 01             | 150        |             | ns    |     |

|                                                                                                  | t <sub>SHL3</sub>   |                                                                                                                    | 01             | 150        |             | ns    |     |

| INT Input Setup Time During                                                                      | t <sub>SLH4</sub>   |                                                                                                                    | 01             | 120        |             | ns    |     |

| Ø1 or Ø2. INT Not Yalid                                                                          | t <sub>SHL4</sub>   | •                                                                                                                  | 01             | 120        |             | ns    |     |

| Hold Input Setup Time to Ø2                                                                      | t <sub>SHL5</sub>   |                                                                                                                    | 01             | 140        |             | ns    | G   |

|                                                                                                  | t <sub>SLH5</sub>   |                                                                                                                    | 01             | 140        |             | ns    |     |

| Data Hold Time From Ø2                                                                           | t <sub>HHL2</sub>   |                                                                                                                    | 01             | 50         |             | ns    |     |

|                                                                                                  | t <sub>HLH2</sub>   |                                                                                                                    | 01             | 50         | ٠           | ns    |     |

| INT Input Hold Time During<br>Øl or Ø2, INT Valid                                                | t <sub>HHL1</sub>   |                                                                                                                    | 01             | 0          |             | ns    | 1   |

| prorps, in tarru                                                                                 | t <sub>HLH1</sub>   |                                                                                                                    | 01             | 0          |             | ns    |     |

| Clock Period                                                                                     | tcY                 |                                                                                                                    | 01             | 0.32       | 2.0         | 4S    |     |

| Data and Status Output<br>Delay from Ø2: D <sub>0</sub> -D <sub>7</sub><br>Data and Status Valid | t <sub>PLH1</sub>   | C = 50 pF all outputs<br>T <sub>A</sub> = +25°C                                                                    | 01             |            | 220         | ns    |     |

|                                                                                                  | t <sub>PHL1</sub>   |                                                                                                                    | 01             |            | 220         | ns    | .   |

|                                                                                                  | t <sub>pZH1</sub>   |                                                                                                                    | 01             |            | 220         | ns    | 1.  |

|                                                                                                  | t <sub>pZL1</sub>   |                                                                                                                    | 01             |            | 220         | ns    |     |

| Delay for Data Bus to Enter<br>Input Mode. D <sub>O</sub> -D <sub>7</sub>                        | t <sub>PHZ1</sub>   | $R_L = 2.2K\Omega$<br>$R = 25K\Omega$<br>C = 50  pF all outputs<br>$T_A = +25^{\circ}C$                            | 01             |            | 140         | ns    |     |

| •                                                                                                | <sup>t</sup> PLZ1   |                                                                                                                    | 01             |            | 140         | ns    |     |

| DEFENSE ELECTRONICS SUPPLY                                                                       | CENTER              | SIZE CODE IDENT. NO.                                                                                               | DWG NO.        | 77002      |             |       |     |

| DAYTON, DHIO                                                                                     |                     | REV A                                                                                                              | T              | GE 6       |             |       | 7 💟 |

| <b>M</b>                                                                                               |                   | 0                                                                                      | Device  | Lin        | nits     | Units     |

|--------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------|---------|------------|----------|-----------|

| Test                                                                                                   | Symbol            | Conditions                                                                             | type    | Min        | Max      | Units     |

| Delay to Float During Hold<br>From Ø2 A <sub>O</sub> -A <sub>l5</sub> : D <sub>O</sub> -D <sub>7</sub> | t <sub>PLZ2</sub> | $R_L = 2.2K\Omega$<br>$R = 25K\Omega$<br>C = 50 pF all outputs<br>$T_A = +25^{\circ}C$ | 01      | <b></b>    | 120      | ns        |

|                                                                                                        | t <sub>PHZ2</sub> | 1A = 123 C                                                                             | 10      |            | 120      | ns        |

| DBIN Output Delay From Ø2                                                                              | t <sub>PLH3</sub> |                                                                                        | 01      | 25         | 140      | ns        |

|                                                                                                        | t <sub>PHL3</sub> |                                                                                        | 01      | 25         | 140      | ns        |

| Delay to Float During Hold                                                                             | t <sub>PHZ3</sub> |                                                                                        | 01      | <u>1</u> / |          |           |

| From HLDA A <sub>0</sub> -A <sub>15</sub> , D <sub>0</sub> -D <sub>7</sub>                             | t <sub>PLZ3</sub> |                                                                                        | 01      | 1/         |          |           |

| SYNC, WR, WAIT, HLDA<br>Dutput Delay                                                                   | t <sub>PLH4</sub> |                                                                                        | 01      |            | 120      | ns        |

| output belay                                                                                           | t <sub>PHL4</sub> | •                                                                                      | 01      |            | 120      | ns<br>- > |

| Address and Data Delay to<br>Float During Hold From                                                    | t <sub>PHZ4</sub> |                                                                                        | 01      | <u>2</u> / |          | ns        |

| HR, A <sub>0</sub> -A <sub>15</sub> , D <sub>0</sub> -D <sub>7</sub>                                   | t <sub>PLZ4</sub> |                                                                                        |         | 2/         |          | ns        |

| INTE Output Delay from Ø2                                                                              | t <sub>PHL5</sub> |                                                                                        | 01      |            | 200      | ns        |

|                                                                                                        | t <sub>PLH5</sub> |                                                                                        | 01      |            | 200      | ns        |

| Address Valid after DBIN<br>During HLDA                                                                | t <sub>PHZ5</sub> |                                                                                        | 01      | -20        |          | ns        |

| or my mean                                                                                             | t <sub>PLZ5</sub> |                                                                                        | 01      | -20        |          | ns        |

| Address Output Delay from                                                                              | t <sub>PLH6</sub> | •                                                                                      | 01      |            | 200      | ns        |

| 32 Address Valid A <sub>0</sub> -A <sub>15</sub>                                                       | t <sub>PHL6</sub> |                                                                                        | 01      |            | 200      | ns        |

| Output Data Stable Prior                                                                               | t <sub>PLH7</sub> |                                                                                        | 01      | <u>3</u> / |          | ns        |

| to WR 1 D <sub>0</sub> -D <sub>7</sub>                                                                 | t <sub>PHL7</sub> | ·                                                                                      | 01      | <u>3</u> / |          | ns        |

| Address Stable Prior to WR                                                                             | t <sub>PLH8</sub> |                                                                                        | 01      | 4/ .       |          | ns        |

| <sup>1</sup> 0 <sup>-4</sup> 15                                                                        | t <sub>PHL8</sub> | ·                                                                                      | 01      | 4/         |          | ns        |

| Output Data, Address Stable rom WR (Not HLDA).                                                         | t <sub>PHL9</sub> |                                                                                        | 01      | <u>5</u> / |          | ns        |

| 00 <sup>-D</sup> 7, A0 <sup>-A</sup> 15                                                                | t <sub>PLH9</sub> |                                                                                        | 01      | <u>5</u> / |          | ns        |

| / See notes on page 8                                                                                  |                   |                                                                                        |         |            | <u> </u> |           |

| EFENSE ELECTRONICS SUPPLY                                                                              | CENTER            | SIZE CODE IDENT. NO.                                                                   | DWG NO. | 77002      |          |           |

| DAYTON, OHIO                                                                                           |                   | REV A                                                                                  | P       | AGE 7      |          |           |

## Table Notes:

The following equations determine the minimum limits for the noted Table I delay measurements.

$$\underline{I}$$

/  $t_{PHZ_2}$  and  $t_{PLZ_3} = t_{SLH_2} + t_{TLH_{22}} - 50 \text{ ns}$

$$\underline{2}$$

/  $t_{PHZ_A}$  and  $t_{PLZ_A} = t_{SLH_T} + t_{TLH_{A2}} - 10 \text{ ns}$

$$\frac{3}{t_{PHL_2}}$$

and  $t_{PLH_2} = t_{period,2324} - t_{SLH_2} - t_{TLH_2} - 170 \text{ ns}$

$$\frac{4}{t_{\text{PHL}_8}}$$

and  $t_{\text{PLH}_8} = 2t_{\text{period}}(\text{clock}) - t_{\text{SLH}_7} - t_{\text{TLH}_{\emptyset2}} - 140 \text{ ns}$

$\frac{5}{t_{\text{PHL}_9}}$  and  $t_{\text{PLH}_9} = t_{\text{SLH}_9} + t_{\text{TLH}_{\emptyset2}} + 10 \text{ ns}$

$$5/$$

$t_{PHL_0}$  and  $t_{PLH_0} = t_{SLH_0} + t_{TLH_{02}} + 10 \text{ ns}$

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO

CODE IDENT. NO. SIZE 14933 REV

DWG NO.

77002

PAGE

DESC FORM 144 A

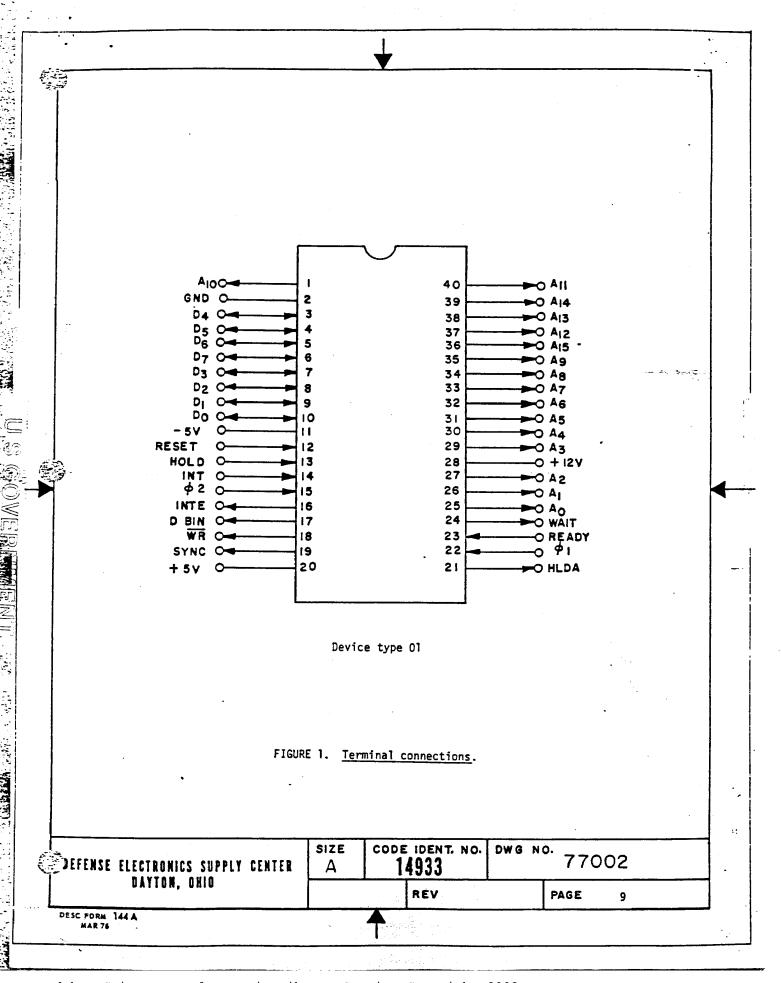

|                | ,    | <del> </del> |          |        |       |

|----------------|------|--------------|----------|--------|-------|

|                | INC  | HES          | MILLI    | METERS |       |

| SYMBOL         | MIN  | MAX          | MIN      | MAX    | NOTES |

| A              |      | .225         |          | 5.72   |       |

| b              | .014 | .023         | .36      | .58    | 8     |

| b <sub>1</sub> | .030 | .070         | .76      | 1.78   | 2,8   |

| С              | .008 | .015         | .20      | .38    | 8     |

| D              |      | 2.080        |          | 52.83  | 4     |

| Ε              | .510 | .615         | 12.95    | 15.52  | 4     |

| Ε <sub>1</sub> | .520 | .625         | 13.21    | 15.88  | 7     |

| E <sub>2</sub> | .280 |              | 7.11     |        |       |

| E <sub>3</sub> | .050 |              | 1.27     |        |       |

| е              | .100 | BSC          | 2.54 BSC |        | 5,9   |

| L              | .120 | .200         | 3.05     | 5.08   |       |

| L <sub>1</sub> | .150 |              | 3.81     |        |       |

| Q              | .020 | .060         | .51      | 1.52   | 3     |

| Q <sub>1</sub> | .020 |              | .51      |        |       |

| S              |      | .080         |          | 2.03   | 6     |

| s <sub>1</sub> | .005 |              | .13      |        | 6     |

| S <sub>2</sub> | .005 |              | .13      |        |       |

| α              | 0°   | 15°          | 0°       | 15°    |       |

## NOTES:

THE PARTY.

- Index area; a notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- The minimum limit for dimension b<sub>1</sub> may be .020 (.51 mm) for leads number 1, 20, 21, and 40 only.

- 3. Dimension Q shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-center lid, meniscus and glass overrun.

- 5. The basic pin spacing is .100 (2.54 mm) between centerlines. Each pin centerline shall be located within  $\pm .010$  (.25 mm) of its exact logitudinal position relative to pins 1 and 40.

- 6. Applies to all four corners (leads number 1, 20, 21, and 40), and 40.5 shall apply.

- 7. Lead center when  $\alpha$  is 0°. E<sub>1</sub> shall be measured at the centerline of the leads (see 40.4 of this appendix).

- All leads Increase maximum limit by .003 (.08 mm) measured at the center of the flat, when lead finish A is applied.

- Thirty eight spaces.

- If this configuration is used, no organic or polymeric materials shall be molded to the bottom of the package to cover the leads.

FIGURE 2. Case outline Q (40-lead, 5/16" x 2-1/16" dual-in-line pack) - Continued.

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO

SIZE CODE IDENT. NO. DWG NO.

14933

77002

REV A PAGE 11

- 3.6.1 <u>Screening</u>. Screening shall be in accordance with method 5004, class B, of MIL-STD-883 and 4.3 herein. The 100 percent final electrical screening for off the shelf devices shall consist of the normal 100 percent DC tests at 25°C with 10 percent PDA, high and low temperature DC tests, and 25°C AC tests followed by normal sampling and LTPD's at group A lot acceptance.

- 3.6.2 Quality conformance inspection. Quality conformance inspection shall be in accordance with MIL-M-38510 and 4.4 herein.

- 3.7 Manufacturer eligibility. To be eligible to supply microcircuits to this drawing, a manu-facturer must have manufacturer certification in accordance with MIL-M-38510 for at least one line. Any suppliers not listed on 6.6 herein shall submit Group A variables data on 22 devices in accordance with 4.4.1. This data is to be submitted to DESC-EQE.

- 4. PRODUCT ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with MIL-M-38510 and method 5005 of MIL-STD-883, except as modified herein.

- 4.2 Qualification inspection. Qualification inspection to this device type shall not be required.

- 4.3 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test (method 1015 of MIL-STD-883).

- (1) Test condition D or E, each circuit must be driven with an appropriate signal to simulate circuit applications and each circuit shall have maximum load applied.

- (2)  $T_A = 125$ °C minimum.

- b. Interim and final electrical test parameters shall be as specified in table II, except interim electrical parameters test prior to burn-in is optional at the discretion of the manufacturer.

- c. Percent defective allowable (PDA) The PDA is specified as 10 percent based on failures from group A, subgroup 1, test after cooldown as final electrical test in accordance with method 5004 of MIL-STD-883, and with no intervening electrical measurements. If interim electrical parameter tests are performed prior to burn-in, failures resulting from pre burn-in screening may be excluded from the PDA. If interim electrical parameter tests prior to burn-in are omitted, then all screening failures shall be included in the PDA. The verified failures of group A, subgroup 1, after burn-in divided by the total number of devices submitted for burn-in in that lot shall be used to determine the percent defective for the lot.

- 4.4 Quality conformance inspection. Quality conformance inspection shall be in accordance with MIL-M-38510. Groups A and B inspections shall be performed on each lot. Quality assurance shall keep lot records for 3 years (minimum), monitor for compliance to the prescribed procedures, and observe that satisfactory manufacturing conditions and records on lots are maintained for these devices. The records, including as a minimum an attributes summary of all screening and quality conformance inspections conducted on each lot, shall be available for review by the customer at all times.

- 4.4.1 Group A inspection. Group A inspection shall consist of the test subgroups and LTPD values shown in table 1 of method 5005 of MIL-STD-883 (class B) and as follows:

- .a. Tests shall be as specified in table II.

- b. Subgroups 4, 5, 6, and 8 of table I of method 5005 of MIL-STD-883 shall be omitted.

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO | SIZE | 14933 | DWG NO. 77002 |  |

|------------------------------------------------|------|-------|---------------|--|

|                                                |      | REV A | PAGE 12       |  |

DESC FORM 144 A MAR 76

- 4.4.2 Group B inspection. In group B inspection, each inspection lot shall be subjected to the test subgroups and LTPD values shown in table IIb of method 5005 of MIL-STD-883, class B.

- 4.4.3 Group C and group D inspection. Group C and group D inspections shall be as specified in method 5005 of MIL-STD-883, class B. The frequency of testing and the sample size shall be in accordance with MIL-M-38510. Generic test data (6.5) may be used to satisfy the requirements for group C and group D inspection.

- a. End point electrical parameters shall be as specified in table II.

- b. Operating life test (method 1005 of MIL-STD-883) conditions:

- (1) Test condition D or E, each circuit must be driven with an appropriate signal to simulate circuit applications and each circuit shall have maximum load applied.

- (2)  $T_A = 125$ °C, minimum.

- (3) Test duration: 1,000 hours.

- c. Subgroups 3 and 4 shall be added to the group C inspection requirements and shall consist of the tests, conditions, and limits specified for subgroups 10 and 11 of group A.

- 4.5 Inspection of preparation for delivery. Inspection of preparation for delivery shall be in accordance with MIL-M-38510, except that the rough handling test shall not apply.

TABLE II. <u>Electrical test requirements</u>.

| MIL-STD-883 test requirements                                            | Subgroups        |

|--------------------------------------------------------------------------|------------------|

| Interim electrical parameters<br>(pre burn-in) (method 5004)             | 1                |

| Final electrical test parameters (method 5004)                           | 1*, 2, 3, 9      |

| Group A test requirements<br>(method 5005)                               | 1, 2, 3,<br>7, 9 |

| Groups C and D end point<br>electrical parameters<br>(method 5005)       | 1, 2, 3          |

| Additional electrical sub-<br>groups for group C<br>periodic inspections | 10, 11           |

<sup>\*</sup> PDA applies to subgroup 1 (see 4.3c).

- 5. PACKAGING

- 5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

- 6. NOTES

<u>@</u>?

6.1 Notes. Only 6.4 of the notes specified in MIL-M-38510 shall apply to this drawing.

CODE IDENT. NO. DWG NO. SIZE 14933 DEFENSE ELECTRONICS SUPPLY CENTER 77002 Α DAYTON, OHIO PAGE 13 ... REV

DESC FORM 144 A

- 6.2 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. This drawing is intended exclusively to prevent the proliferation of unnecessary duplicate specifications, drawings and stock catalog listings. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, this drawing becomes obsolete and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.3 Ordering data. The contract or order should specify the following:

Complete part number (see 1.2).

Requirements for delivery of one copy of the quality conformance inspection data pertinent to the device inspection lot to be supplied with each shipment by the device manufacturer, if applicable.

Requirement for certificate of compliance, if applicable.

Requirements for notification of change of product or process to procuring activity, if applicable.

Requirements for packaging and packing.

- Requirements for carrier, special lead lengths or lead forming, if applicable. These requirements shall not affect the part number. Unless otherwise specified, these requirements will not apply to direct shipment to the Government.

- 6.4 Replaceability. Replaceability is determined as follows:

a. Microcircuits covered by this drawing will replace the same generic device covered by contractor prepared specification or drawing.

When Military Specification MIL-M-38510/420 is issued, the part numbered devices specified in this drawing will be replaced by the microcircuit identified as part number M38510/42001B---.

6.5 Generic test data. Generic test data may be used to satisfy the requirements of 4.4.3. Generic test data is defined as test data from devices manufactured during the same time period, by means of the same production technique, materials, controls and design, and in the same micro-circuit group (see 3.1.3(h) of MIL-M-38510) as the deliverable devices. The same time period shall be interpreted as covering a maximum span of 180 days between the generic test sample fabrication and the fabrication of deliverable devices. The vendor is required to retain generic data for a period of not less than 36 months from the date of shipment.

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, CHIO | SIZE<br>A | 149 |    | DWG NO. | 77002  | ,,, |

|------------------------------------------------|-----------|-----|----|---------|--------|-----|

|                                                |           | R   | EV | Р       | AGE 14 |     |

| DESC FORM 144 A                                | <u></u>   | A   |    | ·       |        |     |

## 6.6 Suggested source(s) of supply. 2/

| DESC DRAWING<br>PART NUMBER | VENDOR<br>FSCM<br>NUMBER         | SIMILAR 1/<br>VENDOR TYPE                    | REPLACEMENT<br>MILITARY SPECIFICATION<br>PART NUMBER |

|-----------------------------|----------------------------------|----------------------------------------------|------------------------------------------------------|

| 7700201Q <b>X</b>           | 34335<br>34649<br>27014<br>01295 | AM9080A<br>MC8080A/B<br>INS8080A<br>TMS8080A | M38510/42001BQX                                      |

| VENDOR FSCM<br>NUMBER | YENDOR NAME<br>AND ADDRESS                                                        |  |

|-----------------------|-----------------------------------------------------------------------------------|--|

| 34335                 | Advanced Micro Devices, Inc.<br>901 Thompson Place<br>Sunnyvale, CA 94086         |  |

| 34649                 | Intel Corporation<br>3065 Bowers Avenue<br>Santa Clara, CA 95051                  |  |

| 27014                 | National Semiconductor Corp.<br>2900 Semiconductor Drive<br>Santa Clara, CA 95051 |  |

| 01295                 | Texas Instruments, Inc. P. O. Box 5012 Dallas, TX 75222                           |  |

- 1/ CAUTION. DO NOT USE THIS NUMBER FOR ITEM PROCUREMENT. ITEMS PROCURED TO THE SIMILAR VENDOR TYPE ONLY MAY NOT SATISFY THE PERFORMANCE REQUIREMENTS OF THIS DRAWING.

- 2/ For additional suggested sources of supply or assistance in the use of this drawing, contact DESC-EC, 1507 Wilmington Pike, Dayton, Ohio 45444 or telephone 513 -296-5375.

DEFENSE ELECTRONICS SUPPLY CENTER A 14933 77002

REV PAGE 15

Dayton, Ohio 45444