|                                 |                |              |               |            |             |                          |                   |               |                   |                     | RE\               | /1 <b>S</b> K | SKC            |                                     |              |          |          |           |                    |                            |                       |          |      |             |              |

|---------------------------------|----------------|--------------|---------------|------------|-------------|--------------------------|-------------------|---------------|-------------------|---------------------|-------------------|---------------|----------------|-------------------------------------|--------------|----------|----------|-----------|--------------------|----------------------------|-----------------------|----------|------|-------------|--------------|

| LTR                             |                |              |               |            |             |                          | D                 | ESC           | RIPTI             | ON                  |                   |               |                |                                     |              |          | ľ        | DATE      | (YR-I              | MO-DA                      | 4)                    | API      | PRO  | /ED         |              |

| A                               | Table<br>1.75  | e I:<br>mW.  | Ad            | ld \       | OL          | para                     | nete              | rs.           | 1.                | 3:                  | Chai              | nge           | P <sub>D</sub> | from 1                              | .5 m         | d to     |          | 1984      | I MA               | R 2                        |                       | M        | 10   | K           | 7            |

| В                               | Revi           | se t<br>erat | able<br>ure   | e I        | lim<br>nge, | its,<br>and              | add<br>rev        | 10<br>tse     | MHz<br>wav        | dev<br>efor         | ice               | , re          | vis            | e oper                              | atin         | <b>g</b> |          | 198       | 5 DE               | C 10                       | 6                     | M        | 0    | ď           | 6            |

| С                               | a QP<br>the    | L so<br>corr | urce<br>espo  | e, e       | chan<br>ing | ge pa<br>wave            | aram<br>form      | ete:          | rs 2<br>n fi      | 8, 5<br>gure        | 6.                | and<br>Ac     | 58<br>Id v     | parts<br>in tab<br>endor<br>oughou  | le I<br>CAGE | and      |          | 1987      | 7 AP               | R 2                        | 3                     | <b>*</b> | 0.   | Z           | þ            |

| D                               | tabl<br>numb   | es I<br>er t | and<br>o 67   | d I<br>726 | I.<br>8.    | Dele<br>Dele             | te f<br>te v      | i gu<br>end   | res<br>or C       | 2 <b>a</b> r<br>AGE | nd 3<br>num       | . (<br>ber    | han<br>047     | hanges<br>ge CAG<br>13 as<br>hout d | E<br>appr    |          |          | 198       | B AF               | R 1                        |                       | 4        | 1.0  | ومرا        | ,            |

| E                               |                | vend         | lor (         | CAG        | E 18        | 324                      |                   |               |                   |                     |                   |               |                | n figu<br>. Edi                     |              |          |          | 198       | 9 N                | OV 1                       | 6                     |          | .aj  | y           | 1            |

|                                 |                |              |               |            |             |                          |                   |               |                   |                     |                   |               |                |                                     |              |          |          |           | - <del></del>      |                            |                       |          |      |             |              |

| CU                              | IRRE           | EN           | ТС            | <b>A</b>   | GE          | E C                      | OE                | Œ             | 67                | 26                  | 8                 |               |                |                                     |              |          |          |           |                    |                            |                       |          |      |             |              |

| CU                              | IRRE           |              | r c           | A          | GE          | E C                      | OE                | Œ             | 67                | 26                  | 8                 |               |                |                                     | Ţ            |          |          |           |                    |                            |                       |          |      |             |              |

| REV                             |                |              |               |            | L           |                          |                   |               |                   |                     |                   |               |                |                                     |              |          |          |           |                    |                            |                       |          |      |             |              |

| REV<br>SHEET<br>REV             | r              | E            | Ε             | E          | E           | E                        | E                 | E             | Ē                 | E                   | E                 | E             |                |                                     |              |          |          |           |                    |                            |                       |          |      |             |              |

| REV<br>SHEET<br>REV<br>SHEET    | r              |              | Ε             | E<br>24    | L           |                          | E                 | E             |                   | E                   |                   | E 32 E        | E              | E                                   | E            | E        | E        | E         | E                  | E                          | E                     | E        | E    | E           | E            |

| REV<br>SHEET<br>REV<br>SHEET    | TATUS          | E            | E 23          | E<br>24    | E 25        | E 26                     | E 27              | E 28          | E 29              | E<br>30             | E<br>31           | 32            |                | _                                   | E E 11       | E 12     |          | E 14      |                    | E 16                       | ┡—                    | E 18     | E 19 | <del></del> | E 21         |

| REV SHEET REV SHEET REV S OF SH | TATUS<br>HEETS | E 22         | E<br>23<br>RE | E 24       | E 25        | E 26 E 1                 | E 27 E 2          | E 28 E 3      | E<br>29<br>E<br>4 | E<br>30<br>E<br>5   | E<br>31<br>E<br>6 | 32<br>E<br>7  | E<br>8         | _                                   | 11           |          | 13       | 14<br>THC | 15<br><b>NIC</b> : | 16<br><b>s su</b>          | 17<br>PPLY            | 18       | 19   | 20          | E 21         |

| REV SHEET REV SHEET REV S OF SH | TATUS HEETS    | E 22         | E 23 REV      | E 24       | E 25        | E 26 E 1                 | E 27 E 2 PARE     | E 28 E 3 D BY | E 29 E 4          | E 30 E 5            | E 31 E 6          | 32<br>E<br>7  | E<br>8         | _                                   | 11           | 12       | 13       | 14<br>THC | 15<br><b>NIC</b> : | 16                         | 17<br>PPLY            | 18       | 19   | 20          | <del>-</del> |

| REV SHEET REV SHEET REV S OF SH | TATUS<br>HEETS | E 22         | E 23 RESHE    | E 24       | E 25        | E<br>26<br>E<br>1<br>PRE | E<br>27<br>E<br>2 | E 28 E 3 D BY | E 29 E 4          | E 30 E 5            | E<br>31<br>E<br>6 | 32<br>E<br>7  | E<br>8         | 9 10<br>MI                          | DEF          | 12       | ELECTORY | TON,      | NIC:<br>OHI        | 16<br>S SU<br>O 45<br>ROCE | 17<br><b>PPL</b> 1444 | 18 CEN   | 19   | 20          | <del></del>  |

AMSC N/A

+ U.S. GOVERNMENT PRINTING OFFICE: 1987 — 748-129/60912 5962-E1242

OF

SHEET

## 1. SCOPE

1.1 <u>Scope</u>. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

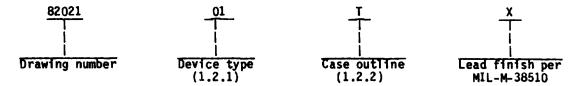

1.2 Part number. The complete part number shall be as shown in the following example:

1.2.1 Device types. The device types shall identify the circuit function as follows:

| Device type | Generic number       | Circuit                                                                         |

|-------------|----------------------|---------------------------------------------------------------------------------|

| 01<br>02    | 68000-6<br>68000-8   | 16-bit fixed instruction microprocessor 16-bit fixed instruction microprocessor |

| 03<br>04    | 68000-10<br>68000-12 | 16-bit fixed instruction microprocessor 16-bit fixed instruction microprocessor |

1.2.2 <u>Case outlines</u>. The case outlines shall be as designated in appendix C of MIL-M-38510, and as follows:

| T | See figure 1 (68-terminal 1.080" x 1.080" x .102") pin grid array               |

|---|---------------------------------------------------------------------------------|

| U | See figure 1 (68-terminal 0.960" x 0.960" x .097") leaded chip carrier package) |

| X | C-7 (68-terminal .962" x .962" x .120") square chip carrier package with        |

|   | thermal pad                                                                     |

| Y | D-13 (64-lead, 3.240" x .920" x .225") dual-in-line package                     |

| Z | C-7 (68-terminal .962" x .962" x .120") square chip carrier package             |

Case outline

1.3 Absolute maximum ratings.

Outline letter

1.4 Recommended operating conditions.

Supply voltage:

| Supply voicage.                                           |                          |

|-----------------------------------------------------------|--------------------------|

| VCC                                                       | 4.75 V dc to 5.25 V dc   |

| High level input voltage (logic inputs)(V <sub>IH</sub> ) | 2.0 V to V <sub>CC</sub> |

| Low level input voltage (logic inputs)(YIL)               | GND to 0.8 V dc          |

| Minimum high level output voltage                         | 2.4 V dc                 |

| Maximum low level output voltage                          |                          |

| Frequency of operation:                                   |                          |

| Device type 01                                            | 4.0 to 6.0 MHz           |

| Device type 02                                            | 4.0 to 8.0 MHz           |

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                |        | 82021   |

|------------------------------------------------------|-----------|----------------|--------|---------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | -<br>F | SHEET 2 |

DESC FORM 193A SEP 87

# U. S. GOVERNMENT PRINTING OFFICE: 1988-650-547

Device type 03 - - - - - - - - - - - - - 4.0 to 10.0 MHz Device type 04 - - - - - - - - - - - - - 4.0 to 12.0 MHz Case operating temperature range ( $T_{\rm C}$ )- - - - - - - - - - - - 55 C to +110 C

# 2. APPLICABLE DOCUMENTS

2.1 Government specification, standard, and bulletin. Unless otherwise specified, the following specification, standard, and bulletin of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

MILITARY

MIL-M-38510

Microcircuits, General Specification for.

**STANDARD**

**MILITARY**

MIL-STD-883

- Test Methods and Procedures for Microelectronics.

BULLETIN

MILITARY

MIL-BUL-103

List of Standardized Military Drawings (SMD's).

(Copies of the specification, standard, and bulletin required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

## 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

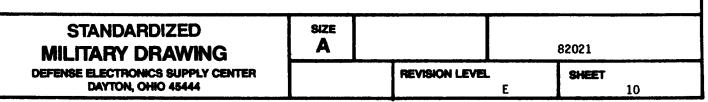

- 3.2.1 Case outlines. The case outlines shall be in accordance with 1.2.2 and figure 1.

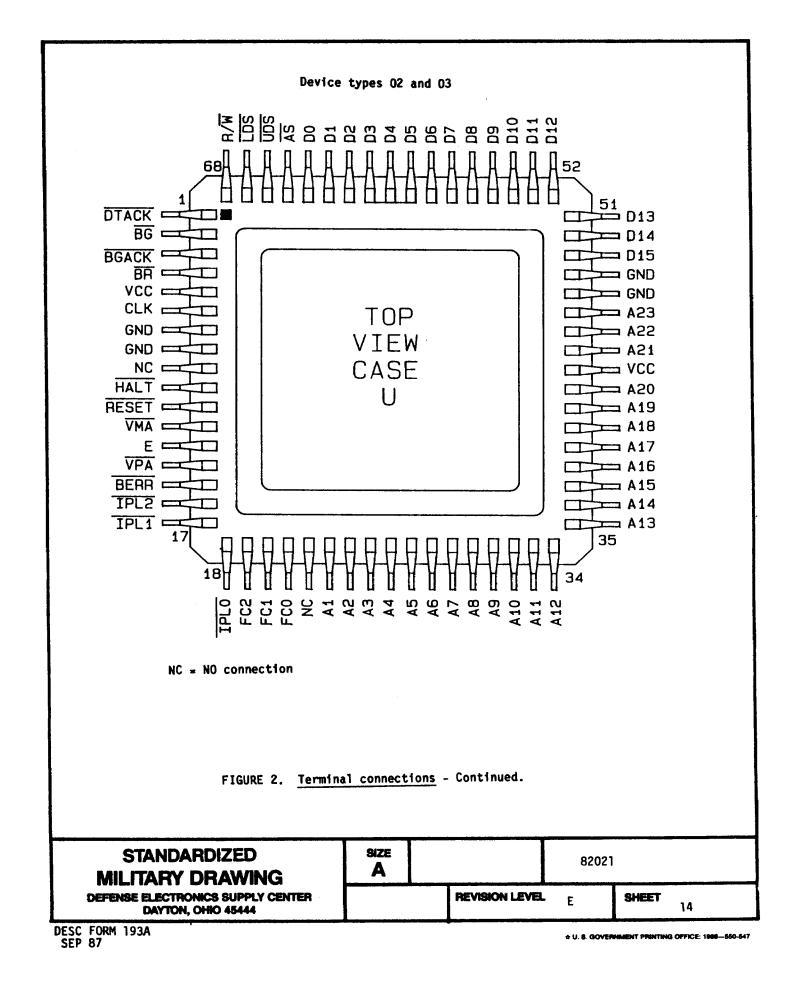

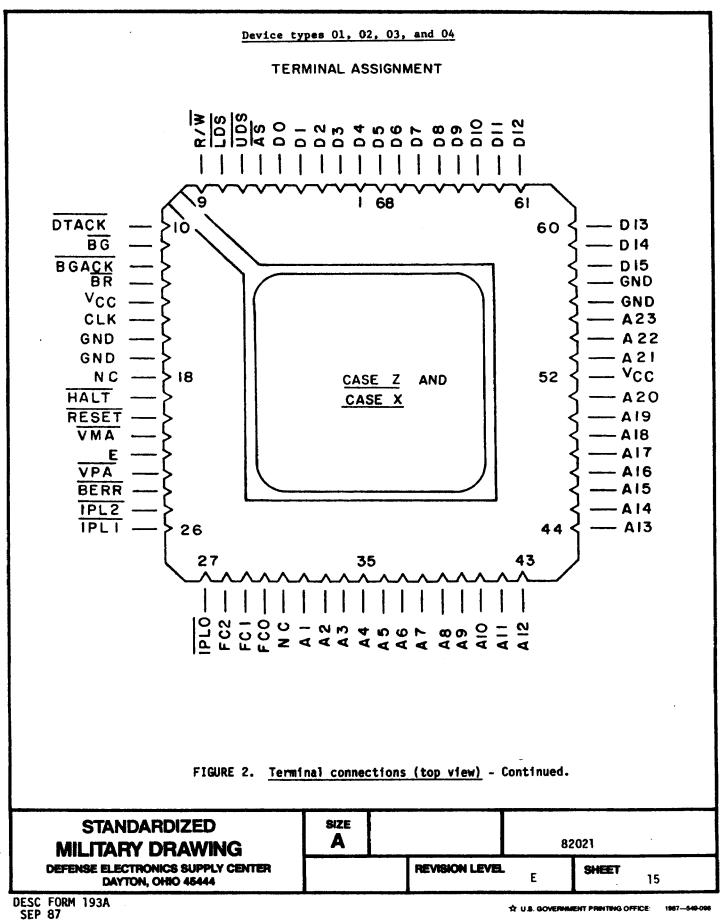

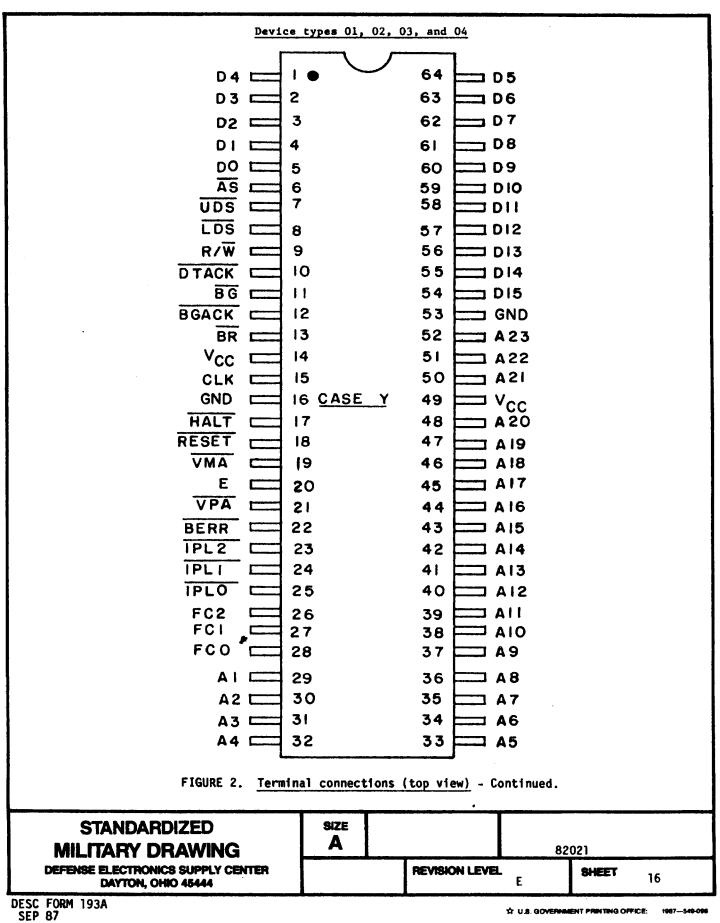

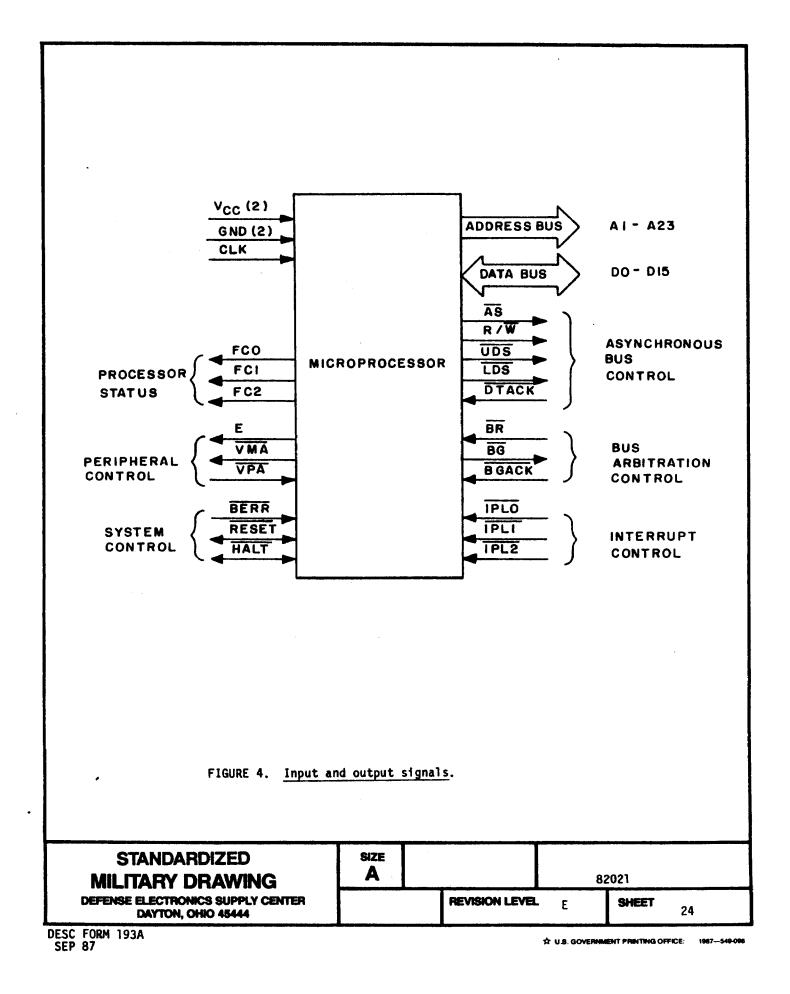

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

- 3.3 Electrical performance characteristics. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 Electrical test requirements. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in MIL-BUL-103 (see 6.7 herein).

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |               |     | 82021   |  |

|------------------------------------------------------|-----------|---------------|-----|---------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | i         | REVISION LEVE | _ F | SHEET 3 |  |

DESC FORM 193A SEP 87

**★ U. B. GOVERNMENT PRINTING OFFICE: 1988—550-547**

| Test                                                      | Symbol                     | Cor<br>-55°C <                                    | nditions 1/<br>T <sub>C</sub> ≤ +110°C | Group A<br> subgroups | Limit              | S              | Unit                 |

|-----------------------------------------------------------|----------------------------|---------------------------------------------------|----------------------------------------|-----------------------|--------------------|----------------|----------------------|

|                                                           |                            | 1 4./5 V <                                        | VCC < 5.25 V<br>erwise specified       |                       | Min I              | Max            | <u> </u>             |

| High-level output<br>voltage all outputs                  | V <sub>OH1</sub>           | I <sub>OH</sub> = -400 μA                         |                                        | 1, 2, 3               | <br>  2.4  <br>    |                | <br>  V<br>          |

| High-level output voltage<br>enable only                  | V <sub>OH2</sub>           | <br> I <sub>OH</sub> = -400 μA<br> R pullup = 1.1 | kΩ                                     | <br> <br>             | V <sub>CC</sub> 75 |                | ٧                    |

| Low-level output voltage<br>A23-1, FCO-2, BG              | Y <sub>OL1</sub>           | V <sub>CC</sub> = 4.75 V                          | I <sub>OL</sub> = 3.2 mA               | 1, 2, 3               |                    | 0.5            | V                    |

| Low-level output<br>voltage HALT                          | <br>  V <sub>OL2</sub><br> | <br>                                              | I <sub>OL</sub> = 1.6 mA               |                       |                    |                | <br> <br>            |

| Low-level output voltage AS, R/W, D15-0, VDS, LDS, VMA, E | V <sub>OL3</sub>           | <br>                                              | I <sub>OL</sub> = 5.3 mA               | 1                     | ]<br> <br>         |                | <br> <br> <br>       |

| Low-level output voltage<br>RESET                         | V <sub>0L4</sub>           |                                                   | IOL = 5.0 mA                           |                       |                    |                | <br> <br>            |

| High-impedance (off-<br>state) output<br>current (HIGH)   | I OHZ                      | V <sub>0</sub> = 2,4 V                            |                                        | 1, 2, 3               |                    | 20             | μ <b>Α</b>           |

| High-impedance (off-<br>state) output<br>current (LOW)    | I I OLZ                    | V <sub>0</sub> = 0.4 V                            |                                        | 1, 2, 3               | -20                | <br> <br> <br> | <br>  μ <b>A</b><br> |

| High-level input current; all inputs 2/                   | I <sub>IH1</sub>           | V <sub>IN</sub> = 5.25 V                          |                                        | 1, 2, 3               |                    | 2.5            | <br>  μ <b>Α</b><br> |

| High-level input current HALT, RESET                      | I <sub>1H2</sub>           | -i<br> <br>                                       |                                        | <br>                  | j<br> <br>         | 20             | †<br>  μΑ<br>        |

| Low-level input current; all inputs 2/                    | IIL1                       | V <sub>IN</sub> = O V                             |                                        | 1, 2, 3               | -2.5               |                | μ <b>A</b>           |

| Low-level input current<br>HALT, RESET                    | I <sub>IL2</sub>           | -<br> <br> -<br> -                                |                                        |                       | 1 -20              | <br> <br>      | 1                    |

| Supply current                                            | Icc                        | V <sub>CC</sub> = 5.25 V                          | <u>3</u> /                             | 1, 2, 3               | T                  | 333            | l mA                 |

| Capacitance                                               | CIN                        | <br> V <sub>IN</sub> = 0 V<br> frequency = 1      | MHz (see 4.3.1c)                       | 4                     | 1                  | 20             | pF                   |

| Functional tests  See footnotes at end of ta              | ble.                       |                                                   |                                        | 7, 8                  |                    |                |                      |

| STANDARDIZ                                                |                            | SIZE                                              |                                        |                       |                    |                |                      |

| MILITARY DRAY                                             |                            | A                                                 |                                        |                       | 82021              |                |                      |

$\pm$  U. S. GOVERNMENT PRINTING OFFICE: 1988—560-547

|                                                                | TABLE                       | . Electrical pe                                                                                   | erforman               | ce cha          | racteri:                             | tics              | - 0             | onti          | nue               | d.            |               |               |                  |             |

|----------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------|------------------------|-----------------|--------------------------------------|-------------------|-----------------|---------------|-------------------|---------------|---------------|---------------|------------------|-------------|

| Test                                                           | Symbol                      | Conditions<br>-55°C <t<sub>C&lt;*110<br/>4.75 V<v<sub>CC&lt;5.2<br/>unless otherw</v<sub></t<sub> | 1/ 1<br>C 1<br>25 V 1  | number<br>(see  | <br> Group<br> A<br> sub-<br> groups | 6 M               | 01              | type          | 02                | type          | 03            | type          |                  | Uni         |

|                                                                |                             | specified                                                                                         |                        | 3)              |                                      | Min               | Max             | Min           | Max               | Min           | Max           | Min           | Max              |             |

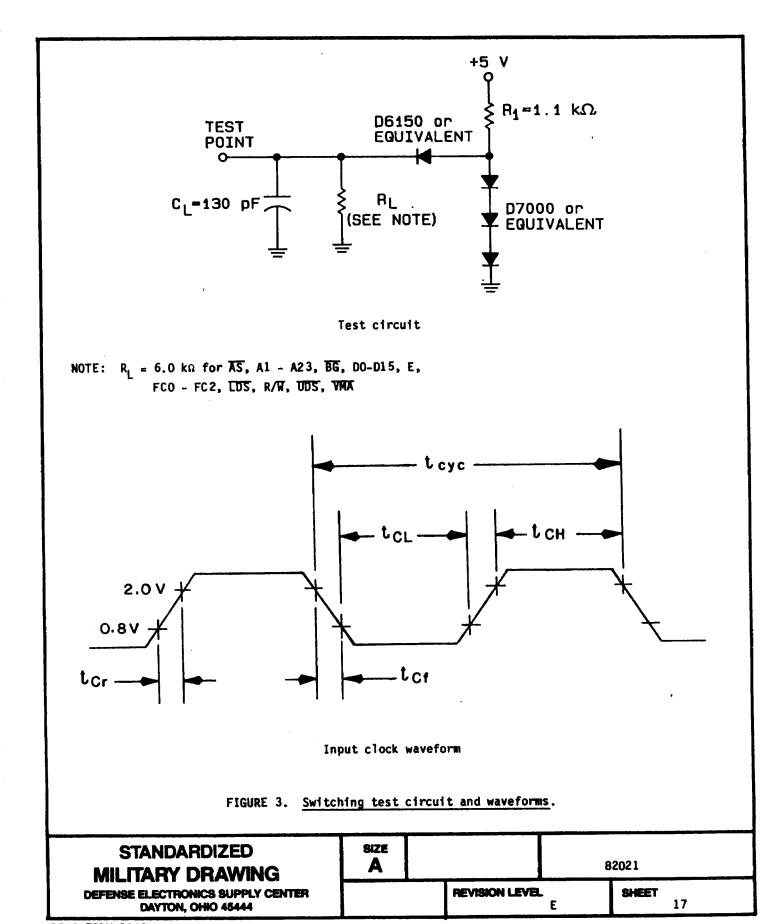

| Clock period                                                   | t <sub>Cyc</sub>            | GND = 0 V<br>C <sub>L</sub> = 130 pF                                                              | <u> </u><br>           | 1               | 9, 10,<br>11                         | 167               | 250             | 125           | 250               | 100           | 250           | 80            | 250              | ns          |

| Clock width low                                                | tCL                         | See figure 3                                                                                      | <u> </u>               | 2               | 9, 10,<br>11                         | 75                | 125             | 55            | 125               | 45            | 125           | 35            | 125              | l<br>I ns   |

| Clock width high                                               | <sup>‡</sup> CH             |                                                                                                   | 1                      | 3               | 9, 10,<br>11                         | 75                | 125             | 55            | 125               | 45            | 125           | <br>  35<br>  | 125<br>          | ns          |

| Clock fall time                                                | <sup>t</sup> Cf             |                                                                                                   | 1                      | 4               | 9, 10,<br>11                         | †<br> <br>        | 10              | <br> <br>     | 10                | !<br>!<br>    | 10            | <br> <br>     | 5                | ns          |

| Clock rise time                                                | t <sub>Cr</sub>             |                                                                                                   | <u> </u>               | 5               | 9, 10,<br>11                         |                   | 10              | <br> <br>     | 10                | !<br>!        | <br>  10<br>  | 1             | 5                | ns          |

| Clock low to<br>address                                        | <sup>t</sup> CLAY           |                                                                                                   | <br>                   | 6               | 9, 10,<br>11                         |                   | 80              |               | 70                | <br> <br>     | <br>  60<br>  | 1<br> <br>    | 55               | ns          |

| Clock high to FC valid                                         | <sup>t</sup> CHFCV          |                                                                                                   | T<br>!<br>!            | 6A              | 9, 10,<br>11                         |                   | 80              |               | 70                | <br> <br>     | 60            |               | <br>  55<br>     | l ns        |

| Clock high to ad-<br>dress data high<br>impedance<br>(maximum) | <sup>t</sup> CHADZ          |                                                                                                   | <br> <br> <br>         | 7<br><u>4</u> / | 9, 10,<br>  11                       | ]<br>             | 100             |               | <br>  80<br> <br> | <br>          | 70            |               | 60<br> <br>      | ns          |

| Clock high to<br>address/FC<br>invalid (minimum)               | <sup>t</sup> CH <b>A</b> FI |                                                                                                   | ]<br> <br> <br> <br>   | 8<br><u>5</u> / | 9, 10,<br>  11                       | 1                 |                 | <br>  0<br>   |                   | <br>  0<br>   |               | 0             | ]<br> <br> -<br> | ns          |

| Clock high to AS, DS low (maximum)                             | tCHSL                       | ]<br> <br>                                                                                        | ]<br> <br><u> </u>     | 9 <u>6</u> /    | 9, 10,                               | 7/<br>  0<br>     | 70              | 7/<br>  0<br> | <br>  60<br>      | 7/<br>  0<br> |               | 7/<br>  0<br> | <br>  55<br>     | ns          |

| Clock high to AS,<br>DS high (minimum)                         | tCHSLn                      |                                                                                                   |                        | <u>8</u> /      | 9, 10,<br>11                         | ]<br> <br>        | !<br>!<br>!     | <br> <br>     | !<br>!<br>!       | ]<br> <br>    | <br> <br>     | <br> <br>     | <br> <br>        | l ns        |

| Address to AS, DS<br>(read) low/AS<br>write                    | tavsl                       |                                                                                                   | <br> <br> <br>         | 11 <u>9</u> /   | 9, 10,<br>  11                       | 35                | <br> <br> <br>  | 30            | <br> <br> <br>    | <br>  20<br>  | <br> <br>     | 0             | <br>             | l ns        |

| FC valid to AS, DS<br>(Read) low/AS<br>write                   | tFCVSL                      | <br>                                                                                              | <br> <br> <br><u> </u> |                 | 9, 10,                               | <br>  70<br> <br> | !<br>!<br>!     | <br>  60<br>  | !<br>!<br>!       | <br>  50<br>  | 1             | 40            | <br> <br> <br>   | ns          |

| Clock low to AS, DS<br>high                                    | tCLSH                       | !<br>!                                                                                            | ·                      | 12 <u>6</u> /   | 9, 10,<br>11                         |                   | 80              |               | 70                |               | 55            |               | 50               | ns          |

| AS, DS high to<br>address/FC<br>invalid<br>See footnotes at en | tSHAFI                      | ]<br>                                                                                             |                        |                 | 9, 10,                               | 40                | 1<br> <br> <br> | 30            | <br>              | 20            |               | 10            | 1                | l ns        |

| STANDA                                                         | <del>,</del>                |                                                                                                   | SIZE                   |                 |                                      |                   |                 |               |                   |               | <del></del>   |               |                  |             |

| MILITARY<br>DEFENSE ELECTRO                                    | DRA                         | WING                                                                                              | A                      |                 | REVIS                                | ON L              | EVEL            | . E           |                   | <del></del>   | 32021<br>SHEE |               | 5                | <del></del> |

$\pm$  U. S. GOVERNMENT PRINTING OFFICE: 1988—550-547

|                                              | TABLE I            | . Electrical pe                                                        | rforman        | ce ch                  | ara         | cteris              | tics           | - 0            | onti      | nue            | 1.         |                 |           |                |      |

|----------------------------------------------|--------------------|------------------------------------------------------------------------|----------------|------------------------|-------------|---------------------|----------------|----------------|-----------|----------------|------------|-----------------|-----------|----------------|------|

| Test                                         | Symbol             | Conditions<br>-55°C <tc≤+110<br>4.75 V≤V<sub>CC≤</sub>5.2</tc≤+110<br> | 1/             | Wave-<br>form<br>numbe | rļA         | roup                | <b>type</b>    | 01             | type      | 02             | type       | ce<br>03<br>MHz | type      | 04.            | Unit |

|                                              |                    | 4./5 V <v<sub>CC&lt;5.2<br/>unless otherw<br/>specified</v<sub>        | ise i          | (see<br>figur<br>3)    |             | ub-<br>roups        | Min            | Max            | Min       | Max            | Mi n       | Max             | Min       | Max            | ,    |

| AS. DS width low<br>(read)/AS write          | t <sub>SL</sub>    | GND = 0 V<br>C <sub>L</sub> = 130 pF                                   | <br> <br> <br> | 14 <u>9</u>            | / 9<br>/    | 11 <sup>10</sup> ,  | 337            |                | 240       |                | 195        |                 | 160       |                | ns   |

| DS width low<br>(write)                      | tosl               | See figure 3                                                           |                |                        | / 9<br>/    | 10,<br>11           | 170            |                | 115       |                | 95         |                 | 80        |                | ns   |

| AS, DS width high                            | t <sub>SH</sub>    |                                                                        | 1              | 15 <u>9</u>            | / 9<br>/    | , 10,<br>11         | 180            |                | 150       |                | 105        |                 | 65        |                | i ns |

| clock high to AS,<br>DS high impedance       | tcHCZ              |                                                                        |                | 16 <u>4</u>            | / 9         | 11 <sup>10</sup> ,  |                | 100            |           | 80             |            | 70              |           | 60             | ns   |

| AS, DS high to R/W<br>high                   | t <sub>shrh</sub>  |                                                                        |                | 17 9<br>10             | / S         | 11 <sup>10</sup> ,  | 50             | <br> <br> <br> | 40        |                | 20         | 1               | 10        |                | ns   |

| Clock high to R/W<br>high (maximum)          | tCHRH              |                                                                        |                | 18 6                   | / 9         | ), 10,<br>11        |                | 80             | <br> <br> | 70             | ]<br> <br> | 60              | <br> <br> | 60             | ns   |

| Clock high to R/W<br>high (minimum)          | <sup>t</sup> CHRHn |                                                                        |                | 8                      | /   9       | ), 10,<br>11        |                | <br> <br>      |           |                |            |                 | <br> <br> |                |      |

| Clock high to R/W                            | <sup>‡</sup> CHRL  |                                                                        | -              | 20 6                   | / 9         | ), 10,<br>11        | <br>           | 80             |           | 70             |            | 60              |           | 60             | ns   |

| AS low to R/W<br>valid                       | tasrv              |                                                                        | •              | 20A10                  | // <u> </u> | ), 10,<br>11        | <br> <br>      | 20             |           | 20             | <br> <br>  | 20              | <br> <br> | 20             | ns   |

| Address valid to<br>R/W low (write)          | tavrl              |                                                                        | _              | 21 <u>1</u>            |             | 9, <sup>10</sup> ,  | 25             |                | 20        |                | 0          |                 | 0         |                | ns   |

| FC valid to R/W<br>low (write)               | tFCVRL             |                                                                        |                | 21A 9                  |             | 9 <sub>11</sub> 10, | <br>  70<br>   |                | 60        | <br> <br> <br> | 50         |                 | 30        |                | ns   |

| R/W low to DS low (write)                    | tRLSL              |                                                                        | ·              | 22 1                   | <u> </u>    | 911 <sup>10</sup> , | 140            |                | 80        |                | 50         | <br>            | 30        | <br> <br> <br> | ns   |

| Clock low to data<br>out valid (write)       | tCLDO              |                                                                        |                | 23                     |             | 9, 10,<br>11        |                | 80             |           | 70             |            | 55              |           | 55             | ns   |

| Clock high to R/W<br>VMA high im-<br>pedance | t <sub>CHRZ</sub>  | <br>                                                                   |                | 1                      |             | 9, 10,<br>11        | <br> <br> <br> |                |           | <br> <br> <br> |            |                 |           | !<br>!         | ns   |

| See footnotes at er                          | d of ta            | ble.                                                                   |                |                        |             |                     |                |                | ·····     |                |            |                 |           |                |      |

| STANDA<br>MILITARY                           |                    |                                                                        | SIZE<br>A      |                        |             |                     |                |                |           |                | 8          | 32021           | ļ         |                |      |

| DEFENSE ELECTR                               |                    | JPPLY CENTER                                                           |                |                        |             | REVIS               | ION I          | LEVE           | LE        |                |            | SHE             | ET        | 6              |      |

★ U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

|                                                  | TABLE I.                | Electrical po                                                                                                                                                                                                                                                                              | erforma             | nce               | cha               | racteri      | stic         | s - C                     | onti             | nued             | •                  | *****                    | -                |                |                        |

|--------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|-------------------|--------------|--------------|---------------------------|------------------|------------------|--------------------|--------------------------|------------------|----------------|------------------------|

| Test                                             | Symbol                  | Condition:<br>-55°C <tc<+1<br>4.75 V<vcc≤5.< th=""><th>s <u>1/</u><br/>10°C</th><th>Way<br/>for<br/>num</th><th>m<br/>mber</th><th>Group</th><th></th><th></th><th>Devi</th><th>e 02</th><th>typ</th><th>e 03</th><th>typ</th><th>e 04</th><th> <br/> <br/> Unit</th></vcc≤5.<></tc<+1<br> | s <u>1/</u><br>10°C | Way<br>for<br>num | m<br>mber         | Group        |              |                           | Devi             | e 02             | typ                | e 03                     | typ              | e 04           | <br> <br> Unit         |

|                                                  | <br>                    | unless other<br>specifie                                                                                                                                                                                                                                                                   | rw1 se              | f19<br> 3)        | jure              | groups       |              | <br> Max                  | <br> Mfn         | Max              | l<br>Min           | Max                      | <br> Min         | <br> Max       | <u> </u>               |

| AS, DS high to data<br>out invalid<br>(write)    | <sup>t</sup> SHDOI      | GND = 0 V<br>C <sub>L</sub> = 130 pF                                                                                                                                                                                                                                                       |                     | <br>  25<br>      | 9/<br>10/         | 9, 10,<br>11 | <br>  40<br> | <br>                      | 1<br>1 30<br>1   | <br> <br> <br>   | !<br>  20<br> <br> | <br>                     | 15<br>15         | <br>           | l ns                   |

| Data out valid to DS low (write)                 | t <sub>DOSL</sub>       | See figure 3                                                                                                                                                                                                                                                                               |                     | 26                | 9/                | 9, 10,<br>11 | 35           |                           | 30               |                  | <br>  20<br>       | <br> <br>                | <br>  15<br>     |                | ns                     |

| Data in to clock<br>low (setup time)<br>(read)   | ₽D I CL                 |                                                                                                                                                                                                                                                                                            |                     | 27                | 10/<br>13/        | 9, 10,<br>11 | 25           |                           | <br>  15<br>     |                  | <br>  10<br>       | <br> <br> <br>           | <br>  10<br>     | <br> <br>      | ns                     |

| AS, DS high to<br>DTACK high                     | <sup>t</sup> shdah      |                                                                                                                                                                                                                                                                                            |                     | <br>  28<br>      | 9/<br>10/         | 9, 10,<br>11 | 0            | <br> 325<br> <br>         | <br>  0<br> <br> | 245              | 0                  | <br>  190<br> <br>       | 0                | 150<br>        | ns                     |

| DS high to data<br>(read) invalid<br>(hold time) | t <sub>SHDII</sub>      |                                                                                                                                                                                                                                                                                            |                     | <br> 29<br> <br>  | <u>10</u> /       | 9, 10,<br>11 | <br>  0<br>  | <br> <br>                 | <br>  0<br>      |                  | <br>  0<br>        | <br> <br> <br> <br>      | <br>  0<br> <br> | <br> <br> <br> | ns                     |

| AS, DS high to<br>BERR High                      | tSHBEH                  |                                                                                                                                                                                                                                                                                            |                     | 30                | <u>10</u> /       | 9, 10,<br>11 | <br>  0<br>  |                           | 0                |                  | 0                  | <br> <br>                | 0                |                | ns                     |

| DTACK low to data<br>in (setup time)             | <sup>t</sup> DALDI      |                                                                                                                                                                                                                                                                                            |                     | <br> 31<br> 10,   | 9/<br><u>13</u> / | 9, 10,<br>11 | !<br> <br>   | <br>  120<br>             | <br> <br> <br>   | <br>  90<br>     | <br> <br>          | <br>  65<br> <br>        | <br>             | <br>  50<br>   | ns                     |

| HALT and RESET<br>input transi-<br>tion time     | t <sub>RHr</sub> , f    |                                                                                                                                                                                                                                                                                            |                     | 32                | 4/                | 9, 10,       | 0            | 200                       | 0                | 200              | <br>  0<br>        | <br> 200<br>             | <br>  0<br>      | 200            | ns                     |

| Clock high to BG<br>low                          | tCHGL                   |                                                                                                                                                                                                                                                                                            | _                   | 33                |                   | 9, 10,<br>11 |              | 80                        | <br> <br>        | 70               |                    | 60                       |                  | <br>  50<br>   | ns                     |

| Clock high to BG<br>high                         | <sup>‡</sup> СНGН       | _                                                                                                                                                                                                                                                                                          |                     | 34                | <u>10</u> /       | 9, 10,<br>11 | !<br>!<br>!  | 80                        | <br> <br>        | 70               |                    | <br>  60<br>             | <br> <br>        | 50             | ns                     |

| BR low to BG low                                 | <sup>t</sup> BRLGL      |                                                                                                                                                                                                                                                                                            |                     | <br>  35<br>      | <u>10</u> /       | 9, 10,<br>11 | 1.5          | 3.5<br>+100<br>ns         |                  | 3.5<br>+90<br>ns | ļ                  | <br> 3.5<br> +80<br>  ns | l                |                | Clk.<br> Per.          |

| BR high to BG high                               | <sup>t</sup> BRHGH      |                                                                                                                                                                                                                                                                                            |                     | 36<br>            | 10/<br>14/        | 9, 10,<br>11 | <br> 1.5<br> | <br> 3.5<br> +100<br>  ns |                  | 3.5<br>+90<br>ns | !                  | <br> 3.5<br> +80<br>  ns | !                |                | <br> Clk.<br> Per.<br> |

| BGACK low to BG<br>high                          | t <sub>GALGH</sub>      |                                                                                                                                                                                                                                                                                            | •                   | <br> 37<br>       | <u>10</u> /       | 9, 10,<br>11 | 1.5          | <br> 3.5<br> +100<br>  ns |                  | 3.5<br>+90<br>ns | ļ                  | 3.5<br> +80<br>  ns      | !                |                | Clk.<br> Per.          |

| BGACK low to BR high (to prevent rearbitration)  | <sup>t</sup> GALBRH     |                                                                                                                                                                                                                                                                                            | •                   | 37 <i>I</i>       | \ <u>10</u> /     | 9, 10,<br>11 | 20<br>  ns   |                           | <br>  20<br>  ns | 1.5              | 20<br>  ns         | 1.5                      | 20<br>  ns       |                | C1k.<br> Per.          |

| See footnotes at end STANDA                      |                         |                                                                                                                                                                                                                                                                                            | SIZE                | 7                 |                   |              |              | <u> </u>                  |                  |                  |                    |                          |                  |                |                        |

| MILITARY                                         | DRAW                    | /ING                                                                                                                                                                                                                                                                                       | A                   |                   |                   | <del></del>  |              |                           |                  |                  | 82                 | 021                      |                  |                |                        |

| DEFENSE ELECTRO<br>DAYTON                        | ONICS SUP<br>, OHIO 454 |                                                                                                                                                                                                                                                                                            |                     |                   |                   | REVIS        | ION L        | .EVEL                     | E                |                  | s                  | HEET                     | 7                |                |                        |

# U. B. GOVERNMENT PRINTING OFFICE: 1988-548-904

|                                                   | INDEL I                       | Electrical pe                                                                                                                                                                                                                         |                    |           |                  | 2000                    |     |              |                |             |           |           |          | N    |                |                    |

|---------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|------------------|-------------------------|-----|--------------|----------------|-------------|-----------|-----------|----------|------|----------------|--------------------|

| Test                                              | Symbol .                      | Conditions<br>-55 C <tc<+11< th=""><th>0°C     1</th><th>or</th><th>ber</th><th></th><th></th><th>Devi</th><th>01</th><th>type</th><th>2 02</th><th>type</th><th>e 03</th><th>Devi</th><th></th><th> <br/> <br/> Uni 1</th></tc<+11<> | 0°C     1          | or        | ber              |                         |     | Devi         | 01             | type        | 2 02      | type      | e 03     | Devi |                | <br> <br> Uni 1    |

|                                                   |                               | 4.75 V∠V <sub>CC</sub> ∠5.2<br>unless other<br>specified                                                                                                                                                                              | wise  1            | fig       |                  | sub-<br>grou            | ps  | Min          | Max            | M1 n        | Max       | Min       | Max      | Min  | Max            | <br> <br>          |

| BG low to bus<br>high impedance<br>(with AS high) | t <sub>GLZ</sub>              | GND = 0 V<br>C <sub>L</sub> = 130 pF                                                                                                                                                                                                  |                    | 38        | 4/               | 9 <sub>11</sub> 1       | 0,  |              | 100            |             | 80        |           | 70<br>   |      | 60             | ns                 |

| BG width high                                     | t <sub>GH</sub>               | See figure 3<br> <br>                                                                                                                                                                                                                 | ]3                 | 39        | <u>10</u> /      | 9, 10<br>11             | 0,  | 1.5          |                | 1.5         |           | 1.5       |          | 1.5  |                | <br> C1k.<br> Per. |

| Clock low to YMA low                              | <sup>t</sup> CLVML            | i                                                                                                                                                                                                                                     |                    | 10        |                  | 9, 1<br>11              | 0,  |              | 80             |             | 70        |           | 70       |      | 70             | l ns               |

| Clock low to E<br>transition                      | <sup>‡</sup> CLET             |                                                                                                                                                                                                                                       | 1                  | <b>41</b> |                  | 9, 1<br>11              | 0,  |              | 85             |             | 70        | <br> <br> | 55       |      | 45             | l ns               |

| E output rise and fall time                       | tEr, f                        | <br> <br> -                                                                                                                                                                                                                           | 1                  | 42        | 10/              | 9, 1<br>11              | 0,  |              | 25             |             | 25        |           | 25       |      | 25             | ns                 |

| VMA low to E high                                 | tymLEH                        |                                                                                                                                                                                                                                       | <br>               | 43        | 10/              | 9, 1<br>11              | 0,  | 240          |                | 200         |           | 150       | <u> </u> | 90   | <br> <br>      | ns                 |

| AS, DS high to<br>VPA high                        | tshvph                        |                                                                                                                                                                                                                                       |                    | 44        | 10/              | 9, 1<br>11              | 0,  | 0            | 160            | 0           | 120       | 0         | 90       | 0    | 90             | ns                 |

| E Low to<br>address/VMA/FC<br>invalid             | telcai                        |                                                                                                                                                                                                                                       | <br> <br>          | 45        | 10/              | 9, 1<br>11              | 0,  | 35           | <br> <br> <br> | 30          |           | 10        |          | 10   | <br> <br> <br> | ns                 |

| BGACK width low                                   | <br> t <sub>GAL</sub><br>     | !<br>!                                                                                                                                                                                                                                | [<br>];<br><u></u> | 46        | <u>10</u> /      | 9, 1<br>11              | 0,  | 1.5          | !<br>!<br>!    | 1.5         | <br> <br> | 1.5       |          | 1.5  |                | <br> Clk.<br> Per. |

| Asynchronous input<br>setup/hold time             | tasi                          | <br>                                                                                                                                                                                                                                  | <br>               | 47        | 13/              | 9, 1<br>11              | 0,  | 25           | <br> <br>      | 20          | <br> <br> | 20        |          | 20   | <br>           | ns                 |

| BERR low to DTACK<br>low                          | <br>  <sup>t</sup> beldal<br> | <br>                                                                                                                                                                                                                                  | ]<br> -<br> -      | 48        | 10/<br>15/       | 9, 1<br>  11            | 0,  | <br>  25<br> |                | 20          |           | 20        |          | 20   | <br> <br> <br> | ns                 |

| E low to AS, DS<br>invalid                        | t <sub>SHEL</sub>             |                                                                                                                                                                                                                                       | Ţ                  | 49        | <u>10</u> /      | 9, 1                    | .0, | -80          | +80            | -70         | +70       | -55       | +55      | -45  | 45             | ns                 |

| E width high                                      | <sup>t</sup> EΗ               |                                                                                                                                                                                                                                       | 1                  | 50        | <u>10</u> /      | 9, 1                    | 10, | 600          |                | 450         |           | 350       |          | 280  | <br> <br>      | ns                 |

| E width low                                       | t <sub>EL</sub>               |                                                                                                                                                                                                                                       | <u> </u>           | 51        | 10/              | 9, 1                    | 10, | 900          |                | 700         |           | 550       |          | 440  |                | ns                 |

| E executed rise time                              | te ichx                       |                                                                                                                                                                                                                                       |                    |           | 10/<br>16/       | <br> 9 <sub>1</sub>   1 | ΙΟ, |              | <br>           |             | 1         |           |          | <br> | <br> <br> <br> | l ns               |

| See footnotes at e                                | nd of tab                     | le.                                                                                                                                                                                                                                   |                    |           |                  |                         |     | <u> </u>     | •              | *           | •         | •         | •        | •    | •              |                    |

| STAND<br>MILITAR                                  | ARDIZI                        |                                                                                                                                                                                                                                       | SIZE<br>A          |           | ·                |                         |     |              |                | <del></del> |           | 82        | 2021     |      |                |                    |

| DEFENSE ELECT                                     |                               | PPLY CENTER                                                                                                                                                                                                                           |                    | ا         | \ <del>.</del> _ | RE                      | VK  | SION         | EVEL           | Ε           |           | T         | SHEE     | т 8  | ,              |                    |

★ U. S. GOVERNMENT PRINTING OFFICE: 1968-549-904

| Test                                   | <br> Symbol          | Conditions 1/<br>  -55°C <tr<+110°c< th=""><th>Wave-<br/>form<br/>number</th><th>,</th><th>Dev<br/>type</th><th>e 01</th><th>Dev<br/>type</th><th>e 02</th><th>type</th><th>e 03</th><th>type</th><th></th><th>l<br/> <br/> Unii</th></tr<+110°c<> | Wave-<br>form<br>number | ,              | Dev<br>type  | e 01      | Dev<br>type | e 02           | type          | e 03        | type          |           | l<br> <br> Unii        |

|----------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------|--------------|-----------|-------------|----------------|---------------|-------------|---------------|-----------|------------------------|

|                                        |                      | 4.75 V≺VCC₹5.25 V<br>unless otherwise<br>specified                                                                                                                                                                                                 | (see<br> figure<br> 3)  | sub-<br>groups | Min          | Max       | Min         | Max            | <br> <br> Min | Max         | Min           | Max       |                        |

| Clock high to data out invalid         | ‡CHD0I               | GND = 0 V<br>C <sub>L</sub> = 130 pF                                                                                                                                                                                                               | 53 10/                  | 9, 10,<br>11   | 0            | <br>      | 0           | <br> <br>      | 0             |             | 0             | <br> <br> | l<br>ns                |

| E low to data out invalid              | tELDOI               | See figure 3<br>                                                                                                                                                                                                                                   | 54 2/<br>10/            | 9, 10,<br>11   | <br>  40<br> | <br>      | 30          | <br>           | <br>  20<br>  | <br>        | <br>  15 <br> | 1         | l ns                   |

| R∕W to data bus<br>impedance           | t <sub>RLDBD</sub>   |                                                                                                                                                                                                                                                    | 55 <u>10</u> /          | 9, 10,<br>11   | 35           |           | 30          | <br> <br>      | 20            | <br> <br>   | 10            |           | ns                     |

| Halt/RESET pulse<br>width              | <br>  thrpw<br> <br> |                                                                                                                                                                                                                                                    | 56 10/<br>15/17/        |                | 10           |           | 10          | <br> <br> <br> | 10            | ]<br>]<br>] | 10            | <br> <br> | <br> Clk.<br> Per.<br> |

| BGACK high to AS,<br>DS and R/W driven | tGASD                |                                                                                                                                                                                                                                                    | 57 10/                  | 9, 10,         | 1.5          |           | 1.5         |                | 1.5           |             | 1.5           |           | <br> Clk.<br> Per.     |

| BGACK high to FC,<br>VMA driven        | <sup>t</sup> GAFCD   |                                                                                                                                                                                                                                                    | 57A <u>10</u> /         | 9, 10,<br>11   | 1.0          |           | 1.0         | <br>           | 1.0           | !<br> <br>  | 1.0           |           | <br> C1k.<br> Per.     |

| BR high to AS, DS<br>and R/W driven    | t <sub>brhsd</sub>   |                                                                                                                                                                                                                                                    | 58 10/<br>  14/         | 9, 10,<br>11   | <br> 1.5<br> |           | 1.5         | <br> <br>      | <br> 1.5<br>  | <br> <br>   | 1.5           | <br> <br> | <br> Clk.<br> Per.     |

| BR high to FC, VMA                     | t <sub>brhfd</sub>   |                                                                                                                                                                                                                                                    | 58A10/<br> 157          | 9, 10,<br>11   | 1.0          | <br> <br> | 1.0         | <br>           | 1.0           |             | 1.0           |           | Clk.<br> Per.          |

$V_{CC} = 5 \text{ V } \pm 5\%$ . After  $V_{CC}$  has been applied for 100 ms.

All outputs unloaded except for load capacitance. Clock should be either 4 MHz or FMAX. Low; HALT, RST, (Part is held in reset). High; DTACK, BR, BGACK, IPLU-Z, VPA, BERR.

Guaranteed to the limits specified in table I, if not tested.

FC invalid, as a minimum, tested initially and for process and design changes only.

4/ 5/ 6/ For a loading capacitance of less than or equal to 50 picofarads, subtract 5 nanoseconds from the values given in the maximum column.

Not tested, for system design purposes only.

- Combined with the above parameter. Previous specification of 0 ns was theoretical and not attainable.

- Actual value depends on clock period.

As a minumum, tested initially and for process or design changes only. When  $\overline{\rm AS}$  and  $R/\overline{\rm W}$  are equally loaded (#20%), subtract 10 nanoseconds from the values given in these columns.

12/ Combined with 16, control bus specification.

13/ If the asynchronous setup time (47) requirements are satisfied, the DTACK low to data setup time (31) requirement can be ignored. The data must only satisfy the data-in to clock-low setup time (27) for the following cycle.

The processor will negate BG and begin driving the bus again if external arbitration logic negates  $\overline{BR}$  before asserting  $\overline{BGACK}$ . If 47 is satisfied for both  $\overline{DTACK}$  and  $\overline{BERR}$ , 48 may be 0 ns.

Deleted, useful only if E clock used to drive clock input on MC6809 Microprocessor.

For power up, the MPU must be held in RESET state for 100 ms to all stabilization of on chip circuitry. After the system is powered up, 56 refers to the minimum pulse width required to 17/ reset the system.

#### STANDARDIZED SIZE 82021 A MILITARY DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER** REVISION LEVEL SHEET Ε 9 DAYTON, OHIO 45444

DESC FORM 193A SEP 87

# U. S. GOVERNMENT PRINTING OFFICE: 1988-849-904

# NOTES:

Dimensions are in inches. 1.

Metric equivalents are given for general information only.

Positional tolerance for leads (68 places):

Ø .005 (0.13 mm)

4.

Manufacturers option, chamfer 0.15 max at  $45^{\circ}$ , all edges. There shall be a 0.20 inch minimum spacing between any 2 metallized areas on the surfaces of 5.

6. Increase maximum limit of pin diameter (Dø) by 0.003 inches when lead finish A is applied.

FIGURE 1. Dimensions and configurations.

DESC FORM 193A SEP 87

**★ U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904**

**☆ U. B. GOVERNMENT PRINTING OFFICE: 1988--550-547**

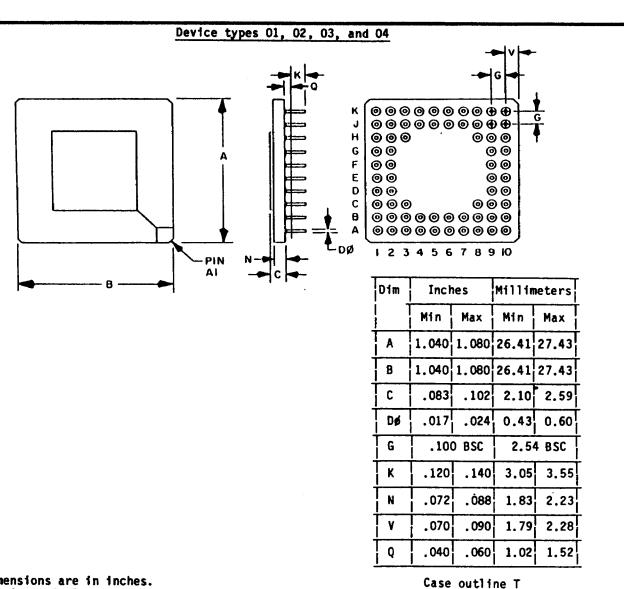

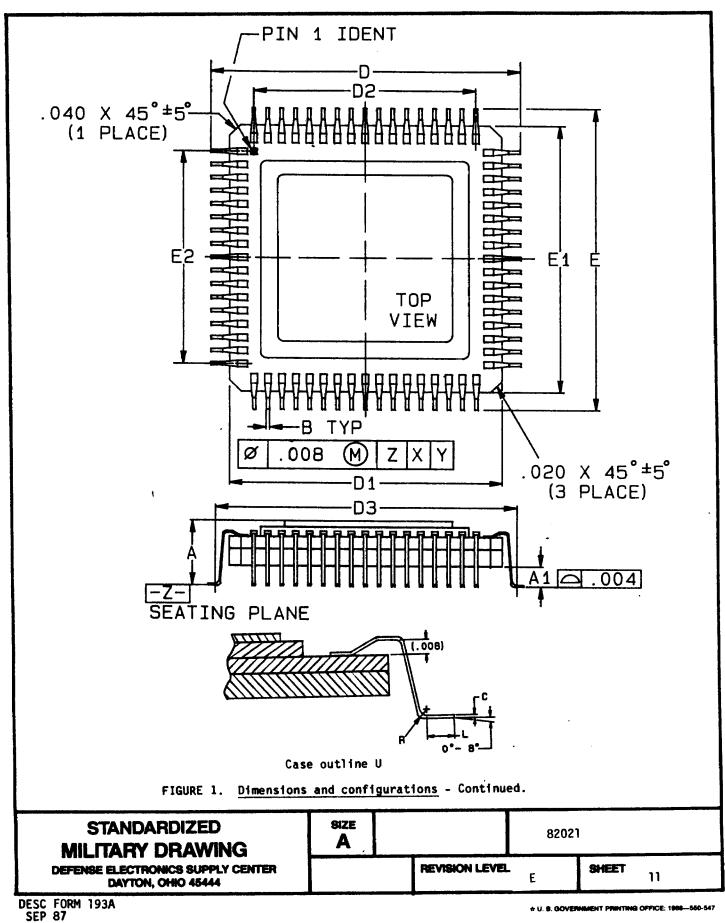

| Dim    | Inc   | hes    | Millim | eters |

|--------|-------|--------|--------|-------|

|        | Min   | in Max |        | Max   |

| A      |       | .135   |        | 3.42  |

| A1     | 0.015 | 0.038  | 0.38   | 0.96  |

| В      | 0.013 | 0.025  | 0.33   | 0.63  |

| С      | 0.004 | 0.010  | 0.10   | 0.25  |

| D, E   | 1.130 | 1.150  | 28.70  | 29.21 |

| D1, E1 | 0.935 | 0.960  | 27.74  | 24.38 |

| D2, E2 | .8    | 00     | 20.    | 32    |

| D3     | 1.0   | 1.080  |        | 43    |

| L      | .022  | .038   | 0.55   | 0.96  |

| R      | .0    | 12     | .0     | 30 I  |

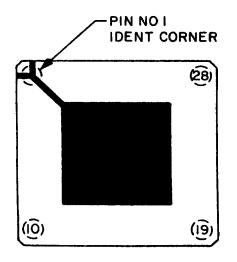

Case outline U - Continued.

# NOTE S:

- Dimensions are in inches.

Metric equivalents are given for general information only.

D<sub>2</sub> and E1 dimensions do not include particles of package material. Such particles shall not exceed .010 inch.

- 4. Maximum lead thickness includes all lead finishes. Minimum dimension is base material.

- 5. A pin one identification mark shall be located adjacent to pin one within the shaded area shown.

FIGURE 1. Dimensions and configurations - Continued.

SIZE **STANDARDIZED** Α MILITARY DRAWING 82021 **DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET DAYTON, OHIO 45444

DESC FORM 193A SEP 87

# U. S. GOVERNMENT PRINTING OFFICE: 1988-549-904

# Device types 01, 02, 03, and 04

|   | 10  | 9   | 8 | 7        | 6           | 5        | 4       | 3   | 2      | 1   |   |

|---|-----|-----|---|----------|-------------|----------|---------|-----|--------|-----|---|

| 1 |     |     |   |          |             |          | @       |     |        |     | A |

|   |     | (e) |   | ၜ        | <b>(9</b> ) | <b>©</b> | 0       | (O) |        | _   | B |

|   | 0   | 0   |   | В        |             | TC       |         |     | 0      | 0   | D |

|   | (O) | (O) |   |          |             | SE       | •       |     | @<br>@ | (O) | E |

|   | 0   | 0   | _ |          | `.<br>_     | <u>T</u> | •       | _   | 0      | 0   | G |

|   |     | 0   | _ | <b>@</b> | 0           | <b>@</b> | 0       | _   | (O)    | _   | H |

|   | _   |     |   |          |             |          | <u></u> |     |        |     | K |

| Pin no.    | <u>Function</u> | Pin no.    | <u>Function</u> | Pin no.    | <u>Function</u> | Pin no. | <u>Function</u>  |

|------------|-----------------|------------|-----------------|------------|-----------------|---------|------------------|

| 1A         | Do not connect  | 9K         | A9              | 3 <b>A</b> | D1              | 9H      | A12              |

| 1B         | DTACK           | 10K        | Do not connect  | 2A         | ĀS              | 9G      | A15              |

| 10         | BGACK           | 10J        | A14             | 2B         | LDS             | 9F      | A18              |

| 10         | BR              | 10Н        | A16             | 2C         | BG              | 9E      | v <sub>cc</sub>  |

| 1E         | CLK             | 10G        | A17             | 2D         | V <sub>CC</sub> | 90      | GND              |

| 1 <i>F</i> | HALT            | 10F        | A19             | 2E         | GND             | 9C      | A23              |

| 1G         | VMA             | 10E        | A20             | 2F         | RESET           | 9B      | D14              |

| 1H         | <u>E</u>        | 10D        | A21             | 2G         | VPA             | 8B      | D11              |

| าง         | BERR            | 10C        | A22             | 2H         | TPL2            | 7B      | D9               |

| 1 K        | Do not connect  | 10B        | D15             | 2J         | TPLO            | 6B      | D6               |

| 2K         | FC2             | 10A        | D12             | 3J         | FCT             | 5B      | D3               |

| 3K         | FC0             | 9 <b>A</b> | D10             | 4J         | Do not connect  | 4B      | DØ               |

| 4K         | A1              | <b>8</b> A | D8              | 5J         | A2              | 3B      | <u>DØ</u><br>UDS |

| 5K         | A3              | 7A         | D7              | 6J         | A5              | 3C      | R/₩              |

| 6K         | A4              | 6A         | D5              | 73         | A8              | 3H      | TPLT             |

| 7K         | A6              | 5A         | D4              | 8J         | A10             | 8H      | A13              |

| 8K         | A7              | 4A         | D2              | 9J         | A11             | 8C      | D13              |

FIGURE 2. Terminal connections.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

82021

REVISION LEVEL

E

SHEET 13

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1967-549-098

Powered by ICminer.com Electronic-Library Service CopyRight 2003

Powered by ICminer.com Electronic-Library Service CopyRight 2003

☆ U.S. GOVERNMENT PRINTING OFFICE: 1967-549-096

★ U. S. GOVERNMENT PRINTING OFFICE: 1988-548-904

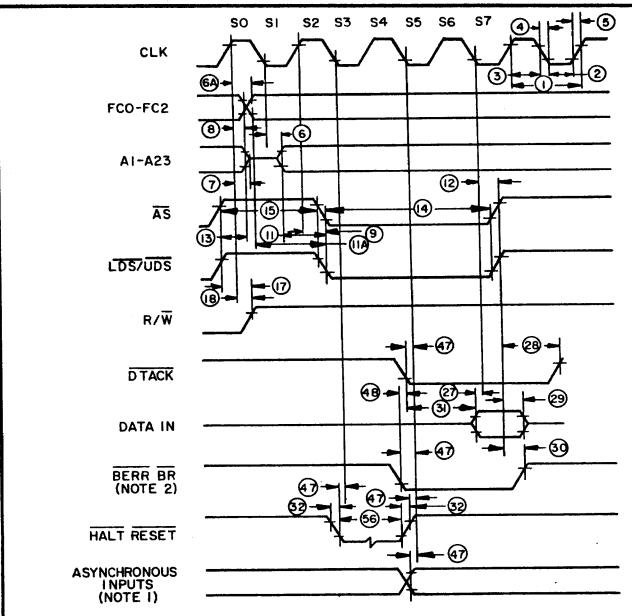

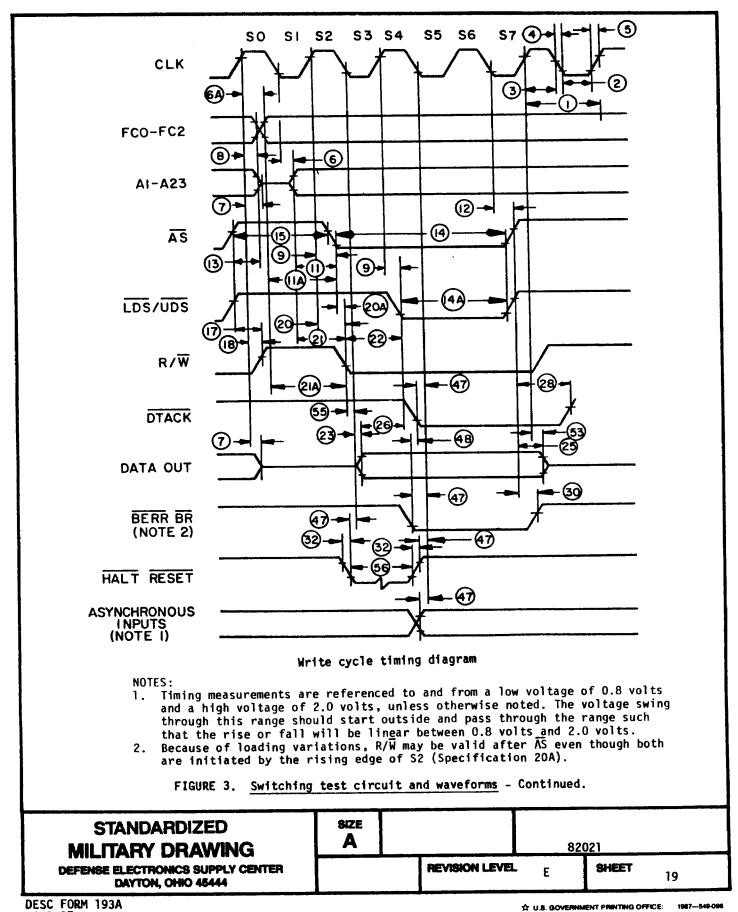

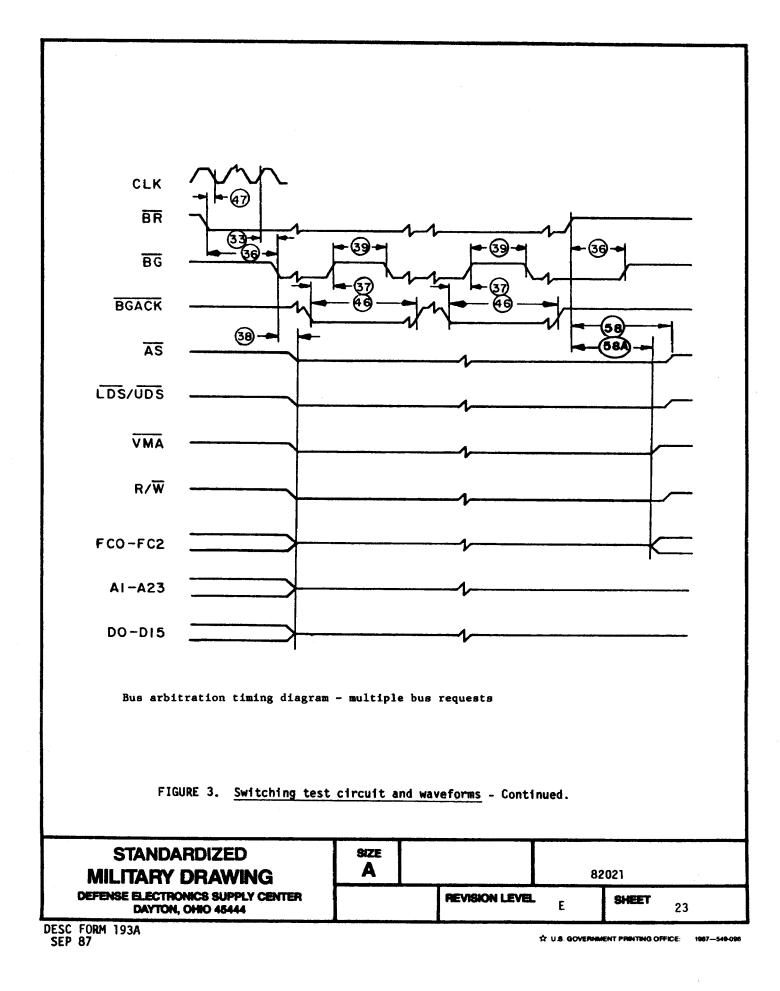

Read cycle timing diagram.

# NOTES:

- 1. Setup time for the asynchronous inputs BGACK, 1PLO-2, and VPA guarantees their recognition at the next falling edge of the clock.

- BR need fall at this time only to insure being recognized at the end of this bus cycle.

- 3. Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall will be linear between 0.8 and 2.0 volts.

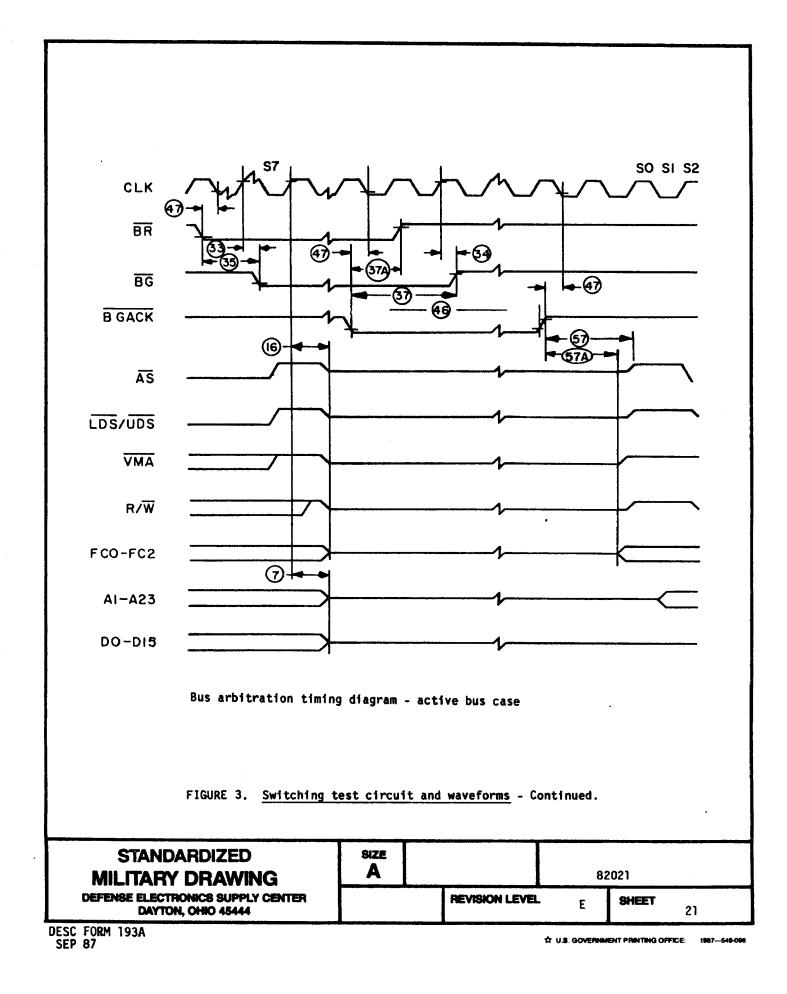

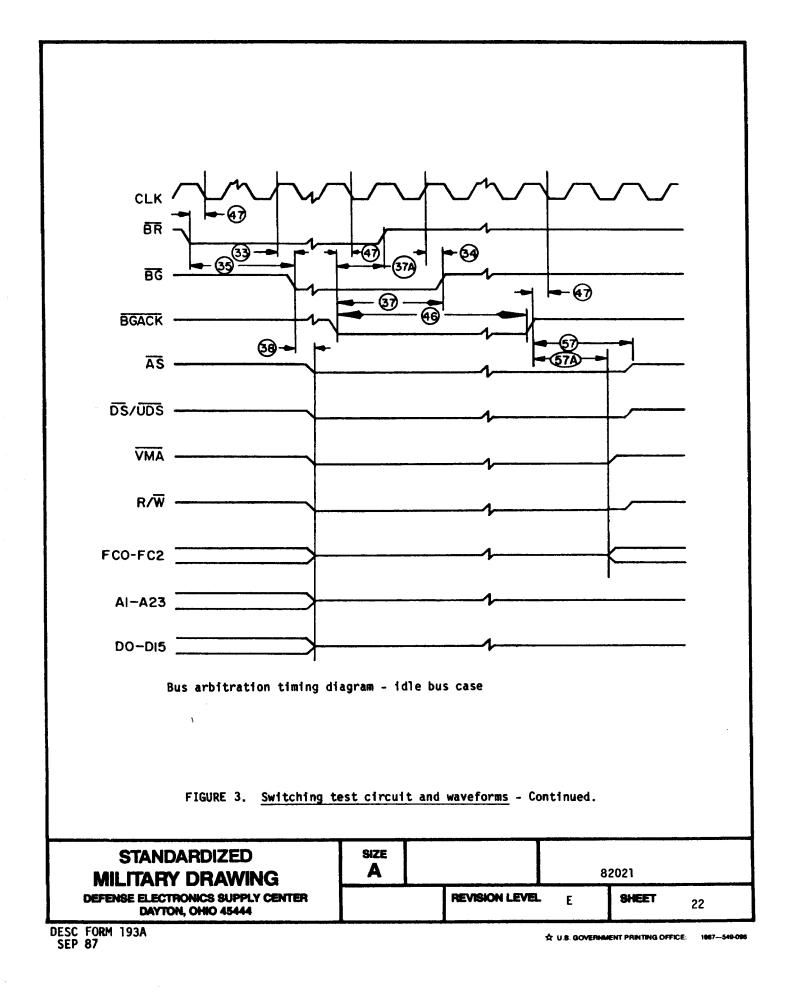

FIGURE 3. Switching test circuit and waveforms - Continued.

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1967--549-096

**SEP 87**

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987-549-096

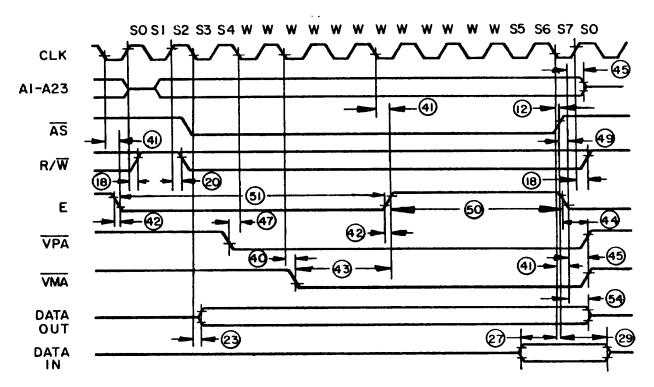

MO68000 to M6800 peripheral diagram - BPST case

NOTE: This timing diagram is included for those who wish to design their own circuit to generate  $\overline{\text{VMA}}$ . It shows the best case possibly attainable.

FIGURE 3. Switching test circuit and waveforms - Continued.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                  | 82021    |

|------------------------------------------------------|-----------|------------------|----------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL E | SHEET 20 |

DESC FORM 193A SEP 87

☆ U.B. GOVERNMENT PRINTING OFFICE: 1987--549-098

Powered by ICminer.com Electronic-Library Service CopyRight 2003

- 3.6 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7 herein). The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.7 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.9 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, D, or E using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.