# 5116S/L 2K x 8-BIT CMOS STATIC RAM

|                                              | 5116S-10 | 5116S-12 | Unit |

|----------------------------------------------|----------|----------|------|

| Address Access Time (t <sub>AA</sub> )       | 100      | 120      | ns   |

| Chip Select Access Time (t <sub>ACS</sub> )  | 100      | 120      | ns   |

| Output Enable Access Time (t <sub>OE</sub> ) | 40       | 50       | ns   |

- Static Operation

- No Clock/Refresh Required

- Equal Access and Cycle Times

Simplifies System Design

- Single +5V Supply

- Power Down Mode

- TTL Compatible

- Common Data Input and Output

- High Reliability 24-Pin 600 Mil PDIP Package

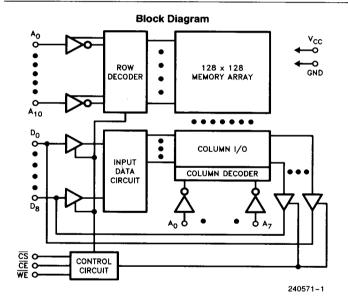

The 5116S is a 2048-word by 8-bit CMOS static RAM fabricated using CMOS Silicon Gate process.

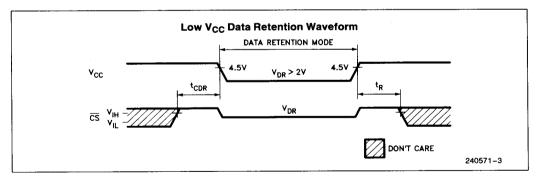

When the Chip Select is brought high, the device assumes a standby mode in which the standby current is reduced to 2  $\mu$ A (max). The 5116S has a data retention mode that guarantees that data will remain at minimum power supply voltage of 2.0V.

### Pin Connections 24 b v<sub>cc</sub> ᄻᆸ 23 A8 ᇯᅥ 22 Ag 21 1 WE 20 🗖 ŌĒ ᄱᄱ 19 🗖 🗛 18 🗖 CS $A_1 \square$ ᄱᅄ 17 07 ь**, Ц** 9 16 D<sub>6</sub> D<sub>1</sub> 10 15 D<sub>5</sub> D<sub>2</sub> 🗖 11 14 D D4 GND 12 13 D D 2 240571-2

## Pin Names

| Address Input       |

|---------------------|

| Data Input/Output   |

| Chip Select Input   |

| Write Enable Input  |

| Output Enable Input |

| Power               |

| Ground              |

|                     |

October 1989 Order Number: 240571-002

### **Device Operation**

The 5116S has two control inputs: Chip Select ( $\overline{CS}$ ) and Write Enable ( $\overline{WE}$ ).  $\overline{CS}$  is the power control pin and should be used for device operation.  $\overline{WE}$  is the data control pin and should be used to gate data at the I/O pins.

# Standby Power

The 5116S is placed in a standby or reduced power consumption mode by applying a high ( $V_{IH}$ ) to the  $\overline{\text{CS}}$  input. When in standby mode, the device is deselected and the outputs are in a high impedance state, independent of the  $\overline{\text{WE}}$  input.

Table 1. Mode Selection Truth Table

| CS | WE | ŌĒ | Mode    | 1/0              | Power   |

|----|----|----|---------|------------------|---------|

| Н  | Х  | Х  | Standby | High Z           | Standby |

| L  | L  | Х  | Write   | D <sub>IN</sub>  | Active  |

| L  | Н  | L  | Read    | D <sub>OUT</sub> | Active  |

| L  | Х  | Н  | Read    | High Z           | Active  |

### **Write Mode**

Write Cycles may be controlled by either  $\overline{WE}$  or  $\overline{CS}$ . In either case, both  $\overline{WE}$  and  $\overline{CS}$  must be high  $(V_{IH})$  during address transitions. During a  $\overline{WE}$  Controlled write cycle,  $\overline{CS}$  must be held low  $(V_{IL})$  while  $\overline{WE}$  is low. Address transfers occur on the falling edge of  $\overline{WE}$  and the data transfers on rising edge of  $\overline{WE}$ . During a  $\overline{CS}$  controlled cycle,  $\overline{WE}$  must be held low  $(V_{IL})$  while  $\overline{CS}$  is low. The addresses are then transferred on the falling edge of  $\overline{CS}$  and data on the rising edge of  $\overline{CS}$ . Data, in both cases, must be valid for a time  $t_{DW}$  before the controlling input is brought high  $(V_{IH})$  and remain valid for a time  $t_{DH}$  after the controlling input is high.

### **Read Mode**

$\overline{\text{CS}}$  must be low (V<sub>IL</sub>) and  $\overline{\text{WE}}$  must be high (V<sub>IH</sub>) to activate a read cycle and obtain data at the outputs. Given stable addresses, valid data is available after a time  $t_{AA}$ .

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Any Pin Relative                           |

|-------------------------------------------------------|

| to Ground ( $V_{IN}$ , $V_{OUT}$ ) – 0.3V to + 7V     |

| Storage Temperature (T <sub>stg</sub> )55°C to +150°C |

| Power Dissipation (PD)1.0W                            |

| DC Continuous Output Current (IOS)50 mA               |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

# **RECOMMENDED OPERATING CONDITIONS** Voltage referenced to V<sub>SS</sub>, T<sub>A</sub> = 0°C to 70°C

| Symbol          | Parameter          | Min  | Тур | Max                  | Unit |

|-----------------|--------------------|------|-----|----------------------|------|

| V <sub>CC</sub> | Supply Voltage     | 4.5  | 5.0 | 5.5                  | V    |

| V <sub>SS</sub> | Ground             | 0    | 0   | 0                    | V    |

| V <sub>IH</sub> | Input High Voltage | 2.2  |     | V <sub>CC</sub> +0.3 | ٧    |

| V <sub>IL</sub> | Input Low Voltage  | -0.3 |     | 0.8                  | V    |

NOTE:

# CAPACITANCE T<sub>A</sub> = 25°C, f = 1.0 MHz

| Symbol           | Parameter                                  | Min | Max | Unit |

|------------------|--------------------------------------------|-----|-----|------|

| C <sub>IN1</sub> | Input Capacitance (V <sub>IN</sub> = 0V)   |     | 6   | pF   |

| C <sub>OUT</sub> | Output Capacitance (V <sub>OUT</sub> = 0V) |     | 8   | pF   |

NOTE:

This parameter is sampled and not 100% tested.

<sup>1.</sup> During transitions, the inputs may undershoot to -3.5V for periods less than 20 ns.

### D.C. AND OPERATING CHARACTERISTICS

Recommended Operating Conditions unless otherwise noted

| Symbol           | Parameter                          |           | Min | Тур  | Max | Units | Test Conditions                                                                                                                        |

|------------------|------------------------------------|-----------|-----|------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>CC1</sub> | Operating Current  Dynamic Current |           |     | 30   | 40  | mA    | V <sub>CC</sub> = Max, $\overline{\text{CS}}$ = V <sub>IL</sub><br>Outputs open                                                        |

| lcc2             |                                    |           |     | 30   | 60  | mA    | T <sub>cyc</sub> = Min, V <sub>CC</sub> = Max<br>Outputs open                                                                          |

| I <sub>SB</sub>  |                                    |           |     |      | 3   | mA    | CS = V <sub>IH</sub>                                                                                                                   |

| I <sub>SB1</sub> | Standby<br>Current                 | STD       |     | 4    | 50  | μΑ    | $\overline{\text{CS}} \ge V_{\text{CC}} - 0.2V$                                                                                        |

|                  |                                    | L         |     | 0.2* | 2   | ] "   | $V_{IN} = GND \text{ to } V_{CC}$                                                                                                      |

| ILI              | Input Load Current                 |           | -1  |      | 1   | μΑ    | $V_{CC} = Max$ $V_{IN} = GND \text{ to } V_{CC}$                                                                                       |

| l <sub>LO</sub>  | Output Leakage                     |           | 1   |      | 1   | μА    | $\overline{\text{CS}} = \text{V}_{\text{IH}}, \text{V}_{\text{CC}} = \text{Max}$ $\text{V}_{\text{OUT}} = \text{GND to V}_{\text{CC}}$ |

| V <sub>OH</sub>  | Output High Voltage                |           | 2.4 |      |     | V     | $I_{OH} = -1.0 \text{ mA}$                                                                                                             |

| V <sub>OL</sub>  | Output Low                         | / Voltage |     |      | 0.4 | ٧     | I <sub>OL</sub> = 2.1 mA                                                                                                               |

<sup>\*</sup>T<sub>A</sub> = 25°C

# DATA RETENTION ELECTRICAL CHARACTERISTICS

| Symbol           | Parameter                               | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Min             | Тур  | Max | Units |

|------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----|-------|

| V <sub>CDR</sub> | Voltage for Data Retention              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2               |      |     | V     |

| ICCDR            | Data Retention Current                  | $eq:continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous$ |                 | 0.05 | 2   | μА    |

| t <sub>CDR</sub> | Chip Deselect to<br>Data Retention Time |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0               |      |     | ns    |

| t <sub>R</sub>   | Operation Recovery Time                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t <sub>RC</sub> |      |     | ns    |

| A.C. TEST CONDITIONS            | Timing Reference Level          |

|---------------------------------|---------------------------------|

| Input Pulse Levels 0.8V to 2.4V | Output Load 1 TTL Load + 100 pF |

| Input Rise and Fall Times       |                                 |

# A.C. CHARACTERISTICS $T_A = 0^{\circ}C$ to $70^{\circ}C,\,V_{CC} = 5V\,\pm10\%$

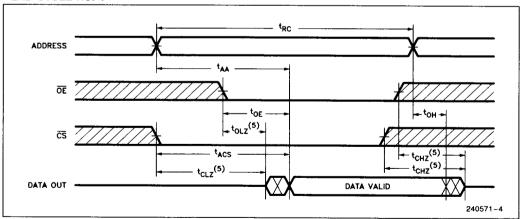

### **READ CYCLE**

| Symbol           | Parameter                               | 5110 | 6S-10 | 5116 | SS-12 | Unit |

|------------------|-----------------------------------------|------|-------|------|-------|------|

|                  | 1 2.4                                   | Min  | Max   | Min  | Max   | Onit |

| t <sub>RC</sub>  | READ Cycle Time                         | 100  |       | 120  |       | ns   |

| t <sub>AA</sub>  | Address Access Time                     |      | 100   |      | 120   | ns   |

| tACS             | Chip Select Access Time                 |      | 100   |      | 120   | ns   |

| tон              | Output Hold from<br>Address Change      | 10   |       | 10   |       | ns   |

| <sup>t</sup> CLZ | Chip Selection to<br>Output in Low Z    | 10   |       | 10   | -     | ns   |

| t <sub>CHZ</sub> | Chip Deselection to<br>Output in High Z | 0    | 40    | 0    | 40    | ns   |

| t <sub>OE</sub>  | Output Enable<br>Access Time            | 40   |       | 50   |       | ns   |

| t <sub>OLZ</sub> | Output Enable to<br>Output in Low Z     | 10   |       | 10   |       | ns   |

| tонz             | Output Enable to<br>Output in High Z    | 0    | 40    | 0    | 40    | ns   |

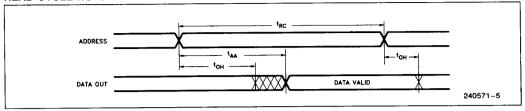

# READ CYCLE NO. 1(1)

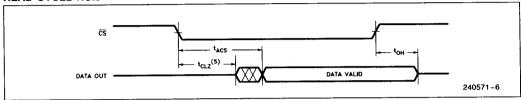

### **READ CYCLE NO. 2**(1, 2, 4)

### **READ CYCLE NO.3(1, 3, 4)**

- 1. WE is high for READ Cycle. The first transitioning address.

2. Device is continuously selected;  $\overline{CS} = V_{\parallel L}$ .

3. Address valid prior to or coincident with  $\overline{CS}$  transition low.

- 4.  $\overline{OE} = V_{IL}$ .

- 5. Transition is measured at  $\pm$  500 mV from steady state voltage.

# A.C. CHARACTERISTICS $T_A = 0$ °C to 70°C, $V_{CC} = 5V \pm 10$ % (Continued)

### WRITE CYCLE

| Symbol          | Parameter                             | 5116 | S-10 | 5116S-12 |     | Unit |

|-----------------|---------------------------------------|------|------|----------|-----|------|

|                 | raidilletei                           | Min  | Max  | Min      | Max |      |

| twc             | WRITE Cycle Time                      | 100  |      | 120      |     | ns   |

| t <sub>CW</sub> | Chip Selection to<br>End of Write     | 65   |      | 70       |     | ns   |

| t <sub>AW</sub> | Address Valid to<br>End of Write      | 80   |      | 105      |     | ns   |

| tas             | Address Set-Up Time                   | 0    |      | 0        |     | ns   |

| t <sub>WP</sub> | Write Pulse Width                     | 60   |      | 70       |     | ns   |

| twR             | Write Recovery Time                   | 10   |      | 10       |     | ns   |

| t <sub>DW</sub> | Data Valid to End of Write            | 30   |      | 35       |     | ns   |

| t <sub>DH</sub> | Data Hold Time                        | 10   |      | 10       |     | ns   |

| twHZ            | Write Enable to<br>Output in High Z   | 0    | 30   | 0        | 35  | ns   |

| tow             | Output Active from<br>End of Write    | 10   |      | 10       |     | ns   |

| tонz            | Output Disable to<br>Output in High Z | 0    | 40   | 0        | 40  | ns   |

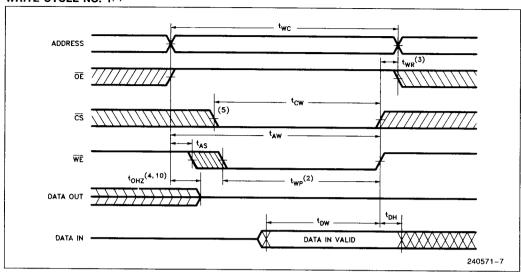

### WRITE CYCLE NO. 1(1)

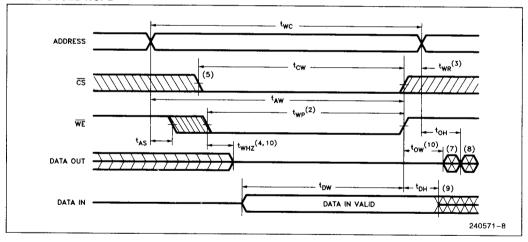

### WRITE CYCLE NO. 2(1, 6)

### NOTES:

- 1. WE must be high during address transitions.

- 2. A Write occurs during the overlap (twp) of a low CS and a low WE.

- 3. All Write Cycle timings are referenced from the last valid address to the first transitioning address.

- 4. During this period, I/O pins are in tri-state.

- 5. If the CS low transition occurs simultaneously with the WE low transitions or after the WE transition, outputs remain in tristate.

- 6.  $\overline{OE}$  is continuously low ( $\overline{OE} = V_{IL}$ ).

- 7. DOUT is the same phase of write data on this write cycle.

- 8. Dour is the read data of next address.

9. If CS is low during this period, I/O pins are in output state.

- 10. Transition is measured at ±500 mV from steady state voltage.

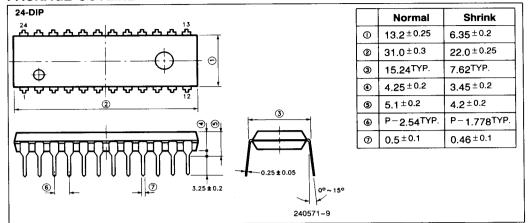

# **PACKAGE OUTLINE**