|                                                        |                                                                                                                                             |                                |      |        |           |                 |      |     | RE   | VISK | ONS | ;           |          |      |            |             |                   |                  |                    |                   |      |     |     |    |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|--------|-----------|-----------------|------|-----|------|------|-----|-------------|----------|------|------------|-------------|-------------------|------------------|--------------------|-------------------|------|-----|-----|----|

| LTR                                                    |                                                                                                                                             |                                |      |        |           | ESC             | RIPT | ION |      |      | -   |             |          |      |            |             | DATE              | (YR-             | MO-D               | A)                | AP   | PRO | VED |    |

| A Rev                                                  | ise t                                                                                                                                       | able                           | I co | nditi  | ons.      | Ma              | ke e | dit | oria | al c | han | jes.        |          |      |            |             | 1985              | NO               | V 15               |                   | W,   | Ø., | 41  | ,  |

| Cha                                                    | Convert to military drawing format. Changes to 1.3 and 1.4<br>Changes to table I. Vendor CAGE 34649 added. Editorial<br>Changes throughout. |                                |      |        |           |                 |      |     |      | 4.   |     | 1987 MAY 21 |          |      |            | M.A. Syc    |                   |                  | 2                  |                   |      |     |     |    |

| Cha                                                    | Remove vendor CAGE 34649 from device 01. Add device 02. Changes to absolute max ratings. Change drawing CAGE. Editorial changes throughout. |                                |      |        |           |                 |      |     |      |      | W   | d.          | 2        | 1    |            |             |                   |                  |                    |                   |      |     |     |    |

|                                                        |                                                                                                                                             |                                |      |        |           |                 |      |     |      |      |     |             |          |      |            |             |                   |                  |                    |                   |      |     |     |    |

| CURF                                                   | REN                                                                                                                                         | ΤC                             | AG   | ΕC     | 30:       | DΕ              | 67   | 26  | 8    |      |     |             |          |      |            | -           |                   |                  |                    |                   |      |     |     |    |

| CURF                                                   | REN                                                                                                                                         | тс                             | AG   | ΕC     | :O[       | DΕ              | 67   | 26  | 8    |      |     |             |          |      |            | •           |                   |                  |                    |                   |      |     |     |    |

| REV                                                    | REN                                                                                                                                         | тс                             | AG   | E C    | :OI       | Œ               | 67   | 26  | 8    |      |     |             | :        |      |            |             |                   |                  |                    |                   |      |     |     |    |

| REV                                                    | REN                                                                                                                                         | тс                             | AG   | EC     | OI        | Œ               | 67   | 26  | 8    |      |     |             |          |      |            |             |                   |                  |                    |                   |      |     |     |    |

| REV<br>SHEET<br>REV                                    | REN                                                                                                                                         | тс                             | AG   | ΕC     | OI        | Œ               | 67   | 26  |      |      |     |             |          |      |            | -           |                   |                  |                    |                   |      |     |     |    |

| REV SHEET REV SHEET REV STATU                          | s                                                                                                                                           | REV                            |      | C      | c         | В               | C    | С   | В    | В    | C   | В           | <u> </u> | В    | В          | В В         | В                 | C                | <u> </u>           | C 17              |      |     |     |    |

| REV<br>SHEET                                           | s                                                                                                                                           |                                |      | C 1    | C 2       | B 3             | C 4  | С   |      | B 7  | C 8 | B 9         | _        | _    | B 12       | _           | B<br>14           |                  | B<br>16            | <u> </u>          |      |     |     |    |

| REV SHEET REV SHEET REV STATU OF SHEETS                | s<br>s                                                                                                                                      | REV                            | īT   | C 1 PR | C 2       | B 3             | C 4  | С   | В    | +-   | -   | <u> </u>    | 10       | 11   | -          | 13          | 14                | 15<br>NIC        | 16<br>s su         | 17<br>PPLY        | 'CEM | TER |     |    |

| REV SHEET REV SHEET REV STATU OF SHEET: PMIC N/A STANI | S S S S S S S S S S S S S S S S S S S                                                                                                       | REV<br>SHE<br>DIZE<br>RY<br>NG | ET D | C 1 PR | C 2 EPARE | B<br>3<br>ED BY | C 4  | С   | В    | +-   | -   | 9<br>M      | 10       | DEFE | 12<br>ENSE | ELEC<br>DAY | 14<br>CTRC<br>TON | 15<br>NIC<br>OHI | 16<br>S SU<br>O 45 | 17<br>PPLY<br>444 |      |     |     | VE |

DESC FORM 193-1 SEP 87

| SCOPE |

|-------|

|       |

|       |

1.1 Scope. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-833, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

1.2 Part number. The complete part number shall be as shown in the following example:

1.2.1 Device type. The device type shall identify the circuit function as follows:

| Device type | Generic number | Frequency | Circuit                                                                       |

|-------------|----------------|-----------|-------------------------------------------------------------------------------|

| 01          | 82C84A         | 25 MHz    | CMOS monolithic clock generator driver CMOS monolithic clock generator driver |

| 02          | 82C84A         | 25 MHz    |                                                                               |

1.2.2 Case outlines. The case outlines shall be as designated in appendix C of MIL-M-38510, and as follows:

Outline letter

### Case outline

p D-6 (18-lead, .960" x .310" x .200"), dual-in-line package

C-2 (20-terminal, .358" x .358" x .100"), square chip carrier package

1.3 Absolute maximum ratings.

1.4 Recommended operating conditions.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

SIZE A 84068

REVISION LEVEL C SHEET 2

### 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

**MILITARY**

MIL-M-38510

- Microcircuits, General Specification for.

STANDARD

**MILITARY**

MIL-STD-883

Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

### 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

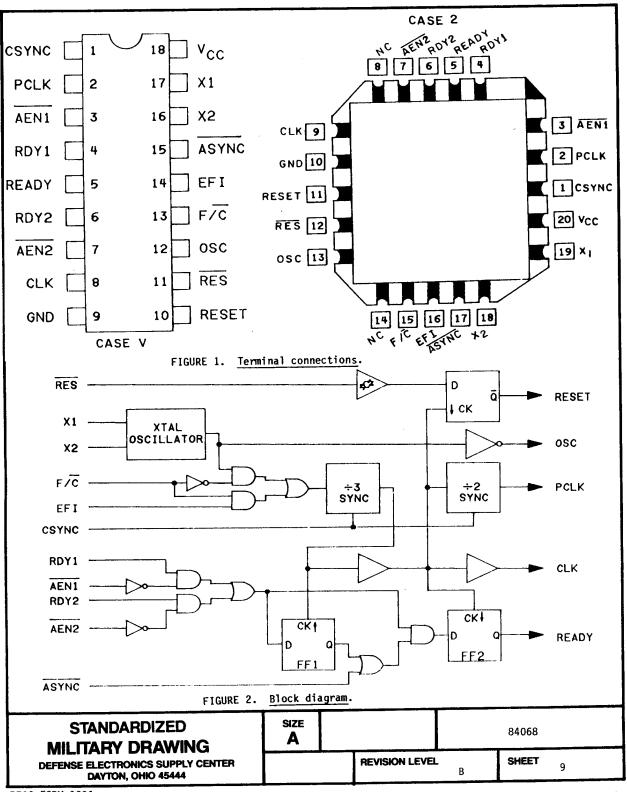

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1.

- 3.2.2 Logic diagram. The logic diagram shall be as specified on figure 2.

- 3.2.3 <u>Case outlines</u>. The case outlines shall be in accordance with 1.2.2 herein.

- 3.3 Electrical performance characteristics. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.5 herein.

- 3.5 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.5. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |          |                |   | 84068   |

|------------------------------------------------------|------------------|----------|----------------|---|---------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | -                | <u>-</u> | REVISION LEVEL | В | SHEET 3 |

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.8 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 ( $C_{\mbox{IN}}$  and  $C_{\mbox{OUT}}$  measurements) shall be measured only for the initial test and after process or design changes which may affect capacitance.

- d. Subgroups 7 and 8 shall consist of verifying the functionality of the device. It forms a part of the vendor's test tape and shall be maintained and available from the approved sources of supply.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                |     | 84068   |  |

|------------------------------------------------------|-----------|----------------|-----|---------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | · c | SHEET 4 |  |

DESC FORM 193A SEP 87

|                            | TABLE                                 | I. Elect                                                       | rical performance                                             | characte             | ristics.                  |                      |                |                  |

|----------------------------|---------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------|----------------------|---------------------------|----------------------|----------------|------------------|

| Parameter                  | Symbol                                | Ţ                                                              | Conditions                                                    | Dovice               | I Group A                 | Limi                 | ts             | <br>  Unit       |

| rarameter                  | Symbol                                | -55°C                                                          | Conditions<br><u>≺</u> T <sub>C</sub> <u>≺</u> +125°C         | Device<br>  type<br> | Group A<br> subgroups<br> | Min                  | Max            | Unit             |

| Input high voltage         | v <sub>IH</sub>                       | V <sub>CC</sub> = 5.                                           | 5 V <u>1</u> / <u>2</u> /                                     | A11                  | 1, 2, 3                   | 2.2                  |                | )<br>  V<br>     |

| Input low voltage          | VIL                                   | V <sub>CC</sub> = 4.                                           | 5 V <u>1</u> / <u>2</u> / <u>3</u> /                          | A11                  | 1, 2, 3                   | <br>   <br>          | 0.8            | V                |

| Output high voltage        | v <sub>OH</sub>                       | $ I_{OH}  = -4$<br>$ I_{OH}  = -2$<br>$ V_{CC}  = 4$ .         | .0 mA CLK output<br>.5 mA all others<br>5 V 4/                | A11<br> <br>         | <br>  1, 2, 3<br> <br>    | V <sub>CC</sub> -0.4 |                | <br>  V<br> <br> |

| Output low voltage         | V <sub>OL</sub>                       |                                                                | .0 mA CLK output<br>.5 mA all others<br>5 V 4/                | <br>  A11<br>        | 1, 2, 3                   | <br> <br> <br> <br>  | 0.4            | V                |

| Reset input high voltage   | VIHR                                  | V <sub>CC</sub> = 5.                                           | 5 V                                                           | A11                  | 1, 2, 3                   | V <sub>CC</sub> -0.8 |                | V<br> <br>       |

| Reset input low voltage    | V <sub>ILR</sub>                      | V <sub>CC</sub> = 4.                                           | 5 V                                                           | <br>  A11<br>        | 1, 2, 3                   | <br>                 | 0.5            | <br>  V<br>      |

| Reset input<br>hysteresis  | <br> V <sub>T+</sub> -V <sub>T-</sub> | V <sub>CC</sub> = 4.                                           | 5 V and 5.5 V                                                 | 01                   | 1, 2, 3                   | .2 V <sub>CC</sub>   |                | ] V              |

|                            |                                       |                                                                |                                                               | 02                   | ]                         | 100                  | · ·            | l mV             |

| Input leakage<br>current   | IIIL                                  | V <sub>IN</sub> = 0<br>does not<br>V <sub>CC</sub> = 5.        | V or V <sub>CC</sub> ,<br>include ASYNC, X1<br>5 V <u>5</u> / | A11                  | 1, 2, 3                   | -1.0                 | 1.0            | μ <b>A</b>       |

| Power supply current       | ICC                                   | V <sub>CC</sub> = 5.<br> Crystal<br> Outputs                   |                                                               | A11<br>              | 1, 2, 3                   |                      | 40             | mA               |

| Input capacitance          | CIN                                   | $ T_{C} = +25$                                                 | y = 1 MHz                                                     | <br>  A11<br>        | <br>  4<br>               |                      | 10             | pF               |

| Output capacitance         | IC <sub>OUT</sub>                     | V <sub>CC</sub> = GN<br> V <sub>IN</sub> = +5<br> See 4.3.<br> | D = O V<br>V or GND                                           | <br> <br> <br>       | 4<br>  4<br>              |                      | 15             |                  |

| Functional tests           | <br> <br> <br>                        | <br> See 4.3.                                                  | 1d                                                            | <br>  A11<br>        | 7,8                       |                      |                |                  |

| See footnotes at end       | of table.                             | 1                                                              |                                                               | 1                    | <u> </u>                  | <u>I</u>             |                | <u> </u>         |

| STANDAF<br>MILITARY D      |                                       | <u>.</u>                                                       | SIZE<br>A                                                     |                      |                           | 84068                |                |                  |

| DEFENSE ELECTRON DAYTON, O | ICS SUPPLY CI                         |                                                                | R                                                             | EVISION LE           | VEL C                     | SHEET                | r <sub>5</sub> |                  |

|                                        | TABLE I.            | Electrical performance o                                                                                                                                                                                                                                                                          | haracteri       | istics - Cor         | itinued.                                      |              |                |                        |

|----------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|-----------------------------------------------|--------------|----------------|------------------------|

| Parameter                              | Symbol              | Conditions $\begin{array}{c c} & \text{Conditions} \\ -55^{\circ}\text{C} < \text{T}_{\text{C}} < +125^{\circ}\text{C} \\ & \text{V}_{\text{CC}} = 4.5 \text{ V} \\ & \text{unless otherwise} \\ & \text{specified} \\ & \underline{7}/\underline{8}/\underline{9}/\\ & \\ & \\ & \\ \end{array}$ | Figure<br>  no. | Reference<br>no. 10/ | <br> Group A<br> subgroups<br> <br> <br> <br> | 1            | Max            | Unit                   |

| External frequency<br>HIGH time        | t <sub>EHEL</sub>   | <br>  90% - 90% V <sub>IN</sub> <u>11</u> /                                                                                                                                                                                                                                                       | 3               | 1                    | <br> 9,10,11<br>                              | 13           |                | ns                     |

| External frequency<br>LOW time         | teleh               | 10% - 10% V <sub>IN</sub> 11/                                                                                                                                                                                                                                                                     | 3               | 2                    | 9,10,11                                       | 13           | <br> <br>      | [<br> <br> <br>        |

| EFI period                             | telel               | 11/                                                                                                                                                                                                                                                                                               | 3               | 3                    | 9,10,11                                       | <br>  36<br> | <br> <br>      | <br> <br>              |

| XTAL frequency                         |                     | 12/                                                                                                                                                                                                                                                                                               |                 |                      |                                               | 2.4          | <br>  25<br>   | MHz                    |

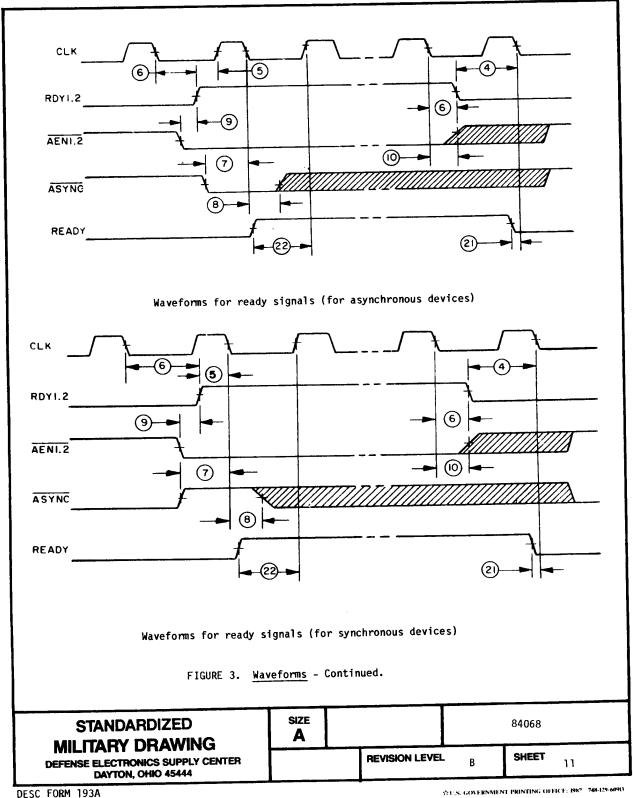

| RDY1, RDY2 active<br>setup to CLK      | t <sub>R1VCL</sub>  | ASYNC = HIGH $\frac{11}{2}$                                                                                                                                                                                                                                                                       | 3               | 4                    | <br> 9,10,11<br>                              | 35           | <br> <br> <br> | <br>  ns<br>           |

| RDY1, RDY2 active<br>setup to CLK      | t <sub>R1VCH</sub>  | ASYNC = LOW                                                                                                                                                                                                                                                                                       | 3               | 5                    | T<br> <br> <br>                               | 35           | <br> <br> <br> | <br> <br>              |

| RDY1, RDY2<br>inactive setup<br>to CLK | t <sub>R1</sub> vcl |                                                                                                                                                                                                                                                                                                   | 3               | 4                    | <br>                                          | 35           |                | !<br> <br> <br> <br> - |

| RDY1, RDY2 hold to                     | t <sub>CLR1X</sub>  | 11/                                                                                                                                                                                                                                                                                               | 3               | 6                    | <br>                                          | 0            | <br> <br> <br> | <br>                   |

| ASYNC setup to CLK                     | tayvcl              |                                                                                                                                                                                                                                                                                                   | 3               | 7                    |                                               | 50           |                | <br> <br>              |

| ASYNC hold to CLK                      | tCLAYX              |                                                                                                                                                                                                                                                                                                   | 3               | 8                    | T<br> <br>                                    | 0            | <br> <br>      | <br> <br><u> </u>      |

| AEN1, AEN2 setup<br>to RDY1, RDY2      | t <sub>A1VR1V</sub> |                                                                                                                                                                                                                                                                                                   | 3               | <br>  9<br>          | <br> <br> <br> -                              | 15           | <br> <br> <br> | <br> <br> <br> -       |

| AEN1, AEN2 hold<br>to CLK              | t <sub>CLA1X</sub>  | 11/                                                                                                                                                                                                                                                                                               | 3               | 10                   |                                               | 0            | <br>           | <br> <br> <br>         |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                |   | 84068   |  |

|------------------------------------------------------|-----------|----------------|---|---------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | В | SHEET 6 |  |

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987--549-096

|                                    |                                 | Electrical performance c  Conditions                                                                                                                                |             |                   |                                     | Limits                                   |              | r                    |

|------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|-------------------------------------|------------------------------------------|--------------|----------------------|

| Parameter                          | <br>  Symbol<br> <br> <br> <br> | conditions $-55^{\circ}\text{C} \leq T_{\text{C}} \leq +125^{\circ}\text{C}$ $V_{\text{CC}} = 4.5 \text{ V}$ unless otherwise specified $\frac{7}{8} = \frac{8}{9}$ | l no.       |                   | Group A<br> subgroups<br> <br> <br> | Min                                      |              | Unit                 |

| CSYNC setup to<br>EFI              | <br> tyHEH<br>                  |                                                                                                                                                                     | <br>  3<br> | <br>  11<br> <br> | <br> 9,10,11<br> <br>               | <br>  20                                 |              | <br>  ns<br> <br>    |

| CSYNC hold to EFI                  | t <sub>EHYL</sub>               |                                                                                                                                                                     | 3           | 12                | T<br> <br>                          | 20                                       |              | T<br> <br>           |

| CSYNC width                        | i<br>t <sub>YHYL</sub>          | 11/                                                                                                                                                                 | 3           | 13                | <br> <br><u> </u>                   | 2 t <sub>ELEL</sub>                      |              | <br> <br> -          |

| RES setup to CLK                   | t <sub>I1HCL</sub>              | 13/                                                                                                                                                                 | 3           | 14                |                                     | 65                                       |              | <br> <br>            |

| RES hold to CLK                    | tCLI1H                          | 11/ 13/                                                                                                                                                             | 3           | 15                | [<br> <br><u> </u>                  | 20                                       |              | <u> </u>             |

| CLK cycle period                   | ‡CLCL                           | 11/                                                                                                                                                                 | 3           | 16                | <br>                                | 125                                      |              | <br> <br> <br>       |

| CLK HIGH time                      | t <sub>CHCL</sub>               | 11/                                                                                                                                                                 | 3,4,5       | <br>  17<br>      | [<br>]<br>[                         | <br> (1/3t <sub>CLCL</sub> ) <br> +2.0   |              | <br> <br> <br>       |

| CLK LOW time                       | t <sub>CLCH</sub>               | 11/                                                                                                                                                                 | 3,4,5       | 18                | †<br> <br> -                        | (2/3t <sub>CLCL</sub> )                  |              | T<br> <br> <br> <br> |

| PCLK HIGH time                     | t <sub>PHPL</sub>               | 11/                                                                                                                                                                 | 3           | 19                | Ť<br> <br>                          | t <sub>CLCL</sub> -20                    |              | T<br> <br>!          |

| PCLK LOW time                      | t <sub>PLPH</sub>               | 11/                                                                                                                                                                 | 3           | 20                |                                     | t <sub>CLCL</sub> -20                    |              | <br> <br>            |

| Ready inactive to CLK 14/          | t <sub>RYLCL</sub>              | 11/                                                                                                                                                                 | 3,5,7       | <br>  21<br>      | <br> <br>                           | <br>  -8<br>                             |              | <br>                 |

| Ready active to<br>CLK <u>15</u> / | t <sub>RYHCH</sub>              | 11/                                                                                                                                                                 | 3,6,7       | <br>  22<br>      | <br> <br> <br>                      | <br> (2/3t <sub>CLCL</sub> )<br> -15<br> |              | !<br>                |

| CLK to reset<br>delay              | tCLIL                           |                                                                                                                                                                     | 3           | 23                |                                     | <br> <br> <br>                           | <br>  40<br> |                      |

| CLK to PCLK HIGH<br>delay          | t <sub>CLPH</sub>               |                                                                                                                                                                     | 3           | 24                | T<br> <br>                          |                                          | 22           | <br> <br> <br>       |

| See footnotes at e                 | end of tab                      | le.                                                                                                                                                                 |             |                   |                                     |                                          |              |                      |

| STANDA<br>MILITARY                 |                                 |                                                                                                                                                                     |             |                   |                                     | 84068                                    |              |                      |

| DEFENSE ELECTR                     |                                 | PLY CENTER                                                                                                                                                          | REV         | ISION LE          | VEL B                               | SHEET                                    | 7            |                      |

|                          | 1                   | Conditions           | T   |                                    |                                   | L   | imits                  | - 1                           |

|--------------------------|---------------------|----------------------|-----|------------------------------------|-----------------------------------|-----|------------------------|-------------------------------|

| Parameter                | Symbol              |                      | no. | Reference<br>  no. <u>10</u> /<br> | Group A 7<br> subgroups <br> <br> | Min | Max<br> <br> <br> <br> | TUnit<br> <br> <br> <br> <br> |

| CLK to PCLK LOW<br>delay | t <sub>CLPL</sub>   |                      | 3   | 25                                 | 9,10,11  <br>  9                  |     | 22                     | ns                            |

| OSC to CLK HIGH          | tolch               | 11/                  | 3   | 26                                 | <br>                              | -5  | 22                     | <u> </u>                      |

| OSC to CLK LOW<br>delay  | tolcl               | 11/                  | 3   | 27                                 | <br>                              | 2   | 35                     |                               |

| CLK rise or fall time    | t <sub>CH1CH2</sub> | +1.0 V to +3.5 V 11/ | 3   | 28                                 | #<br>                             |     | 10                     |                               |

- 1/ F/C pin is a strap option and should be held either  $\le 0.8$  volt or  $\ge 2.2$  volts. Does not apply to X1 or X2 pin.

- $\frac{2}{}$  Due to test equipment limitations related to noise, the actual tested value may differ from that specified, but the specified limit is guaranteed.

- $3/\,$  CSYNC pin is tested with V  $_{IL}$   $\leq\!0.8$  volt.

- 4/ Interchanging of force and sense conditions are permitted.

- $\frac{5}{\text{ASYNC}}$  pin includes an internal 17.5 k $\Omega$  nominal pull-up resistor. For ASYNC input at GND, ASYNC input leakage current = 130  $\mu$ A nominal. X1 crystal feedback input.

- $\frac{6}{f}$  f = 25 MHz may be tested using the extrapolated value based on measurements taken at f = 2 MHz and f = 10 MHz.

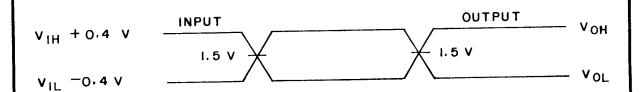

- 7/ Unless otherwise specified, all timing delays are measured at 1.5 volts.

- Input signals must switch between V  $_{I1}$  maximum -.4 volt and V  $_{IH}$  minimum +.4 volt. RES and F/C must switch between 0.4 V and V  $_{CC}$  0.4 V. T  $_R$  and T  $_F$  typically equal to 1 ns/V. V  $_{IL} \leq$  V  $_{IL}$  (max) -.4 V for CSYNC pin.

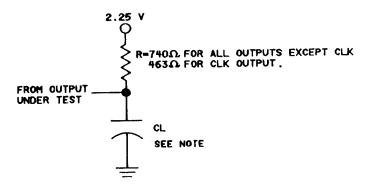

- $\underline{9}$ / All ac parameters apply to device types 01 and 02 and are tested per circuit on figure 8.

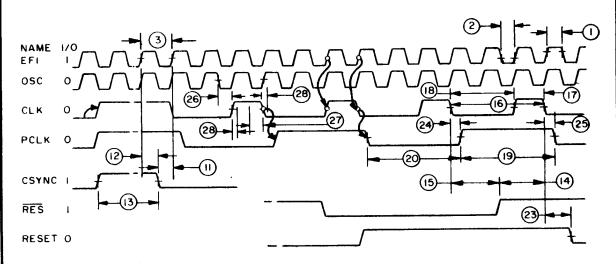

- 10/ The reference number refers to the parameter being measured on figure 3.

- 11/ Not tested but characterized at initial design and major process design changes.

- 12/ Tested using EFI or X1 input pin.

- 13/ Setup and hold necessary only to guarantee recognition at next clock.

- 14/ Applies only to T2 states.

- 15/ Applies only to T3 TW states.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                |   | 84068   |

|------------------------------------------------------|-----------|----------------|---|---------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | С | SHEET 8 |

NOTE: ALL TIMING MEASUREMENTS ARE MADE AT 1.5 VOLTS, UNLESS OTHERWISE NOTED.

Waveforms for clocks and reset signals

FIGURE 3. Waveforms.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

REVISION LEVEL

B

84068

REVISION LEVEL

B

DESC FORM 193A SEP 87

☆U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-409ほ

NOTES: 1. C<sub>L</sub> = 100 pF.

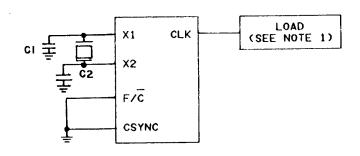

FIGURE 4. Clock high and low times (using X1 and X2).

NOTES: 1.  $C_L = 100 \text{ pF}$ .

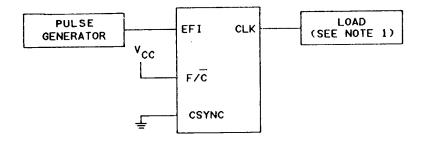

FIGURE 5. Clock high and low times (using EFI).

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                |   | 84068 |    |

|------------------------------------------------------|-----------|----------------|---|-------|----|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | В | SHEET | 12 |

DESC FORM 193A SEP 87

NOTES:

1. C<sub>L</sub> = 100 pF. 2. C<sub>L</sub> = 30 pF.

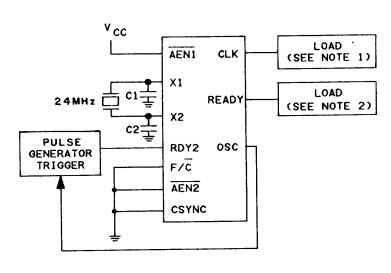

FIGURE 6. Ready to clock (using X1 and X2).

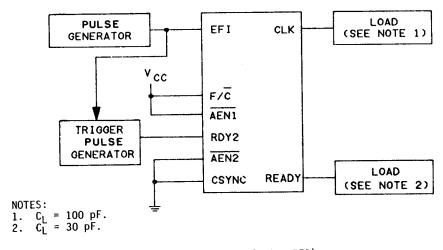

FIGURE 7. Ready to clock (using EFI).

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

REVISION LEVEL

B

84068

REVISION LEVEL

B

13

AC testing: All input signals must switch between  $V_{IL}$  (max) -0.4 V and  $V_{IH}$  (min) +0.4 V.  $\overline{RES}$  and  $F/\overline{C}$  must switch between 0.4 V and  $V_{CC}$  -0.4 V.  $T_R$  and  $T_F$  typically equal 1 ns/V.  $V_{IL} \leq V_{IL}$  (max) -0.4 V for CSYNC pin.

NOTE: CL includes test fixture capacitance.

FIGURE 8. AC test circuit.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |  |                |   | 84068    |  |

|------------------------------------------------------------------------------------|-----------|--|----------------|---|----------|--|

|                                                                                    |           |  | REVISION LEVEL | В | SHEET 14 |  |

TABLE II. <u>Electrical test requirements</u>.

| MIL-STD-883 test requirements    | Subgroups  <br>  (per method  <br>  5005, table I) |

|----------------------------------|----------------------------------------------------|

| Interim electrical parameters    |                                                    |

| (method 5004)                    |                                                    |

| Final electrical test parameters |                                                    |

| (method 5004)                    | 1*,2,3,9                                           |

| Group A test requirements        | 1,2,3,7,8,9,                                       |

| (method 5005)                    | 10,11**                                            |

| Groups C and D end-point         |                                                    |

| electrical parameters            | 2,8 (+125°C                                        |

| (method 5005)                    | only)                                              |

| Additional electrical subgroups  |                                                    |

| for group C periodic             |                                                    |

| inspections                      | <u>                                     </u>       |

- \* PDA applies to subgroup 1.

- \*\* Subgroups 10 and 11, if not tested, shall be guaranteed to the specified limits in table I.

# 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125$ °C, minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

## 5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

#### 6. NOTES

- 6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Comments</u>. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

REVISION LEVEL

C

SHEET 15

| 6.4 Terminal and functional definitions. Terminal and functional definitions and descriptions for this device shall be as follows:                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |  |                |   |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|----------------|---|----------|

| Symbol Symbol                                                                                                                                                                                               | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |  |                |   |          |

| AEN1, AEN2                                                                                                                                                                                                  | ADDRESS ENABLE. $\overline{\text{AEN}}$ is an active LOW signal. $\overline{\text{AEN}}$ serves to qualify its respective Bus Ready Signal (RDY1 or $\overline{\text{RDY2}}$ ). AEN1 validates RDY1 while $\overline{\text{AEN}}$ 2 validates RDY2. Two AEN signal inputs are useful in system configurations which permit the processor to access two Multi-Master System Busses. In non-Multi-Master configurations, the $\overline{\text{AEN}}$ signal inputs are tied true (LOW). |                  |  |                |   |          |

| RDY1, RDY2                                                                                                                                                                                                  | BUS READY (transfer complete). RDY is an active HIGH signal which is an indication from a device located on the system data bus that data has been received, or is available. RDY1 is qualified by AEN1 while RDY2 is qualified by AEN2.                                                                                                                                                                                                                                              |                  |  |                |   |          |

| ASYNC                                                                                                                                                                                                       | READY SYNCHRONIZATION SELECT. $\overline{\text{ASYNC}}$ is an input which defines the synchronization mode of the $\overline{\text{READY}}$ logic. When ASYNC is low, two stages of READY synchronization are provided. When $\overline{\text{ASYNC}}$ is left open or HIGH, a single stage of READY synchronization is provided.                                                                                                                                                     |                  |  |                |   |          |

| READY                                                                                                                                                                                                       | READY is an active HIGH signal which is the synchronized RDY signal input.<br>READY is cleared after the guaranteed hold time to the processor has been met.                                                                                                                                                                                                                                                                                                                          |                  |  |                |   |          |

| X1, X2                                                                                                                                                                                                      | CRYSTAL IN. X1 and X2 are the pins to which a crystal is attached. The crystal frequency is three times the desired processor clock frequency.                                                                                                                                                                                                                                                                                                                                        |                  |  |                |   |          |

| F/C                                                                                                                                                                                                         | FREQUENCY/CRYSTAL SELECT. F/ $\overline{\mathbb{C}}$ is a strapping option. When strapped LOW, F/ $\overline{\mathbb{C}}$ permits the processor's clock to be generated by the crystal. When F/ $\overline{\mathbb{C}}$ is strapped HIGH, CLK is generated from the EFI input.                                                                                                                                                                                                        |                  |  |                |   |          |

| EFI                                                                                                                                                                                                         | EXTERNAL FREQUENCY IN. When $F/\overline{C}$ is strapped HIGH, CLK is generated from the input frequency appearing on this pin. The input signal is a square wave three times the frequency of the desired CLK output.                                                                                                                                                                                                                                                                |                  |  |                |   |          |

| CLK                                                                                                                                                                                                         | PROCESSOR CLOCK. CLK is the clock output used by the processor and all devices which directly connect to the processor's local bus. CLK has an output frequency which is one-third of the crystal or EFI input frequency and a one-third duty cycle.                                                                                                                                                                                                                                  |                  |  |                |   |          |

| PCLK                                                                                                                                                                                                        | PERIPHERAL CLOCK. PCLK is a peripheral clock signal whose output frequency is one-half that of CLK and has a 50 percent duty cycle.                                                                                                                                                                                                                                                                                                                                                   |                  |  |                |   |          |

| osc                                                                                                                                                                                                         | OSCILLATOR OUTPUT. OSC is the output of the internal oscillator circuitry; its frequency is equal to that of the crystal.                                                                                                                                                                                                                                                                                                                                                             |                  |  |                |   |          |

| RESET IN. RES is an active LOW signal which is used to generate RESET. The device provides a Schmitt trigger input so that an RC connection can be used to establish the power-up reset of proper duration. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |  |                |   |          |

|                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |  |                |   |          |

| STANDARDIZED MILITARY DRAWING                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SIZE<br><b>A</b> |  |                |   | 84068    |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |  | REVISION LEVEL | В | SHEET 16 |

RESET RESET is an active HIGH signal which is used to reset the processors. Its

timing characteristics are determined by RES.

CSYNC

CLOCK SYNCHRONIZATION. CSYNC is an active HIGH signal which allows multiple devices to be synchronized to provide clocks that are in phase. When CSYNC is HIGH the internal counters are reset. When CSYNC goes LOW the internal counters are allowed to resume counting. CSYNC needs to be externally synchronized to EFI. When using the internal oscillator, CSYNC should be hardwired to ground.

GND

Ground.

VCC

+5 V supply.

6.5 Approved sources of supply. Approved sources of supply are listed herein. Additional sources will be added as they become available. The vendors listed herein have agreed to this drawing and a certificate of compliance (see 3.5 herein) has been submitted to DESC-ECS.

| Military drawing<br>part number | Vendor<br>  CAGE<br>  number<br> | Vendor<br>  similar part<br>  number 1/ | Replacement   military specification   part number |  |  |

|---------------------------------|----------------------------------|-----------------------------------------|----------------------------------------------------|--|--|

| 8406801VX                       | 34371                            | MD82C84A/883                            |                                                    |  |  |

| 84068012X                       | 34371                            | MR82C84A/883                            |                                                    |  |  |

| 8406802VX                       | 34649                            | MD82C84A/B                              |                                                    |  |  |

Caution. Do not use this number for item aquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

> **Vendor CAGE** Vendor name and address number Harris Semiconductor 34371 P.O. Box 883 Melbourne, FL 32901

34649

Intel Corporation 5000 W. Williams Field Road Chandler, AZ 85224

**STANDARDIZED MILITARY DRAWING**

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

SIZE 84068 Α REVISION LEVEL SHEET