# 82590 ADVANCED CSMA/CD LAN CONTROLLER WITH 8-BIT DATA PATH

- Supports Industry Standard LANs

- Ethernet and Cheapernet (IEEE 802.3 10BASE5 and 10BASE2)

- StarLAN (IEEE 802.3 1BASE5)

- IBM™ PC Network—Baseband and Broadband

- Integrates Physical and Data Link Layers of OSI Model

- Complete CSMA/CD Medium Access Control (MAC) Functions

- Manchester, Differential Manchester, or NRZI Encoding/Decoding

- On-Chip, Logic-Based Collision

Detection

- IEEE 802.3 or HDLC Frame Delimiting

- Broadband Ethernet (IEEE 802.3 10BROAD36)

- Two Modes of Operation

- Bit Rates up to 4 Mb/s with On-Chip Encoder/Decoder (High-Integration Mode)

- Bit Rates up to 20 Mb/s with External Encoder/Decoder (High-Speed Mode)

- High-Performance System Interface

16-MHz Clock, 2 Clocks per Transfer

- 64 Bytes of Configurable FIFO

- Efficient Memory Use via Buffer and Frame Chaining

- DMA Interface for Retransmission and Continuous Reception without CPU Intervention

- EOP Signal Generation for 8237 and 82380

- Tightly Coupled Interface to 82560

Host Interface and Memory Manager

- 82588 Pin- and Software-Compatible Mode

- Local and Remote Power-Down Modes

- 24-Bit General Purpose Timer

- On-Chip Jabber Inhibit Function

- Network Management and Diagnostics

- Monitor Mode

- CRC, Alignment, and Short Frame Error Detection

- Three 16-Bit Event Counters

- Short or Open Circuit Localization

- Self-Test Diagnostics

- Internal and External Loopback Operation

- Internal Register Dump

- High-Speed CHMOS III Technology

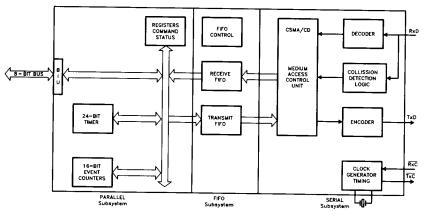

Figure 1. 82590 Block Diagram

290147-1

\*IBM, PC, PCAT, PCXT are trademarks of International Business Machines.

October 1990 Order Number: 290147-004

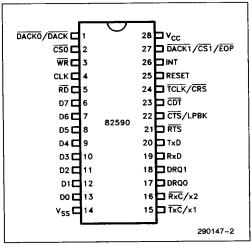

Figure 2. 82590 Pin Configuration (DIP)

The 82590 is a second-generation, 8-bit data path CSMA/CD controller. Its system interface enables efficient operation with a wide variety of Intel microprocessors (such as iAPX 188, 186, 286, or 386) and industry standard buses (such as the IBM PC I/O channel or Personal System/2TM Micro ChannelTM). The 82590 can be configured to support a wide variety of industry standard networks, including StarLAN and Ethernet/Cheapernet.

The 82590 provides a natural upgrade path for existing 82588 applications, since it is pin and software compatible with its predecessor. Its rich incremental functionality compared to the 82588 can be utilized by selectively modifying existing software drivers.

Together with the 82560 (Host Interface and Memory Manager) the 82590 offers a complete solution for

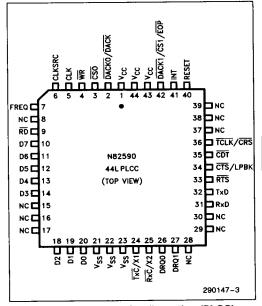

Figure 3. 82590 Pin Configuration (PLCC)

CSMA/CD LAN adapters oriented to the IBM PC environment. The 82590 fully conforms to existing IEEE 802.3 standards (1BASE5, 10BASE5, 10BASE2, and 10BROAD36). Intel also offers the 82592, a 16-bit data path version of the 82590, for higher performance applications.

The 82590 is available in a 28-pin Plastic DIP or a 44-pin PLCC package. It is fabricated with Intel's reliable CHMOS III technology.

Table 1. 82590 Pin Description

|               | Table 1, 82590 Pin Description |                   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|---------------|--------------------------------|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol        | Pin No.<br>(DIP)               | Pin No.<br>(PLCC) | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| D7            | 6                              | 10                | 1/0  | DATA BUS—The Data Bus lines are bidirectional, three-state lines                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| D6            | 7                              | 11                | 1    | connected to the CPU's Data Bus for transfers of data, commands,                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| D5            | 8                              | 12                |      | status, and parameters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| D4            | 9                              | 13                | ļ    | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| D3            | 10                             | 14                | İ    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| D2            | 11                             | 18                |      | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| D1            | 12                             | 19                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| D0            | 13                             | 20                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RD            | 5                              | 9                 | I .  | <b>READ</b> —Together with CS0, CS1, DACK0, or DACK1, Read controls data or status transfers out of the 82590.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| WR            | 3                              | 4                 | I    | WRITE—Together with CS0, CS1, DACK0, or DACK1, Write controls data or command transfers into the 82590.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| CS0           | 2                              | 3                 | _    | CHIP SELECT (PORT 0)—When LOW, the 82590 is selected by the CPU for command or status transfer through PORT 0.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| RESET         | 25                             | 40                | _    | RESET—A HIGH signal on this pin causes the 82590 to terminate current activity. This signal is internally synchronized and must be held HIGH for at least four Clock (CLK) cycles.  When the Clock signal is provided internally (CLKSRC is strapped HIGH), the RESET signal must be held HIGH for at least 50 µs. (PLCC version only.)                                                                                                                                                                                        |  |  |  |

| INT           | 26                             | 41                | 0    | INTERRUPT—A HIGH signal on this pin notifies the CPU that the 82590 is requesting an interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DRQ0          | 17                             | 26                | 0    | DMA REQUEST (CHANNEL 0)—This pin is used by the 82590 to request DMA transfer. DRQ0 remains HIGH as long as the 82590 requires DMA transfers. Burst transfers are thus possible.  When the 82590 is programmed for Tightly Coupled Interface, the 82590 notifies the DMA controller of the status of transmission or reception, using this pin together with EOP.                                                                                                                                                              |  |  |  |

| DRQ1          | 18                             | 27                | 0    | DMA REQUEST (CHANNEL 1)—This pin is used by the 82590 to request DMA transfer. DRQ1 remains HIGH as long as the 82590 requires DMA transfers. Burst transfers are thus possible.  When the 82590 is programmed for Tightty Coupled Interface, the 82590 notifies the DMA controller of the status of transmission or reception, using this pin together with EOP.                                                                                                                                                              |  |  |  |

| DACKO<br>DACK | 1                              | 2                 | l    | DMA ACKNOWLEDGE (CHANNEL 0)—When LOW, this input signal from the DMA controller notifies the 82590 that the requested DMA cycle is in progress. This signal acts similarly to Chip Select for data and parameter transfers, using DMA channel 0.  DMA ACKNOWLEDGE (CHANNELS 0 AND 1)—When the DACK1/EOP pin is programmed to CS1/EOP, this pin provides a DMA acknowledge for both channels 0 and 1. Two DMA acknowledge signals from the DMA controller, DACK0 and DACK1, must be externally ANDed in this mode of operation. |  |  |  |

1

Table 1. 82590 Pin Description (Continued)

| Symbol           | Pin No.<br>(DiP) | Pin No.<br>(PLCC) | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  | Name and Fu | ınction |  |

|------------------|------------------|-------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|-------------|---------|--|

| DACK1<br>CS1/EOP | 27               | 42                | 1/0  | This is a multifunction, bidirectional pin which can be programmed to DACK1 or CS1/EOP during configuration. When it is configured for EOP, it provides an open-drain output.  DMA ACKNOWLEDGE (CHANNEL 1)—When LOW, this input signal from the DMA controller notifies the 82590 that the requested DMA cycle is in progress. This signal acts similarly to Chip Select for data and parameter transfers, using DMA channel 1.  CHIP SELECT (PORT 1)—When LOW, the 82590 is selected by the CPU for command or status transfer through PORT 1.  END OF PROCESS—A LOW output signal requests the DMA controller to terminate the active DMA service.                                                                                                                                                |  |  |             |         |  |

| CLK              | 4                | 5                 | 1/0  | CLOCK—In the 28-pin DIP, this is only an input pin. A TTL-compatible clock input to this pin provides the timing for the 82590 parallel subsystem.  In the 44-pin PLCC, this pin can be a clock input or output, depending on the state of CLKSRC. If CLKSRC is strapped LOW, this pin is a clock input which provides timing for the 82590 parallel subsystem. If CLKSRC is strapped HIGH, the clock for the 82590 parallel subsystem is generated from the internal clock generator. The CLK pin is then a clock output and provides a clock signal whose frequency can be one-half of or identical to, the frequency of the internally generated parallel subsystem clock, depending on the state of FREQ. Note that the maximum frequency of the clock signal supplied by the CLK pin is 8 MHz. |  |  |             |         |  |

|                  |                  |                   |      | CLKSRC FREQ CLK Clock for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |             |         |  |

|                  |                  |                   |      | Type Signal Parallel Subsystem  0 (LOW) Don't I Clock Clock as Provided on the CLK Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |             |         |  |

|                  |                  |                   |      | 1 (HIGH) 1 O Internal Prescaled Clock Generated from the Internal Clock Generator Subsystem Clock Divided by Two                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |             |         |  |

|                  |                  | <b>1</b>          |      | 1 0 O Internal Prescaled Clock Generated from the Internal Clock Generator Subsystem Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |             |         |  |

| CLKSRC           | NA               | 6                 | 1    | CLOCK SOURCE—When strapped LOW, a clock signal on the CLK pin provides timing for the parallel subsystem. When strapped HIGH, timing for the parallel subsystem is internally generated from the clock generator provided in the serial subsystem. The internal prescaler is programmed during configuration to determine the frequency of the clock for the                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |             |         |  |

| FREQ             | NA               | 7                 |      | during configuration to determine the frequency of the clock for the parallel subsystem.  FREQUENCY—When strapped LOW, CLK has an output frequency equal to that of the internal parallel subsystem clock. When strapped HIGH, CLK has an output frequency one-half that of the internal parallel subsystem clock. The state of this pin is relevant only when CLKSRC is strapped HIGH.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |             |         |  |

Table 1. 82590 Pin Description (Continued)

|                 | Pin No. | Pin No.        |          | Die 1. 82590 Pin Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|-----------------|---------|----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol          | (DIP)   | (PLCC)         | Туре     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

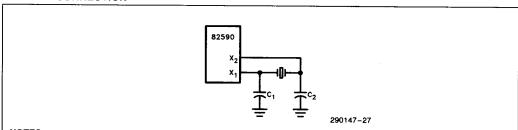

| X1/X2           | 15/16   | 24/25          | l        | High integration Mode OSCILLATOR INPUTS—These inputs may be used to connect a quartz crystal which controls the internal clock generator for the serial subsystem. When CLKSRC is strapped HIGH, the clock generator also provides a clock for the parallel subsystem. X1 may also be driven by a MOS-level clock whose frequency is 8, 10, 16, or 18 times the bit rate of Transmit/Receive data. X2 must be left floating if X1 is connected to an external MOS clock. |  |  |  |

| TxC             | 15      | 24             | 1        | High Speed Mode TRANSMIT CLOCK—This signal provides the fundamental timing for the serial subsystem. The clock is also used to transmit data synchronously on the TxD pin. For NRZ encoding, data is transferred to the TxD pin on the HIGH to LOW clock transition. For Manchester encoding, the transmitted bit center is aligned with the LOW to HIGH transition.                                                                                                     |  |  |  |

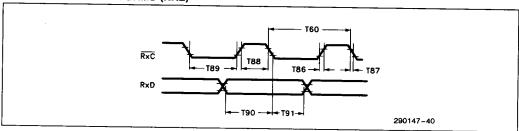

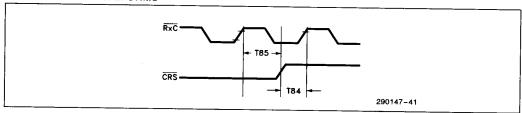

| RxC             | 16      | 25             | <b>.</b> | <b>RECEIVE CLOCK</b> —This clock is used to synchronously sample data on the RxD pin. Only NRZ data format is supported for reception. The state of the RxD pin is sampled on the HIGH to LOW transition.                                                                                                                                                                                                                                                                |  |  |  |

| TCLK/CRS        | 24      | 36             | 0        | CARRIER SENSE—In High Speed Mode this pin is Carrier Sense, CRS, and is used to notify the 82590 that the serial link is active TRANSMIT CLOCK—In High Integration Mode this pin is Transmit Clock, TCLK.                                                                                                                                                                                                                                                                |  |  |  |

| CDT             | 23      | 35             | į        | COLLISION DETECT—This input notifies the 82590 that a collision has occurred. In High Speed Mode a collision is sensed by this pin only when the 82590 is configured for external Collision Detect (external means are then required for collision detection). In High Integration Mode collisions are sensed by this pin regardless of the internal or external Collision Detect configuration of the 82590.                                                            |  |  |  |

| RxD             | 19      | 31             | _        | RECEIVE DATA—This pin receives serial data. It must be HIGH when not receiving.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| TxD             | 20      | 32             | 0        | TRANSMIT DATA—This pin transmits data to the serial link. It is HIGH when not transmitting.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| RTS             | 21      | 33             | 0        | <b>REQUEST TO SEND</b> —When this signal is LOW the 82590 notifies the channel that it has data to transmit. It is forced HIGH after a reset or when transmission is stopped.                                                                                                                                                                                                                                                                                            |  |  |  |

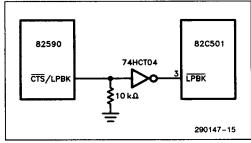

| CTS/LPBK        | 22      | 34             | 1/0      | CLEAR TO SEND—An active LOW signal which enables the 82590 to start transmitting data. Asserting this signal HIGH stops the transmission.  LOOPBACK—This pin, in conjunction with a pull-down resistor, can be programmed to provide an active HIGH loopback signal to the external interface device.                                                                                                                                                                    |  |  |  |

| V <sub>CC</sub> | 28      | 1<br>43<br>44  |          | <b>POWER:</b> +5V ±10%                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| V <sub>SS</sub> | 14      | 21<br>22<br>23 |          | GROUND: 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

### FUNCTIONAL DESCRIPTION

### Internal Architecture

The 82590 consists of a parallel subsystem, a serial subsystem, and a FIFO subsystem (see Figure 1).

### **Parallel Subsystem**

The parallel subsystem consists of a bus interface unit (BIU), command and status registers, a 24-bit general purpose timer, and three 16-bit event counters.

The BIU provides an 8-bit data bus interface to the external system bus. It handles all data transfers to and from memory (at speeds up to 8 Mbytes/sec.), accepts commands from the CPU, and provides status to the CPU. There are two separate I/O ports, Port 0 and Port 1; and two separate DMA channels, Channel 0 and Channel 1. Port 0 is the 82588-compatible I/O port through which the CPU issues commands such as Transmit and Receive Enable. The 82590's enhanced features, such as the general purpose timer and event counters, are accessed through Port 1. The two DMA channels are independent of each other and can be used for high-performance operations such as simultaneous transmission and reception.

The 24-bit timer consists of a 24-bit maximum count register, a 24-bit count register, and associated control bits in the command registers. Its clock source can be the transmit clock or the parallel subsystem clock. The timer can be programmed to halt or continue on a terminal count with or without causing an interrupt.

The three 16-bit event counters can be programmed to count valid frames, collided frames, and errored (CRC or Alignment) frames. When these event counters are used in Monitor mode, the 82590 is capable of maintaining the network statistics by itself; i.e., without requesting DMA services or causing interrupts to the CPU.

### Serial Subsystem

The serial subsystem consists of a CSMA/CD unit, a data encoder and decoder, collision detect and carrier sense logic, and a clock generator.

The 82590's CSMA/CD unit is highly flexible in implementing the CSMA/CD protocol. It can operate in

a variety of IEEE 802.3 and other CSMA/CD LAN environments, including 1BASE5 (StarLAN, 10BASE5 (Ethernet), 10BASE2 (Cheapernet), and the IBM™ PC Network (Baseband and Broadband). The programmable parameters include:

- Framing (IEEE 802.3 Framing or HDLC Framing)

- Address Field Length

- Station Priority

- Interframe Spacing

- Slot Time

- CRC-32 or CRC-16

The encoder and decoder in the serial subsystem is capable of NRZI, Manchester, and Differential Manchester encoding and decoding at bit rates up to 4 Mb/s in High-Integration Mode, and Manchester encoding at bit rates up to 20 Mb/s in High-Speed Mode. A digital phase-lock loop is used in High-Integration Mode to decode the receive data and to generate the synchronous receive clock.

The collision detect and carrier sense logic generate the internal collision detect and carrier sense signals for the CSMA/CD unit.

The 82590 implements several different internal, logic-based collision detect mechanisms. Two of these, Code Violation and Bit Comparison, are also available with the 82588. The Code Violation method defines a collision where a transition edge occurs outside the area of normal transitions (as specified by the data encoding method). For example, if there are no mid-bit cell transitions in the Manchester encoded data, this method interprets that condition as a collision. The Bit Comparison method compares the signature of the transmitted frame to the signature of the received frame. If the signatures are different, a collision is assumed to have occurred. Two other internal collision detect methods implemented in the 82590 are Source Address Comparison and StarLAN CPS (Collision Presence Signal) Recognition. The Source Address Comparison compares the source address field of the transmitted frame to the source address field of the received frame. If the source addresses are different, it assumes that a collision has occurred resulting in data corruption in the source address field. The StarLAN CPS Recognition method looks for the specific collision presence signal defined by the IEEE 802.3 1BASE5 standard. Other abnormal circumstances, such as no carrier for more than one-half slot time in the receive channel during transmission, are interpreted as collisions by the 82590.

In addition to these internal, logic-based collision detection methods, an external means of collision detection can be used in parallel by using the  $\overline{\text{CDT}}$  input pin.

The clock generator in the serial subsystem is available only in High-Integration Mode and provides timing for the serial subsystem. The clock signal can also be routed to the parallel subsystem, if so desired. The oscillator circuit is designed for use with an external, parallel resonant, fundamental mode crystal. The crystal frequency should be selected at  $8\times$ ,  $10\times$ ,  $16\times$ , or  $18\times$  the required serial bit rate.

### **FIFO Subsystem**

The FIFO subsystem is located between the parallel subsystem and the serial subsystem. It consists of a transmit FIFO, a receive FIFO, and FIFO control logic. The transmit and receive FIFOs are independent of each other and individually provide optimal interfaces between the two subsystems which may have different speeds. There is a total of 64 bytes that can be used for the two separate FIFOs. During configuration these 64 bytes can be divided into one of four possible combinations: 16 and 16 bytes, 16 and 48 bytes, 32 and 32 bytes, or 48 and 16 bytes for the transmit and receive FIFO respectively. The FIFO threshold is also programmed during configuration.

# PROGRAMMING MODEL—REGISTER OVERVIEW

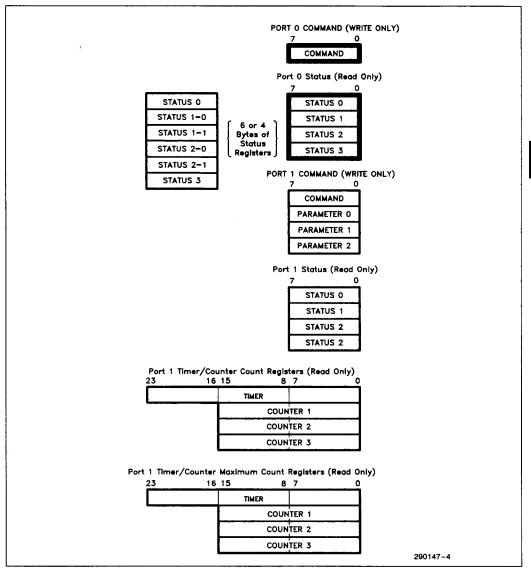

Figure 4 shows the 82590 internal registers that are directly accessible through the 8-bit I/O ports: Port 0 and Port 1. The registers enclosed in darker lines are 82588-compatible registers and are accessible only through Port 0.

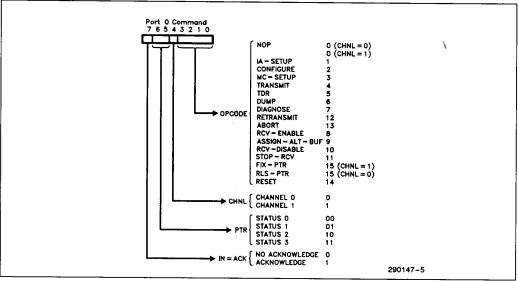

Figure 5 shows the Port 0 commands. All of the Port 0 commands are compatible with the 82588 except for the NOP command with the channel bit set to 1. If the NOP command is executed with the channel bit set to 1, the active port is switched to Port 1. Port 0, which is selected by  $\overline{\text{CSO}}$  in hardware, logically becomes Port 1. When the hardware does not support the second chip select,  $\overline{\text{CSI}}$ , this software port

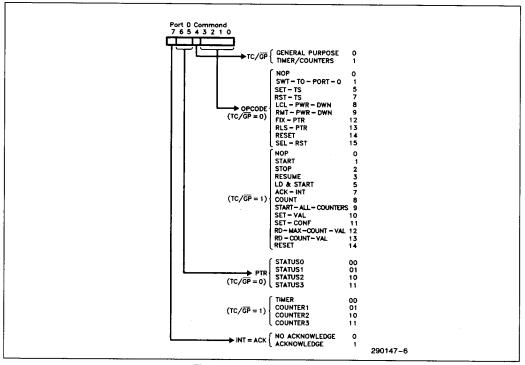

switch command is used. Figure 6 shows the Port 1 commands. When the SWT-TO-PORT-0 command is executed, the active port is switched back to Port 0

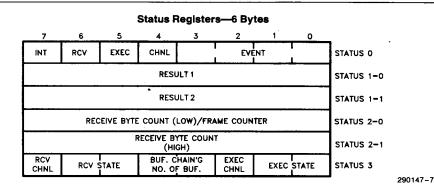

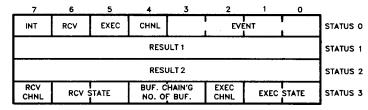

The 82590 can be configured to have 4 or 6 bytes of status registers in Port 0 (see Figures 4 and 7). When configured to 4 bytes of status registers, formats of these registers are identical to those of the 82588. The first three status registers (STATUS 0 through 2) contain the information about the last command executed or the last frame received. The last status register, STATUS 3, contains the state of the 82590. When the 82590 is configured to 6 bytes of status registers, the two additional bytes are used to report a more complete status of the most recently received frame.

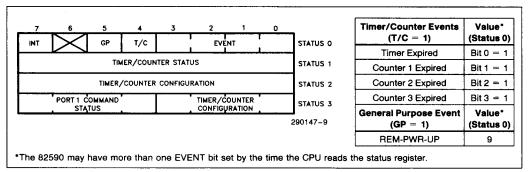

Status of the timer and event counters is available in the Port 1 status registers as shown in Figure 8.

### 82590 AND HOST INTERACTION

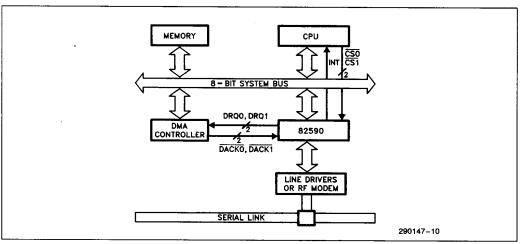

The CPU interacts with the 82590 through the system's memory and the 82590's on-chip registers. The CPU creates a data structure in memory, programs the external DMA controller with the start address and byte count of the memory block, and issues a command to the 82590.

The chip select and interrupt lines are used to communicate between the 82590 and the CPU as shown in Figure 9. The interrupt signal is used by the 82590 to attract the CPU's attention. The chip select signal is used by the CPU to attract the 82590's attention. Note that the 82590 does not have any address lines.

There are two kinds of transfers over the bus: command/status and data transfers. The command/status transfers are always performed by the CPU. The data transfers are requested by the 82590, and are usually performed by a DMA controller. Table 2 shows the command/status and data transfer control signals. The CPU writes commands to the 82590 using the CS0 (or CS1) and WR signals, and reads status using the CS0 (or CS1) and RD signals. When data transfers are performed, DACK0 or DACK1 must be asserted by the DMA controller instead of the Chip Select.

Figure 4. Programming Model—Directly Accessible Registers (Accessible Through 8-Bit I/O Port[s])

Figure 5. Port 0 Commands

Figure 6. Port 1 Commands

Status Registers—4 Bytes (82588 Compatible Modes)

290147-8

| Events         | Value<br>(Status 0) | Events              | Value<br>(Status 0) |

|----------------|---------------------|---------------------|---------------------|

| CMOS*          | 0 (CHNL = 1)        | Diagnose-Passed     | 7                   |

| IA-Setup-Done  | 1                   | End-Of-Frame        | 8                   |

| Configure-Done | 2                   | Request-Next-Buffer | 9 .                 |

| MC-Setup-Done  | 3                   | Reception-Aborted   | 10                  |

| Transmit-Done  | 4                   | Retransmit-Done     | 12                  |

| TDR-Done       | 5                   | Execution-Aborted   | 13                  |

| Dump-Done      | 6                   | Diagnose-Failed     | 15                  |

<sup>\*</sup>Available only after Hardware or Software Reset

Figure 7. Port 0 Status Registers

Figure 8. Port 1 Status Registers

1-73

Figure 9. 82590/Host CPU Interaction

Table 2. Data Bus Control Signals and Functions

| Pin             | Name   |        |                                        |

|-----------------|--------|--------|----------------------------------------|

| CS0<br>CS1*     | RD     | WR     | Function                               |

| 1<br>0          | X<br>1 | X<br>1 | No Transfer To/From<br>Command/Status  |

| 0               | 0      | 0      | Illegal                                |

| 0               | 0      | 1      | Read from Status<br>Register           |

| 0               | 1      | 0      | Write to Command<br>Register           |

| DACKO<br>DACK1* | RD     | WR     |                                        |

| 1               | Х      | Х      | No DMA Transfer                        |

| 0               | 1      | 1      |                                        |

| 0               | 0      | 0      | Illegal                                |

| 0               | 0      | 1      | Data Read from DMA<br>Channel 0 (or 1) |

| 0               | 1      | 0      | Data Write to DMA<br>Channel 0 (or 1)  |

<sup>\*</sup>Only one of CSO, CST, DACKO, or DACKT may be active at any time.

To initiate an operation such as Transmit or Configure (see Figure 5), the command from the CPU must first be written to the 82590. Any parameters or data associated with the command are transferred from memory to the 82590 using DMA. Upon completion of the operation, the 82590 updates the appropriate status registers and sends an interrupt to the CPU.

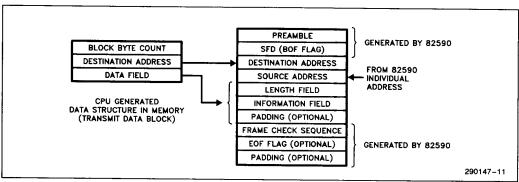

### FRAME TRANSMISSION

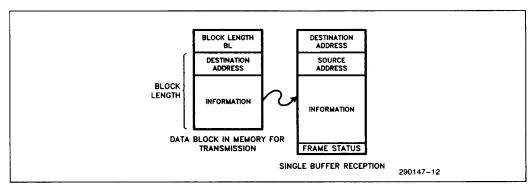

To transmit a frame, the CPU prepares a Transmit Data Block in memory as shown in Figure 10. Its first two bytes specify the length of the rest of the block. The next few bytes (up to six) contain the destination address of the station the frame is being sent to. The rest of the block is the data field. The CPU programs the DMA controller with the start address of the block, length of the block, and other control information and then issues a Transmit command to the 82590. Upon receiving this command, the 82590 fetches the first two bytes of the block to determine its length. If the link is free and the first data byte was fetched, the 82590 begins transmitting the preamble and concurrently fetches more bytes from the Transmit Data Block and loads them into the transmit FIFO to keep them ready for transmission.

Figure 10. The 82590 Frame Structure and Location of Data Element in System Memory

The destination address is transmitted after the preamble. This is followed by the source or the station individual address, which was previously stored in the 82590 by the IA-Setup command. After this, the entire information field is transmitted, followed by a CRC field calculated by the 82590. If a collision is encountered during transmission of the frame, then the transmission is aborted after a jam pattern is sent. If the collision is detected during preamble or SFD (Start Frame Delimiter) transmission, the 82590 transmits the jam pattern after the SFD is transmitted. An interrupt is then generated to inform the CPU of the unsuccessful transmission due to a collision. The CPU reinitializes the DMA controller and issues a Retransmit command to the 82590. Retransmission is done by the CPU exactly as the Transmit command is done, except the Retransmit command keeps track of the number of collisions encountered. When the 82590 gets the Retransmit command and the backoff timer is expired, it transmits the frame again. Retransmission is repeated until the attempt is successful, or until the preprogrammed retry number expires.

If the 82590 is programmed to generate the  $\overline{\text{EOP}}$  signal to the 8237 or 82380 DMA controller, or if it is used with a DMA controller which implements the

Tightly Coupled Interface, retransmission is performed without CPU intervention.

### FRAME RECEPTION

The 82590 can receive frames when its receiver has been enabled. The 82590 checks for an address match for an Individual address, a Multicast address, or a Broadcast address. In the Promiscuous mode the 82590 receives all frames. When the address match is successful, the 82590 transfers the frame to memory using the DMA controller. Before enabling the receiver, it is the CPU's responsibility to make a memory buffer area available to the receiver and to properly program the starting address of the DMA controller. The received frame is transferred to the memory buffer in the format shown in Figure 11. This method of reception is called Single Buffer reception; the entire frame is contained in one continuous buffer. Upon completion of reception, the status of the reception is appended at the end of the received frame in the memory buffer, and the total number of bytes transferred to the memory buffer is loaded into the internal status registers 1 and 2. An interrupt is then generated to inform the CPU of the frame reception.

Figure 11. Single Buffer Reception

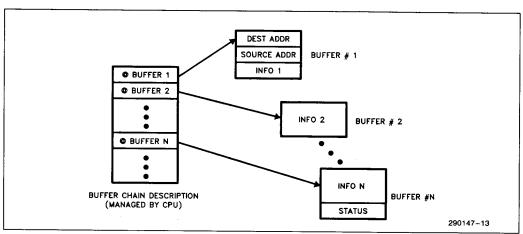

If the frame size is unknown, memory usage can be optimized by using Multiple Buffer reception. In this mode of operation, the CPU and DMA Controller can dynamically allocate memory space as it receives frames. This method requires both DMA channels to receive the frame alternately. As frame reception begins, the 82590 interrupts the CPU and automatically requests assignment of the next available buffer. The CPU does this and loads the second DMA channel with the next buffers information so the 82590 can immediately switch to the other channel when the current buffer is full. When the 82590 switches from the first to the second buffer it again interrupts the CPU and requests another buffer to be allocated on the previous channel. This process continues until the entire frame is received. The received frame is spread over multiple memory buffers. The link between the buffers is easily maintained by the CPU, using a buffer chain descriptor structure in memory as shown in Figure 12. This dynamic allocation of memory buffers results in efficient use of available storage when handling frames of widely differing sizes.

If the 82590 is programmed to generate the EOP signal to the 8237 or 82380 DMA controller, or if it is used with a DMA controller which implements the Tightly Coupled Interface, buffer reclamation and

more advanced data structures for the buffer area can significantly improve system performance.

# EOP SIGNAL TO THE DMA CONTROLLER

The 82590 can be programmed to assert the EOP signal to the 8237 or 82380 DMA controller when one or more of the following occurs:

- · A collision during transmission

- An error (CRC or alignment) during reception

- A good frame reception

If the 8237 or 82380 is programmed for Auto-initialize mode and if the 82590 is programmed to assert the EOP signal on a collision during transmission, the retransmission following a collision is done automatically by the 8237 and the 82590. The 8237 will reinitialize itself automatically and the 82590 will retransmit the same frame from the same memory area without CPU intervention. When the 82590 is programmed for this mode it does not interrupt the CPU upon a collision, and the CPU does not need to issue a Retransmit command to the 82590. The CPU is interrupted only after a successful transmission or retransmission, or after a transmission failure, such as DMA underrun.

Figure 12. Multiple Buffer Reception

If the 82590 is programmed to assert the  $\overline{\text{EOP}}$  signal when an error occurs during reception, the 8237 or the 82380 in Auto-initialize mode will be able to reclaim the memory area which would otherwise be wasted for the errored frame reception. If the 82590 is programmed to assert  $\overline{\text{EOP}}$  at the end of a frame reception, automatic buffer switching can be accomplished by alternating the DMA channels with the 8237 or the 82380. When the 82380 is used, the buffer switching can be done with only one DMA channel.

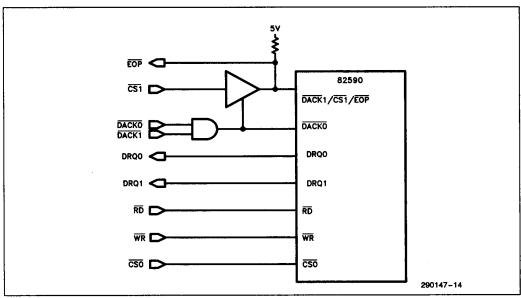

The EOP signal must be derived from the DACK1/CS1/EOP pin using external logic (see Figure 13).

# 82590/82560 TIGHTLY COUPLED INTERFACE

The 82590 has a mode of operation called "Tightly Coupled Interface." In this mode the 82590 provides a tightly coupled interface to a DMA controller in order to execute some of the time-critical processes of the CSMA/CD protocol without any CPU intervention. By using the 82590's companion chip, the 82560, or by implementing the Tightly Coupled Interface in a DMA controller, operations such as automatic retransmission, continuous back-to-back frame reception, and transmit and/or receive buffer chaining can be accomplished.

The 82590 provides the status of the current active transmission or reception to the DMA controller by using the DRQ and  $\overline{\text{EOP}}$  signals at the end of every DMA cycle. The status is encoded according to Ta-

ble 3. As long as the 82590 generates DRQ High and  $\overline{EOP}$  Floating at the rising edge of  $\overline{RD}$  or  $\overline{WR}$ , the DMA controller repeats DMA transfers. If the transmission is completed without collisions or if the reception is good (no collision, no CRC, or no Alignment error), then DRQ and  $\overline{EOP}$  both become Low at the end of a DMA transfer which follows the last DMA data transfer. If the transmission encountered a collision or if the reception had an error, DRQ becomes High and  $\overline{EOP}$  becomes Low. The DMA controller must decode these signals appropriately and must reinitialize the DMA channel so it can retransmit the same frame or reclaim the otherwise wasted buffer. It is the DMA controller's responsibility to reprogram itself for the next appropriate operation.

The 82560 fully implements the Tightly Coupled Interface and provides very high-performance DMA services for the 82590 with minimal CPU involvement.

# NETWORK MANAGEMENT AND DIAGNOSTICS

The 82590 provides a large set of diagnostic and network management functions including: internal and external loopback, monitor mode, optional capture of all frames regardless of destination address (Promiscuous mode), and time domain reflectometry for locating fault points in the network cable. The 82590 Dump command ensures software reliability by dumping the contents of the 82590 internal registers into the system memory.

Figure 13. Demultiplexing DACK/CS1/EOP Pin

Table 3. Transmit/Receive Status Encoding on DRQ and EOP

| DRQ | EOP  | Status Information                      |

|-----|------|-----------------------------------------|

| 0   | Hi-Z | ldle                                    |

| 1   | Hi-Z | DMA Transfer                            |

| 0   | 0    | Transmission or Reception Terminated OK |

| 1   | 0    | Transmission or Reception Aborted       |

### OTHER ENHANCEMENTS

Compared to the 82588 the 82590 has a number of functional and performance enhancements. This section lists some of these enhancements which are not covered in other sections.

- Multi-IA—The 82590 implements multiple-individual address (Multi-IA) filtering. It can receive more than one IA frame in this mode.

- Power Down Modes—Two power down modes, Local Power Down and Remote Power Down, are available. When the 82590 is in Remote Power Down mode, it can be powered up remotely by sending a special frame to it.

- Automatic Padding and IEEE 802.3 Length Field—If a frame to be transmitted is shorter than the configured Slot Time, the 82590 automatically appends pad bytes up to the shortest

frame greater than the Slot Time. If the data field of a received frame is longer than the byte count indicated in the Length field, the extra bytes are stripped automatically according to the Length field. Erroneous conditions are detected and reported by the 82590. An example of such conditions is reception of a frame which is shorter than the byte count indicated in the Length field.

- Automatic Retransmission on Collision Dur- Ing Preamble—The 82590 can be pro- grammed to retransmit automatically if it de- tects a collision during transmission of the preamble.

- On-Chip Jabber Inhibit Function—The 82590 can be programmed to provide an on-chip jabber inhibit function.

- © CRC Transfer to Memory—The 82590 can be programmed to transfer the CRC field of a received frame into memory.

- D Loopback Signal to the 82C501—The 82590 can be programmed to provide an active High loopback signal to the 82C501 (see Figure 14).

- StarLAN—The 82590 can be configured to recognize the IEEE 802.3 1BASE5 Collision Presence Signal (CPS). In this mode it also delays deactivation of the RTS signal at the end of a frame transmission in order to insert an end-of-frame marker according to the standard.

### **APPLICATIONS**

The 82590 can be used in a variety of applications. When it is used in High-Integration Mode, it implements most of the Data Link and Physical Layer functions required by the IEEE 802.3 1BASE5 (Star-LAN) and the IBM PC Network—Baseband and Broadband. When it is used in High-Speed Mode, it can work with the 82C501 and a standard transceiver for IEEE 802.3 10BASE5 (Ethernet) and 10BASE2 (Cheapernet) implementations.

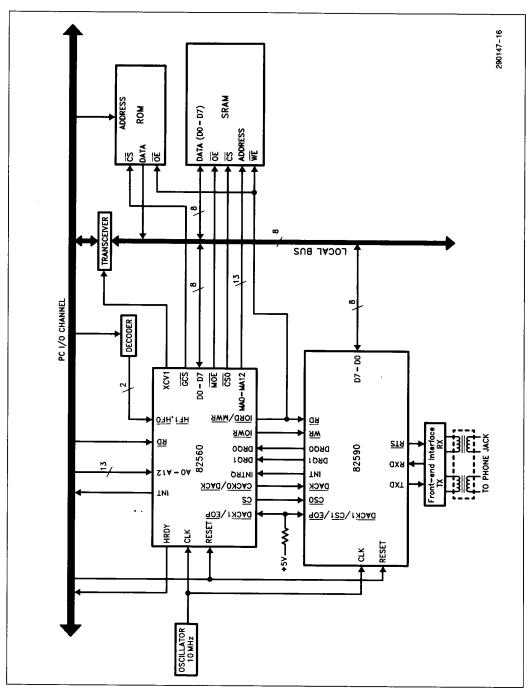

Figure 15 shows a block diagram of an 82590/82560 High Integration adapter board. The 82560 provides the following functions: DMA for the 82590 with Tightly Coupled Interface and dual-port memory control for the static RAM. The 82590 is configured to High-Integration mode to minimize the serial interface logic.

Figure 14. Loopback Output to the 82C501

4

Figure 15. 82590/82560 High-Integration Adapter

1-80

### **ABSOLUTE MAXIMUM RATINGS\***

| Case Temperature (T <sub>C</sub> ) Under Bia | ıs              |

|----------------------------------------------|-----------------|

| Plastic                                      | 0°C to +85°C    |

| PLCC                                         | 0°C to +85°C    |

| Storage Temperature                          | -65°C to +150°C |

| Voltage on any Pin with                      |                 |

| Respect to Ground                            | – 1V to + 7V    |

| Power Dissination                            | 550 mW          |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### D.C. CHARACTERISTICS

(T<sub>C</sub> [Plastic] = 0°C to +85°C, T<sub>C</sub> [PLCC] = 0°C to +85°C,  $V_{CC}$  = +5V  $\pm$ 10%)

TxC and RxC have MOS levels (see V<sub>MIL</sub>, V<sub>MIH</sub>). All other signals have TTL levels (see V<sub>IL</sub>, V<sub>IH</sub>, V<sub>OL</sub>, V<sub>OH</sub>).

| Symbol           | Parameter                   | Min  | Max                   | Units | Test Conditions                        |

|------------------|-----------------------------|------|-----------------------|-------|----------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage (TTL)     | -0.5 | 0.8                   | V     |                                        |

| V <sub>IH</sub>  | Input High Voltage (TTL)    | 2.0  | V <sub>CC</sub> + 0.5 | ٧     |                                        |

| V <sub>OL</sub>  | Output Low Voltage (TTL)    |      | 0.45                  | V     | I <sub>OL</sub> = 2.0 mA               |

| V <sub>OH</sub>  | Output High Voltage (TTL)   | 2.4  |                       | V     | $I_{OH} = -400 \mu\text{A}$            |

| V <sub>MIL</sub> | Input Low Voltage (MOS)     | -0.5 | 0.6                   | V     |                                        |

| V <sub>MIH</sub> | Input High Voltage (MOS)    | 3.9  | V <sub>CC</sub> + 0.5 | V     |                                        |

| լը               | Input Leakage Current       |      | ±10                   | μА    | 0V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> |

| ILIO             | I/O Leakage Current         |      | ±10                   | μΑ    | $0.45V \le V_{OUT} \le V_{CC} - 0.45V$ |

| C <sub>IN</sub>  | Capacitance of Input Buffer |      | 10                    | pF    | Frequency = 1 MHz                      |

| C <sub>IO</sub>  | Capacitance of I/O Buffer   |      | 20                    | pF    | Frequency = 1 MHz                      |

| Icc              | Power Supply Current        |      | 80                    | mA    | (Note 1)                               |

|                  |                             |      | 5                     | mA    | (Note 2)                               |

|                  |                             |      | 1                     | mA    | (Note 3)                               |

|                  |                             |      |                       |       | (Note 4)                               |

### NOTES:

<sup>1.</sup> System side (CLK) at 16 MHz, serial side (TxC) at 20 MHz in High-Speed Mode.

<sup>2.</sup> Remote power-up mode.

<sup>3.</sup> Power-down mode—all inputs connected to V<sub>CC</sub> level.

<sup>4.</sup> General formulas for current are: (a) f(CLK)  $\times$  2.9 + f(TXC)  $\times$  1.8 for High Speed Mode. (b) f(CLK)  $\times$  2.9 + f(TFC)  $\times$  0.2 + f(TFC)  $\times$  1.8/SR, where SR is the sampling rate in High-Integration Mode, and f = frequency in MHz.

| (of on an outputs is 20 pr = 125 pr unless otherwise specified | C. CHARACTERISTICS (C <sub>L</sub> on all outputs is 20 pF-125 pF un | less otherwise specified. |

|----------------------------------------------------------------|----------------------------------------------------------------------|---------------------------|

|----------------------------------------------------------------|----------------------------------------------------------------------|---------------------------|

| Symbol           | Parameter                                       | Min             | Max | Units                                 | Test Conditions |

|------------------|-------------------------------------------------|-----------------|-----|---------------------------------------|-----------------|

| SYSTEM C         | LOCK INPUT PARAMETERS                           |                 | ·   | ·                                     | <u> </u>        |

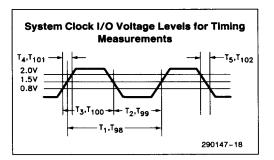

| t <sub>1</sub>   | CLK Cycle Time                                  | 62.5            |     | ns                                    |                 |

| t <sub>2</sub>   | CLK Low Time                                    | 27              |     | ns                                    | (Note 5)        |

| t <sub>3</sub>   | CLK High Time                                   | 27              |     | ns                                    | (Note 5)        |

| t <sub>4</sub>   | CLK Rise Time                                   |                 | 5   | ns                                    | (Note 1)        |

| t <sub>5</sub>   | CLK Fall Time                                   |                 | 5   | ns                                    | (Note 2)        |

| SYSTEM C         | LOCK OUTPUT PARAMETERS                          | <u> </u>        |     | · · · · · · · · · · · · · · · · · · · |                 |

| t <sub>98</sub>  | CLK Cycle Time                                  | 120             |     | ns                                    | (Notes 4, 7)    |

| t <sub>99</sub>  | CLK Low Time                                    | 50              |     | ns                                    | (Note 4)        |

| t <sub>100</sub> | CLK High Time                                   | 50              |     | ns                                    | (Note 4)        |

| t <sub>101</sub> | CLK Rise Time                                   |                 | 15  | ns                                    | (Notes 1, 4)    |

| t <sub>102</sub> | CLK Fall Time                                   |                 | 15  | ns                                    | (Notes 2, 4)    |

| RESET PA         | RAMETERS                                        |                 |     |                                       |                 |

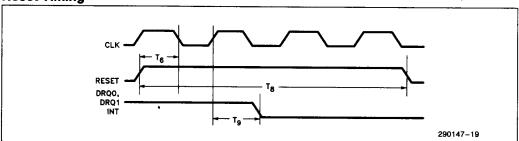

| t <sub>6</sub>   | Reset Active to Clock Low                       | 20              |     | ns                                    | (Note 3)        |

| t <sub>8</sub>   | Reset Pulse Width                               | 4t <sub>1</sub> |     | ns                                    |                 |

| t <sub>9</sub>   | Control Inactive after Reset                    |                 | 2t1 | ns                                    |                 |

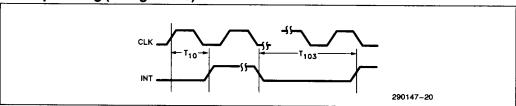

| INTERRUP         | T PARAMETERS                                    |                 |     |                                       | -               |

| t <sub>10</sub>  | CLK High to Interrupt Active                    |                 | 55  | ns                                    | (Note 4)        |

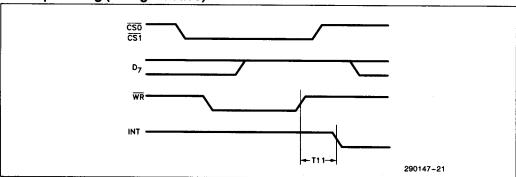

| t <sub>11</sub>  | WR Inactive to Interrupt                        |                 | 55  | ns                                    | (Note 4)        |

| t <sub>103</sub> | Int Low to Int High Gap                         | 2t <sub>1</sub> |     | ns                                    | (Note 4)        |

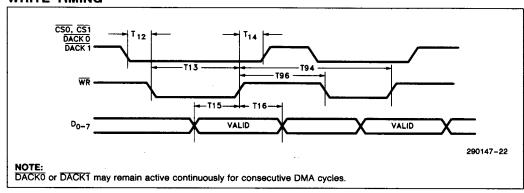

| WRITE PAI        | RAMETERS                                        |                 |     |                                       |                 |

| t <sub>12</sub>  | CS0, CS1, DACK0, or<br>DACK1 Setup to WR Low    | 0               |     | ns                                    |                 |

| t <sub>13</sub>  | WR Pulse Width                                  | 55              |     | ns                                    |                 |

| t <sub>14</sub>  | CS0, CS1, DACK0, or<br>DACK1 Hold after WR High | 0               |     | ns                                    |                 |

| t <sub>15</sub>  | Data Setup to WR High                           | 30              |     | ns                                    |                 |

| t <sub>16</sub>  | Data Hold after WR High                         | 3               |     | ns                                    |                 |

| t <sub>94</sub>  | Write Cycle Time                                | 2t <sub>1</sub> |     | ns                                    | <u></u>         |

| t <sub>96</sub>  | WR Inactive Time                                | 55              |     | ns                                    |                 |

### NOTE:

To achieve socket compatibility with the Intel 82588, the rise and fall time specifications of the Intel 82588 can be applied for the 82590 clock inputs (CLK, TXC, TXC). This is valid only for standard 82588 operating frequencies. Refer to the Intel 82588 data sheet for these specifications.

### A.C. CHARACTERISTICS (C<sub>L</sub> on all outputs is 20 pF-125 pF unless otherwise specified.) (Continued)

| Symbol          | Parameter                                   | Min             | Max | Units | Test Conditions |

|-----------------|---------------------------------------------|-----------------|-----|-------|-----------------|

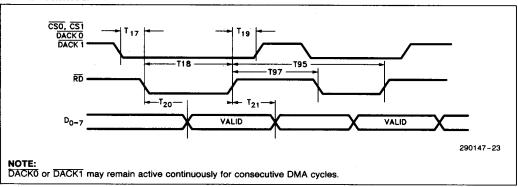

| READ PAI        | RAMETERS                                    |                 |     |       |                 |

| t <sub>17</sub> | CS0, CS1, DACK0, or DACK1 Setup to RD Low   | 0               |     | ns    |                 |

| t <sub>18</sub> | RD Pulse Width                              | 55              |     | ns    |                 |

| t <sub>19</sub> | CS0, CS1 DACK0, or DACK1 Hold after RD High | 0               |     | ns    |                 |

| t <sub>20</sub> | RD Low to Data Valid                        |                 | 45  | ns    |                 |

| t <sub>21</sub> | Data Float after RD High                    | 5               | 40  | ns    |                 |

| t <sub>95</sub> | Read Cycle Time                             | 2t <sub>1</sub> |     | ns    |                 |

| t <sub>97</sub> | RD Inactive Time                            | 55              |     | ns    |                 |

### **DMA PARAMETERS**

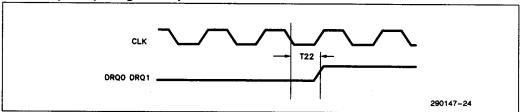

| t <sub>22</sub>  | CLK Low to DRQ0<br>or DRQ1 Active                                                       |     | 55 | ns | (Note 4) |

|------------------|-----------------------------------------------------------------------------------------|-----|----|----|----------|

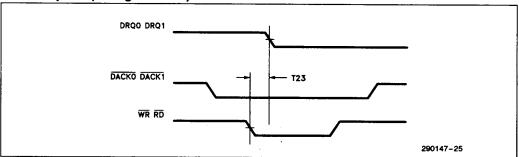

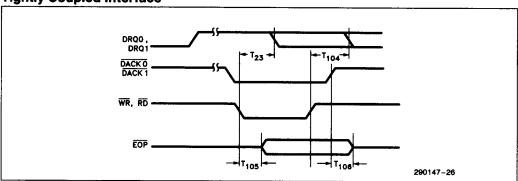

| t <sub>23</sub>  | WR or RD Low to DRQ0 or DRQ1 Inactive                                                   |     | 45 | ns | (Note 4) |

| t <sub>104</sub> | WR or RD High to DRQ0 or<br>DRQ1 Inactive—82560<br>Retransmit or Receive Buffer Reclaim | 2.5 | 65 | ns | (Note 4) |

| t <sub>105</sub> | WR or RD Low to EOP Active                                                              |     | 45 | ns | (Note 6) |

| t <sub>106</sub> | EOP Float after DACK0 or DACK1 Going Inactive                                           |     | 40 | ns | (Note 6) |

### NOTES:

- 1. 0.8V to 2.0V.

- 2. 2.0V to 0.8V.

- 3. To guarantee recognition on the next clock.

- 4. C<sub>L</sub> = 50 pF.

- 5. Measured at 1.5V.

- 6. Open drain I/O pin.

- 7. None of the A.C. Parameters are related to the CLK output pin.

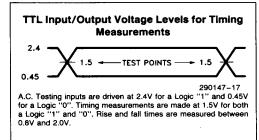

### A.C. TESTING INPUT/OUTPUT WAVEFORMS

# **Reset Timing**

# **Interrupt Timing (Going Active)**

# **Interrupt Timing (Going Inactive)**

### **WRITE TIMING**

## **READ TIMING**

# **DMA Request (Going Active)**

# **DMA Request (Going Inactive)**

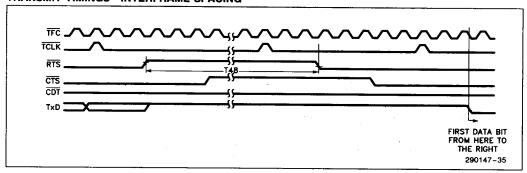

# **Tightly Coupled Interface**

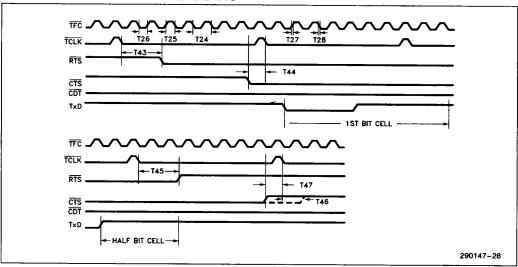

SERIAL INTERFACE A.C. TIMING CHARACTERISTICS TFC is the Crystal or Serial Clock Input at X1.

|                                         | X8 Sampling                            | X10 Sampling                           | X16 Sampling                                          | X18 Sampling                            |

|-----------------------------------------|----------------------------------------|----------------------------------------|-------------------------------------------------------|-----------------------------------------|

| High Integration I<br>For TFC Frequence |                                        | z (High)                               |                                                       |                                         |

| TCLK Frequency                          | 0.125 MHz-4 MHz                        | 100 kHz-3.2MHz                         | 62.5 kHz-2 MHz                                        | 55.6 kHz-1.78 MHz                       |

| t <sub>29</sub> = TCLK<br>Cycle Time    | 8 × t <sub>24</sub>                    | 10 × t <sub>24</sub>                   | 16 × t <sub>24</sub>                                  | 18 × t <sub>24</sub>                    |

| t <sub>30</sub> = TCLK<br>High Time     | t <sub>24</sub> (Typically)            | t <sub>24</sub> (Typically)            | t <sub>24</sub> (Typically)                           | t <sub>24</sub> (Typically)             |

| t <sub>31</sub> = TCLK<br>Low Time      | 7 × t <sub>24</sub> (Typically)        | 9 × t <sub>24</sub> (Typically)        | 15 × t <sub>24</sub> (Typically)                      | $17 	imes t_{24}$ (Typically)           |

| For TFC Frequence                       | cy = 0 MHz to 1 MHz                    | (Low)                                  |                                                       |                                         |

| TCLK Frequency                          | 0-0.125 MHz                            | 0-100 kHz                              | 0-62.5 kHz                                            | 0-55.6 kHz                              |

| t <sub>29</sub> = TCLK<br>Cycle Time    | 8 × t <sub>24</sub>                    | 10 × t <sub>24</sub>                   | 16 × t <sub>24</sub>                                  | 18 × t <sub>24</sub>                    |

| t <sub>30</sub> = TCLK<br>High Time     | t <sub>25</sub> (Typically)            | t <sub>25</sub> (Typically)            | t <sub>25</sub> (Typically)                           | t <sub>25</sub> (Typically)             |

| t <sub>31</sub> = TCLK<br>Low Time      | $7 \times t_{24} + t_{26}$ (Typically) | $9 \times t_{24} + t_{26}$ (Typically) | 15 × t <sub>24</sub> + t <sub>26</sub><br>(Typically) | $17 \times t_{24} + t_{26}$ (Typically) |

### NOTES:

X10 and X18 are available only for Manchester or Differential Manchester encoding/decoding

t24 = Serial Clock Cycle Time

t<sub>25</sub> = Serial Clock High Time t<sub>26</sub> = Serial Clock Low Time

### HIGH SPEED MODE

- Applies for TxC, RxC

- $f_{max} = 20 \text{ MHz } \pm 100 \text{ ppm}$

- For Manchester, symmetry is required:  $t_{64}$ ,  $t_{64} = \frac{1}{2f} \pm 5\%$

| HIGH INT        | EGRATION MODE                                                   | + ,          |             |         |                                       |

|-----------------|-----------------------------------------------------------------|--------------|-------------|---------|---------------------------------------|

| Symbol          | Parameter                                                       | Min          | Max         | Units   | Test Conditions                       |

| EXTERNA         | L (FAST) CLOCK PARAMETERS                                       | 3            |             |         |                                       |

| t <sub>24</sub> | Fast Clock (TFC) Cycle Time                                     | 31.25        |             | ns      | (Notes 1, 16)                         |

| t <sub>25</sub> | TFC High Time                                                   | (Note 13)    | ·           | ns      | (Notes 1, 7)                          |

| t <sub>26</sub> | TFC Low Time                                                    | 12           |             | ns      | (Notes 1, 17)                         |

| t <sub>27</sub> | TFC Rise Time                                                   |              | 3           | ns      | (Note 1)                              |

| t <sub>28</sub> | TFC Fall Time                                                   |              | 3           | ns      | (Note 1)                              |

| TRANSMI         | T CLOCK PARAMETERS                                              |              |             |         |                                       |

| t <sub>29</sub> | Transmit Clock (TCLK) Cycle Time                                | (Note 13)    |             | ns      | (Note 2)                              |

| t <sub>30</sub> | TCLK High Time                                                  | (Note 7)     |             | ns      | (Note 2)                              |

| t <sub>31</sub> | TCLK Low Time                                                   | (Note 8)     |             | ns      | (Note 2)                              |

| t <sub>32</sub> | TCLK Rise Time                                                  |              | 10          | ns      | (Note 2)                              |

| t <sub>33</sub> | TCLK Fall Time                                                  |              | 10          | ns      | (Note 2)                              |

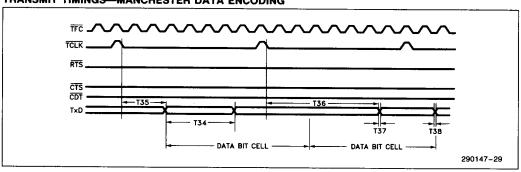

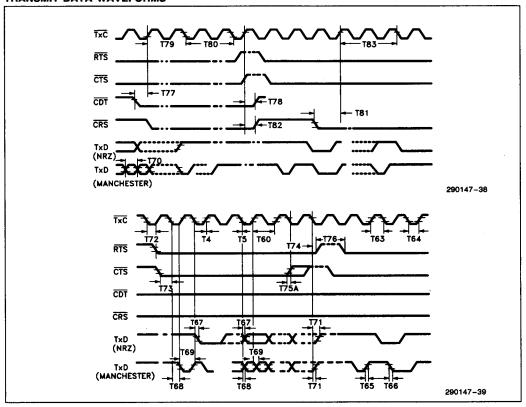

| TRANSMI         | T DATA PARAMETERS (MANCH                                        | ESTER, DIFFE | RENTIAL MAI | CHESTER | R)                                    |

| t <sub>34</sub> | TxD Transition-Transition                                       | (Note 14)    |             | ns      |                                       |

| t <sub>35</sub> | TCLK Low to TxD Mid Bit Cell Transition                         |              | (Note 10)   | ns      | (Note 2)                              |

| t <sub>36</sub> | TCLK Low to TxD Bit Cell Boundary Transition                    |              | (Note 9)    | ns      | (Note 2)                              |

| t <sub>37</sub> | TxD Rise Time                                                   |              | 10          | ns      | (Note 2)                              |

| t <sub>38</sub> | TxD Fall Time                                                   |              | 10          | ns      | (Note 2)                              |

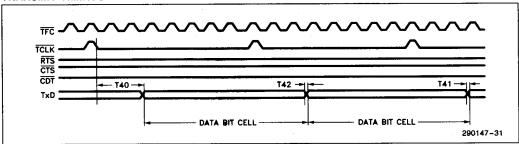

| TRANSMI         | T DATA PARAMETERS (NRZI)                                        |              | *           |         |                                       |

| t <sub>39</sub> | TxD Transition-Transition                                       | (Note 15)    |             | ns      |                                       |

| t <sub>40</sub> | TCLK Low to TxD Transition                                      |              | (Note 9)    | ns      | (Note 2)                              |

| t <sub>41</sub> | TxD Rise Time                                                   |              | 10          | ns      | (Note 2)                              |

| t <sub>42</sub> | TxD Fall Time                                                   |              | 10          | ns      | (Note 2)                              |

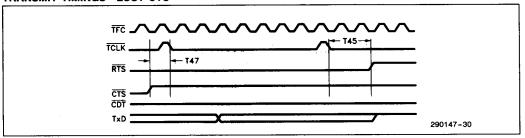

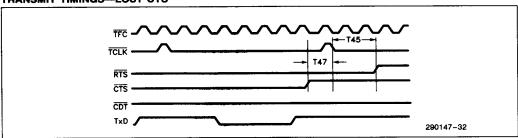

| RTS, CTS        | PARAMETERS                                                      |              |             |         | , , , , , , , , , , , , , , , , , , , |

| t <sub>43</sub> | TCLK Low to RTS Low                                             |              | (Note 9)    | ns      | (Note 2)                              |

| t <sub>44</sub> | CTS Low to TCLK Low                                             | 35           |             | ns      |                                       |

| t <sub>45</sub> | TCLK Low to RTS High                                            |              | (Note 9)    | ns      | (Note 2)                              |

| t <sub>46</sub> | TCLK Low to CTS Invalid<br>CTS Hold Time                        | 10           |             | ns      | (Notes 3, 12)                         |

| t <sub>47</sub> | CTS High to TCLK Low;<br>CTS Setup Time to Stop<br>Transmission | 35           |             | ns      | (Note 3)                              |

| IFS PARA        | METERS                                                          |              | ·           |         |                                       |

| t <sub>48</sub> | Interframe Delay                                                | (Note 4)     |             | ns      |                                       |

|                 | · · · · · · · · · · · · · · · · · · ·                           | ·            | I           |         |                                       |

### **HIGH INTEGRATION MODE (Continued)**

| Symbol          | Parameter                                                 | Min      | Max      | Units | Test Conditions |

|-----------------|-----------------------------------------------------------|----------|----------|-------|-----------------|

| COLLISIO        | N DETECT PARAMETERS                                       |          |          | -     |                 |

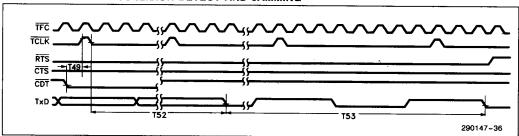

| t <sub>49</sub> | CDT Low to TCLK High External Collision Detect Setup Time | 35       |          | ns    | (Note 12)       |

| t <sub>50</sub> | CDT High to TCLK High                                     | 35       |          | ns    | (Note 12)       |

| t <sub>51</sub> | TCLK High to CDT Inactive CDT Hold Time                   | 10       |          | ns    | (Note 12)       |

| t <sub>52</sub> | CDT Low to Jamming Start                                  |          | (Note 5) | ns    |                 |

| t <sub>53</sub> | Jamming Period                                            | (Note 6) |          | ns    |                 |

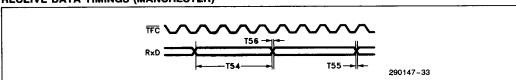

### RECEIVED DATA PARAMETERS (MANCHESTER, DIFFERENTIAL MANCHESTER)

| t <sub>54</sub> | RxD Transition-Transition | 115 |    | ns | (Note 14) |

|-----------------|---------------------------|-----|----|----|-----------|

| t <sub>55</sub> | RxD Rise Time             |     | 10 | ns | ,         |

| t <sub>56</sub> | RxD Fall Time             |     | 10 | ns |           |

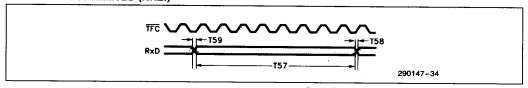

### RECEIVED DATA PARAMETERS (NRZI)

| t <sub>57</sub> | RxD Transition-Transition | 240 |    | ns | (Note 11) |

|-----------------|---------------------------|-----|----|----|-----------|

| t <sub>58</sub> | RxD Rise Time             |     | 10 | ns |           |

| t <sub>59</sub> | RxD Fall Time             |     | 10 | ns |           |

### **EXTERNAL LOOPBACK PARAMETERS**

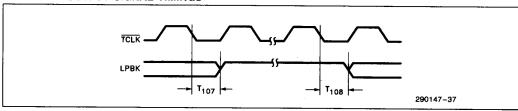

| t <sub>107</sub> | TCLK Low to LPBK High  | 50 | ns | (Note 2) |

|------------------|------------------------|----|----|----------|

| t <sub>108</sub> | TCLK Low to LPBK Float | 50 | ns | (Note 2) |

### NOTES:

- 1. MOS Levels.

- 1 TTL Load + 50 pF.

- 3. Abnormal End of Transmission: CTS expires before

- Programmable value: t<sub>28</sub> = N<sub>IFS</sub> × t<sub>29</sub> (ns) NIES: the IFS configuration value.

If N<sub>IFS</sub> is less than 12 then it is enforced to 12.

5. Programmable Values:

$t_{52}$  = N<sub>CDF</sub>  $\times$   $t_{29}$  + (12 to 15)  $\times$   $t_{29}$  (if collision occurs after preamble).

N<sub>CDF</sub>: The Collision Detect Filter Configuration Value.

6.  $t_{53} = 32 \times t_{29}$

7. Depends on frequency range:

High Range:  $t_{24} - 10$  ns Low Range:  $t_{25} - 10$  ns 8.  $t_{31} = t_{29} - t_{30} - t_{32} - t_{33}$ 9.  $2 \times t_{24} + 40$  ns for 8X or 10X

$4 \times t_{24} + 40 \text{ ns for } 16X$

10. 6 imes t<sub>24</sub> + 40 ns for 8X

$12 \times t_{24} + 40$  ns for 16X  $7 \times t_{24} + 40$  ns for 10X

$13 \times t_{24} + 40$  ns for 18X

11. 8  $\times$  t<sub>24</sub> - 10 ns for 8X

$\begin{array}{c} 10 \times t_{24} - 10 \text{ ns for } 10\text{X} \\ 16 \times t_{24} - 10 \text{ ns for } 16\text{X} \\ 18 \times t_{24} - 10 \text{ ns for } 18\text{X} \end{array}$

12. To Guarantee recognition on the next clock.

13. 10 ns for High Range

30 ns for Low Range

14.  $4 \times t_{24} - 10$  ns for 8X  $5 \times t_{24} - 10$  ns for 10X