# PA7128 PEEL™ Array Programmable Electrically Erasable Logic Array

1

### **Features**

- CMOS Electrically Erasable Technology

- Reprogrammable in 28-pin DIP, SOIC and PLCC packages

- Versatile Logic Array Architecture

- 12 I/Os, 14 inputs, 36 registers/latches

- Up to 36 logic cell output functions

- PLA structure with true product-term sharing

- Logic functions and registers can be I/O-buried

- Flexible Logic Cell

- Up to 3 output functions per logic cell

- D,T and JK registers with special features

- Independent or global clocks, resets, presets, clock polarity and output enables

- Sum-of-products logic for output enables

- **■** High-Speed Commercial and Industrial Versions

- As fast as 9ns/15ns (tpdi/tpdx), 83.3MHz (fMAX)

- Industrial grade available for 4.5 to 5.5V Vcc and -40 to +85 °C temperatures

- Ideal for Combinatorial, Synchronous and Asynchronous Logic Applications

- Integration of multiple PLDs and random logic

- Buried counters, complex state-machines

- Comparitors, decoders, other wide-gate functions

- **■** Development and Programmer Support

- ICT PLACE Development Software

- Fitters for ABEL, CUPL and other software

- Programming support by ICT PDS-3 and other popular third-party programmers.

## **General Description**

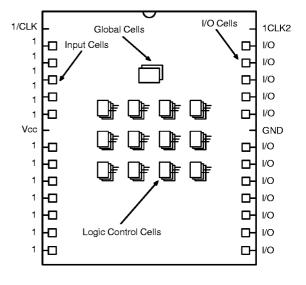

The PA7128 is a member of the Programmable Electrically Erasable Logic (PEEL) Array family based on ICT's CMOS EEPROM technology. PEEL Arrays free designers from the limitations of ordinary PLDs by providing the architectural flexibility and speed needed for today's programmable logic designs. The PA7128 offers a versatile logic array architecture with 12 I/O pins, 14 input pins and 36 registers/latches (12 buried logic cells, 12 input registers/latches, 12 buried I/O registers/latches). Its logic array implements 50 sum-of-products logic functions that share 64 product terms. The PA7128's logic and I/O cells (LCCs, IOCs) are extremely flexible offering up to three output functions per cell (a total of 36 for all 12 logic cells). Cells are configurable as D, T and JK registers with independent or global clocks, resets,

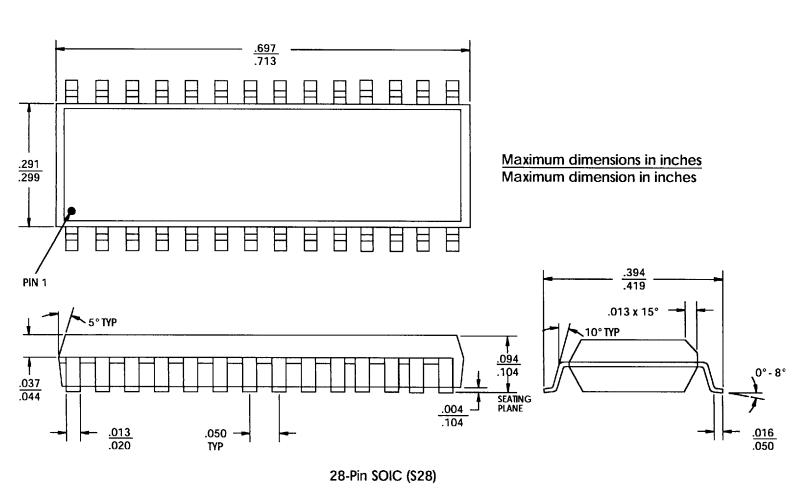

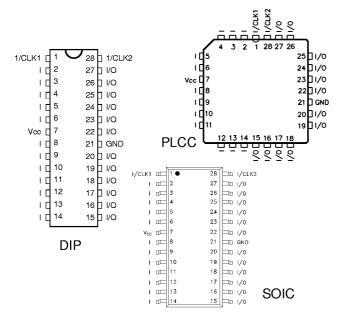

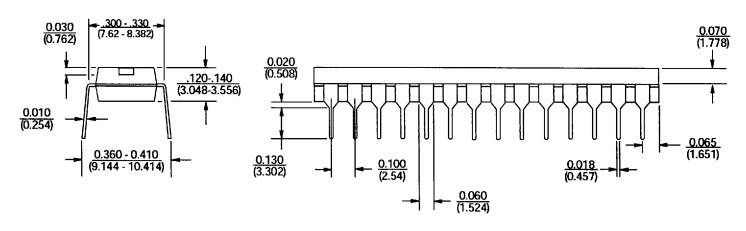

presets, clock polarity and other special features, making the PA7128 suitable for a variety of combinatorial, synchronous and asynchronous logic applications. The PA7128 offers pin compatibility and super-set functionality to popular 28-pin PLDs, such as the 26V12. Thus, designs that exceed the architectures of such devices can be expanded upon. The PA7128 supports speeds as fast as 9ns/15ns (tpdi/tpdx) and 83.3MHz (fMAX) at moderate power consumption 105mA (75mA typical). Packaging includes 28-pin DIP, SOIC and PLCC (see Figure 1). Development and programming support for the PA7128 is provided by ICT and popular third-party development tool manufacturers.

Figure 1. Pin Configuration

Figure 2. Block Diagram

This device has been designed and tested for the recommended operating conditions. Proper operation outside of these levels is not guaranteed. Exposure to absolute maximum ratings may cause permanent damage

## **Table 2. Absolute Maximum Ratings**

| Symbol | Parameter                  | Conditions                      | Ratings           | Unit |

|--------|----------------------------|---------------------------------|-------------------|------|

| Vcc    | Supply Voltage             | Relative to Ground              | -0.5 to + 7.0     | V    |

| VI, VO | Voltage Applied to Any Pin | Relative to Ground <sup>1</sup> | -0.5 to VCC + 0.6 | V    |

| lo lo  | Output Current             | Per pin (IOL, IOH)              | ±25               | mA   |

| TST    | Storage Temperature        |                                 | -65 to + 150      | °C   |

| TLT    | Lead Temperature           | Soldering 10 seconds            | +300              | °C   |

## **Table 3. Operating Ranges**

| Symbol | Parameter           | Conditions | Min  | Max  | Unit |  |

|--------|---------------------|------------|------|------|------|--|

| Vcc    | Supply Voltage      | Commercial | 4.75 | 5.25 | - v  |  |

|        |                     | Industrial | 4.5  | 5.5  |      |  |

| ТА     | Ambient Temperature | Commercial | 0    | +70  | °C   |  |

|        |                     | Industrial | -40  | +85  | 30   |  |

| TR     | Clock Rise Time     | See Note 2 |      | 20   | ns   |  |

| TF     | Clock Fall Time     | See Note 2 |      | 20   | ns   |  |

| TRVCC  | VCC Rise Time       | See Note 2 |      | 250  | ms   |  |

Table 4. D.C. Electrical Characteristics

Over the recommended operating conditions

| Symbol            | Parameter                                 | Conditions                             |                               | Min                     | Max       | Unit |

|-------------------|-------------------------------------------|----------------------------------------|-------------------------------|-------------------------|-----------|------|

| VOH               | Output HIGH Voltage - TTL                 | VCC = Min, IOH = -4.0mA                |                               | 2.4                     |           | V    |

| VOHC              | Output HIGH Voltage - CMOS                | VCC = Min, IOH = -10μA                 |                               | VCC - 0.3               |           | V    |

| VOL               | Output LOW Voltage - TTL                  | VCC = Min, IOL = 16mA                  |                               |                         | 0.5       | V    |

| Volc              | Output LOW Voltage - CMOS                 | VCC = Min, IOL = -10μA                 |                               |                         | 0.15      | V    |

| VIH               | Input HIGH Level                          |                                        |                               | 2.0                     | VCC + 0.3 | V    |

| VIL               | Input LOW Level                           |                                        |                               | -0.3                    | 0.8       | V    |

| IIL               | Input Leakage Current                     | VCC = Max, GND ≤ VIN ≤ VCC             |                               |                         | ±10       | μΑ   |

| loz               | Output Leakage Current                    | I/O = High-Z, GND ≤ VO ≤ VCC           |                               |                         | ±10       | μΑ   |

| ISC               | Output Short Circuit Current <sup>4</sup> | VCC = 5V, VO = 0.5V, TA= 25°           | VCC = 5V, VO = 0.5V, TA= 25°C |                         | -120      | mA   |

|                   |                                           | VIN = 0V or VCC <sup>3,11</sup>        | -15                           |                         | 105       |      |

| ICC <sup>10</sup> | VCC Current                               | f = 25MHz                              | -20                           | 75 (typ.) <sup>19</sup> | 105       | mA   |

|                   |                                           | All outputs disabled <sup>4</sup> I-20 |                               | 1                       | 115       |      |

| CIN <sup>7</sup>  | Input Capacitance <sup>5</sup>            | TA = 25°C, VCC = 5.0V                  |                               |                         | 6         | pF   |

| COUT <sup>7</sup> | Output Capacitance <sup>5</sup>           | @ f = 1 MHz                            | <b>⊒</b>                      |                         | 12        | pF   |

2

04-02-027D

### **A.C Electrical Characteristics Combinatorial**

|          |                                                     |     | -15 -20 |     | 1 -20 |      |

|----------|-----------------------------------------------------|-----|---------|-----|-------|------|

| Symbol   | Parameter <sup>6,12</sup>                           | Min | Max     | Min | Max   | Unit |

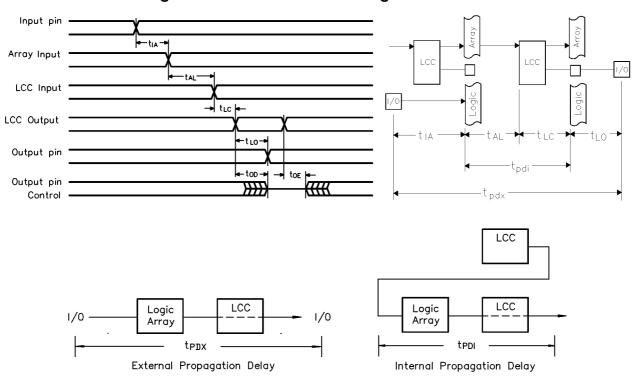

| tPDI     | Propagation delay Internal (tAL + tLC)              |     | 9       |     | 12    | ns   |

| tPDX     | Propagation delay External (tIA + tAL +tLC + tLO)   |     | 15      |     | 20    | ns   |

| tiA      | Input or I/O pin to array input                     |     | 2       |     | 3     | ns   |

| tAL      | Array input to LCC                                  |     | 8       |     | 10    | ns   |

| tLC      | LCC input to LCC output <sup>10</sup>               |     | 1       |     | 2     | ns   |

| tLO      | LCC output to output pin                            |     | 4       |     | 5     | ns   |

| tOD, tOE | Output Disable, Enable from LCC output <sup>7</sup> |     | 4       |     | 5     | ns   |

| tox      | Output Disable, Enable from input pin <sup>7</sup>  |     | 15      |     | 20    | ns   |

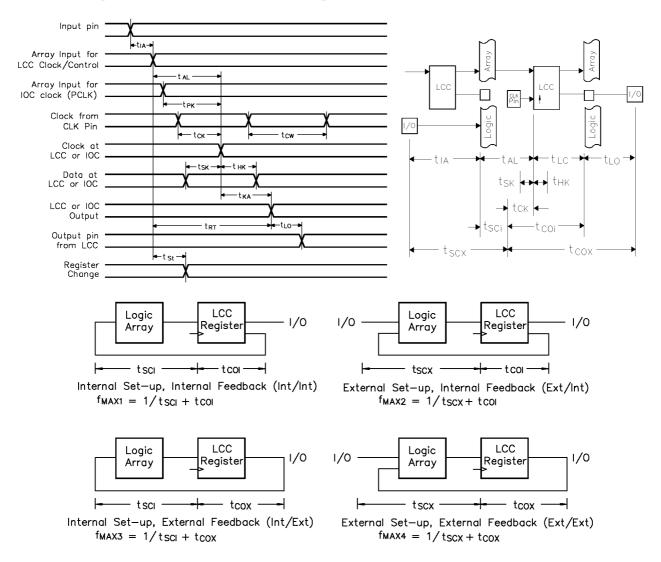

## **Combinatorial Timing - Waveforms and Block Diagram**

3 04-02-027D

# A.C. Electrical Characteristics Sequential

| Symbol |                                                                                          | -2  | 20   | -20 / I-20 |      | -20 / I-20 |  | Unit |

|--------|------------------------------------------------------------------------------------------|-----|------|------------|------|------------|--|------|

|        | Parameter <sup>6,12</sup>                                                                | Min | Max  | Min        | Max  |            |  |      |

| tsci   | Internal set-up to system clock <sup>8</sup> - LCC <sup>14</sup> (tAL + tSK + tLC - tCK) | 5   |      | 7          |      | ns         |  |      |

| tSCX   | Input <sup>16</sup> (EXT.) set-up to system clock, - LCC (tIA + tSCI)                    | 7   |      | 10         |      | ns         |  |      |

| tCOI   | System-clock to Array Int LCC/IOC/INC <sup>14</sup> (tCK +tLC)                           |     | 7    |            | 9    | ns         |  |      |

| tCOX   | System-clock to Output Ext LCC (tCOI + tLO)                                              |     | 11   |            | 14   | ns         |  |      |

| tHX    | Input hold time from system clock - LCC                                                  | 0   |      | 0          |      | ns         |  |      |

| tsk    | LCC Input set-up to async. clock <sup>13</sup> - LCC                                     | 2   |      | 2          |      | ns         |  |      |

| tAK    | Clock at LCC or IOC - LCC output                                                         | 1   |      | 1          |      | ns         |  |      |

| tHK    | LCC input hold time from system clock - LCC                                              | 4   |      | 4          |      | ns         |  |      |

| tsı    | Input set-up to system clock - IOC/INC <sup>14</sup> (tSK - tCK)                         | 0   |      | 0          |      | ns         |  |      |

| tHI    | Input hold time from system clock - IOC/INC <sup>14</sup> (tSK - tCK)                    | 4   |      | 5          |      | ns         |  |      |

| tPK    | Array input to IOC PCLK clock                                                            |     | 6    |            | 7    | ns         |  |      |

| tSPI   | Input set-up to PCLK clock <sup>18</sup> - IOC/INC (tSK-tPK-tIA)                         | 0   |      | 0          |      | ns         |  |      |

| tHPI   | Input hold from PCLK clock <sup>18</sup> - IOC/INC (tPK+tIA-tSK)                         | 6   |      | 8          |      | ns         |  |      |

| tSD    | Input set-up to system clock - IOC/INC Sum-D <sup>15</sup> (tIA + tAL + tLC + tSK - tCK) | 7   |      | 10         |      | ns         |  |      |

| tHD    | Input hold time from system clock - IOC Sum-D                                            | 0   |      | 0          |      | ns         |  |      |

| tSDP   | Input set-up to PCLK clock<br>(tIA + tAL + tLC + tSK - tPK) - IOC Sum-D                  | 7   |      | 10         |      | ns         |  |      |

| tHDP   | Input hold time from PCLK clock - IOC Sum-D                                              | 0   |      | 0          |      | ns         |  |      |

| tCK    | System-clock delay to LCC/IOCINC                                                         |     | 6    |            | 7    | ns         |  |      |

| tCW    | System-clock low or high pulse width                                                     | 6   |      | 7          |      | ns         |  |      |

| fMAX1  | Max. system-clock frequency Int/Int 1/(tSCI + tCOI)                                      |     | 83.3 |            | 62.5 | MHz        |  |      |

| fMAX2  | Max. system-clock frequency Ext/Int 1/(tSCX + tCOI)                                      |     | 71.4 |            | 52.6 | MHz        |  |      |

| fMAX3  | Max. system-clock frequency Int/Ext 1/(tSCI + tCOX)                                      |     | 62.5 |            | 47.6 | MHz        |  |      |

| fMAX4  | Max. system-clock frequency Ext/Ext 1/(tSCX + tCOX)                                      |     | 55.5 |            | 41.6 | MHz        |  |      |

| fTGL   | Max. system-clock toggle frequency 1/(tCW + tCW)                                         |     | 83.3 |            | 71.4 | MHz        |  |      |

| tPR    | LCC presents/reset to LCC output                                                         |     | 1    |            | 2    | ns         |  |      |

| tsT    | Input to Global Cell present/reset (tIA + tAL + tPR)                                     |     | 11   |            | 15   | ns         |  |      |

| tAW    | Asynch. preset/reset pulse width                                                         | 8   |      | 8          |      | ns         |  |      |

| tRT    | Input to LCC Reg-Type (RT)                                                               |     | 7    |            | 9    | ns         |  |      |

| trtv   | LCC Reg-Type to LCC output register change                                               |     | 1    |            | 2    | ns         |  |      |

| tRTC   | Input to Global Cell register-type change (tRT + tRTV)                                   |     | 8    |            | 11   | ns         |  |      |

| tRW    | Asynch. Reg-Type pulse width                                                             | 10  |      | 10         |      | ns         |  |      |

| tRESET | Power-on reset time for registers in clear state <sup>2</sup>                            |     | 5    |            | 5    | μs         |  |      |

04-02-027D

### **Sequential Timing - Waveforms and Block Diagram**

5

#### Notes:

- Minimum DC input is -0.5V, however inputs may under-shoot to -2.0V for periods less than 20ns.

- 2. Test points for Clock and Vcc in tR, tF, tcL, tcH, and tRESET are referenced at 10% and 90% levels.

- 3. I/O pins are 0V or Vcc.

- 4. Test one output at a time for a duration of less than 1 sec.

- 5. Capacitances are tested on a sample basis.

- Test conditions assume: signal transition times of 5ns or less from the 10% and 90% points, timing reference levels of 1.5V (unless otherwise specified).

- 7. toE is measured from input transition to VREF ( 0.1V (See test loads at end of Section 6 for VREF value). toD is measured from input transition to VOH -0.1V or VOL +0.1V.

- 8. "System-clock" refers to pin 1 or pin 28 high speed clocks.

- 9. For T or JK registers in toggle (divide by 2) operation only.

- 10. For combinatorial and async-clock to LCC output delay.

- 11. ICC for a typical application: This parameter is tested with the device programmed as a 10-bit D-type counter.

- 12. Test loads are specified in Section 5 of this Data Book.

- 13. "Async. clock" refers to the clock from the Sum term (OR gate).

- 14. The "LCC" term indicates that the timing parameter is applied to the LCC register. The "IOC" term indicates that the timing parameter is applied to the IOC register. The "LCC/IOC" term indicates that the timing parameter is applied to both the LCC and IOC registers. The "LCC/ IOC/INC" term indicates that the timing parameter is applied to the LCC, IOC and INC registers.

- 15. This refers to the Sum-D gate routed to the IOC register for an additional buried register

- 16. The term "Input" without any reference to another term refers to an (external) input pin.

- 17. The parameter tsplindicates that the PCLK signal to the IOC register is always slower than the data from the pin or input by the absolute value of (tsk-tpk-tla). This means that no set-up time for the data from the pin or input is required, i.e. the external data and clock can be sent to the device simultaneously. Additionally, the data from the pin must remain stable for the time, i.e. to wait for the PCLK signal to arrive at the IOC register.

- 18. Typical (typ) Icc is measured at Ta =25  $_{\circ}$  C, Freq = 25MHz, Vcc =5V.

04-02-027D

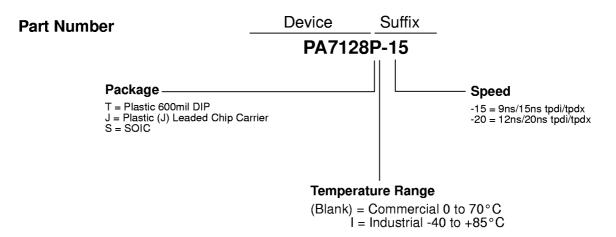

**Table 2. Ordering Information**

| Part Number | Speed    | Temperature | Package |  |

|-------------|----------|-------------|---------|--|

| PA7128P-15  |          |             | P28     |  |

| PA7128J-15  | 9/15ns   | С           | J28     |  |

| PA7128S-15  | ]        |             | S28     |  |

| PA7128P-20  | 12/20ns  | С           | P28     |  |

| PA7128PI-20 | 12/20118 | I           | F20     |  |

| PA7128J-20  | 12/20ns  | С           | J28     |  |

| PA7128JI-20 | 12/20118 | I           | J28     |  |

| PA7128S-20  | 12/20ns  | С           | S28     |  |

| PA7128SI-20 | 12/20118 | I           | 520     |  |

6 04-02-027D

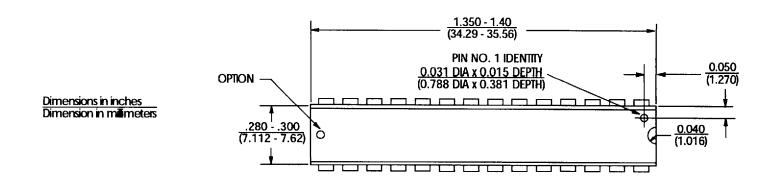

28-Pin Plastic DIP (P28)