# LCD Super VGA Controller Chip

## 1.0 Introduction

The OPTi 92C178, a fully integrated follow-on to the OPTi 92C168, provides an unmatched price/performance LCD VGA solution for portable IBM® compatible personal computers. The 92C178 offers high performance, full integration, low power consumption, complete panel support, and simultaneous LCD/CRT display as part of a highly integrated graphics subsystem.

High performance is made possible by a built-in fixed function graphics accelerator. The accelerator supports BitBlt, polygon fill, line draw, color expansion, and clipping. Acceleration is supported for pixel depths of 8, 15, 16, and 24 bits/pixel. Hardware cursor support and linear addressing support further enhance performance in GUI environments by removing software cursor overhead and eliminating bank switching.

The RAMDAC and clock synthesizer are built into the 92C178. No external logic is required to connect to the 16-bit ISA, 16/32-bit Local bus, or PCI bus. Panels may be driven directly without external drive buffers or separate frame buffer memory (dual scan panels). A complete LCD VGA video subsystem can be implemented with two 256Kx16 DRAM chips.

The 92C178 is optimized for minimum power consumption during normal operation and provides three power saving modes. 3.3V/5V mixed voltage operation helps to further reduce video subsystem power consumption.

The 92C178 supports a wide variety of dual scan color/mono STN, single scan color/mono STN and TFT panels. Panel resolutions of 640x480, 800x600 and 1024x768 are supported. The 92C178 supports up to 16.8 million colors on color panels and up to 256 gray scales on monochrome panels.

The 92C178 supports CRT display resolutions up to 1280x1024-256 colors. LCD display is provided at resolutions up to 1024x768 non-interlaced.

The OPTi 92C178 is 100% register level compatible with the IBM VGA standard. OPTi supplies a fully compatible VGA/ VESA BIOS, drivers for common applications and operating systems, such as AutoCAD and Windows, and OEM and end-user level utility software.

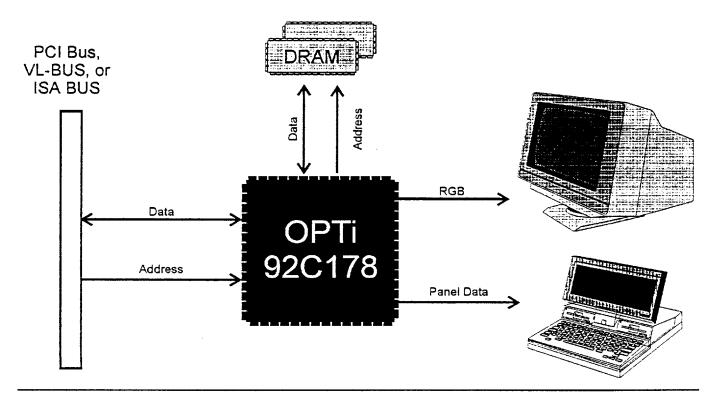

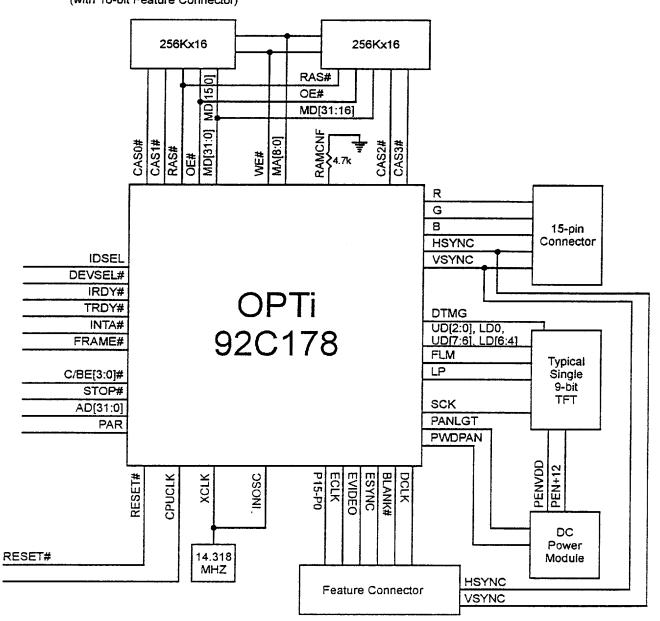

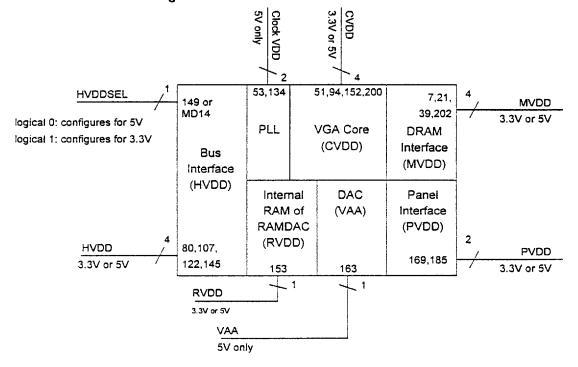

Figure 1-1 OPTi 92C178 System Block Diagram

912-3000-027

Page 1

9004196 0000047 482 📟

# 2.0 Features

| 2.1 Features                                                                                                                                                                                    | 2.2 Benefits                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Integrated true color RAMDAC and clock.                                                                                                                                                         | Full integration. One chip solution.                                                                           |

| Built-in graphics accelerator. Supports BitBlt, polygon fill, line draw, color expansion and clipping.                                                                                          | Superior performance.                                                                                          |

| 32-bit direct interface with VESA local bus and PCI bus, and 16-bit direct interface with ISA bus.                                                                                              | No external glue logic. Reduced footprint design. Cost savings.                                                |

| Direct interface to dual scan color/mono STN, single scan color/mono STN, and TFT panels.                                                                                                       | No drive buffer or additional video frame buffer requirement. Reduced footprint design.                        |

| Support for 800x600 panels:  STN type  TFT type  Expansion of standard VGA modes to 800x600                                                                                                     | Provides complete support for new generation laptops which use 800x600 panels.                                 |

| Advanced power management to minimize power consumption:  Remove backlight power.  Hardware/Software activated Standby Mode.  Hardware/Software activated Suspend Mode.  Deep Sleep Mode.  DPMS | Extends battery life. Flexible power-down options.                                                             |

| 3.3V/5V mixed voltage operation.                                                                                                                                                                | Optimizes power consumption.                                                                                   |

| Flexible DRAM configurations: One/two/four 256Kx16 DRAMs, Four/eight/sixteen 256Kx4 DRAMs.                                                                                                      | Design flexibility for 1MB or 2MB implementations. Facilitates cost-effective graphics frame buffer solutions. |

| Support simultaneous display for dual scan STN panel with one 256Kx16 DRAM.                                                                                                                     | Reduced footprint design. Cost savings for base system.                                                        |

| Hardware cursor (32x32x2 and 64x64x2 cursor sizes supported).                                                                                                                                   | No distracting cursor flicker. Improved performance.                                                           |

| Hardware pop-up icon (64x64x2 and 128x128x2 icon sizes supported).                                                                                                                              | Use icon as a second hardware cursor to display system status.                                                 |

| Supports up to 16.8 million colors on both CRT and color LCD displays.                                                                                                                          | Superior color display quality on both LCDs and CRTs.                                                          |

| Supports up to 256 gray shades for mono LCD displays.                                                                                                                                           | Superior monochrome display quality on LCD panels.                                                             |

| Supports the following LCD display adjustment features:     Text mode contrast enhancement.     Reverse video for graphics and text modes.     Vertical expansion and auto-centering.           | Provides display flexibility to meet individual requirements.                                                  |

| <ul><li>Screen Saver Option</li><li>Blanks screen</li><li>HW cursor and pop-up icon remain on the display</li></ul>                                                                             | Easy to implement. Operating system independent.                                                               |

| Programmable linear addressing.                                                                                                                                                                 | Eliminates bank switching.                                                                                     |

| 100% hardware/BIOS compatible with IBM VGA standard.                                                                                                                                            | Allows use of any VGA compatible software with the video subsystem.                                            |

| Multimedia Features  VAFC compatible feature connector  Overlay  Genlock                                                                                                                        | Multimedia ready.                                                                                              |

912-3000-027

9004196 0000048 319

#### 2.3 Architecture

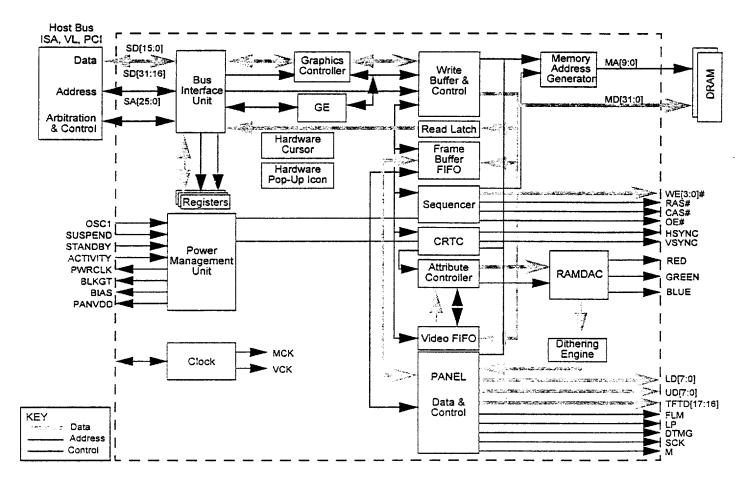

The OPTi 92C178 contains the following major functional modules:

- Bus Interface Unit

- Write Buffer Control Unit

- · Graphic Controller

- Memory Sequencer

- Video FIFO

- CRT Controller

- Attribute Controller

- GUI Engine

- · Hardware Cursor

- Pop-up icon

- Frame Buffer Controller

- RAMDAC

- Dithering Engine

- · Flat Panel Interface Controller

- · Power Management Unit

- Power Distribution Module

- · Clock Synthesizer

- · Multi-media Module

The function of each module is described in Section 4.0, Bus Interface Unit.

Figure 2-1 OPTi 92C178 Functional Block Dia-

#### gram

912-3000-027

#### 2.4 Example Controller Block Diagrams

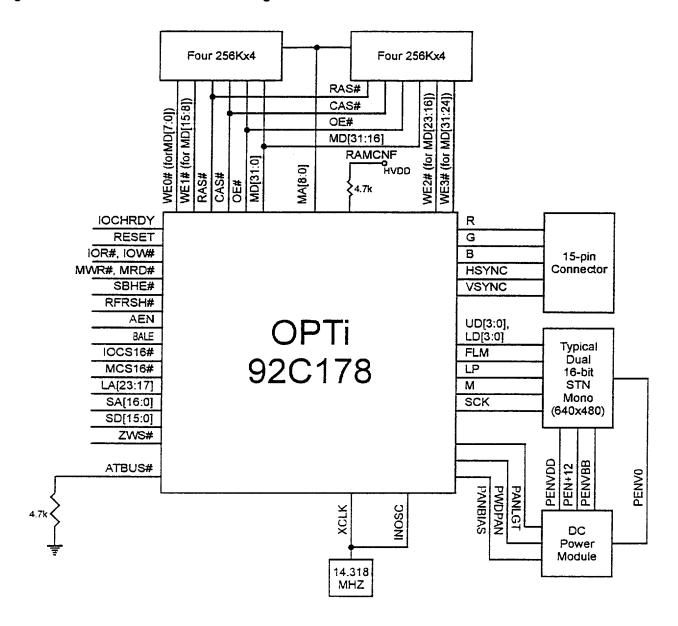

Figure 2-2 1MB ISA-Bus Solution using Dual Scan Monochrome Panel

Page 4

9004196 0000050 777

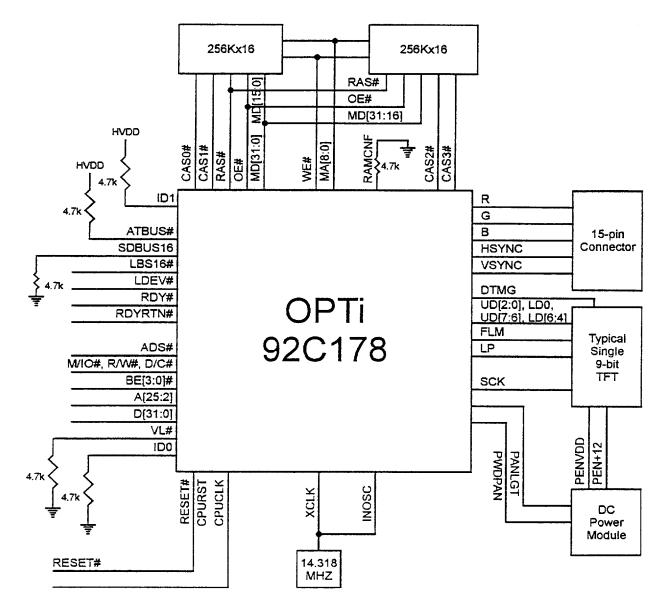

Figure 2-3 1MB 486DX VL-Bus Solution using 9-bit TFT Color Panel

Figure 2-4 1MB 486DX PCI -Bus Solution using 9-bit TFT Color Panel (with 16-bit Feature Connector)

Page 6

| 9004196 0000052 84T **|**|

## 2.4.1 Definitions of MD31-MD0 at System Reset

Table 2-1 lists the definitions of MD31-MD0 at system reset. To set the given MD bit to a logical 1, pull high through a 4.7Kohm resistor. To set the given bit to a logical 0, pull low through a  $4.7K\Omega$  resistor.

NOTE MD31-MD16 do not directly set any register bits in the chip. The OPTi BIOS resets MD31-MD16 and then sets the 92C178 register bits appropriately.

Table 2-1 MD31-MD0 Definitions at Reset

| MD <sup>a</sup> | Logica  | al Level | Definition                                                                                                                                                               |        |  |  |  |

|-----------------|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|

| MD31            |         | 1        | Enables Feature Connector. For feature connector enabled, MD definitions for MD15-MD8 hold.                                                                              |        |  |  |  |

|                 |         | 0        | Disables Feature Connector. For feature connector disabled, MD15-MD8 are not used since configuration pins backward compatible to the 92C168 are available.  See Note 1. |        |  |  |  |

| MD30            |         | 1        | Enable PCI BIOS interface.                                                                                                                                               |        |  |  |  |

|                 |         | 0        | Disable PCI BIOS interface.                                                                                                                                              |        |  |  |  |

| MD29-26         | 1       |          | Reserved                                                                                                                                                                 |        |  |  |  |

| MD25            |         | 1        | Indicates 3.3V CVDD                                                                                                                                                      |        |  |  |  |

|                 |         | 0        | Indicates 5V CVDD                                                                                                                                                        |        |  |  |  |

| MD24            |         | 1        | Indicates 3.3V panel interface                                                                                                                                           |        |  |  |  |

|                 | 0       |          | Indicates 5V panel interface                                                                                                                                             |        |  |  |  |

| MD23            | 1       |          | Indicates 3.3V memory interface                                                                                                                                          |        |  |  |  |

|                 | (       | )        | Indicates 5V memory interface                                                                                                                                            |        |  |  |  |

| MD22            |         | 1        | Selects single scan panel                                                                                                                                                |        |  |  |  |

|                 | (       | )        | Selects dual scan panel                                                                                                                                                  |        |  |  |  |

| MD21 - MD20     | Selects | panel da | ta interface width                                                                                                                                                       |        |  |  |  |

|                 | MD21    | MD20     | STN                                                                                                                                                                      | TFT    |  |  |  |

|                 | 0       | 0        | mono 4-bit (single), mono 8-bit (dual)                                                                                                                                   | 9-bit  |  |  |  |

|                 | 0       | 1        | mono 8-bit (single)                                                                                                                                                      | 12-bit |  |  |  |

|                 | 1       | 0        | color 8-bit                                                                                                                                                              | 3-bit  |  |  |  |

|                 | 1       | 1        | color 16-bit                                                                                                                                                             | 18-bit |  |  |  |

| MD19            | 1       |          | Selects TFT panel                                                                                                                                                        |        |  |  |  |

|                 | (       | )        | Selects STN panel                                                                                                                                                        |        |  |  |  |

| MD18            |         | 1        | Selects high resolution panel (800x600 or 1024x768)                                                                                                                      |        |  |  |  |

| 0               |         |          | Selects 640x480 panel                                                                                                                                                    |        |  |  |  |

Table 2-1 MD31-MD0 Definitions at Reset (cont.)

| MD <sup>a</sup> | Logica      | al Level | Definition                          |  |  |  |  |

|-----------------|-------------|----------|-------------------------------------|--|--|--|--|

| MD17 - MD16     | Selects     | the num  | nber of Line Pulses per Frame       |  |  |  |  |

|                 | MD17        | MD16     | Line Pulses per Frame               |  |  |  |  |

|                 | 0           | 0        | 240                                 |  |  |  |  |

|                 | 0           | 1        | 242                                 |  |  |  |  |

|                 | 1           | 0        | 244                                 |  |  |  |  |

|                 | 1           | 1        | 800x600 (STN or TFT)                |  |  |  |  |

| MD15            |             | 1        | Select dual WE# DRAM                |  |  |  |  |

|                 | (           | כ        | Select dual CAS# DRAM               |  |  |  |  |

| MD14            |             | 1        | 46E8 is the VGA enable port         |  |  |  |  |

|                 | (           | )        | 3C3 is the VGA enable port          |  |  |  |  |

| MD13            |             | 1        | Selects 16-bit data bus             |  |  |  |  |

|                 | (           | )        | Selects 32-bit data bus             |  |  |  |  |

| MD12            | 1           | 1        | Select local bus                    |  |  |  |  |

|                 | (           | )        | Select AT bus                       |  |  |  |  |

| MD11-MD10       | Bus ID pins |          |                                     |  |  |  |  |

|                 | MD11        | MD10     | Bus ID                              |  |  |  |  |

|                 | 0           | 0        | PCI Bus                             |  |  |  |  |

|                 | 0           | 1        | 386 VL-Bus                          |  |  |  |  |

|                 | 1           | 0        | 486 VL-Bus                          |  |  |  |  |

|                 | 1           | 1        | Reserved                            |  |  |  |  |

| MD9             | 1           |          | Selects general local bus interface |  |  |  |  |

|                 | С           | )        | Selects VESA local bus interface    |  |  |  |  |

| MD8             | 1           |          | Selects 3.3V for Host Bus Interface |  |  |  |  |

|                 | C           | )        | Selects 5V for Host Bus Interface   |  |  |  |  |

| MD7-MD0         |             | -        | Reserved                            |  |  |  |  |

a. MD15-MD8 are used when the feature connector option is enabled. See feature connector pinout definitions in Section 3.3.11 for details regarding the multiplexed definitions of the feature connector pins.

OPTi

Page 8

**9004196 0000054 612**

# 3.0 Signal Descriptions

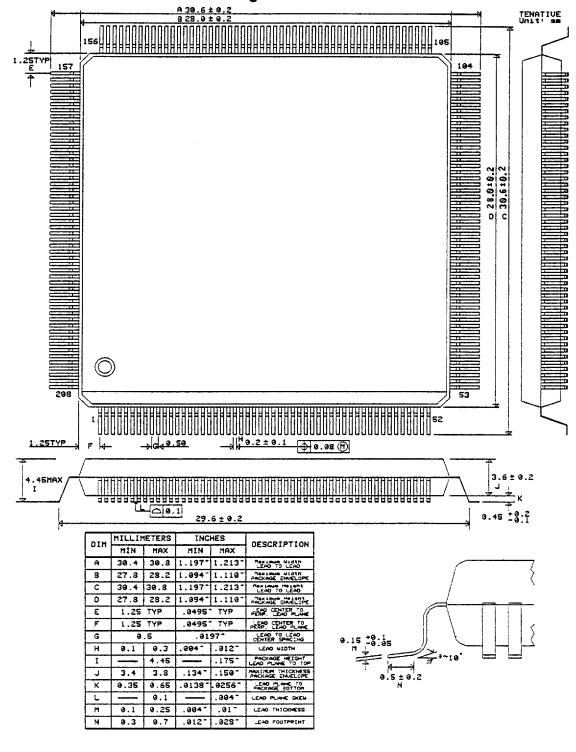

## 3.1 Pin Diagrams

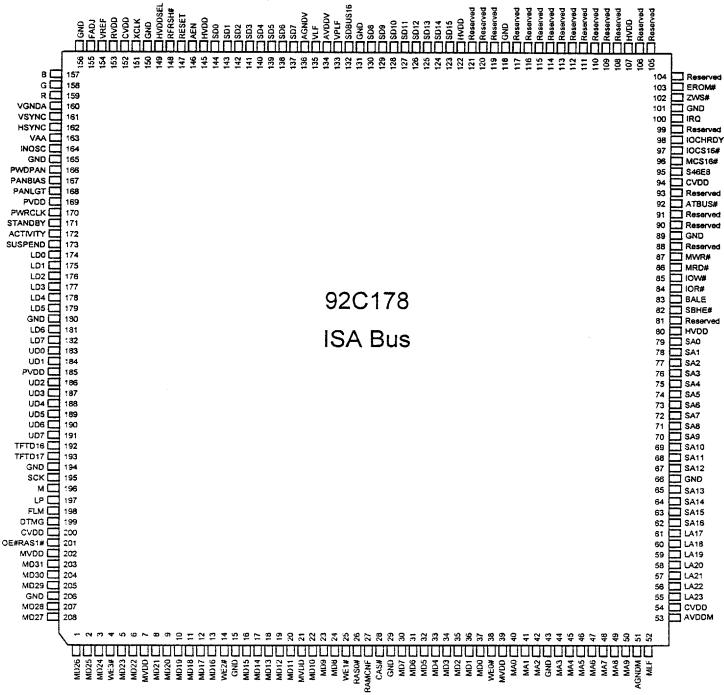

Figure 3-1 ISA Bus Pin Diagram

912-3000-027

**-** 9004196 0000055 559 **-**

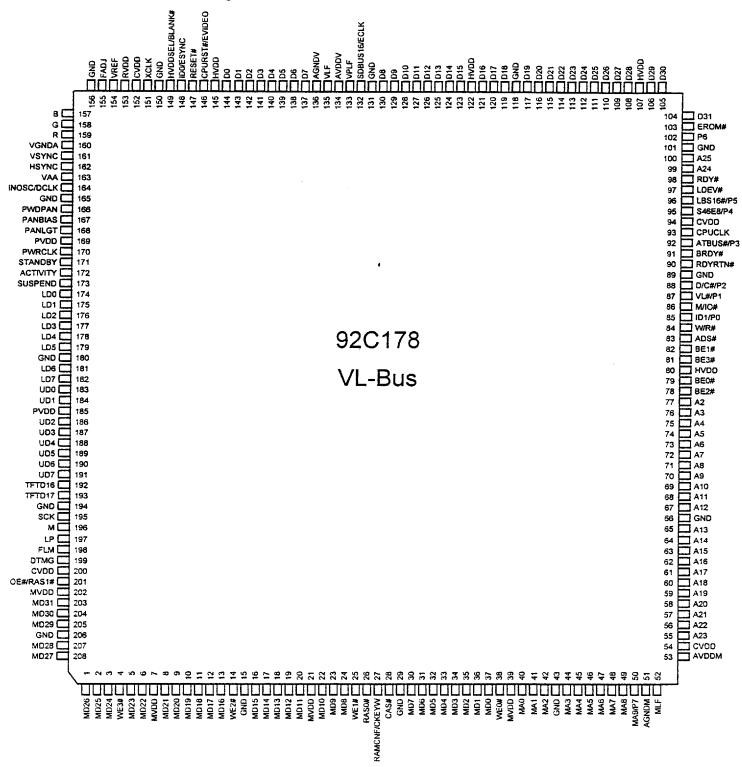

Figure 3-2 VL-Bus Pin Diagram

Page 10

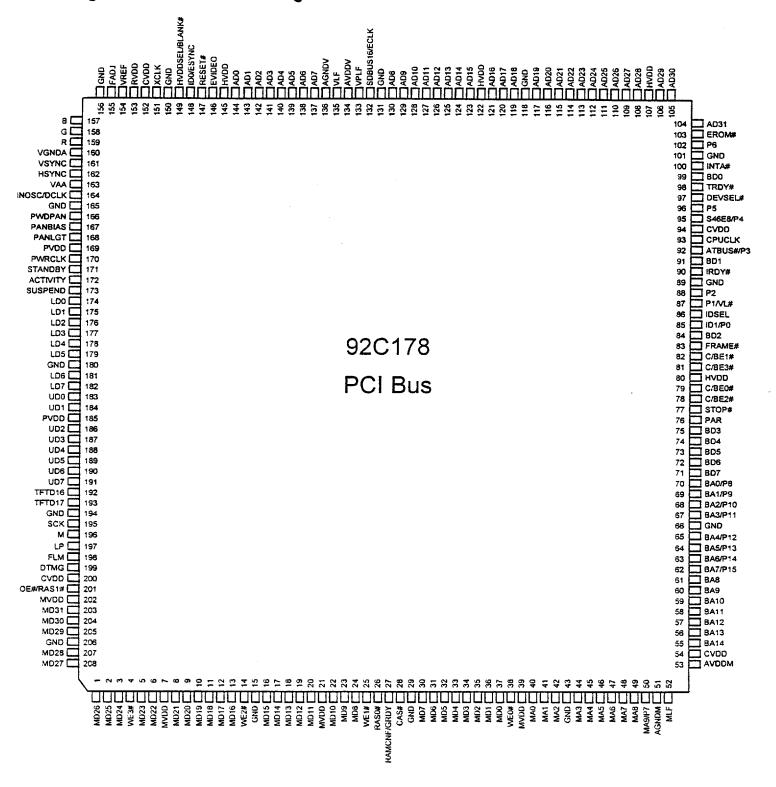

Figure 3-3 PCI Bus Pin Diagram

912-3000-027

9004196 0000057 321 🚥

## 3.2 Pin Cross-Reference Lists

## 3.2.1 Alphabetical Pin List-ISA Bus

| Pin | Name        | Pin | Name    | Pin | Name   | Pin | Name      | Pin | Name    |

|-----|-------------|-----|---------|-----|--------|-----|-----------|-----|---------|

| 81  |             | 29  | GND     | 40  | MAO    | 203 | MD31      | 143 | SD1     |

| 88  | -           | 43  | GND     | 41  | MA1    | 52  | MLF       | 142 | SD2     |

| 90  |             | 66  | GND     | 42  | MA2    | 86  | MRD#      | 141 | SD3     |

| 91  |             | 89  | GND     | 44  | MA3    | 7   | MVDD      | 140 | SD4     |

| 93  |             | 101 | GND     | 45  | MA4    | 21  | MVDD      | 139 | SD5     |

| 99  |             | 118 | GND     | 46  | MA5    | 39  | MVDD      | 138 | SD6     |

| 104 | <del></del> | 131 | GND     | 47  | MA6    | 202 | MVDD      | 137 | SD7     |

| 105 |             | 150 | GND     | 48  | MA7    | 87  | MWR#      | 130 | SD8     |

| 106 |             | 156 | GND     | 49  | MA8    | 201 | OE#/RAS1# | 129 | SD9     |

| 108 | _           | 165 | GND     | 50  | MA9    | 167 | PANBIAS   | 128 | SD10    |

| 109 | -           | 180 | GND     | 96  | MCS16# | 168 | PANLGT    | 127 | SD11    |

| 110 | -           | 194 | GND     | 37  | MD0    | 166 | PWDPAN    | 126 | SD12    |

| 111 | -           | 206 | GND     | 36  | MD1    | 170 | PWRCLK    | 125 | SD13    |

| 112 | <b>-</b>    | 162 | HSYNC   | 35  | MD2    | 169 | PVDD      | 124 | SD14    |

| 113 |             | 80  | HVDD    | 34  | MD3    | 185 | PVDD      | 123 | SD15    |

| 114 | -           | 107 | HVDD    | 33  | MD4    | 159 | R         | 132 | SDBUS16 |

| 115 | -           | 122 | HVDD    | 32  | MD5    | 27  | RAMCNF    | 171 | STANDBY |

| 116 | -           | 145 | HVDD    | 31  | MD6    | 26  | RAS0#     | 173 | SUSPEND |

| 117 |             | 149 | HVDDSEL | 30  | MD7    | 147 | RESET     | 192 | TFTD16  |

| 119 | -           | 164 | INOSC   | 24  | MD8    | 148 | RFRSH#    | 193 | TFTD17  |

| 120 |             | 98  | IOCHRDY | 23  | MD9    | 153 | RVDD      | 183 | UD0     |

| 121 |             | 97  | IOCS16# | 22  | MD10   | 95  | S46E8     | 184 | UD1     |

| 172 | ACTIVITY    | 84  | IOR#    | 20  | MD11   | 79  | SA0       | 186 | UD2     |

| 146 | AEN         | 85  | IOW#    | 19  | MD12   | 78  | SA1       | 187 | UD3     |

| 51  | AGNDM       | 100 | IRQ     | 18  | MD13   | 77  | SA2       | 188 | UD4     |

| 136 | AGNDV       | 61  | LA17    | 17  | MD14   | 76  | SA3       | 189 | UD5     |

| 92  | ATBUS#      | 60  | LA18    | 16  | MD15   | 75  | SA4       | 190 | UD6     |

| 53  | AVDDM       | 59  | LA19    | 13  | MD16   | 74  | SA5       | 191 | UD7     |

| 134 | AVDDV       | 58  | LA20    | 12  | MD17   | 73  | SA6       | 163 | VAA     |

| 157 | 8           | 57  | LA21    | 11  | MD18   | 72  | SA7       | 160 | VGNDA   |

| 83  | BALE        | 56  | LA22    | 10  | MD19   | 71  | SA8       | 135 | VLF     |

| 28  | CAS#        | 55  | LA23    | 9   | MD20   | 70  | SA9       | 133 | VPLF    |

| 54  | CVDD        | 174 | LD0     | 8   | MD21   | 69  | SA10      | 154 | VREF    |

| 94  | CVDD        | 175 | LD1     | 6   | MD22   | 68  | SA11      | 161 | VSYNC   |

| 152 | CVDD        | 176 | LD2     | 5   | MD23   | 67  | SA12      | 38  | WE0#    |

| 200 | CVDD        | 177 | LD3     | 3   | MD24   | 65  | SA13      | 25  | WE1#    |

| 199 | DTMG        | 178 | LD4     | 2   | MD25   | 64  | SA14      | 14  | WE2#    |

| 103 | EROM#       | 179 | LD5     | 1   | MD26   | 63  | SA15      | 4   | WE3#    |

| 155 | FADJ        | 181 | LD6     | 208 | MD27   | 62  | SA16      | 151 | XCLK    |

| 198 | FLM         | 182 | LD7     | 207 | MD28   | 82  | SBHE#     | 102 | ZWS#    |

| 158 | G           | 197 | LP      | 205 | MD29   | 195 | SCK       |     |         |

| 15  | GND         | 196 | М       | 204 | MD30   | 144 | SD0       |     |         |

Page 12

📟 9004196 0000058 268 📟

## 3.2.2 Numerical Pin List-ISA Bus

| Pin | Name   | Pin | Name  | Pin | Name    | Pin | Name    | Pin | Name      |

|-----|--------|-----|-------|-----|---------|-----|---------|-----|-----------|

| 1   | MD26   | 43  | GND   | 85  | IOW#    | 127 | SD11    | 169 | PVDD      |

| 2   | MD25   | 44  | MA3   | 86  | MRD#    | 128 | SD10    | 170 | PWRCLK    |

| 3   | MD24   | 45  | MA4   | 87  | MWR#    | 129 | SD9     | 171 | STANDBY   |

| 4   | WE3#   | 46  | MA5   | 88  | -       | 130 | SD8     | 172 | ACTIVITY  |

| 5   | MD23   | 47  | MA6   | 89  | GND     | 131 | GND     | 173 | SUSPEND   |

| 6   | MD22   | 48  | MA7   | 90  | -       | 132 | SDBUS16 | 174 | LD0       |

| 7   | MVDD   | 49  | MA8   | 91  | -       | 133 | VPLF    | 175 | LD1       |

| 8   | MD21   | 50  | MA9   | 92  | ATBUS#  | 134 | AVDDV   | 176 | LD2       |

| 9   | MD20   | 51  | AGNDM | 93  | -       | 135 | VLF     | 177 | LD3       |

| 10  | MD19   | 52  | MLF   | 94  | CVDD    | 136 | AGNDV   | 178 | LD4       |

| 11  | MD18   | 53  | AVDDM | 95  | S46E8   | 137 | SD7     | 179 | LD5       |

| 12  | MD17   | 54  | CVDD  | 96  | MCS16#  | 138 | SD6     | 180 | GND       |

| 13  | MD16   | 55  | LA23  | 97  | IOCS16# | 139 | SD5     | 181 | LD6       |

| 14  | WE2#   | 56  | LA22  | 98  | IOCHRDY | 140 | SD4     | 182 | LD7       |

| 15  | GND    | 57  | LA21  | 99  | -       | 141 | SD3     | 183 | UDO       |

| 16  | MD15   | 58  | LA20  | 100 | IRQ     | 142 | SD2     | 184 | UD1       |

| 17  | MD14   | 59  | LA19  | 101 | GND     | 143 | SD1     | 185 | PVDD      |

| 18  | MD13   | 60  | LA18  | 102 | ZWS#    | 144 | \$D0    | 186 | UD2       |

| 19  | MD12   | 61  | LA17  | 103 | EROM#   | 145 | HVDD    | 187 | UD3       |

| 20  | MD11   | 62  | SA16  | 104 | -       | 146 | AEN     | 188 | UD4       |

| 21  | MVDD   | 63  | SA15  | 105 | -       | 147 | RESET   | 189 | UD5       |

| 22  | MD10   | 64  | SA14  | 106 | _       | 148 | RFRSH#  | 190 | UD6       |

| 23  | MD9    | 65  | SA13  | 107 | HVDD    | 149 | HVDDSEL | 191 | UD7       |

| 24  | MD8    | 66  | GND   | 108 | -       | 150 | GND     | 192 | TFTD16    |

| 25  | WE1#   | 67  | SA12  | 109 | -       | 151 | XCLK    | 193 | TFTD17    |

| 26  | RAS0#  | 68  | SA11  | 110 | -       | 152 | CVDD    | 194 | GND       |

| 27  | RAMONF | 69  | SA10  | 111 | -       | 153 | RVDD    | 195 | SCK       |

| 28  | CAS#   | 70  | SA9   | 112 |         | 154 | VREF    | 196 | М         |

| 29  | GND    | 71  | SA8   | 113 | -       | 155 | FADJ    | 197 | LP        |

| 30  | MD7    | 72  | SA7   | 114 | -       | 156 | GND     | 198 | FLM       |

| 31  | MD6    | 73  | SA6   | 115 |         | 157 | 8       | 199 | DTMG      |

| 32  | MD5    | 74  | SA5   | 116 | -       | 158 | G       | 200 | CVDD      |

| 33  | MD4    | 75  | SA4   | 117 | -       | 159 | R       | 201 | OE#/RAS1# |

| 34  | MD3    | 76  | SA3   | 118 | GND     | 160 | VGNDA   | 202 | DOVM      |

| 35  | MD2    | 77  | SA2   | 119 | -       | 161 | VSYNC   | 203 | MD31      |

| 36  | MD1    | 78  | SA1   | 120 | -       | 162 | HSYNC   | 204 | MD30      |

| 37  | MD0    | 79  | SA0   | 121 | _       | 163 | VAA     | 205 | MD29      |

| 38  | WEO#   | 80  | HVDD  | 122 | HVDD    | 164 | INOSC   | 206 | GND       |

| 39  | MVDD   | 81  | -     | 123 | SD15    | 165 | GND     | 207 | MD28      |

| 40  | MAO    | 82  | SBHE# | 124 | SD14    | 166 | PWDPAN  | 208 | MD27      |

| 41  | MA1    | 83  | BALE  | 125 | SD13    | 167 | PANBIAS |     |           |

| 42  | MA2    | 84  | IOR#  | 126 | SD12    | 168 | PANLGT  | 1   |           |

912-3000-027

**.** 9004196 0000059 174 **...**

# 92C178

## 3.2.3 Alphabetical Pin List-VL Bus

| Pin | Name      | Pin | Name    | Pin | Name       | Pin                                   | Name      | Pin | Name         |

|-----|-----------|-----|---------|-----|------------|---------------------------------------|-----------|-----|--------------|

| 77  | A2        | 152 | CVDD    | 43  | GND        | 49                                    | MA8       | 168 | PANLGT       |

| 76  | A3        | 200 | CVDD    | 66  | GND        | 50                                    | MA9/P7    | 166 | PWDPAN       |

| 75  | A4        | 144 | D0      | 89  | GND        | 37                                    | MD0       | 170 | PWRCLK       |

| 74  | A5        | 143 | D1      | 101 | GND        | 36                                    | MD1       | 169 | PVDD         |

| 73  | A6        | 142 | D2      | 118 | GND        | 35                                    | MD2       | 185 | PVDD         |

| 72  | A7        | 141 | D3      | 131 | GND        | 34                                    | MD3       | 159 | R            |

| 71  | A8        | 140 | D4      | 150 | GND        | 33                                    | MD4       | 27  | RAMCNF/      |

| 70  | A9        | 139 | D5      | 156 | GND        | 32                                    | MD5       |     | CKEYW        |

| 69  | A10       | 138 | D6      | 165 | GND        | 31                                    | MD6       | 26  | RAS0#        |

| 68  | A11       | 137 | D7      | 180 | GND        | 30                                    | MD7       | 98  | RDY#         |

| 67  | A12       | 130 | D8      | 194 | GND        | 24                                    | MD8       | 90  | RDYRTN#      |

| 65  | A13       | 129 | D9      | 206 | GND        | 23                                    | MD9       | 147 | RESET#       |

| 64  | A14       | 128 | D10     | 162 | HSYNC      | 22                                    | MD10      | 153 | RVDD         |

| 63  | A15       | 127 | D11     | 80  | HVDD       | 20                                    | MD11      | 95  | S46E8/P4     |

| 62  | A16       | 126 | D12     | 107 | HVDD       | 19                                    | MD12      | 195 | SCK          |

| 61  | A17       | 125 | D13     | 122 | HVDD       | 18                                    | MD13      | 132 | SDBUS16/ECLK |

| 60  | A18       | 124 | D14     | 145 | HVDD       | 17                                    | MD14      | 171 | STANDBY      |

| 59  | A19       | 123 | D15     | 149 | HVDDSEL/   | 16                                    | MD15      | 173 | SUSPEND      |

| 58  | A20       | 121 | D16     |     | BLANK#     | 13                                    | MD16      | 192 | TFTD16       |

| 57  | A21       | 120 | D17     | 148 | ID0/ESYNC  | 12                                    | MD17      | 193 | TFTD17       |

| 56  | A22       | 119 | D18     | 85  | ID1/P0     | 11                                    | MD18      | 183 | 000          |

| 55  | A23       | 117 | D19     | 164 | INOSC/DCLK | 10                                    | MD19      | 184 | UD1          |

| 99  | A24       | 116 | D20     | 96  | LBS16#/P5  | 9                                     | MD20      | 186 | UD2          |

| 100 | A25       | 115 | D21     | 174 | LD0        | 8                                     | MD21      | 187 | UD3          |

| 172 | ACTIVITY  | 114 | D22     | 175 | LD1        | 6                                     | MD22      | 188 | UD4          |

| 83  | ADS#      | 113 | D23     | 176 | LD2        | 5                                     | MD23      | 189 | UD5          |

| 51  | AGNDM     | 112 | D24     | 177 | LD3        | 3                                     | MD24      | 190 | UD6          |

| 136 | AGNDV     | 111 | D25     | 178 | LD4        | 2                                     | MD25      | 191 | UD7          |

| 92  | ATBUS#/P3 | 110 | D26     | 179 | LD5        | 1                                     | MD26      | 163 | VAA          |

| 53  | AVDDM     | 109 | D27     | 181 | LD6        | 208                                   | MD27      | 160 | VGNDA        |

| 134 | AVDDV     | 108 | D28     | 182 | LD7        | 207                                   | MD28      | 87  | VL#/P1       |

| 157 | В         | 106 | D29     | 97  | LDEV#      | 205                                   | MD29      | 135 | VLF          |

| 79  | 8E0#      | 105 | D30     | 197 | LP         | 204                                   | MD30      | 133 | VPLF         |

| 82  | BE1#      | 104 | D31     | 196 | М          | 203                                   | MD31      | 154 | VREF         |

| 78  | BE2#      | 88  | D/C#/P2 | 86  | M/IO#      | 52                                    | MLF       | 161 | VSYNC        |

| 81  | BE3#      | 199 | DTMG    | 40  | MAO        | 7                                     | MVDD      | 84  | W/R#         |

| 91  | BRDY#     | 103 | EROM#   | 41  | MA1        | 21                                    | MVDD      | 38  | WE0#         |

| 28  | CAS#      | 155 | FADJ    | 42  | MA2        | 39                                    | MVDD      | 25  | WE1#         |

| 93  | CPUCLK    | 198 | FLM     | 44  | MA3        | 202                                   | MVDD      | 14  | WE2#         |

| 146 | CPURST#/  | 158 | G       | 45  | MA4        | 201                                   | OE#/RAS1# | 4   | WE3#         |

| -   | EVIDEO    | 15  | GND     | 46  | MA5        | 102                                   | P6 (      | 151 | XCLK         |

| 54  | CVDD      | 29  | GND     | 47  | MA6        | 167                                   | PANBIAS   |     |              |

| 94  | CVDD      | ·   |         | 48  | MA7        | · · · · · · · · · · · · · · · · · · · |           |     |              |

Page 14

**■ 4004196 0000060 916 ■**

## 3.2.4 Numerical Pin List-VL Bus

| Pin      | Name             | Pin | Name   | Pin | Name      | Pin | Name               | Pin | Name      |

|----------|------------------|-----|--------|-----|-----------|-----|--------------------|-----|-----------|

| 1        | MD26             | 43  | GND    | 86  | M/IO#     | 129 | D9                 | 171 | STANDBY   |

| 2        | MD25             | 44  | MA3    | 87  | VL#/P1    | 130 | D8                 | 172 | ACTIVITY  |

| 3        | MD24             | 45  | MA4    | 88  | D/C#/P2   | 131 | GND                | 173 | SUSPEND   |

| 4        | WE3#             | 46  | MA5    | 89  | GND       | 132 | SDBUS16/ECLK       | 174 | LD0       |

| 5        | MD23             | 47  | MA6    | 90  | RDYRTN#   | 133 | VPLF               | 175 | LD1       |

| 6        | MD22             | 48  | MA7    | 91  | BRDY#     | 134 | AVDDV              | 176 | LD2       |

| 7        | MVDD             | 49  | BAM 8  | 92  | ATBUS#/P3 | 135 | VLF                | 177 | LD3       |

| 8        | MD21             | 50  | MA9/P7 | 93  | CPUCLK    | 136 | AGNDV              | 178 | LD4       |

| 9        | MD20             | 51  | AGNDM  | 94  | CVDD      | 137 | D7                 | 179 | LD5       |

| 10       | MD19             | 52  | MLF    | 95  | S46E8/P4  | 138 | D6                 | 180 | GND       |

| 11       | MD18             | 53  | AVDDM  | 96  | LBS16#/P5 | 139 | D5                 | 181 | LD6       |

| 12       | MD17             | 54  | CVDD   | 97  | LDEV#     | 140 | D4                 | 182 | LD7       |

| 13       | MD16             | 55  | A23    | 98  | RDY#      | 141 | D3                 | 183 | UD0       |

| 14       | WE2#             | 56  | A22    | 99  | A24       | 142 | D2                 | 184 | UD1       |

| 15       | GND              | 57  | A21    | 100 | A25       | 143 | D1                 | 185 | PVDD      |

| 16       | MD15             | 58  | A20    | 101 | GND       | 144 | D0                 | 186 | UD2       |

| 17       | MD14             | 59  | A19    | 102 | P6        | 145 | HVDD               | 187 | UD3       |

| 18       | MD13             | 60  | A18    | 103 | EROM#     | 146 | CPURST#/           | 188 | UD4       |

| 19       | MD12             | 61  | A17    | 104 | D31       | 447 | EVIDEO             | 189 | UD5       |

| 20       | MD11             | 62  | A16    | 105 | D30       | 147 | RESET#             | 190 | UD6       |

| 21       | MVDD             | 63  | A15    | 106 | D29       | 148 | IDO/ESYNC          | 191 | UD7       |

| 22       | MD10             | 64  | A14    | 107 | HVDD      | 149 | HVDDSEL/<br>BLANK# | 192 | TFTD16    |

| 23       | MD9              | 65  | A13    | 108 | D28       | 150 | GND                | 193 | TFTD17    |

| 24       | MD8              | 66  | GND    | 109 | D27       | 151 | XCLK               | 194 | GND       |

| 25       | WE1#             | 67  | A12    | 110 | D26       | 152 | CVDD               | 195 | SCK       |

| 26       | RAS0#            | 68  | A11    | 111 | D25       | 153 | RVDD               | 196 | М         |

| 27       | RAMCNF/<br>CKEYW | 69  | A10    | 112 | D24       | 154 | VREF               | 197 | LP        |

| 28       | CAS#             | 70  | A9     | 113 | D23       | 155 | FADJ               | 198 | FLM       |

| 29       | GND              | 71  | A8     | 114 | D22       | 156 | GND                | 199 | DTMG      |

| 30       | MD7              | 72  | A7     | 115 | D21       | 157 | 8                  | 200 | CVDD      |

| 31       | MD6              | 73  | A6     | 116 | D20       | 158 | G                  | 201 | OE#/RAS1# |

| 32       | MD5              | 74  | A5     | 117 | D19       | 159 | R                  | 202 | MVDD      |

| 33       | MD4              | 75  | A4     | 118 | GND       | 160 | VGNDA              | 203 | MD31      |

| 34       | MD3              | 76  | A3     | 119 | D18       | 161 | VSYNC              | 204 | MD30      |

| 35       | MD2              | 77  | A2     | 120 | D17       | 162 | HSYNC              | 205 | MD29      |

| 36       | MD1              | 78  | BE2#   | 121 | D16       | 163 | VAA                | 206 | GND       |

| 37       | MDO              | 79  | BE0#   | 122 | HVDD      | 164 | INOSC/DCLK         | 207 | MD28      |

| 38       | WE0#             | 80  | HVDD   | 123 | D15       | 165 | GND                | 208 | MD27      |

| 39       | MVDD             | 81  | BE3#   | 124 | D14       | 166 | PWDPAN             |     |           |

| 40       | MAO              | 82  | BE1#   | 125 | D13       | 167 | PANBIAS            |     |           |

| 40       | MA1              | 83  | ADS#   | 126 | D12       | 168 | PANLGT             |     |           |

| 42       | MA2              | 84  | W/R#   | 127 | D11       | 169 | PVDD               |     |           |

| <u> </u> |                  | 85  | !D1/P0 | 128 | D10       | 170 | PWRCLK             |     |           |

912-3000-027

# 92C178

## 3.2.5 Alphabetical Pin List-PCI Bus

| Pin | Name      | Pin | Name    | Pin | Name           | Pin | Name      | Pin | Name         |

|-----|-----------|-----|---------|-----|----------------|-----|-----------|-----|--------------|

| 172 | ACTIVITY  | 67  | BA3/P11 | 89  | GND            | 37  | MD0       | 167 | PANBIAS      |

| 144 | AD0       | 65  | BA4/P12 | 101 | GND            | 36  | MD1       | 168 | PANLGT       |

| 143 | AD1       | 64  | BA5/P13 | 118 | GND            | 35  | MD2       | 76  | PAR          |

| 142 | AD2       | 63  | BA6/P14 | 131 | GND            | 34  | MD3       | 166 | PWDPAN       |

| 141 | AD3       | 62  | BA7/P15 | 150 | GND            | 33  | MD4       | 170 | PWRCLK       |

| 140 | AD4       | 61  | BA8     | 156 | GND            | 32  | MD5       | 169 | PVDD         |

| 139 | AD5       | 60  | BA9     | 165 | GND            | 31  | MD6       | 185 | PVDD         |

| 138 | AD6       | 59  | BA10    | 180 | GND            | 30  | MD7       | 159 | R            |

| 137 | AD7       | 58  | BA11    | 194 | GND            | 24  | MD8       | 27  | RAMCNF/GRDY  |

| 130 | AD8       | 57  | BA12    | 206 | GND            | 23  | MD9       | 26  | RAS0#        |

| 129 | AD9       | 56  | BA13    | 162 | HSYNC          | 22  | MD10      | 147 | RESET#       |

| 128 | AD10      | 55  | BA14    | 80  | HVDD           | 20  | MD11      | 153 | RVDD         |

| 127 | AD11      | 99  | 8D0     | 107 | HVDD           | 19  | MD12      | 95  | S46E8/P4     |

| 126 | AD12      | 91  | B01     | 122 | HVDD           | 18  | MD13      | 195 | SCK          |

| 125 | AD13      | 84  | BD2     | 145 | HVDD           | 17  | MD14      | 132 | SDBUS16/ECLK |

| 124 | AD14      | 75  | BD3     | 149 | HVDDSEL/BLANK# | 16  | MD15      | 171 | STANDBY      |

| 123 | AD15      | 74  | BD4     | 148 | ID0/ESYNC      | 13  | MD16      | 77  | STOP#        |

| 121 | AD16      | 73  | BD5     | 85  | ID1/P0         | 12  | MD17      | 171 | SUSPEND      |

| 120 | AD17      | 72  | BD6     | 86  | IDSEL          | 11  | MD18      | 192 | TFTD16       |

| 119 | AD18      | 71  | 8D7     | 164 | INOSC/DCLK     | 10  | MD19      | 193 | TFTD17       |

| 117 | AD19      | 79  | C/BE0#  | 100 | INTA#          | 9   | MD20      | 98  | TRDY#        |

| 116 | AD20      | 82  | C/BE1#  | 90  | IRDY#          | 8   | MD21      | 183 | UD0          |

| 115 | AD21      | 78  | C/BE2#  | 174 | LD0            | 6   | MD22      | 184 | UD1          |

| 114 | AD22      | 81  | C/BE3#  | 175 | LD1            | 5   | MD23      | 186 | UD2          |

| 113 | AD23      | 28  | CAS#    | 176 | LD2            | 3   | MD24      | 187 | UD3          |

| 112 | AD24      | 93  | CPUCLK  | 177 | LD3            | 2   | MD25      | 188 | UD4          |

| 111 | AD25      | 54  | CVDD    | 178 | LD4            | 1   | MD26      | 189 | UD5          |

| 110 | AD26      | 94  | CVDD    | 179 | LD5            | 208 | MD27      | 190 | UD6          |

| 109 | AD27      | 152 | CVDD    | 181 | LD6            | 207 | MD28      | 191 | UD7          |

| 108 | AD28      | 200 | CVDD    | 182 | LD7            | 205 | MD29      | 163 | VAA          |

| 106 | AD29      | 97  | DEVSEL# | 197 | LP             | 204 | MD30      | 160 | VGNDA        |

| 105 | AD30      | 199 | DTMG    | 196 | М              | 203 | MD31      | 135 | VLF          |

| 104 | AD31      | 103 | EROM#   | 40  | MAO            | 52  | MLF       | 133 | VPLF         |

| 51  | AGNDM     | 146 | EVIDEO  | 41  | MA1            | 7   | MVDD      | 154 | VREF         |

| 136 | AGNDV     | 155 | FADJ    | 42  | MA2            | 21  | MVDD      | 161 | VSYNC        |

| 92  | ATBUS#/P3 | 198 | FLM     | 44  | МАЗ            | 39  | MVDD      | 38  | WE0#         |

| 53  | AVDDM     | 83  | FRAME#  | 45  | MA4            | 202 | MVDD      | 25  | WE1#         |

| 134 | AVDDV     | 158 | G       | 46  | MA5            | 201 | OE#/RAS1# | 14  | WE2#         |

| 157 | 8         | 15  | GND     | 47  | MA6            | 87  | P1/VL#    | 4   | WE3#         |

| 70  | BA0/P3    | 29  | GND     | 48  | MA7            | 88  | P2        | 151 | XCLK         |

| 69  | 8A1/P9    | 43  | GND     | 49  | MA8            | 96  | P5        | ]   |              |

| 68  | BA2/P10   | 66  | GND     | 50  | MA9/P2         | 102 | P6        |     |              |

Page 16

📟 9004196 0000062 799 📟

## 3.2.6 Numerical Pin List-PCI Bus

| Pin | Name        | Pin | Name    | Pin | Name      | Pin | Name           | Pin | Name      |

|-----|-------------|-----|---------|-----|-----------|-----|----------------|-----|-----------|

| 1   | MD26        | 43  | GND     | 85  | ID1/P0    | 127 | AD11           | 169 | PVDD      |

| 2   | MD25        | 44  | маз     | 86  | IDSEL     | 128 | AD10           | 170 | PWRCLK    |

| 3   | MD24        | 45  | MA4     | 87  | P1/VL#    | 129 | AD9            | 171 | STANDBY   |

| 4   | WE3#        | 46  | MA5     | 88  | P2        | 130 | AD8            | 172 | ACTIVITY  |

| 5   | MD23        | 47  | MA6     | 89  | GND       | 131 | GND            | 173 | SUSPEND   |

| 6   | MD22        | 48  | MA7     | 90  | IRDY#     | 132 | SDBUS16/ECLK   | 174 | LD0       |

| 7   | MVDD        | 49  | MA8     | 91  | 8D1       | 133 | VPLF           | 175 | LD1       |

| 8   | MD21        | 50  | MA9/P2  | 92  | ATBUS#/P3 | 134 | AVDDV          | 176 | LD2       |

| 9   | MD20        | 51  | AGNDM   | 93  | CPUCLK    | 135 | VLF            | 177 | LD3       |

| 10  | MD19        | 52  | MLF     | 94  | CVDD      | 136 | AGNDV          | 178 | LD4       |

| 11  | MD18        | 53  | AVDDM   | 95  | S46E8/P4  | 137 | AD7            | 179 | LD5       |

| 12  | MD17        | 54  | CVDD    | 96  | P5        | 138 | AD8            | 180 | GND       |

| 13  | MD16        | 55  | BA14    | 97  | LDEV#     | 139 | AD5            | 181 | LD6       |

| 14  | WE2#        | 56  | BA13    | 98  | RDY#      | 140 | AD4            | 182 | LD7       |

| 15  | GND         | 57  | BA12    | 99  | BD0       | 141 | AD3            | 183 | UDO       |

| 16  | MD15        | 58  | BA11    | 100 | IRQ       | 142 | AD2            | 184 | UD1       |

| 17  | MD14        | 59  | 8A10    | 101 | GND       | 143 | AD1            | 185 | PVDD      |

| 18  | MD13        | 60  | BA9     | 102 | P6        | 144 | AD0            | 186 | UD2       |

| 19  | MD12        | 61  | BA8     | 103 | EROM#     | 145 | HVDD           | 187 | UD3       |

| 20  | MD11        | 62  | BA7/P15 | 104 | AD31      | 146 | EVIDEO         | 188 | UD4       |

| 21  | MVDD        | 63  | BA6/P14 | 105 | AD30      | 147 | RESET#         | 189 | UD5       |

| 22  | MD10        | 64  | BA5/P13 | 106 | AD29      | 148 | ID0/ESYNC      | 190 | UD6       |

| 23  | MD9         | 65  | BA4/P12 | 107 | HVDD      | 149 | HVDDSEL/BLANK# | 191 | UD7       |

| 24  | MD8         | 66  | GND     | 108 | AD28      | 150 | GND            | 192 | TFTD16    |

| 25  | WE1#        | 67  | BA3/P11 | 109 | AD27      | 151 | XCLK           | 193 | TFTD17    |

| 26  | RASO#       | 68  | BA2/P10 | 110 | AD26      | 152 | CVDD           | 194 | GND       |

| 27  | RAMCNF/GRDY | 69  | BA1/P9  | 111 | AD25      | 153 | RVDD           | 195 | SCK       |

| 28  | CAS#        | 70  | BA0/P8  | 112 | AD24      | 154 | VREF           | 196 | М         |

| 29  | GND         | 71  | BD7     | 113 | AD23      | 155 | FADJ           | 197 | LP        |

| 30  | MD7         | 72  | BD6     | 114 | AD22      | 156 | GND            | 198 | FLM       |

| 31  | MD6         | 73  | BD5     | 115 | AD21      | 157 | В              | 199 | DTMG      |

| 32  | MD5         | 74  | BD4     | 116 | AD20      | 158 | G              | 200 | CVDD      |

| 33  | MD4         | 75  | BD3     | 117 | AD19      | 159 | R              | 201 | OE#/RAS1# |

| 34  | MD3         | 76  | PAR     | 118 | GND       | 160 | VGNDA          | 202 | MVDD      |

| 35  | MD2         | 77  | STOP#   | 119 | AD18      | 161 | VSYNC          | 203 | MD31      |

| 36  | MD1         | 78  | C/BE2#  | 120 | AD17      | 162 | HSYNC          | 204 | MD30      |

| 37  | MD0         | 79  | C/BE0#  | 121 | AD16      | 163 | VAA            | 205 | MD29      |

| 38  | WE0#        | 80  | HVDD    | 122 | HVDD      | 164 | INOSC/DCLK     | 206 | GND       |

| 39  | MVDD        | 81  | C/BE3#  | 123 | AD15      | 165 | GND            | 207 | MD28      |

| 40  | MAO         | 82  | C/BE1#  | 124 | AD14      | 166 | PWDPAN         | 208 | MD27      |

| 41  | MA1         | 83  | FRAME#  | 125 | AD13      | 167 | PANBIAS        |     |           |

| 42  | MA2         | 84  | BD2     | 126 | AD12      | 168 | PANLGT         |     |           |

912-3000-027

9004196 0000063 625 📼

# 3.3 Interface Signals

## 3.3.1 Host Interface- ISA Bus

| Pin Name   | Pin                 | Туре | Description                                                                                                                                                                                                                                                                     |

|------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AEN        | 146                 |      | Address Enable. When active, indicates DMA is occurring over the ISA bus. The 92C178 will ignore any I/O cycles while this signal is active. AEN has no effect on memory read/write commands.                                                                                   |

| ATBUS#     | 92                  | 1    | Bus configuration pin. For ISA, tie to GND through a 4.7Kohm resistor.                                                                                                                                                                                                          |

| BALE       | 83                  | ı    | Bus Address Latch Enable. Signals LA23 through LA17 are latched inside the 92C178 at the falling edge of this signal.                                                                                                                                                           |

| CPUCLK     | 93                  | 1    | CPU Clock. This pin should be tied to GND through a 4.7Kohm resistor.                                                                                                                                                                                                           |

| EROM#      | 103                 | 0    | Enable BIOS ROM. This signal is activated for memory read cycles which fall in the address range of the video BIOS. The address range is C000:0-C7FFF:F.                                                                                                                        |

| IOCHRDY    | 98                  | 0    | I/O Channel Ready. This signal is used to request additional wait states for completion a video memory access cycle. IOCHRDY is not generated for I/O access, BIOS ROM access, or for zero-wait state video memory writes.                                                      |

| IOCS16#    | 97                  | 0    | I/O Chip Select 16 for ISA bus. This signal responds to the host to enable 16-bit I/O access.                                                                                                                                                                                   |

| IOR#       | 84                  | 1    | ISA bus I/O read strobe.                                                                                                                                                                                                                                                        |

| IOW#       | 85                  | ı    | ISA bus I/O write strobe.                                                                                                                                                                                                                                                       |

| IRQ        | 100                 | 0    | Interrupt Request. Interrupt generation is enabled by bit 5 of the Vertical Sync End Register (3D5.11). Interrupt requests are generated at the vertical display end time.                                                                                                      |

| LA23- LA17 | 55-61               | ı    | Unlatched system address bus bits 23 through 17.                                                                                                                                                                                                                                |

| MCS16#     | 96                  | 0    | Memory Chip Select 16 for ISA bus. This signal responds to the host to enable 16-bit video memory read/writes. The 92C178 will also activate this signal for I/O commands.                                                                                                      |

| MRD#       | 86                  | ı    | ISA bus memory read strobe.                                                                                                                                                                                                                                                     |

| MWR#       | 87                  | I    | ISA bus memory write strobe.                                                                                                                                                                                                                                                    |

| RESET      | 147                 | ı    | Reset. This pin used initialize the 92C178 to a known state. At the falling edge of RESET, the 92C178 will latch the data on MD31-16 into Configuration Registers 2 and 1 (3C5.1E and 3C5.1F) and the hardware configuration pin values into Configuration Register 0 (3C5.1D). |

| RFRSH#     | 148                 | ļ    | Refresh. This pin indicates that DRAM refresh is occurring over the ISA bus. The 92C178 will ignore any memory read/write cycles while this signal is active. This signal has no effect on I/O commands.                                                                        |

| S46E8      | 95                  | 1    | VGA enable port select. A logical 1 selects port 46E8 as the VGA enable port. A logical 0 selects 3C3 as the VGA enable port. Signal should be tied through a 4.7Kohm resistor.                                                                                                 |

| SA16-SA0   | 62-65,<br>67-79     | 1    | System address bus bits 16 through 0.                                                                                                                                                                                                                                           |

| SBHE#      | 82                  | 1    | System 8us High Byte Enable. Enables high byte data transfer on the ISA bus.                                                                                                                                                                                                    |

| SD15:0     | 123-130.<br>137-144 | 1/0  | ISA data bus pins 15-0.                                                                                                                                                                                                                                                         |

Page 18

912-3000-027

■ 9004196 0000064 561 **■**

## 3.3.1 Host Interface- ISA Bus (cont.)

| Pin Name | Pin | Type | Description                                                                                                                                                                           |

|----------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDBUS16  | 132 | ı    | Data bus configuration pin. Configures the system data bus as 16-bit or 32-bit. For ISA bus, this pin should be tied to HVDD through a 4.7Kohm resistor.                              |

| ZWS#     | 102 | 0    | Zero Wait State signal. This signal is used to indicate the 92C178 can process a zero wait state video memory write command. ZWS# can be generated when the write buffer is not full. |

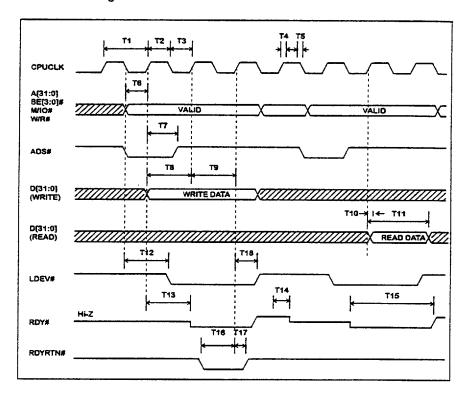

## 3.3.2 Host Interface-VESA Local Bus

| Pin Name             | Pin                         | Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|-----------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A25-A2               | 100, 99,<br>55-65,<br>67-77 | 1        | Local bus address bits 25-2.                                                                                                                                                                                                                                                                                                                                                                                                              |

| ATBUS#/P3            | 92                          | 1/0      | AT Bus Select. When the feature connector is disabled, this pin should be tied high through a 4.7Kohm resistor for local bus configurations. This pin is defined as P3 when the feature connector is enabled. When the feature connector is enabled, the value for ATBUS# is determined by MD12 at power-on.                                                                                                                              |

| ADS#                 | 83                          | ı        | Address Data Strobe. Indicates start of a local bus cycle.                                                                                                                                                                                                                                                                                                                                                                                |

| BE3#-BE0#            | 81, 78,<br>82, 79           | 1        | Byte Enables 3-0. A logical 0 indicates valid data for the given byte lane.                                                                                                                                                                                                                                                                                                                                                               |

| BRDY#                | 91                          | -        | Burst Ready. Signal used to reset the bus interface state machine after a burst cycle on the local bus. The signal is needed since not all system core logic generates RDYRTN# upon completion of a local bus burst cycle.                                                                                                                                                                                                                |

| CPUCLK               | 93                          | ı        | CPU Clock. Timing reference clock for local bus. Bus timing is synchronized to the rising edge of this clock. The clock rate should be 1X CPU clock for a 486 local bus implementation and 2X CPU clock for a 386 local bus implementation. For the 386 local bus implementation, the 92C178 divides the clock internally to drive the chip logic.                                                                                        |

| CPURST#/<br>EVIDEO   | 146                         | 1/0      | CPU Reset. This signal is used to reset the 92C178's internal CPU clock divider and to synchronize the internal state machine. The signal should be connected for non-VL Bus solutions which use a 2X input clock (VL# high, and ID1, ID0 configured for i386). This signal is not required for VL-Bus solutions. This pin is defined as EVIDEO when the feature connector is enabled.                                                    |

| D/C#/P2              | 88                          | ı        | Data/Code. Indicates whether the current cycle is transmitting data or code. This pin is defined as P2 when the feature connector is enabled.                                                                                                                                                                                                                                                                                             |

| EROM#/P7             | 103                         | 1/0      | Enable BIOS ROM. This signal is activated for memory read cycles which fall in the address range of the video BIOS. The address range is C000:0-C7FFF:F. This pin is defined as P7 when the feature connector is enabled.                                                                                                                                                                                                                 |

| ID1/P0-<br>ID0/ESYNC | 85,<br>148                  | 1/O<br>1 | ID Pins 1 and 0. These pins are used in combination with pin VL# (pin 87) and ATBUS# (pin 92) to configure bus type. Each pin should be tied through a 4.7Kohm resistor. See Table 1 in Bus Interface Unit section for additional details. These pins are described as P0 and ESYNC when the feature connector is enabled. When the feature connector is enabled, ID1 and ID0 are determined by MD11 and MD10, respectively, at power-on. |

| LBS16#/P5            | 96                          | 1/0      | Local Bus Select 16. Informs the CPU to transfer only up to 16 bits of data. The 92C178 will activate this signal for local bus I/O commands. This pin is defined as P5 when the feature connector is enabled.                                                                                                                                                                                                                            |

912-3000-027

## 3.3.2 Host Interface-VESA Local Bus (cont.)

| Pin Name         | Pin                                                     | Type | Description                                                                                                                                                                                                                                                                                                                                                                      |  |

|------------------|---------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LDEV#            | 97                                                      | 0    | Local Device. Informs the core logic that the 92C178 will respond to the current cycle.                                                                                                                                                                                                                                                                                          |  |

| M/IO#            | 86                                                      | 1    | Memory/IO. Indicates whether the current cycle is a memory or I/O transaction.                                                                                                                                                                                                                                                                                                   |  |

| RDY#             | 98                                                      | 0    | Ready. Informs the system core logic that processing for the current local bus cycle has been completed.                                                                                                                                                                                                                                                                         |  |

| RDYRTN#          | 90                                                      | ı    | Ready Return. This pin is the Ready feedback from the core logic to terminate the current local bus cycle and reset the bus interface state machine.                                                                                                                                                                                                                             |  |

| RESET#           | 147                                                     | I    | Reset. This pin used initialize the 92C178 to a known state. At the rising edge of RESET#, the 92C178 will latch the data on MD31-16 into Configuration Registers 2 and 1 (3C5.1E and 3C5.1F) and the hardware configuration pin values into configuration Register 0 (3C5.1D).                                                                                                  |  |

| S46E8/P4         | 95                                                      | 1/0  | VGA enable port select. A logical 1 selects port 46E8 as the VGA enable port. A ogical 0 selects 3C3 as the VGA enable port. When the feature connector is disabled, bull high or low through a 4.7Kohm resistor. This pin is defined as P4 when the feature connector is enabled. When the feature connector is enabled, the value for 646E8 is determined by MD14 at power-on. |  |

| SD31:0           | 104-106,<br>108-117,<br>119-121,<br>123-130,<br>137-144 | 1/0  | These pins are the system data bus that are connected directly to the local data bus. For ISA or 386SX local bus, the SD31:16 pins are not connected.                                                                                                                                                                                                                            |  |

| SDBUS16/<br>ECLK | 132                                                     | l    | Data bus configuration pin. Configures the system data bus as 16-bit or 32-bit. For ISA bus, this pin should be tied to HVDD through a 4.7Kohm resistor. This pin is defined as ECLK when the feature connector is enabled. When the feature connector is enabled, the value for SDBUS16 is determined by MD13 at power-on.                                                      |  |

| VL#/P1           | 87                                                      | 1/0  | VL-Bus Select. Selects VL-bus or general purpose local bus. A logical 0 selects VL-Bus. A logical 1 selects general purpose local bus. Pin should be tied through a 4.7Kohm resistor. This pin is defined as P1 when the feature connector is enabled. When the feature connector is enabled, the value for VL# is determined by MD9 at power-on.                                |  |

| W/R#             | 84                                                      | ı    | Write/Read. Indicates whether the current cycle is a read or write transaction.                                                                                                                                                                                                                                                                                                  |  |

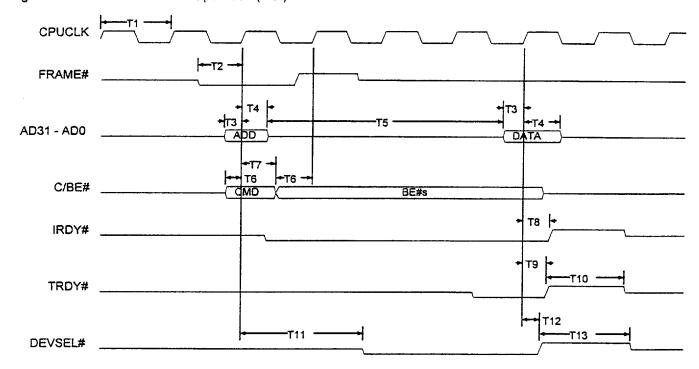

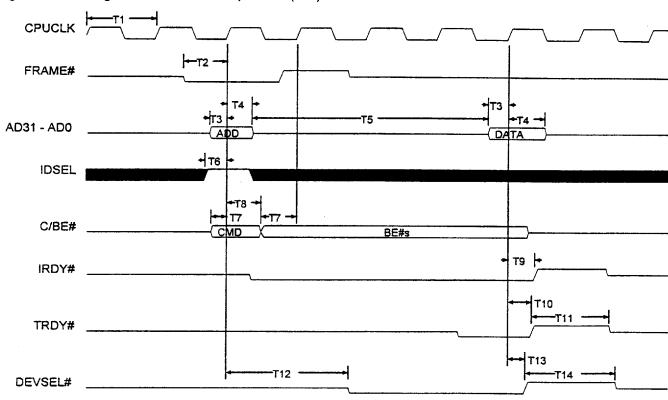

## 3.3.3 Host Interface-PCI Bus

| Pin Name   | Pin                                                     | Туре | Description                                                                                                                                                                                                                                                          |  |

|------------|---------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AD[31:0]   | 104-106,<br>108-117,<br>119-121,<br>123-130,<br>137-144 | I/O  | Multiplexed Address and Data Lines, bits 31 through 0: These pins are the multiplexed PCI address and data lines. During the address phase, these pins a inputs. During the data phase, these pins are inputs for write cycles or outputs for read cycles.           |  |

| ATBUS#/P3  | 92                                                      | 1/0  | AT Bus Select. When the feature connector is disabled, tie this pin high through a 4.7Kohm resistor. This pin is defines as P3 when the feature connector is enabled. When the feature connector is enabled, the value for ATBUS# is determined by MD12 at power-on. |  |

| C/BE[3:0]# | 81, 78, 82,<br>79                                       | I    | Bus Command and Byte Enables, bits 3 through 0: These pins are the multiplexed PCI command and byte enable lines.                                                                                                                                                    |  |

Page 20 912-3000-027

**■ 9004196 0000066 334 ■**

## 3.3.3 Host Interface-PCI Bus (cont.)

| Pin Name             | Pin                  | Type Description |                                                                                                                                                                                                                                                                                                                                                                                   |  |

|----------------------|----------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPUCLK               | 93                   | 1                | CPU Clock: Timing reference clock for PCI Bus. Connect directly to the PCI Bus Clock.                                                                                                                                                                                                                                                                                             |  |

| DEVSEL#              | 97                   | 0                | Device Select: This signal is driven low when the 92C178 decodes its address as the target of the current access.                                                                                                                                                                                                                                                                 |  |

| FRAME#               | 83                   | I                | Cycle Frame: This pin is driven by the PCI bus master to indicate the beginning and duration of an access.                                                                                                                                                                                                                                                                        |  |

| ID1/P0,<br>ID0/ESYNC | 85<br>148            | 1/0              | ID Pins 1 and 0. When the feature connector is disabled, these pins should be tied low through a 4.7Kohm resistor. These pins are defined as P0 and ESYNC when the feature connector is enabled. When the feature connector is enabled, the values for ID1 and ID0 are determined by MD10 and MD9, respectively, at power-on.,                                                    |  |

| IDSEL                | 86                   | 1                | ID Select. This signal is used as a chip select for PCI configuration space accesses.                                                                                                                                                                                                                                                                                             |  |

| INTA#                | 100                  | 0                | Interrupt Request. Interrupt generation is enabled by bit 5 of the Vertical Sync End register (3D5.11). Interrupt requests are generated at the Vertical Display Enable End time.                                                                                                                                                                                                 |  |

| IRDY#                | 90                   | I                | Initiator Ready: This signal is asserted by the PCI bus master to indicate the ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                     |  |

| PAR                  | 76                   | 1/0              | Parity: This signal is used to provide even parity across AD31-AD0 and C/BE3#-C/BE0#. This signal is sampled as an input during write cycles and provides correct parity as an output for read cycles.                                                                                                                                                                            |  |

| S46E8/P4             | 95                   | 1/0              | VGA port enable select. A logical 1 selects port 46E8 as the VGA enable port. A logical 0 selects 3C3 as the VGA enable port. When the feature connector is disabled, pull high or low through a 4.7Kohm resistor. This pin is defined as P4 when the feature connector is enabled. When the feature connector is enabled, the value for S46E8 is determined by MD14 at power-on. |  |

| SDBUS16/<br>ECLK     | 132                  | I                | Data bus configuration pin. When the feature connector is disabled, pull low through a 4.7Kohm resistor. This pin is defined as ECLK when the feature connector is enabled. When the feature connector is enabled, the value for SDBUS16 is determined by MD13 at power-on.                                                                                                       |  |

| STOP#                | 77                   | 0                | Stop: This signal is used by the target to request the master to stop the current transaction.                                                                                                                                                                                                                                                                                    |  |

| TRDY#                | 98                   | 0                | Target Ready: This pin is asserted by the 92C178 to indicate the ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                   |  |

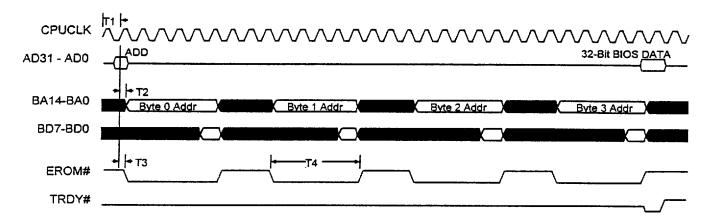

| BA14-BA0*            | 55-65,<br>67-70      | 0                | BIOS Address bits 14-0. BA7-BA0 function as P15-P8 when the 16-bit feature connector is enabled.                                                                                                                                                                                                                                                                                  |  |

| BD7-8D0*             | 71-75,<br>84, 91, 99 | ł                | BIOS Data bits 7-0.                                                                                                                                                                                                                                                                                                                                                               |  |

| EROM#                | 103                  | 0                | Enable BIOS ROM. This signal is activated for memory read cycles which fall in the address range of the video BIOS (C000:0-C7FF:F).                                                                                                                                                                                                                                               |  |

<sup>\*</sup> To enable BA14-BA0 and BD7-BD0 pin definitions, pull MD30 to logical 0 at power-on. Pull MD30 low through a  $4.7 k\Omega$  resistor.

# 92C178

## 3.3.4 Memory Interface

| Pin Name         | Pin                                                                   | Type | Description                                                                                                                                                                                                                                                                                                                                   |  |

|------------------|-----------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CAS#             | 28                                                                    | 0    | DRAM column address strobe. When signal RAMCNF is pulled low, this pin functions as WE# for display memory (for 256Kx16 dual CAS DRAM).                                                                                                                                                                                                       |  |