# 93L425A 1024 x 1-Bit Static Random Access Memory

### **General Description**

The 93L425A is a 1024-bit read write Random Access Memory (RAM), organized 1024 words by one bit. It is designed for high speed cache control and buffer storage applications. The device includes full on-chip decoding, separate Data input and non-inverting Data output, as well as an active LOW Chip Select line.

#### **Features**

- New design to replace old 93425/93L425

- Improved ESD thresholds

- Alpha hard without die coat

- Commercial address access time 93L425A

25 ns max

- Features TRI-STATE® output

- Power dissipation decreases with increasing temperature

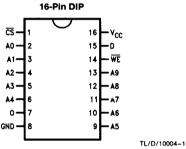

## **Connection Diagram**

Top View

Order Number 93L425ADC or 93L425APC See NS Package Number J16A\* or N16E\*

Optional Processing QR = Burn-In \*For most current package information, contact product marketing.

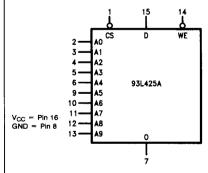

## **Logic Symbol**

#### Pin Names

| Chip Select (Active LOW)        |

|---------------------------------|

| Address Inputs                  |

| Write Enable Input (Active LOW) |

| Data Input                      |

| Data Output                     |

|                                 |

TL/D/10004-3

#### Absolute Maximum Ratings

Above which the useful life may be impaired

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Storage Temperature -65°C to +150°C Supply Voltage Range -0.5V to +7.0V

Input Voltage (DC) (Note 1) -0.5V to  $V_{CC}$ Input Current (DC) -12 mA to +5.0 mA

Voltage Applied to Outputs

-0.5V to 5.5V (Note 2)

Lead Temperature (Soldering, 10 sec.) 300°C Maximum Junction Temperature (T<sub>.</sub>) + 175°C **Output Current** + 20 mA

### **Guaranteed Operating Ranges**

Commercial

Supply Voltage (V<sub>CC</sub>) Commercial 5.0V ±5% Case Temperature (T<sub>C</sub>)

0°C to +75°C

## DC Characteristics over operating temperature ranges (Note 3)

| Symbol           | Parameter                                       | Conditions                                                     | Min | Тур  | Max  | Units |

|------------------|-------------------------------------------------|----------------------------------------------------------------|-----|------|------|-------|

| V <sub>OH</sub>  | Output HIGH Voltage                             | $V_{CC} = Min, I_{OH} = -5.2 \text{ mA}$                       | 2.4 |      |      | V     |

| VOL              | Output LOW Voltage                              | V <sub>CC</sub> = Min, I <sub>OL</sub> = 16 mA                 |     |      | 0.45 | V     |

| V <sub>IH</sub>  | Input HIGH Voltage                              | Guaranteed Input HIGH Voltage for All Inputs (Notes 4, 5, & 6) | 2.1 |      |      | V     |

| VIL              | Input LOW Voltage                               | Guaranteed Input LOW Voltage for All Inputs (Notes 4, 5, & 6)  |     |      | 0.8  | ٧     |

| I <sub>IL</sub>  | Input LOW Current                               | V <sub>CC</sub> = Max, V <sub>IN</sub> = 0.4V                  | -   | -180 | -300 | μА    |

| h <sub>H</sub>   | Input HIGH Current                              | $V_{CC} = Max, V_{IN} = 4.5V$                                  |     | 1.0  | 40   | μА    |

| I <sub>IHB</sub> | Input Breakdown Current                         | V <sub>CC</sub> = Max, V <sub>IN</sub> = V <sub>CC</sub>       |     |      | 1.0  | ∠mA   |

| V <sub>IC</sub>  | Input Diode Clamp Voltage                       | $V_{CC} = Max, I_{IN} = -10 \text{ mA}$                        |     | -1.0 | -1.5 | V     |

| lozh             | Output Current (HIGH Z)                         | V <sub>CC</sub> = Max, V <sub>OUT</sub> = 2.4V                 |     |      | 50   | μА    |

| lozL             |                                                 | V <sub>CC</sub> = Max, V <sub>OUT</sub> = 0.5V                 |     |      | -50  | μА    |

| los              | Output Current Short Circuit to Ground (Note 7) | V <sub>CC</sub> = Max (Note 7)                                 |     | -100 | mA   |       |

| Icc              | Power Supply Current                            | V <sub>CC</sub> = Max, All Inputs = GND,<br>Output Open        |     |      | 65   | mA    |

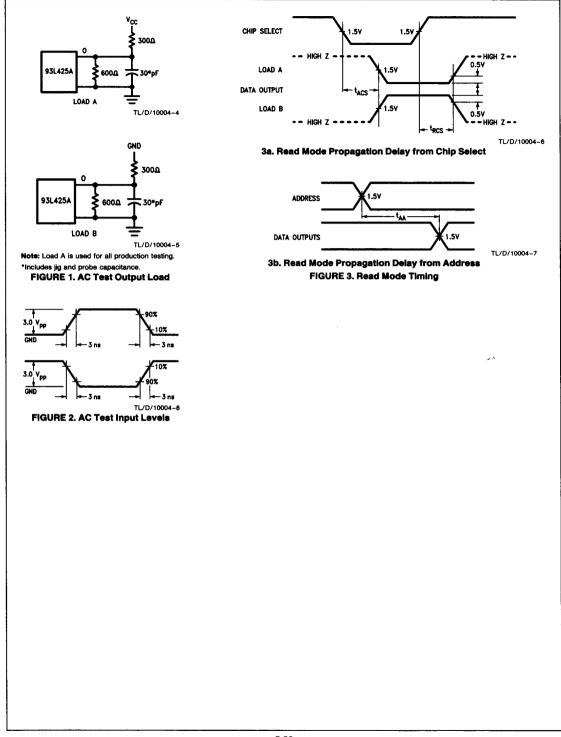

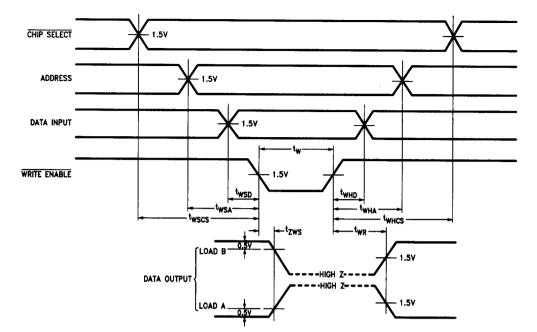

#### AC Electrical Characteristics (Note 6) $V_{CC} = 5.0 \pm 5\%$ , GND = 0V, $T_{C} = 0^{\circ}C$ to $+ 75^{\circ}C$ **Symbol Parameter** Conditions Max Units **READ TIMING** tACS Chip Select Access Time 15 ns Figures Chip Select to HIGH Z tzRCS 15 3a, 3b ns tAA Address Access Time (Note 8) 25 ns WRITE TIMING Write Pulse Width to Guarantee tw 20 ns Writing (Note 9) twsp Data Setup Time Prior to Write 5 ns Data Hold Time after Write twhD 5 ns Address Setup Time Prior twsa Figure 4 5 ns to Write (Note 9) Address Hold Time after Write 5 twha ns Chip Select Setup Time Prior to Write twscs 5 ns Chip Select Hold Time after Write **twncs** ns Write Enable to Output Disable tzws 15 ns 15 Write Recovery Time twR ns

Note 1: Either input voltage limit or input current limit is sufficient to protect the inputs.

Note 3: Typical values are at V<sub>CC</sub> = 5.0V, T<sub>C</sub> = +25°C and maximum loading.

Note 4: Static condition only.

Note 5: Functional testing done at input levels  $V_{iH} = 0.45V$  ( $V_{OL}$  Max) and  $V_{iH} = 2.4V$  ( $V_{OH}$  Min).

Note 6: AC testing done at input levels  $V_{IH} = 3V$ ,  $V_{IL} = 0V$ .

Note 7: Short circuit to ground not to exceed one second.

Note 8: The maximum address access time is guaranteed to be the worst case bit in the memory using a pseudorandom testing pattern.

Note 9:  $t_W$  measured at  $t_{WSA}$  = Min.  $t_{WSA}$  measured at  $t_W = Min$ .

Note 2: Output current limit required.

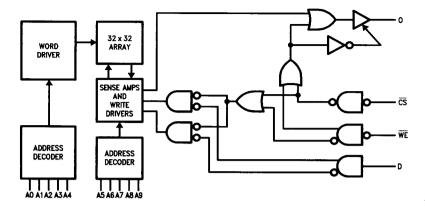

### **Logic Diagram**

TL/D/10004-2

#### **Functional Description**

The 93L425A is a fully decoded 1024-bit read write Random Access Memory organized 1024 words by one bit. Bit selection is achieved by means of a 10-bit address A0-A9.

One Chip Select (CS) input is provided for easy memory array expansion of up to 2048 bits without the need for external decoding. For larger memories the fast chip select access time permits direct address decoding without an increase in overall memory access time.

The read and write functions of the 93L425A are controlled by the state of the active LOW Write Enable  $\overline{WE}$  input. When  $\overline{WE}$  is held LOW and the chip is selected, the data at D is written into the location specified by the binary address present at A0 through A9. Since the write function is level triggered, data must be held stable at the data input for at least twsD(min) plus tw(min) plus twHD(min) to insure a valid write. When  $\overline{WE}$  is held HIGH and the chip selected, data is read from the addressed location and presented at the output O.

The 93L425A has a three-state output which provides an active pull-up or pull-down when enabled and a high impedance (HIGH Z) state when disabled. The active pull-up provides drive capability for high capacitive loads while the high impedance state allows optimization of word expansion in bus organized systems.

#### **Truth Table**

| Inputs |    |   | Outputs          | Mode         |

|--------|----|---|------------------|--------------|

| CS     | WE | D | 0                |              |

| Ι      | Н  | Х | HIGH Z           | Not Selected |

| L      | L  | L | HIGH Z           | Write 0      |

| L      | L  | Н | HIGH Z           | Write 1      |

| L      | Н  | X | D <sub>OUT</sub> | Read         |

H = HIGH Voltage Level: 2.4V

L = LOW Voltage Level: 0.45V X = Don't Care HIGH or LOW

HIGH Z = High-Impedance

TL/D/10004-9

Note 1: Timing Diagram represents one solution which results in an optimum cycle time Timing may be changed to fit various applications as long as the worst case limits are not violated.

Note 2: input voltage levels for worst case AC test are 3.0V-0V.

FIGURE 4. Write Mode Timing