# 93Z665/93Z667 8192 x 8-Bit Programmable Read Only Memory

#### **General Description**

The 93Z665/93Z667 are fully decoded 65,536-bit Programmable Read Only Memories (PROMs) organized 8192 words by eight bits per word. The 93Z665 and 93Z667 are manufactured using highly reliable ISO-Z vertical fuse technology.

- Commercial address access time

35 ns, 40 ns and 45 ns max

- Military address access time — 45 ns, 50 ns and 55 ns max

- Highly reliable vertical fuses ensure high programming yields

- Power-up TRI-STATE® outputs

- Low current PNP inputs

- Complete AC/DC testability

#### **Features**

- 93Z667 available in 300-mil side-braze DIP

- 93Z665 available in 600-mil side-braze DIP, leadless chip carrier, and Flatpak

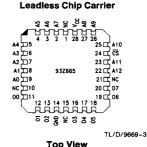

#### **Connection Diagrams**

See NS Package Number D24H\*

#### Flatpak 23 22 21 20 - cs A<sub>3</sub> 19 A2 93Z665/ 18 -A<sub>12</sub> 07 00 01 02 ٠٥, ٠0,

GND 12 13 03 TL/D/9669-10

Order Number 93Z665L See NS Package Number V28A\*

Order Number 93Z665F See NS Package Number W24C\*

\*For most current package information, contact product marketing

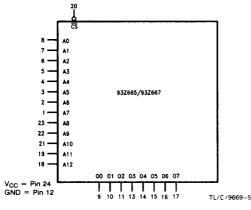

# Logic Symbol

| A0-A12 | Address Inputs                 |

|--------|--------------------------------|

| CS     | Chip Select Input (Active LOW) |

| 00-07  | Data Outputs                   |

|        |                                |

Pin Names

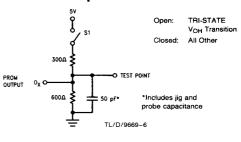

# **AC Test Output Load**

4-99

# Absolute Maximum Ratings Above which the useful life may be impaired

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/Distributors for availability and specifications.

-65°C to +150°C Storage Temperature -0.5V to +7.0VSupply Voltage Range -1.5V to V<sub>CC</sub> Input Voltage (DC) (Notes 1 & 2) Voltage Applied to Outputs -1.5V to +5.5V(Output HIGH) (Notes 2 & 3) Lead Temp. (Soldering, 10 seconds) 300°C + 175°C Maximum Junction Temperature (T<sub>J</sub>) Output Current per Output - 100 mA for VOH and (10 seconds Max) + 100 mA for  $V_{OL}$ + 20 mA (Max) Output Current High Impedance

Input Current (DC)

Note 1: Either Input Voltage limit or Input Current limit is sufficient to protect the inputs.

Note 2: These values may be exceeded as required during PROM programming.

Note 3: Output Current limit required.

### **Operating Conditions**

Ambient Operating Temperature Commercial  $0^{\circ}\text{C to } + 70^{\circ}\text{C}$ Military  $-55^{\circ}\text{C to } + 125^{\circ}\text{C}$

Positive Supply Voltage

Commercial

5.0V ±5%

Military

5.0V ± 10%

Maximum Low-Level Input Voltage (VIL)

Minimum High-Level Input Voltage (V<sub>IH</sub>) 2.0V

V8.0

#### DC Performance Characteristics: over guaranteed operating ranges unless otherwise noted

-18 mA to +5.0 mA

| Symbol           | Parameter                                          | Conditions                                                             | Min | Typ<br>(Note 1)  | Max      | Units    |

|------------------|----------------------------------------------------|------------------------------------------------------------------------|-----|------------------|----------|----------|

| V <sub>IL</sub>  | Input LOW Voltage                                  | Guaranteed Input LOW Voltage for All Inputs                            |     |                  | 0.8      | ٧        |

| V <sub>IH</sub>  | Input HIGH Voltage                                 | Guaranteed Input HIGH Voltage for All Inputs                           | 2.0 |                  |          | V        |

| V <sub>IC</sub>  | Input Clamp Diode Voltage                          | $V_{CC} = Min, I_{IN} = -18 \text{ mA}$                                |     |                  | -1.2     | V        |

| V <sub>OL</sub>  | Output LOW Voltage                                 | V <sub>CC</sub> = Min, I <sub>OL</sub> = 16 mA                         |     | 0.30             | 0.45     | V        |

| V <sub>OH</sub>  | Output HIGH Voltage                                | V <sub>CC</sub> = Min, I <sub>OH</sub> = −2.0 mA<br>Address Any "1"    | 2.4 |                  |          | ٧        |

| ار               | Input LOW Current                                  | V <sub>CC</sub> = Max, V <sub>IL</sub> = 0.45V                         |     | -10              | -100     | μΑ       |

| I <sub>Н</sub>   | Input HIGH Current                                 | V <sub>CC</sub> = Max, V <sub>IH</sub> = 2.4V to V <sub>CC</sub>       | -40 |                  | 40       | μΑ       |

| I <sub>OHZ</sub> | Output Leakage Current for<br>HIGH Impedance State | V <sub>OH</sub> = 2.4V<br>V <sub>OL</sub> = 0.4V                       |     |                  | 40<br>40 | μA<br>μA |

| los              | Output Short-Circuit<br>Current                    | V <sub>CC</sub> = Max, V <sub>O</sub> = 0V (Note 2)<br>Address Any "1" | -15 | -80              | -100     | mA       |

| lcc              | Power Supply Current                               | V <sub>CC</sub> = Max, Ali Inputs GND,<br>All Outputs Open             |     |                  | 180      | mA       |

| C <sub>IN</sub>  | Input Pin Capacitance                              | $V_{CC} = 5.0V, V_{IN} = 4.0V,$<br>f = 1.0 MHz                         |     | 7.0<br>(Note 3)  | 15.0     | pF       |

| Co               | Output Pin Capacitance                             | $V_{CC} = 5.0V, V_{O} = 4.0V,$<br>f = 1.0 MHz                          |     | 10.0<br>(Note 3) | 15.0     | pF       |

# **AC Performance Characteristics**

| Symbol          | Parameter                                                | Conditions                    | -35 | -40 | -45  | Units        |

|-----------------|----------------------------------------------------------|-------------------------------|-----|-----|------|--------------|

| COMMERCIA       | <b>L</b> $V_{CC} = 5.0V \pm 5\%$ , GND = 0V, $T_{C} = 0$ | °C to + 75°C                  |     | ,   | ···· | <del>,</del> |

| t <sub>AA</sub> | Address to Output Access Time                            | See AC Output Load and Note 5 | 35  | 40  | 45   | ns           |

| tACS            | Chip Select to Output Access Time                        | See AC Output Load and Note 5 | 20  | 20  | 30   | ns           |

| tHZ             | Chip Deselect to Output TRI-STATE                        | See AC Output Load and Note 4 | 20  | 20  | 30   | ns           |

## **AC Performance Characteristics (Continued)**

| Symbol          | Parameter                                                                            | Conditions                    | -40 | -45 | -50 | Units |

|-----------------|--------------------------------------------------------------------------------------|-------------------------------|-----|-----|-----|-------|

| MILITARY VC     | $_{\rm CC} = 5.0 \text{V} \pm 10\%, \text{GND} = 0 \text{V}, \text{T}_{\rm C} = -55$ | °C to + 125°C                 |     |     |     |       |

| t <sub>AA</sub> | Address to Output Access Time                                                        | See AC Output Load and Note 5 | 45  | 50  | 55  | ns    |

| tACS            | Chip Select to Output Access Time                                                    | See AC Output Load and Note 5 | 25  | 25  | 30  | ns    |

| t <sub>HZ</sub> | Chip Deselect to Output TRI-STATE                                                    | See AC Output Load and Note 4 | 25  | 25  | 30  | ns    |

Note 1: Typical values are at V<sub>CC</sub> = 5.0V, +25°C and maximum loading.

Note 2: Not more than one output to be shorted at a time. Duration of the short circuit should not exceed one second.

Note 3: This parameter value is based on initial design qualification and is also verified on every design change. These are not tested in production.

Note 4: t<sub>HZ</sub> is tested with load shown in Figure 2. Transition to High-Z is measured at steady state high V<sub>OH</sub> level -500 mV or steady state low V<sub>OL</sub> level +500 mV on the outputs from the point at which chip select crosses the 1.5V level towards its V<sub>IH</sub> level.

Note 5: AC Address Access and Chip Select Access is done under the following test conditions. Input pulse levels are from 0V to 3V and input/output timing reference levels at 1.5V.

#### Current-Pulse Programming Specifications (Note 4)

| Symbol                | Parameter                            | Conditions                                                 | Min      | Тур  | Max  | Units |

|-----------------------|--------------------------------------|------------------------------------------------------------|----------|------|------|-------|

| POWER SUPI            | PLY                                  |                                                            |          |      |      |       |

| V <sub>CC</sub>       | Power Supply Voltage                 | Typical I <sub>CC</sub> at 6.5V = 250 mA                   | 6.4      | 6.5  | 6.6  | ٧     |

| t <sub>r</sub> vcc    | Power Supply Rise Time (Note 3)      |                                                            | 0.2      | 2.0  |      | μs    |

| t <sub>f VCC</sub>    | Power Supply Fall Time               |                                                            | 0.2      | 2.0  |      | μs    |

| ton                   | V <sub>CC</sub> ON Time              | See Programming                                            | (Note 1) |      |      |       |

| toff                  | V <sub>CC</sub> OFF Time             | Timing Diagram                                             | (Note 2) |      |      | ·     |

|                       | Duty Cycle for V <sub>CC</sub>       | ton/(toff + ton)                                           |          |      | 50   | %     |

| READ STROE            | BE (Note 5)                          |                                                            |          |      |      |       |

| tw                    | Fuse Read Time                       | Machine Cycle                                              |          | 1.0  |      | μs    |

| t <sub>dRAP</sub>     | Delay to Read after Programming      | Verify                                                     |          | 3.0  |      | μs    |

| t <sub>CS</sub>       | Chip Enable                          |                                                            | 0.1      | 1.0  |      | μs    |

| OUTPUT DES            | ELECT                                |                                                            |          |      |      |       |

| Vos                   | Output Deselect Voltage              |                                                            | 11.8     | 12   | 12.5 | ٧     |

| los                   | Output Deselect Current Limit        |                                                            | 20       | 50   | 100  | mA    |

| O <sub>VS</sub>       | Output Voltage Select                | TTL H or L                                                 |          | 5.0  | 5.5  | ٧     |

| t <sub>rod</sub>      | Output Deselect Rise Time            |                                                            | 1.0      | 1.0  | 2.0  | μs    |

| t <sub>fod</sub>      | Output Deselect Fall Time            |                                                            | 0.1      | 0.1  | 1.0  | μs    |

| tcspp                 | Deselect Chip to Deselect Output     |                                                            | 0.1      | 1.0  |      | μs    |

| PROGRAMMI             | NG CURRENT-PULSE TRAIN ON CHIP S     | ELECT                                                      |          |      |      |       |

| I <sub>CSp(Min)</sub> | Initial Current Pulse                |                                                            |          | 40   | 60   | mA    |

| <sup>I</sup> CSp(Max) | CS Programming Current Limit         | Apply Current Pulse to<br>Chip Select Pin 20               | 155      | 160  | 165  | mA    |

| V <sub>CSp(Max)</sub> | CS Programming Voltage Limit         |                                                            | 24       | 25   | 26   | >     |

| t <sub>rcsp</sub>     | Programming Pulse Rise Time          |                                                            | 160      | 100  | 100  | mA/μs |

| t <sub>dBP</sub>      | Delay to Initial Programming Pulse   |                                                            | 2.0      | 3.0  |      | μ\$   |

| t <sub>dAP</sub>      | Delay after Programming Pulse        |                                                            | 1.0      | 1.0  |      | μs    |

| tpw                   | Programming Pulse Widths             |                                                            | 6.0      | 7.0  | 9.0  | μs    |

| t <sub>fCSp</sub>     | Programming Pulse Fall Time (Note 3) |                                                            | 0.1      | 0.1  | 0.2  | μs    |

| ΔI <sub>CSp</sub>     | Current Pulse Step Increase          |                                                            | 5.0      | 10.0 | 10.0 | mA    |

|                       | Duty Cycle for Programming<br>Pulses | Each Successive Pulse is<br>Increased by ΔI <sub>CSp</sub> | 10       | 50   | 50   | %     |

Note 1: Total time V<sub>CC</sub> is on to program fuse is equal to or greater than the sum of all the specified delays, pulse widths and rise/fall times.

Note 2: toFF is equal to or greater than toN.

Note 3: Rise and fall times are from 10% to 90%.

Note 4: Recommended programming temp.  $T_C = +25^{\circ}C \pm 10^{\circ}C$ .

Note 5: Proceed to next address after read strobe indicates programmed  $\varepsilon \text{ell.}$

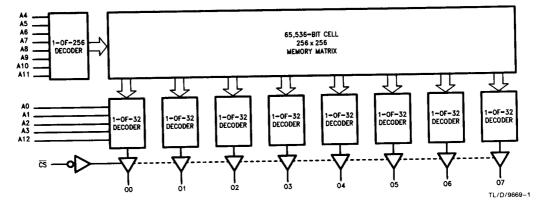

#### **Block Diagram**

Note: Programmed = Low Unprogrammed = High on the Outputs

#### **Functional Description**

The 93Z665 and 93Z667 are TTL bipolar field Programmable Read Only Memories (PROMs) organized 8192 words by eight bits per word. The 93Z665 and 93Z667 have TRISTATE outputs which provide active pull-ups and pull-downs when enabled and high output impedence when disabled. This allows optimization of word expansion in bus organized systems.

Chip Select is provided for memory expansion without the need for additional decoding. The fast Chip Select access time permits direct address decoding without increasing overall memory access times. The device is enabled only when  $\overline{CS}$  is LOW. During system power up, outputs remain in the high impedance state until DC power supply conditions are met, thereafter changing state according to the condition of  $\overline{CS}$ .

The devices contain internal test rows and test columns which are accessed and programmed during both wafer sort and final test. These test fuses are used to assure high programmability and to guarantee AC performance and DC parameters. PROM programmability is verified through test row and test column. PROM input levels on unprogrammed devices are also verified through testing of test row and test column.

The 93Z665 and 93Z667 use open base vertical (junction) fuse cells. Initially the unprogrammed cell is in the logic "1" state. A cell can be programmed to the logic "0" state by following the specified programming procedure which defuses aluminum through the emitter base junction of the cell transistor, thereby forming a low impedance path.

The read function is identical to that of a conventional Read Only Memory (ROM). A binary address is applied to the address pins A0 through A12 and the chip is selected. Data is then available at the outputs after t<sub>AA</sub>.

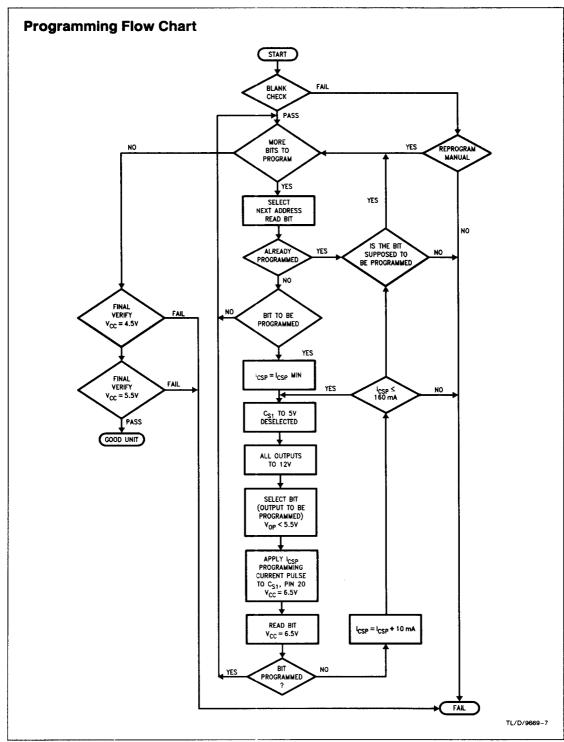

## **Programming**

The 93Z665 and 93Z667 are manufactured with all bits in the logic "1" state. Any desired bit (output) can be

programmed to a logic "0" state by following the procedure below. One may use any of the commercially available programmers which have been approved by National Semiconductor.

- I. Blank Check-Initial Read.

- A. Chip Select is Enabled

- B. V<sub>CC</sub> is Raised to 5.5V

- C. TTL Levels are Applied to All Address Lines

- D. Verify All Outputs are TTL High on All Addresses

- E. Repeat C and D until All Addresses have been Checked

- II. Programming Mode

- A. TTL Levels are Applied to All Address Lines

- B. V<sub>CC</sub> is Raised to 6.5V

- C. Chip Select is Deselected

- D. All Outputs are Raised to 12V

- E. Selected Output is Lowered Below 5.5V

- F. Programming Current Pulse Train is Applied to the Chip Select Pin

- G. Consecutive Current Pulses are 7  $\mu s-9$   $\mu s$  Wide and Increase at 10 mA per Pulse

- H. A Read is Performed before and after Each Pulse  $(V_{CC} = 6.5V)$

- I. The Programming Current is Stepped Up until the Cell Programs

- III. Final Verify (2 Pass)

- A. V<sub>CC</sub> is Lowered to 4.5V

- B. Chip Select is Enabled

- C. TTL Levels are Applied to All Address Lines

- D. Verify Pattern on All Outputs, All Addresses

- E. Repeat C and D for All Addresses

- F. V<sub>CC</sub> Increases to 5.5V

- G. Repeat B, C, D and E

4-103

T.S. is TRI-STATE.

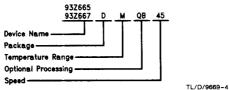

**Packages**

D = Side-Braze DIP

L = Leadless Chip Carrier

F = Flatpak

Temperature Ranges

Com. = 0°C to +75°C

Mil. =  $-55^{\circ}$ C to  $+125^{\circ}$ C

Speed

Com = 35 ns Mil. = 45 ns

= 40 ns = 50 ns = 45 ns = 55 ns

**Optional Processing**

QB = Mil STD 883

Method 5004 & 5005

Level B