# **PD32HC01**

## DIGITAL SIGNAL PROCESSOR INTERFACE for the TMS 32010 / DSP 32010

#### **Features**

- Single-chip solution to TMS32010 serial interfacing

- Serial Codec port

- · Serial Data communications port

- I/O and Interrupt control

- Decoding for external RAM and ROM memory

- I/O expansion interface

- · 2400 Hz bit rate generator

- Low-power CMOS technology

## **Applications**

- Digital Telephony

- Data Communications

- Digital Radio

- · Voice Coders/Decoders

- · Speech Synthesis

- · Speech Recognition

### Description

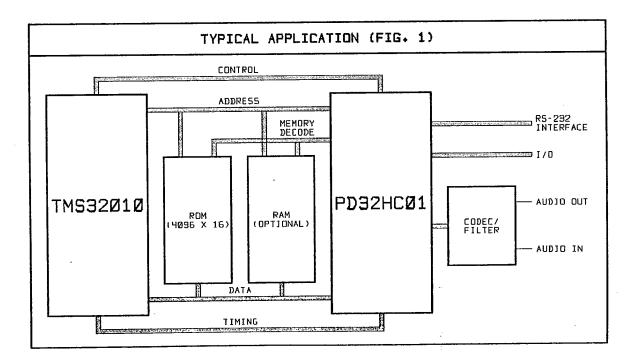

The PD32HC01 is a DIGITAL SIGNAL PROCESSOR INTERFACE circuit, intended for use in voice band signal processing circuits. It provides an optimized interface between the TMS32010 digital signal processor, and external RAM, ROM, and Codec.

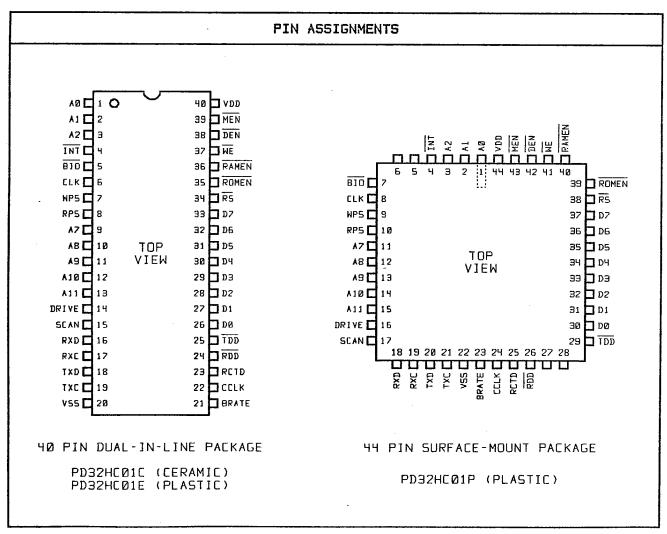

## Package Availability

- 40 Lead DIL Ceramic (PD32HC01C)

- 40 Lead DIL Plastic (PD32HCO1E)

- 44 Lead Surface Mounted Plastic (PD32HC01P)

© 1985 Pacific Microcircuits Ltd. D/S 601-00012-AA January 1986

Pacific Microcircuits Ltd.,

In Canada: Pacific Microcircuits Ltd.,

240 'H' Street, Blaine, WA 98230 1645 - 140th St., White Rock, BC V4A 4H1 1-800-663-5015 (604) 536-1886

# PD32HC01 Pin Description

| <u>Pin</u>  | <u>Name</u>        | <u>I/O</u>       | Description                                                                                                             |

|-------------|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1-3         | A0-A2              | Inputs           | Address bus from processor.                                                                                             |

| 4           | INT-               | Output           | Interrupt request to processor. Responds to RXC, TXC, or Codec                                                          |

|             |                    |                  | A/D interrupts.                                                                                                         |

| 5           | BIO-               | Output           | Polled output port bit to processor. Data source to be polled is                                                        |

| _           |                    |                  | specified in the Peripheral Status Register.                                                                            |

| 6           | CLK                | Input            | 4.128 MHz (nominal) clock, derived from processor clock. Drives                                                         |

| 7.0         | WDE DDE            | Outout           | the bit rate generator and Codec interface timing.  Decoded I/O port write and read pulses for I/O expansion.           |

| 7,8<br>9-13 | WP5, RP5<br>A7-A11 | Output<br>Inputs | Address bus from processor.                                                                                             |

| 14          | DRIVE              | Output           | Output bit controlled from the Peripheral Status Register.                                                              |

| 15          | SCAN               | Input            | Input bit selected from the Peripheral Status Register to appear on BIO                                                 |

| 16          | RXD                | Input            | Serial data input. Must be stable on the rising edge of RXC.                                                            |

| .0          | 117.2              |                  | Selected from the Peripheral Status Register to appear on BIO                                                           |

| 17          | RXC                | Input            | Serial data receive clock. Rising edge retimes RXD, and raises an                                                       |

|             |                    | •                | RX clock interrupt.                                                                                                     |

| 18          | TXD                | Output           | Serial data output. Programmed from the Peripheral Status                                                               |

|             |                    |                  | Register. Edges of TXD are synchronized to the rising edge of TXC.                                                      |

| 19          | TXC                | Input            | Serial data transmit clock. Rising edge clocks out data onto TXD                                                        |

|             |                    | _                | from the Peripheral Status Register, and raises a TX clock interrupt.                                                   |

| 20          | v <sub>ss</sub>    | Power            | Negative supply (ground).                                                                                               |

| 21          | BRATE              | Output           | 2400 Hz square wave (CLK / 1720 mask programmable).                                                                     |

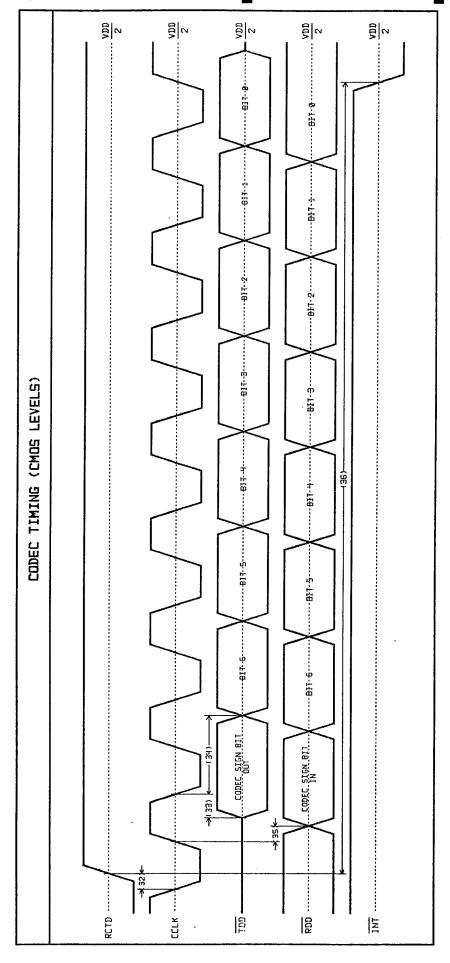

| 22          | CCLK               | Output           | 2.064 MHz (nominal) Codec clock.                                                                                        |

| 23          | RCTD               | Output           | Codec framing pulse for Codec synchronization. Codec A/D                                                                |

| 0.4         | 888                | 0.44             | interrupt occurs 16 CLK cycles after RCTD goes high. Serial data output to Codec. PCM data is shifted out on the rising |

| 24          | RDD-               | Output           | edges of the first 8 CCLK cycles after the rising edge of RCTD.                                                         |

| 25          | TDD-               | Input            | Serial data input from Codec. PCM data is sampled on the first 8                                                        |

| 25          | 100-               | mpat             | CCLK falling edges after the rising edge of RCTD.                                                                       |

| 26-33       | D0-D7              | In/Out           | Data bus to chip.                                                                                                       |

| 34          | RS-                | Input            | Master reset to chip. A low on this input will reset the INT- signal,                                                   |

|             |                    |                  | and initalize the bit rate timer. This is a Schmitt trigger input.                                                      |

| 35          | ROMEN-             | Output           | ROM enable output. This signal goes low during a valid read from                                                        |

|             |                    |                  | memory locations >000 - >F7F (MEN- low).                                                                                |

| 36          | RAMEN-             | Output           | RAM enable output. This signal goes low during a valid read or write                                                    |

|             |                    |                  | to memory locations >F80 - >FFF (MEN- low or WE- low).                                                                  |

| 37          | WE-                | Input            | Write enable to chip. Goes low for I/O or RAM write operations.                                                         |

| 38          | DEN-               | Input            | Data enable to chip. Goes low for I/O read operations.  Memory enable to chip. Goes low for ROM or RAM reads.           |

| 39<br>40    | MEN-               | Input<br>Power   | Positive supply (+5 Volts).                                                                                             |

| 40          | $v_{DD}$           | Power            | rusitive supply (+3 votts).                                                                                             |

|             |                    |                  |                                                                                                                         |

### **Detailed Description**

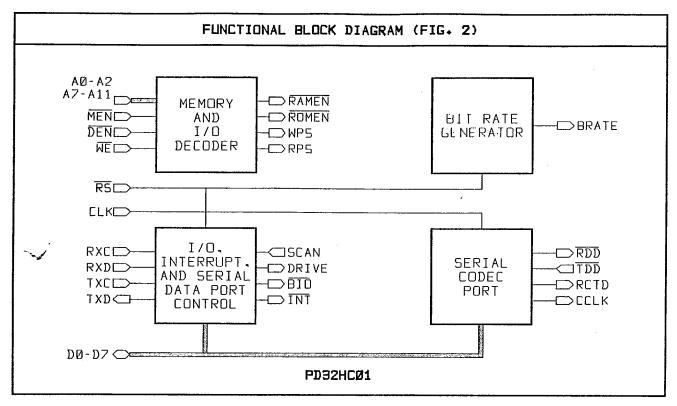

The PD32HC01 consists of 4 functional blocks: a memory and I/O decoder; I/O, interrupt, and serial data port control; a serial Codec port; and a bit rate generator (see figures, 2 & 3).

#### Memory and I/O Decoder

The memory and I/O decoder segments the 4K word address space of the TMS32010 into 3 areas: a 3968 word ROM area inclusive of addresses >000 to >F7F; a 128 word RAM area inclusive of addresses >F80 to >FFF: and from addresses >XX0 to >XX7, an I/O expansion port, an I/O, interrupt, and serial data port control; and a serial Codec port.

#### Memory Decoding

The ROMEN- signal is used for selecting external program ROM. It goes low during memory read or table read cycles (MEN- low), and the processor address is less than >F80.

The RAMEN- signal is used for selecting external data RAM. It goes low during memory read, table read, or table write cycles (MEN- or WE- low), and the processor address is above >F7F.

#### I/O Expansion Port

The RP5 and WP5 signals are used for I/O port expansion. RP5 goes high during an I/O read cycle from port 5 (DEN- low). WP5 goes high during an I/O write cycle to port 5, or a table write cycle to address >XX5 (WE- low).

#### I/O, Interrupt, and Serial Data Port

The Program Status Register (PSR) at port location 6 controls the DRIVE and TXD output signals; the INToutput operation via the Codec A/D, TX clock, and RX clock interrupt mask bits; and selects inputs to be tested on BIO- (interrupt flags; the SCAN input; or the retimed RXD input). The bit encoding of the PSR is shown below:

bit 0: RXMSK, RX clock interrupt mask. bit 1: TXMSK, TX clock interrupt mask. bit 2: ADMSK, Codec interrupt mask.

Writing 1's to these bits will mask interrupts from the respective sources, and/or clear posted interrupts. Writing 0's will enable interrupts. By testing for the interrupting source on the BIO- line, interrupt vectoring can be managed (see bits 3,4,5 description).

bits 3,4,5: BIO Source Select. These three bits select one of five input sources (interrupt flags or pin inputs) onto the BIO- output.

| bit 5 | bit 4 | bit 3 | Selected Source       |

|-------|-------|-------|-----------------------|

| 0     | 0     | 0     | Codec A/D Int. status |

| 0     | 0     | 1     | TX Clock Int. status  |

| 0     | 1     | 0     | RX Clock Int. status  |

| 0     | 1     | 1     | SCAN bit input        |

| 1     | X     | X     | Retimed RXD input     |

Whenever a posted interrupt is selected, BIO- will go low. BIO- will stay high if the selected interrupt is not posted. When the SCAN- input or the retimed RXD input is selected, BIO- follows the polarity of the respective signal.

bit 6: TXD, the serial data port transmit data bit. This signal is retimed by the rising edge of the TXC clock, and appears on the TXD output pin.

bit 7: DRIVE, a general purpose output pin.

#### Serial Codec Port

The Serial Codec Port consists of 8-bit Transmit and Receive data registers, designed to directly interface to Motorola 14400 series PCM Monochips, and the Intel 2914.

The Transmit Register forms incoming serial data on TDD- into 8-bit parallel PCM samples, while the Receive Register forms 8-bit parallel PCM data samples into serial data on RDD- . The operation of these registers is controlled by the Codec Timing Generator, which also generates the CCLK, the RCTD, and the internal A/D interrupt signals.

Data written to the Receive Register at I/O port location 3 is inverted, and sent MSB first on the RDD- Pin. Data is shifted out on the 8 rising edges of CCLK following the rising edge of RCTD. To prevent Receive Register underflow, data must be available in the Receive Register within 248 CCLK cycles after an A/D interrupt (nominally 120 usec).

Serial PCM data on the TDD- pin is inverted, and read into the Transmit Register, MSB first, at I/O port location 3. Data is shifted in on the 8 falling edges of CCLK following the rising edge of RCTD. To prevent Transmit Register overflow, data must be read within 248 CCLK cycles after an A/D interrupt (nominally 120 usec).

#### Bit Rate Generator

The BRATE output signal is nominally a 2400 Hz square wave, derived from the CLK input divided by 1720 (mask programmable). This signal may be used for bit rate generation, TXC or RXC clocking, or real-time interrupts. BRATE is reset whenever the RS- signal is low.

| Address/<br><u>Ports</u> | <u>R/W</u> 2      | <u>Function</u>                                                                                                                                                                                                                                                                                                                      |

|--------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| >XX3<br>Port 3           | Read <sup>3</sup> | Codec Transmit Register. Valid for 248 CCLK cycles (nominally 120 usec) after an A/D interrupt. This 8-bit register contains the inverted version of the digitized serial PCM signal appearing on TDD This register can only be read by using a IN from port 3 instruction.                                                          |

| >XX3<br>Port 3           | Write             | Codec Receive Register. Must be valid within 248 CCLK cycles (nominally 120 usec) after an A/D interrupt. Data written to this 8-bit register will be inverted and shifted out on the RDD- pin. This register can be written using a OUT to port 3 instruction, or by using a TBLW to address >XX3 (address must be less than >F80). |

| >XX5<br>Port 5           | Read <sup>3</sup> | Input Port Expansion. The RP5 signal will pulse high whenever an IN from port 5 instruction is executed.                                                                                                                                                                                                                             |

| >XX5<br>Port 5           | Write             | Output Port Expansion. The WP5 signal will pulse high whenever an OUT to port 5, or TBLW to >XX5 instruction is executed (address must be less than >F80).                                                                                                                                                                           |

| >XX6<br>Port 6           | Write             | Peripheral Status Register. This register is used to: Select I/O and interrupt status bits onto the BIO- pin; mask and reset interrupts; control the DRIVE pin; and to send data on TXD. This register can be written using an OUT to port 6 instruction, or by using a TBLW to address >XX6 (address must be less than >F80).       |

| >000-<br>>77F            | Read              | Program ROM space. Notice that the I/O space and the ROM space are mapped to overlapping addresses, but are distinguished by the MEN- and DEN- signals. MEN- will go low for valid instruction reads, while DEN- will go low for I/O reads.                                                                                          |

| >780-<br>>7FF            | R/W               | Data/Program RAM space. For read cycles, MEN- goes low; for write cycles WE- goes low.                                                                                                                                                                                                                                               |

#### Notes:

- When using TBLW to perform Output, many aliases of the I/O port locations exist due to incomplete address decoding. To maintain compatibility with future products, it is recommended that addresses >000 to >007 be used. When using OUT instructions, the TMS32010 always addresses >000 to >007, and the aliases are irrelevant.

- Some I/O addresses are not used. To prevent data corruption, port locations 0, 1, 2, and 4 should not be written with TBLW or OUT.

- The I/O read locations can only be accessed with a TMS32010 IN instruction. The actual address locations are shown, however, for applications using other than the TMS32010 processor.

| <u>Parameter</u><br>Supply voltage | <u>Symbol</u><br>V <sub>DD</sub> | <u>Min</u><br>4.75 | <u>Typ</u><br>5.0 | <u>Max</u><br>5.25   | <u>Units</u><br>V | Notes |

|------------------------------------|----------------------------------|--------------------|-------------------|----------------------|-------------------|-------|

| Input high voltage                 |                                  | 2                  | 0.0               | V <sub>DD</sub> +0.3 | v                 |       |

|                                    | v <sub>IH</sub>                  | . –                |                   |                      | •                 |       |

| Input low voltage                  | $v_IL$                           | -0.3               |                   | 0.8                  | ٧.                |       |

| Output high current                | lон                              |                    |                   | 3                    | mA                |       |

| Output low current                 | loL                              |                    |                   | 3                    | mA                |       |

| Operating Temperature              | $T_A$                            | 0                  |                   | 70                   | .c                |       |

## Electrical characteristics over recommended operating conditions<sup>1</sup>

| <u>Parameter</u>            | Symbol           | <u>Min</u> | Typ <sup>2</sup> | <u>Max</u> | <u>Units</u> | Test Condition             |

|-----------------------------|------------------|------------|------------------|------------|--------------|----------------------------|

| High level output voltage   | v <sub>OH</sub>  | 3.5        | 4.5              |            | V            | I <sub>OH</sub> = 1 ma     |

| Low level output voltage    | $v_{OL}$         |            | 0.3              | 0.5        | ٧            | I <sub>OL</sub> = 2 ma     |

| RS- hysteresis voltage      | V <sub>HYS</sub> |            | 200              |            | mV           |                            |

| Off-state leakage current   | loz              |            | 0.5              | 5          | uA           |                            |

| Input current               | l <sub>IN</sub>  |            | 0.5              | 5          | uA           | $V_{SS} < V_{IN} < V_{DD}$ |

| Supply current <sup>3</sup> | IDD              |            | 2                |            | mA           | •                          |

| Input capacitance           | CI               |            | 10               |            | рF           | @ 1 MHz;                   |

| Output capacitance          | Co               |            | 10               |            | рF           | all other pins 0 V         |

| CLK input frequency         | FCLK             | 0          | 4.128            | 6.25       | MHz          |                            |

Note:

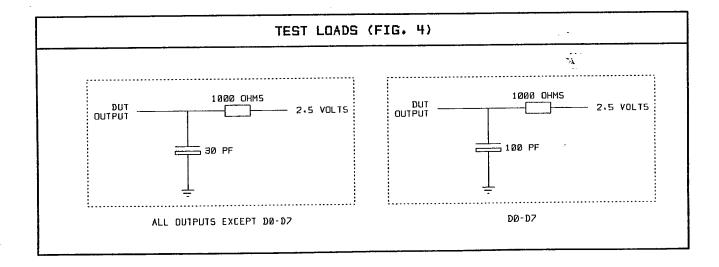

- See Fig. 4 or DUT test loads. Typical specifications are valid at  $T_A$  = 25 °C,  $V_{DD}$  = 5.0 Volts.

- $I_{\mbox{\scriptsize DD}}$  Is a function of  $V_{\mbox{\scriptsize DD}}$ , clock frequency, and output loading.

|   | Name                     | Description                      | Min         | Typ <sup>2</sup> | Max    | Units |

|---|--------------------------|----------------------------------|-------------|------------------|--------|-------|

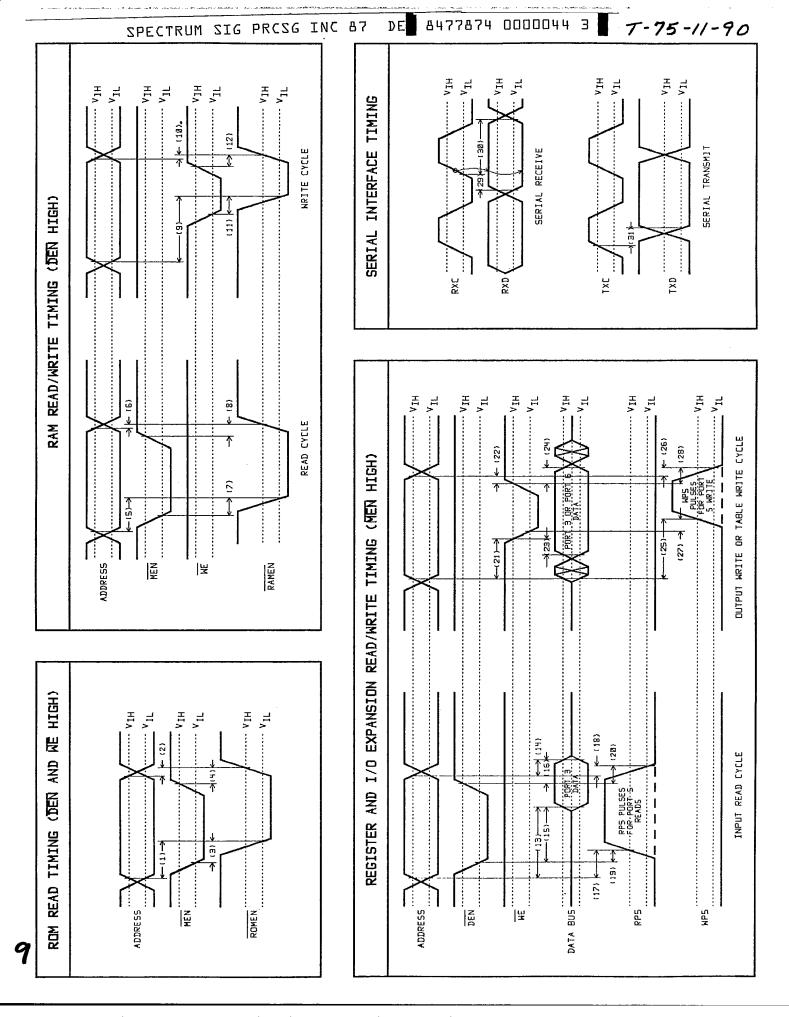

| R | (1) t <sub>ROMHL1</sub>  | ROMEN- select time from addr.    | <del></del> | 28               |        | nsec  |

| 0 | (2) t <sub>ROMLH1</sub>  | ROMEN- deselect time from addr.  |             | 30               |        | nsec  |

| М | (3) t <sub>ROMHL2</sub>  | ROMEN- select time from MEN-     |             | 25               |        | nsec  |

|   | (4) tROMLH2              | ROMEN- deselect time from MEN-   |             | 18               |        | nsec  |

|   | (5) t <sub>RAMHL1</sub>  | RAMEN- select time from addr.    |             | 27               |        | nsec  |

|   | (6) t <sub>RAMLH1</sub>  | RAMEN- deselect time from addr.  |             | 15               |        | nsec  |

| R | (7) t <sub>RAMHL2</sub>  | RAMEN- select time from MEN-     |             | 24               |        | nsec  |

| A | (8) t <sub>RAMLH2</sub>  | RAMEN- deselect time from MEN-   |             | 14               |        | nsec  |

| M | (9) t <sub>RAMHL3</sub>  | RAMEN- select time from addr.    |             | 27               |        | nsec  |

|   | (10) t <sub>RAMLH3</sub> | RAMEN- deselect time from addr.  |             | 15               |        | nsec  |

|   | (11) t <sub>RAMHL4</sub> | RAMEN- select time from WE-      |             | 21               |        | nsec  |

|   | (12) t <sub>RAMLH4</sub> | RAMEN- deselect time from WE-    |             | 15               |        | nsec  |

|   | (13) t <sub>DR1</sub>    | Data read access time from addr. |             | 33               |        | nsec  |

| R | (14) t <sub>DRHLD1</sub> | Data read hold time from addr.   |             | 60               |        | nsec  |

| E | (15) t <sub>DR2</sub>    | Data read access time from DEN-  |             | 29               |        | nsec  |

| G | (16) t <sub>DRHLD2</sub> | Data read hold time from DEN-    |             | 56               |        | nsec  |

| 1 | (17) t <sub>RPLH1</sub>  | RP5 select time from address     |             | 30               |        | nsec  |

| S | (18) t <sub>RPHL1</sub>  | RP5 deselect time from address   |             | 32               |        | nsec  |

| T | (19) t <sub>RPLH2</sub>  | RP5 select time from DEN-        |             | 26               |        | nsec  |

| Ε | (20) t <sub>RPHL2</sub>  | RP5 deselect time from DEN-      |             | 26               |        | nsec  |

| R | (21) t <sub>ASUW</sub>   | Address set-up time to WE-       |             | 4                |        | nsec  |

|   | (22) t <sub>AHLDW</sub>  | Address hold time from WE-       |             | -5               |        | nsec  |

| & | (23) t <sub>DWSU</sub>   | Data write set-up time to WE-    |             | -25              |        | nsec  |

|   | (24) t <sub>DWHLD</sub>  | Data write hold time from WE-    |             | 0                |        | nsec  |

| I | (25) t <sub>WPLH1</sub>  | WP5 select time from address     |             | 31               |        | nsec  |

| 1 | (26) t <sub>WPHL1</sub>  | WP5 deselect time from address   |             | 32               |        | nsec  |

| 0 | (27) t <sub>WPLH2</sub>  | WP5 select time from WE-         |             | 27               |        | nsec  |

|   | (28) t <sub>WPHL2</sub>  | WP5 deselect time from WE-       |             | 27               |        | nsec  |

| S | (29) t <sub>RXDSU</sub>  | RXD set-up time to RXC           | 20          | 3                |        | nsec  |

| I | (30) tRXDHLD             | RXD hold time from RXC           | 20          | 2                |        | nsec  |

| 0 | (31) t <sub>TXD</sub>    | TXD delay time from TXC          |             | 28               |        | nsec  |

| С | (32) t <sub>RCTD</sub>   | RCTD Delay time from CCLK        | 15          | 34               | 100    | nsec  |

| 0 | (33) t <sub>TDDSU</sub>  | TDD- set-up time to CCLK         | 50          | 16               |        | nsec  |

| D | (34) t <sub>TDDHLD</sub> | TDD- hold time from CCLK         | 20          | -14              |        | nsec  |

| E | (35) t <sub>RDD</sub>    | RDD- delay time from CCLK        |             | 19               | -50    | nsec  |

| C | (36) t <sub>ADINT</sub>  | INT- delay time from RCTD        |             |                  | Note 3 |       |

Note:

1.

See Fig. 4 for DUT test loads.

Typical specifications are valid at T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 5.0 Volts 2.

$t_{\mbox{ADINT}}(\mbox{max})$  is 17 x  $t_{\mbox{CLK}}$  - 45 nsec (nominally 4.1 usec).