# High Speed Pin Driver with Inhibit Mode

AD1321

FEATURES

100 MHz Driver Operation

Driver Inhibit Function

250 ps Edge Matching

Guaranteed Industry Specifications

50 Ω Output Impedance

1 V/ns Slew Rate

Variable Output Voltages for ECL, TTL and CMOS

High Speed Differential Inputs for Maximum Flexibility

Hermetically Sealed Small Gull Wing Package

APPLICATIONS

Automatic Test Equipment

Semiconductor Test Systems

Semiconductor Test Systems

Board Test Systems

Instrumentation & Characterization Equipment

#### PRODUCT DESCRIPTION

The AD1321 is a complete high speed pin driver designed for use in digital or mixed signal test systems. By combining a high speed monolithic process with a unique surface mount package, this product attains superb electrical performance while preserving optimum packaging densities and long term reliability in an ultrasmall 16-lead, hermetically sealed gull wing package.

Featuring unity gain programmable output levels of -2 V to +7 V with output swing capability of less than 100 mV to 9 V, the AD1321 is designed to stimulate ECL, TTL and CMOS logic families. The 100 MHz (5.0 ns pulsewidth) data rate capacity, 1 V/ns slew rate, and matched output impedance allows for real-time stimulation of these digital logic families. To test I/O devices, the pin driver can be switched into a high impedance state (inhibit mode) electrically removing the driver from the path through the inhibit mode feature. The pin driver leakage current in inhibit is typically 50 nA, and output charge transfer entering inhibit is typically less than 15 pC.

The AD1321 transition from HI/LO or to inhibit is controlled through the data and inhibit inputs. The input circuitry is implemented utilizing high speed differential inputs with a common mode range of 3 volts. This allows for direct interface to

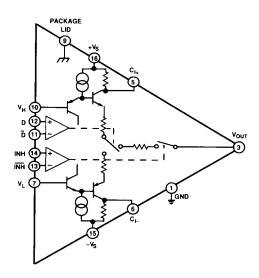

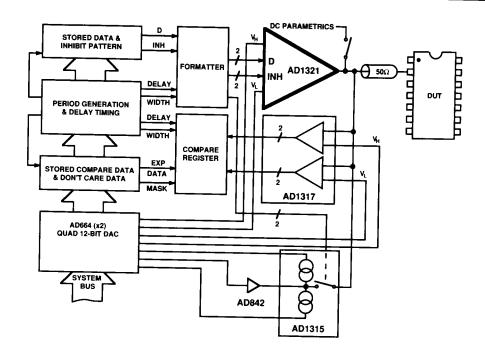

#### FUNCTIONAL BLOCK DIAGRAM

the precision of differential ECL timing or the simplicity of stimulating the pin driver from a single ended TTL or CMOS logic source. The analog logic HI/LO inputs are equally easy to interface. Typically requiring 350  $\mu$ A of bias current, the AD1321 can be directly coupled to the output of a digital-to-analog converter.

The 150 MHz analog bandwidth of the logic HI/LO inputs allows for four quadrant multiplying providing maximum flexibility as a standard pin driver and a waveform generator all in one package.

The AD1321 is available in a 16-lead, hermetically sealed gull wing package and is specified to operate over the ambient commercial temperature range from 0 to  $+70^{\circ}$ C.

# AD1321 — SPECIFICATIONS (All measurements made in free air at +25°C. Output load 10 k $\Omega$ /6 pF with + $v_s$ = +10 V, - $v_s$ = -5.2 V unless otherwise noted)

|                                                   |                               | 321KZ    | Max               | Units          | Comments                        |

|---------------------------------------------------|-------------------------------|----------|-------------------|----------------|---------------------------------|

| Parameter                                         | Min                           | Тур      | Max               |                |                                 |

| DIFFERENTIAL INPUT                                |                               |          |                   |                |                                 |

| CHARACTERISTICS                                   |                               |          |                   |                |                                 |

| D to $\overline{D}$ , INH to INH                  |                               |          | . 7.0             | Volts          |                                 |

| Input Voltage, Any One Input                      | -2.0                          |          | +7.0              | Volts          |                                 |

| Differential Input Range                          | 0.4                           | ECL      | 3.0               |                |                                 |

| Bias Current                                      |                               | 175      | 300               | μΑ             |                                 |

| REFERENCE INPUTS                                  |                               |          |                   | ¥7. h.         | See Note 1                      |

| $V_{HIGH}$ Range $(V_H)$                          | -2.5                          |          | +7.5              | Volts          |                                 |

| V <sub>LOW</sub> Range (V <sub>L</sub> )          | -2.5                          |          | +7.5              | Volts          |                                 |

| V <sub>HIGH</sub> Bias Currents (V <sub>H</sub> ) |                               | 0.5      | 1.2               | mA             |                                 |

| V <sub>LOW</sub> Bias Currents (V <sub>L</sub> )  |                               | 0.3      | 0.5               | mA             | 0 5: 0                          |

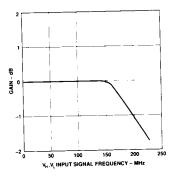

| Input Bandwidth                                   |                               | 150      |                   | MHz            | See Figure 9                    |

| OUTPUT CHARACTERISTICS                            |                               |          |                   |                | See Notes 1, 2                  |

| Logic High Range                                  | -2.0                          |          | +7.0              | Volts          |                                 |

| Logic Low Range                                   | -2.0                          |          | +7.0              | Volts          |                                 |

| Amplitude $[V_H - V_L]$                           | 0.1                           |          | +9.0              | Volts          |                                 |

|                                                   |                               |          |                   |                | See Figure 1                    |

| Accuracy<br>Initial Offset                        | -50                           |          | +50               | mV             |                                 |

|                                                   | -4.5                          | -2.5     | -0.5              | % of Set Level | See Note 3                      |

| Gain Error                                        | 4.5                           |          |                   |                |                                 |

| Linearity Error                                   | -0.5                          |          | +0.5              | % of Set Level |                                 |

| 0 V to +5.5 V                                     | -1.0                          |          | +1.0              | % of Set Level |                                 |

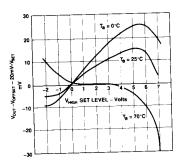

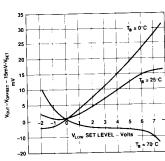

| -2  V to  +7  V                                   | -1.0                          | 0.5      | 1.0               | mV/°C          | See Figures 7 & 8               |

| Output Voltage TC                                 |                               | 0.5      |                   |                |                                 |

| Current Drive                                     | 20                            |          |                   | mA             |                                 |

| Static                                            | 30                            |          |                   | mA             | See Note 4                      |

| Dynamic                                           | 100                           |          | 85                | mA             |                                 |

| Current Limit                                     | 40.5                          | 50.0     | 51.5              | ohms           | See Note 5                      |

| Output Impedance                                  | 48.5                          |          |                   | +              |                                 |

| DYNAMIC PERFORMANCE                               |                               |          |                   |                | See Note 6                      |

| Driver Mode                                       |                               |          | 1.7               |                | See Figure 2                    |

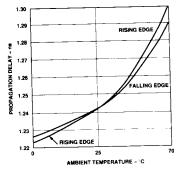

| Delay Time                                        | 0.8                           | 1.2      | 1.6               | ns<br>ms/°C    | See Figure 4                    |

| Prop Delay TC                                     |                               | 2.0      |                   | ps/°C          | See Figure 1                    |

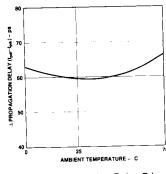

| Delay Time Matching                               |                               |          | 270               |                | See Figure 5                    |

| Edge-to-Edge                                      | -250                          | $\pm 80$ | + 250             | ps             | See Figure 10                   |

| Rise & Fall Times                                 |                               |          |                   |                | Measurement 20%–80%             |

| 1 V Swing                                         |                               | 0.9      | 1.2               | ns             | Measurement 10%–90%             |

| 3 V Swing                                         |                               | 2.7      | 3.0               | ns             |                                 |

| 5 V Swing                                         |                               | 4.0      | 4.4               | ns             | Measurement 10%–90%             |

| Large Signal Slew                                 | 0.8                           | 1.1      |                   | V/ns           | Measurement 20%-80% of 9 V Swin |

| Toggle Rate                                       | 100                           |          |                   | MHz            | ECL Output                      |

| Minimum PW, $V_{OUT} = 2 \text{ V}$               |                               | 5.0      |                   | ns             | See Figure 12                   |

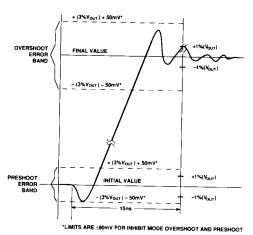

| Overshoot & Preshoot                              | $-(3\% \text{ V}_{\odot})-50$ |          | $+(3\% V_{O})+50$ | mV             | See Figure 3, Note 7            |

| Settling Time                                     | ) ) )                         |          |                   |                | See Figure 3, Note 7            |

| to $\pm 1\% V_{\Omega}$                           |                               |          | 15                | ns             |                                 |

| Delay Time vs. PW                                 |                               | 150      |                   | ps             | See Note 8; See Figure 6        |

6–34 ATE COMPONENTS

| _                      |             | AD1321K2 | Z     |                     |                         |  |

|------------------------|-------------|----------|-------|---------------------|-------------------------|--|

| Parameter              | Min         | Typ      | Max   | Units               | Comments                |  |

| DYNAMIC PERFORMANCE    |             |          |       | <del>-  </del>      |                         |  |

| Inhibit Mode           |             |          |       |                     | San Films 2             |  |

| Delay Time             |             |          |       |                     | See Figure 2 See Note 9 |  |

| Drive-to-Inhibit       | 1.1         |          | 1.7   | ns                  | See Note 9              |  |

| Inhibit-to-Drive       | 1.6         |          | 2.2   | ns ns               |                         |  |

| Edge-to-Edge Matching  | -250        | ±100     | +250  | 1                   |                         |  |

| Overshoot & Preshoot   |             | 40       | 80    | ps<br>mV            | C . T' 2                |  |

| Output Capacitance     |             | 8        | 10    | pF                  | See Figure 3            |  |

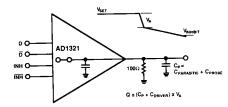

| Output Charge Going    | 1           | ŭ        | 10    | pr                  |                         |  |

| into Inhibit Mode      |             | 15       |       | 1-0                 | 0 77                    |  |

| Leakage Current        | İ           | 13       |       | рC                  | See Figure 13           |  |

| in Inhibit Mode        | ļ           |          |       |                     |                         |  |

| -2 V to +5 V           |             | 50       | 200   |                     |                         |  |

| +5 V to +7 V           |             | 50       | 1.0   | nA                  | ļ                       |  |

| POWER SUPPLIES         | <del></del> |          |       | μА                  |                         |  |

| $-V_S$ to $+V_S$ Range |             |          |       | ľ                   |                         |  |

| Supply Range           | 1           | 15.2     | 15.4  | Volts               |                         |  |

| Positive Supply        |             |          |       |                     | See Note 10             |  |

| Negative Supply        | +8.0        |          | +12.0 | Volts               |                         |  |

| Current                | -7.2        | -5.2     | -3.2  | Volts               |                         |  |

|                        | 42          |          |       |                     |                         |  |

| Positive Supply        | 42          | 60       | 78    | mA                  |                         |  |

| Negative Supply        | <b>−78</b>  | -60      | -42   | mA                  |                         |  |

| $+PSRR V_{OH} = +7 V$  | 0.5         |          | 0.5   | %/%V <sub>OUT</sub> | $+V = \pm 2.5\%$        |  |

| $-PSRR V_{OL} = -2 V$  | 0.5         |          | 0.5   | %/%V <sub>OUT</sub> | $-V = \pm 2.5\%$        |  |

#### NOTES

<sup>3</sup>The gain error of the driver is always in the negative direction with respect to the voltage set level.

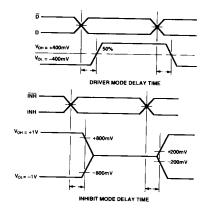

Delay times are measured from the crossing of differential ECL outputs at the inputs to the driver to the 50% point of an ±400 mV driver output.

Specifications subject to change without notice.

# ABSOLUTE MAXIMUM RATINGS\*

| Power Supply Voltage                                                    |

|-------------------------------------------------------------------------|

| +V <sub>s</sub> to GND                                                  |

| -V <sub>s</sub> to GND8.2 V                                             |

| Difference from $+V_s$ to $-V_s$                                        |

| Inputs                                                                  |

| Difference from D to D 5 V                                              |

| Difference from INH to INH 5 V                                          |

| D, $\overline{D}$ , INH, $\overline{INH}$ + $V_s$ -12 V, $-V_s$ +11.5 V |

| $V_H$ to $V_L$                                                          |

| $V_{H}, V_{L} \dots + V_{S} - 13.0 V, -V_{S} + 13.2 V$                  |

| Driver Output                                                           |

| Voltage $+V_{s}$ -13.0 V, $-V_{s}$ +13.2 V                              |

| Short Circuit to GND                                                    |

| Operating Temperature Range                | to +70°C |

|--------------------------------------------|----------|

| Storage Temperature Range65°C to           | +125℃    |

| Lead Temperature Range (Soldering 20 sec)† | + 300°C  |

#### NOTES

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>†</sup>To ensure lead coplanarity (±0.002 inches) and solderability, handling with bare hands should be avoided and the device should be stored in an environment at 24°C, ±5°C (75°F, ±10°F) with relative humidity not to exceed 65%.

The output voltage range is specified for -2 V to +7 V for typical power supply values of -5.2 V and +10.0 V but can be offset for different values of VOLT such as 0 V to +9 V as long as the required headroom of 3 V is maintained between both V<sub>H</sub> and +V<sub>S</sub> and V<sub>L</sub> and -V<sub>S</sub>.

<sup>&</sup>lt;sup>2</sup>V<sub>H</sub> can be set to be as much as 4 volts below V<sub>L</sub> without any harm to the driver with the restriction that neither level can go below -2 V with the typical power supply setting. In this condition the rise and fall times will approximately double.

<sup>\*</sup>Transient output current can easily exceed the AD1321's steady-state current limit when driving capacitive loads. The transient output current capability can be increased by connecting 0.039 µF capacitors between Pin 5 and ground and Pin 6 and ground. This will prevent the driver from current limiting by providing the "edge" current necessary when driving capacitive loads. These capacitors will not affect the driver's de current limit. <sup>5</sup>Driver output resistance is trimmed and guaranteed for a 3 V swing into a 50 ohm cable.

Due to uncontrolled inductances in the test socket, overshoot, preshoot and settling time cannot be 100% tested. These characteristics are guaranteed based on

Delay matching vs. PW is defined as the amount of change in propagation, with respect to the leading edge, due to change in pulsewidth of the input signal. The AD1321 is characterized over the pulsewidth range of 5 ns to 100 ns.

Inhibit mode delay times are measured from the crossing of differential (ECL) INH inputs to a 200 mV transition at the pin driver output. V<sub>OUT</sub> is connected to a 100 ohm/15 pF load terminated to ground.  $V_{O'I}$  is set at +1 V and  $V_{OL}$  is set at -1 V for this test.

<sup>&</sup>lt;sup>10</sup>A supply range of 15.2 V must be maintained to guarantee a 9 V output swing.

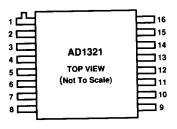

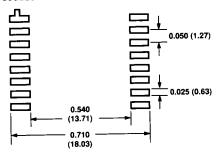

# CONNECTION DIAGRAMS

Dimensions shown in inches and (mm).

# SUGGESTED LANDING PADS LOCATION

# PIN CONFIGURATION

| PIN NO. | SYMBOL          | FUNCTION           |

|---------|-----------------|--------------------|

| 1       | GND             | CIRCUIT GROUND     |

| 2       | N/C             | NO CONNECTION      |

| 3       | Vout            | DRIVER OUTPUT      |

| 4       | N/C             | NO CONNECTION      |

| 5       | C <sub>I+</sub> | POSITIVE DECOUPLE  |

| 6       | C <sub>L</sub>  | NEGATIVE DECOUPLE  |

| 7       | l v⊾            | VOLTAGE LOGIC LOW  |

| 8       | N/C             | NO CONNECTION      |

| 9       | LID             | LID CONNECTION*    |

| 10      | V <sub>H</sub>  | VOLTAGE LOGIC HIGH |

| 11      | <u>ס</u>        | DRIVER INPUT       |

| 12      | D               | DRIVER INPUT       |

| 13      | INH             | INHIBIT INPUT      |

| 14      | INH             | INHIBIT INPUT      |

| 15      | -V <sub>s</sub> | NEGATIVE SUPPLY    |

| 16      | +V <sub>s</sub> | POSITIVE SUPPLY    |

\*IT IS RECOMMENDED TO CONNECT PIN 9 TO CIRCUIT GROUND.

# ORDERING GUIDE

| Model    | Temperature<br>Range | Package<br>Option*              |

|----------|----------------------|---------------------------------|

| AD1321KZ | 0 to +70°C           | 16-Lead<br>Gull Wing<br>(Z-16A) |

<sup>\*</sup>For outline information see Package Information section.

# **Definition of Terms—AD1321**

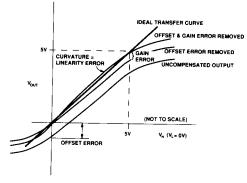

#### OFFSET ERROR

The offset error for logic high is determined by holding the output of the driver at logic high, and applying zero volts to the logic high reference input. The driver output value represents the offset "high" error. The same approach is used to identify offset "low" error

$$V_{HIGH\ OFFSET} = V_{OUT}$$

where:

$V_H = 0 V$ D = HIGH

$\overline{\mathbf{D}} = \mathbf{LOW}$

INH = LOW

INH = HIGH.

#### GAIN ERROR

Defined as the ratio of the driver's output voltage to its logic set level voltage and is expressed in terms of percent of set level. The gain error is typically seen as 2.5% and is always in the negative direction with respect to the logic set level

$$V_{HIGH\ GAIN}$$

(%) =  $\frac{V_{OUT} - V_H - V_{HIGH\ OFFSET}}{V_H} \times 100$

where:

$V_{H} = 5.0 V + V_{HIGH OFFSET}$

$\underline{\mathbf{D}} = \mathbf{H}\mathbf{I}\mathbf{G}\mathbf{H}$

$\overline{D} = LOW$

$\frac{INH}{INH} = LOW$

# LINEARITY ERROR

The deviation of the transfer function from a reference line. For the AD1321, the linearity error is calculated by subtracting the worst case gain error from the best case gain error (for the specified range) and divide the result by two. This method guarantees that the maximum linearity error for any set level within the specified range will be within the specified limits

### where:

$$V_{HIGH\ LINEARITY}\ (\%) = \frac{V_{HIGH\ GAIN}\ (max) - V_{HIGH\ GAIN}\ (min)}{2} \times 100.$$

# **DELAY TIME**

The amount of time it takes the input signal to propagate through the driver and be converted to the desired logic levels. The measurement technique is defined in the notes and is shown in Figure 2.

#### **EDGE-TO-EDGE MATCHING**

Edge-to-edge matching is the difference, in time, between the delay time of the rising edge and the falling edge.

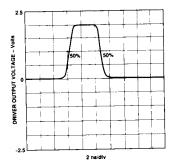

#### MINIMUM PULSEWIDTH

Defined as the smallest pulse applied to the input of the driver which can maintain an output signal amplitude of 2 V. The minimum pulsewidth is measured at the 50% points of the waveform.

# OVERSHOOT AND PRESHOOT

The amount by which the driver's output voltage exceeds the desired set voltage. Preshoot is similar to overshoot but is the amount by which the driver's output goes below the initial voltage when driving to the new set level (or inhibit mode). See Figure 3.

WHERE VOUT = VSET + | OFFSET ERROR | - GAIN ERROR : LINEARITY ERROR

Figure 1. Definition of Terms

Figure 2. Timing Diagram for Driver and Inhibit Propagation Delay

Figure 3. Definition of Waveform Aberrations

# AD1321 — Typical Performance Characteristics

Figure 4. Driver Propagation Delay vs. Temperature

Figure 5. Propagation Delay Edge Matching vs. Temperature

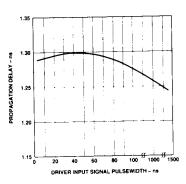

Figure 6. Propagation Delay vs. Input Signal Pulsewidth

Figure 7. Change in V<sub>HIGH</sub> over Temperature

Figure 8. Change in  $V_{LOW}$  over Temperature

Figure 9. V<sub>HIGH</sub> , V<sub>LOW</sub> Input Bandwidth

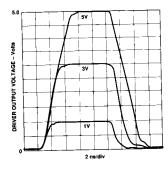

Figure 10. 10 ns Output Pulse at 1 V, 3 V and 5 V

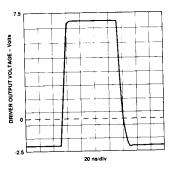

Figure 11.  $V_{OUT} = 9 \text{ V}$  as Seen at the End of a 50 ns, 50  $\Omega$  Cable

Figure 12. Minimum (Data) Pulsewidth as Defined by  $V_{OUT} = 2 V$ , 50% Crossing  $\leq 5 \text{ ns}$

Figure 13. Charge into Inhibit Test Setup

Figure 14. AD1321 Test Setup

# FUNCTIONAL DESCRIPTION

The AD1321 is a complete high speed pin driver designed for use in general purpose instrumentation and digital functional test equipment. The purpose of a pin driver is to accept digital, analog and timing information from a system source and combine these to drive the device to be tested.

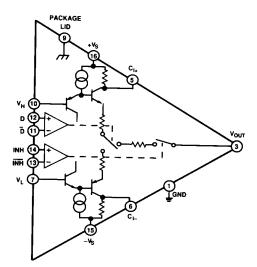

Figure 15. AD1321 Block Diagram

The circuit configuration for the AD1321 is outlined in Figure 15. Simply stated, a pin driver performs the function of a precise, high speed level translator with an output which can be disabled. The AD1321 accepts differential digital information utilizing a high speed differential design on the D and INH inputs providing precise timing at logic crossover and high noise immunity. The wide input voltage range allows for ECL operation with power supplies at 0 to -5.2 V, +2 V to -3.2 V or +5 V to 0 V. Where timing is less critical, TTL or CMOS logic levels may be used to toggle the AD1321. By biasing the D and INH inputs to approximately +1.3 V for TTL and 1/2  $V_{\rm CC}$  for CMOS, the D and INH inputs can be directly driven from these single-ended output sources. The output of the pin driver will follow the logic state of the D input providing the INH input is low. When inhibit is asserted, the output is disconnected and any activity on the input does not affect the output.

Analog information is provided to the pin driver through the  $V_H$  and  $V_L$  terminals as reference voltages. These analog voltages are buffered internally using unity gain followers. The resulting gain and linearity errors are provided in the specification table. System timing requirements are achieved through a specified 1.2 ns,  $\pm 400$  ps driver propagation delay, 1.0 V/ns slew rate, defined preshoot and overshoot, and a dynamically trimmed 50  $\Omega$  output impedance.

# AD1321

# LAYOUT CONSIDERATIONS

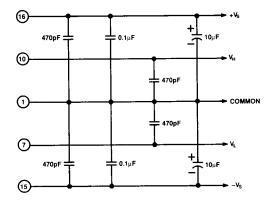

While it is generally considered good engineering practice to capacitively decouple the power supplies of an active device, it is absolutely essential for a high power, high speed device such as the AD1321. The engineer merely has to consider the current pulse demand from the power supply when a dynamic current change of -100 mA to +100 mA is required in only a few nanoseconds. Therefore, a 470 pF high frequency decoupling capacitor must be located within 0.25 inches of the  $+V_s$  and  $-V_s$ terminals to a low impedance ground. A 0.1 µF capacitor in parallel with a 10 µF tantalum capacitor should also be situated between the power supplies and ground however, the proximity to the device is less critical assuming low impedance power supply distribution techniques are employed. Circuit performance will be similarly enhanced and noise minimized by locating a 470 pF capacitor as close as possible to V<sub>H</sub>, V<sub>L</sub> and connected to ground. Bypass considerations have been summarized in Figure 16.

Figure 16. Basic Circuit Decoupling

An equally important consideration is the use of microwave stripline techniques on the output of the AD1321. Failure to preserve the 50  $\Omega$  output impedance of the pin driver will result in unwanted reflections, ringing and general corruption of the wave shape. Care should be exercised when selecting etch widths and routing, wire and cable to the device to be tested, and in choosing relays if they are required.

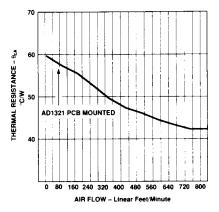

#### THERMAL CONSIDERATIONS

The AD1321 is provided in a  $0.450'' \times 0.450''$ , 16-lead (bottom brazed) gull wing, surface mount package with a typical junction-to-case thermal resistance of  $5.6^{\circ}\text{C/W}$ . Thermal resistance  $\theta_{\text{CA}}$  (case to ambient) vs. air flow for the AD1321 in this package is shown in Figure 17. The improvement in thermal resistance vs. air flow begins to flatten out just above  $400 \text{ lfm}^{(1,2)}$ .

#### NOTES

1lfm is air flow in Linear Feet/Minute.

<sup>2</sup>For convection cooled systems, the minimum recommended airflow is 400 lfm.

Figure 17. Case-to-Ambient Thermal Resistance vs. Air Flow

Figure 18. High Speed Digital Test System Block Diagram

# APPLICATIONS

The AD1321 has been optimized to function as a pin driver in an ATE test system. Shown in Figure 18 is a block diagram illustrating the electronics behind a single pin of a high speed digital functional test system with the ability to test I/O pins on logic devices. The AD1321 pin driver, AD1317 high speed dual

comparator, AD1315 active load, and the AD664 quad 12-bit voltage DAC would comprise the pin electronic portion of the test system. Such a system could operate at 100 MHz in a data mode or 50 MHz in the I/O mode, yet fit into a neat trim package.

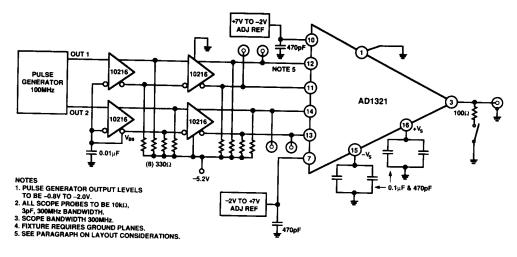

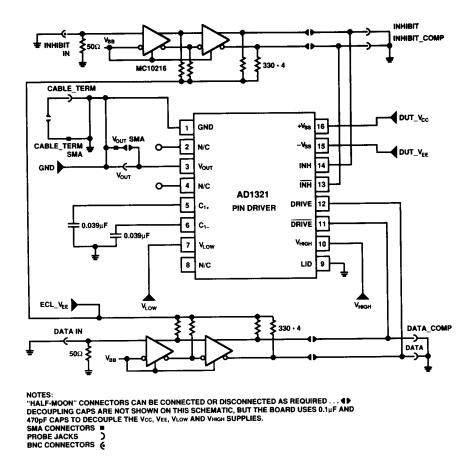

Figure 19. AD1321EB Evaluation Board Schematic

6-42 ATE COMPONENTS REV. A

- CONNECTORS ON AD1321 EVALUATION BOARD:

- 1. DC POWER SUPPLIES: FEMALE BANANA JACKS

- 2. PULSE GENERATORS: FEMALE BNC CONNECTORS

- 3. OSCILLOSCOPE: FEMALE PROBE SOCKET (TEKTRONIX p/n: 131-0258-00)

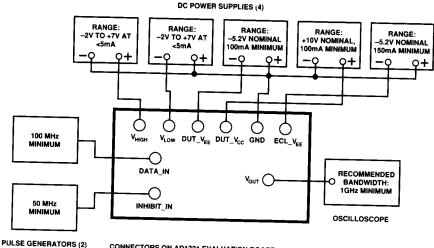

Figure 20. AD1321 Evaluation Board Connections

# **AD1321 EVALUATION BOARD**

#### Introduction

The AD1321EB evaluation board was developed to aid the customer in quickly evaluating the performance of the AD1321. Included is complete documentation of the evaluation board along with suggestions on equipment to use and measurement limitations.

#### Overview

The AD1321 is a high speed pin driver used in automatic test equipment.

The device has true differential inputs for both the drive and inhibit which can be driven from either TTL or ECL logic levels (ECL is recommended). Standard ECL design and layout techniques should be used.

The device runs from dual power supplies +10 V and -5.2 V. It is very important that these power supplies are decoupled properly at the device pin. (High frequency oscillations will couple through to the device output.)

The reference input pins are dc inputs; therefore they also should be decoupled properly. The reference input range is -2 V to +7 V

The output slew rate is 1 V/ns for large signals and has a rep rate for an ECL level of 100 MHz minimum.

#### Equipment

The Drive and Inhibit inputs should be driven with standard ECL levels. If the full performance of the AD1321 needs to be evaluated, the generator must be able to supply an ECL level at frequencies greater than 200 MHz. Motorola's MC10216 is used on the evaluation board to simulate the actual application.  $V_{BB}$ is used on the MC10216 as the logic reference and the outputs have 330 ohm pulldowns to  $V_{\rm EE}$ .

Five power supplies are required: DUT\_V<sub>CC</sub>, DUT\_V<sub>EE</sub>,  $V_{\rm HIGH},\,V_{\rm LOW}$  and ECL\_V\_{EE}. DUT\_V\_{CC} requires  $+\,10$  V at 100 mA minimum; DUT V<sub>EE</sub> requires -5.2 V at 100 mA minimum; ECL\_V<sub>EE</sub> requires -5.2 V at 150 mA minimum. V<sub>HIGH</sub> and V<sub>LOW</sub> require -2 V to +7 V at 5 mA (each).

The output performance of the pin driver can only be measured properly with a scope which has the proper bandwidth for the required application. The input impedance and the bandwidth of the scope probe should be taken into consideration when evaluating the performance of the device. The resultant bandwidth of the system is the RMS value of the components in the svstem.

The characterizations performed by Analog Devices were performed using the following equipment: Tektronix 11402 mainframe (1 GHz BW), P6203 FET probe (1 GHz, 1.2 pF, 1 M ohm) and 11A71 plug-in (1 GHz BW, 50 ohm).

The Hewlett-Packard 54120 and 54110 were also evaluated with 500 ohm, 1.2 pF passive probes and the Data Precision 6100 with their model 640 FET probe (50 k $\Omega$ , 4 pF). When measuring the performance of waveforms close to or exceeding the bandwidth of a scope, it is not uncommon for the results between scopes to be different because of aberrations and slew rates.