# **PCM Interface Controller (PIC)**

**PEB 2052**

#### **Preliminary Data**

**CMOSIC**

| Туре       | Ordering Code | Package        |

|------------|---------------|----------------|

| PEB 2052-C | Q67100-H6059  | C-DIP-40       |

| PEB 2052-N | Q67100-H6060  | PL-CC-44 (SMD) |

| PEB 2052-P | Q67100-H6061  | P-DIP-40       |

The PCM interface controller PEB 2052 is a device for the control of voice, data, and signaling paths of up to 16 subscribers on peripheral component boards in digital telephone systems. In combination with the highly flexible Signal Processing Codec Filter (SICOFI® PEB 2060) it forms an optimized analog subscriber-line board architecture. Its flexibility allows operation as general-purpose controller for data switching and MUX/ De MUX applications.

The PIC controls space and time switching functions between subscriber-line devices and time-division multiplex highways. Further, it controls the flow of information between the subscriber interface ports and a local line card processor.

To meet the different requirements the PIC PEB 2052 provides the following interfaces:

- 8 serial, bidirectional I/O ports for the transfer of voice, data, control, and signaling information between the PBC and codec filters (e.g. SICOFI PEB 2060), digital interface circuits or signal processors.

- Double-constructed PCM interface.

- Bit-parallel interface for the connection of 8-bit standard microcomputers such as the SAB 8051.

The PIC PEB 2052 is pin and software compatible with PEB 2050 and is optimized for applications without an HDLC signaling link. It is fabricated using Siemens ACMOS 3 technology.

#### **Features**

- Board controller for up to 16 subscribers of a digital switching system

- Designed for different PCM systems

- Time-slot assignment freely programmable for all subscribers connected

- Control of voice, data, signaling and line board parameters to minimize hardware requirements and to simplify software

- Provides two full duplex PCM highways for the system interface

- Pin and software compatible with PEB 2050

- Standard uP interface

- μP access to all internal data streams including time-slot oriented data streams

- Support of subscriber circuits by generating timing signals

- Single +5 V power supply

- Advanced CMOS technology

- Low power consumption

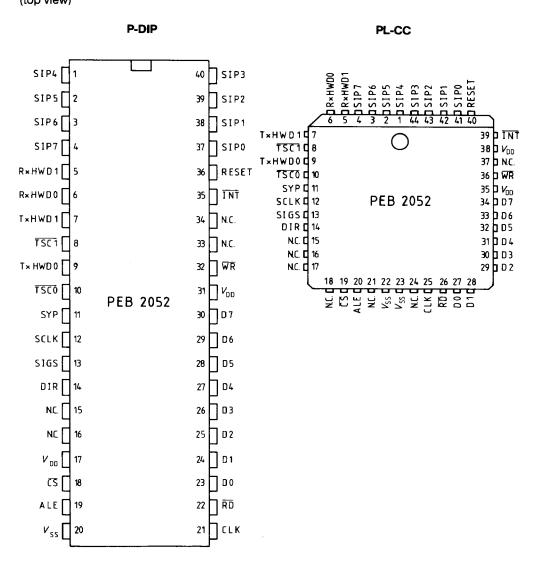

# Pin Configurations (top view)

#### **Pin Definitions and Functions**

| Pin No.<br>PL-CC | Pin No.<br>P-DIP | Symbol          | Name                                                               | Function                                                                                                                                                                                                                                                                                                                                                       |

|------------------|------------------|-----------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 4              | 1 4              | SIP 4           | Subscriber<br>interface port<br>(input/output)                     | These interface ports are used for bi-<br>directional, bit-serial transfer of speech,<br>data and control words to and from<br>the signal processing codec filter<br>(SICOFI) or standard codec. Corre-<br>sponding with the direction signal, the<br>PIC PEB 2052 is transmitting during<br>the high level of DIR within the first half<br>of a 125 µs frame. |

| 5<br>6           | 5<br>6           | R×HWD 1 R×HWD 0 | Receive highway<br>data (input)<br>Receive highway<br>data (input) | Receive PCM highway 1 interface.  Receive PCM highway 0 interface.  The PIC serially receives a PCM word (8 bits) through one of these leads at the programmed time slot.                                                                                                                                                                                      |

| 7                | 7                | TxHWD 1         | Transmit highway data (output)                                     | Output of the transmit side onto the send PCM highway 1 (serial bus). The 8-bit PCM word is serially sent out on this pin at the programmed time slot. Tristate output.                                                                                                                                                                                        |

| 8                | 8                | TSC 1           | Tristate control (output, active low)                              | Normally high, this signal goes low while the PIC is transmitting an 8-bit PCM word on the PCM highway 1.                                                                                                                                                                                                                                                      |

| 9                | 9                | TxHWD 0         | Transmit highway data (output)                                     | Output of the transmit side onto the send PCM highway 0.                                                                                                                                                                                                                                                                                                       |

| 10               | 10               | TSC 0           | Tristate control (output, active low)                              | Tristate control of highway 0.                                                                                                                                                                                                                                                                                                                                 |

| 11               | 11               | SYP             | Synchronization                                                    | SYP is a frame synchronization pulse which resets the on-chip time-slot counters.                                                                                                                                                                                                                                                                              |

| 12               | 12               | SCLK            | Slave clock<br>(output)                                            | Clock output for the peripheral devices. The signals between the codec filter and the PIC are latched and transmitted with the rising edge of SCLK.                                                                                                                                                                                                            |

| 13               | 13               | SIGS            | Signal strobe<br>(output, active<br>high)                          | The SIGS output supplies a programmable strobe signal.                                                                                                                                                                                                                                                                                                         |

## Pin Definitions and Functions (cont'd)

| Pin No.<br>PL-CC | Pin No.<br>P-DIP | Symbol                         | Name                                            | Function                                                                                                                                                                                                               |

|------------------|------------------|--------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14               | 14               | DIR                            | Direction<br>(output, active<br>high)           | DIR is an 8-kHz-symmetric frame signal which controls the direction of data transfer from and to the peripheral devices. The PIC is able to receive data during the low state of DIR.                                  |

| 15               | 15               | N.C.                           |                                                 | Not connected                                                                                                                                                                                                          |

| 16               | 16               | N.C.                           |                                                 | Not connected                                                                                                                                                                                                          |

| 38               | 17               | $V_{\scriptscriptstyle  m DD}$ |                                                 | Power supply: $V_{DD} = 5.0 \text{ V} \pm 0.25 \text{ V}$                                                                                                                                                              |

| 19               | 18               | <u>CS</u>                      | Chip select<br>(input, active low)              | CS is used to address the PIC. A low level at this input enables the PIC to accept commands or data from a µP within a write cycle, or to transmit data during a read cycle.                                           |

| 20               | 19               | ALE                            | Address latch<br>enable (input,<br>active high) | A high level at this input indicates that the data on the external bus is an address selecting one of the PIC-internal sources or destinations. Latching into the address latch occurs during the high-low transition. |

| 22, 23           | 20               | V <sub>ss</sub>                |                                                 | Ground (0 V)                                                                                                                                                                                                           |

| 25               | 21               | CLK                            | Clock<br>(input)                                | A standard TTL clock provides the basic timing of the controller. The clock is synchronous to the PCM clock.                                                                                                           |

| 26               | 22               | RD                             | Read strobe (input, active low)                 | RD is used together with CS to transfer data from the PBC to a μP or memory.                                                                                                                                           |

| 27               | 23               | D0                             |                                                 |                                                                                                                                                                                                                        |

| •                |                  | •                              |                                                 |                                                                                                                                                                                                                        |

|                  |                  |                                | System data bus                                 | The data bus transfers data and com-                                                                                                                                                                                   |

|                  |                  |                                |                                                 | mands between the $\mu P$ or memory and the PIC.                                                                                                                                                                       |

| 34               | 30               | D7                             |                                                 |                                                                                                                                                                                                                        |

| 35               | 31               | V <sub>DD</sub>                | -                                               | Power supply: $V_{DD} = 5.0 \pm 0.25 \text{ V}$                                                                                                                                                                        |

## Pin Definitions and Functions (cont'd)

| Pin No.<br>PL-CC | Pin No.<br>P-DIP | Symbol       | Name                                           | Function                                                                                                                                                                                                                                                                                                                                               |

|------------------|------------------|--------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36               | 32               | WR           | Write strobe<br>(input, active low)            | During the low state of $\overline{WR}$ data can be transferred from the $\mu P$ or memory to the PBC.                                                                                                                                                                                                                                                 |

| 37               | 33<br>34         | N.C.<br>N.C. |                                                | Not connected<br>Not connected                                                                                                                                                                                                                                                                                                                         |

| 39               | 35               | INT          | Interrupt<br>request (output,<br>active low)   | The signal is pulled down, when the PIC is requesting an interrupt. In that case, the µP should enter an interrupt routine for reading status register 1.                                                                                                                                                                                              |

| 40               | 36               | RESET        | Reset (input, active hogh)                     | A high on this input forces the P/C into reset state. The minimum reset pulse is 16 complete clock cycles.                                                                                                                                                                                                                                             |

| 41               | 37               | SIP 0        | Subscriber<br>interface port<br>(input/output) | These interface ports are used for bi-<br>directional, bit-serial transfer of speech,<br>data and control words to and from<br>the Signal Processing Filter (SICOFI)<br>or standard codec. Corresponding<br>with the direction signal, the PIC<br>PEB 2052 is transmitting during the<br>high level of DIR within the first half of a<br>125 µs frame. |

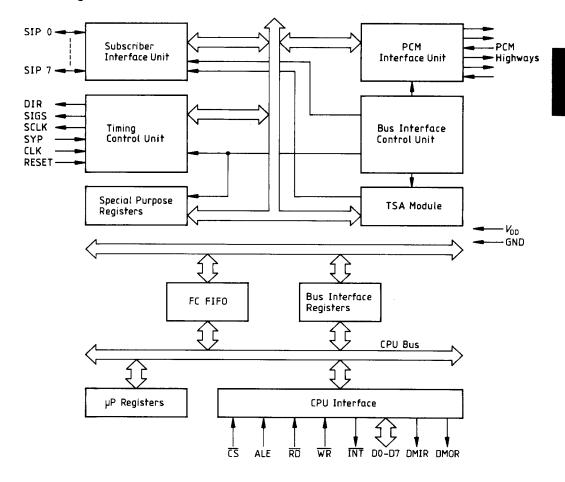

#### **Block Diagram**

#### **Description of the Functional Blocks**

The PIC has been designed especially for use in peripheral subscriber boards, but its functional flexibility also permits its application in various parts of a digital exchange telecommunications system.

Used in peripheral subscriber boards it performs two essential functions:

- Exchange of control data between an on-board processing unit and individual subscriber connections.

- 2) The time-slot controlled transfer of PCM data (64-Kbaud channels) between the PCM highways and the subscriber connections. Data transfers between both parts, such as the access of the on-board µP to 64-Kbaud channels, are considerably simplified by the IC.

## The PIC Consists of the Following Functional Blocks

- Subscriber Interface Unit

- PCM Interface Unit

- TSA Module (Contents-Addressable Memory)

- Timing Control Unit

- µP Interface

- μP Control and Status Register

- Feature Control FIFO (16 byte)

- Bus Interface Register

160

#### **Maximum Ratings**

|                     |                  | Limit | Values |      |

|---------------------|------------------|-------|--------|------|

| Parameter           | Symbol           | min.  | max.   | Unit |

| Storage temperature | T <sub>stg</sub> | -65   | 125    | °C   |

#### Range of Operation

| Operating temperature                 | TA                    | 0    | 70 | °C |

|---------------------------------------|-----------------------|------|----|----|

| Voltage at any pin referred to ground | <b>V</b> <sub>S</sub> | -0.5 | 7  | V  |

| Total power consumption               | P <sub>tot</sub>      |      | 35 | mW |

#### **DC Characteristics**

$T_{\rm A}$  = 0 to 70 °C;  $V_{\rm CC}$  = 5 V ± 0.25 V; GND = 0 V

|                                                                |                 |      | Limit Values |      |      |

|----------------------------------------------------------------|-----------------|------|--------------|------|------|

| Parameter                                                      | Symbol          | min. | typ.         | max. | Unit |

| L-input voltage                                                | V <sub>IL</sub> | -0.5 |              | 0.8  | V    |

| H-input voltage                                                | V <sub>IH</sub> | 2.0  |              | 5.5  | ٧    |

| L-output voltage $I_{\mathrm{OL}} = +1.6 \; \mathrm{mA}$       | V <sub>OL</sub> |      |              | 0.45 | ٧    |

| H-output voltage $I_{\text{OH}} = -400  \mu\text{A}$           | V <sub>OH</sub> | 2.4  |              |      | ٧    |

| Input leakage current V <sub>IN</sub> = V <sub>CC</sub> to 0 V | $I_{IL}$        | -10  |              | 10   | μА   |

| Output leakage current $V_{\text{OUT}} = V_{\text{CC}}$ to 0 V | $I_{OL}$        | -10  |              | 10   | μА   |

| $V_{\rm CC}$ supply current $V_{\rm CC} = 5 \text{ V}$         | I <sub>CC</sub> |      |              | 7    | mA   |

#### Capacitance

$T_{\rm A} = 25\,{\rm ^{o}C}; V_{\rm CC} = {\rm GND} = 0~{\rm V}$

|                                                          |                  |      | Limit Valu | ies  |      |

|----------------------------------------------------------|------------------|------|------------|------|------|

| Parameter                                                | Symbol           | min. | typ.       | max. | Unit |

| Input capacitance  f <sub>C</sub> = 1 MHz                | C <sub>IN</sub>  |      | 5          | 10   | pF   |

| Input/output capacitance                                 | C <sub>1/O</sub> |      | 10         | 20   | pF   |

| Output capacitance<br>unmeasured pins<br>returned to GND | Соит             |      | 8          | 15   | pF   |

#### AC Characteristics

$T_{\rm A} = 0$  to 70 °C;  $V_{\rm CC} = 5$  V  $\pm$  0.25 V; GND = 0 V

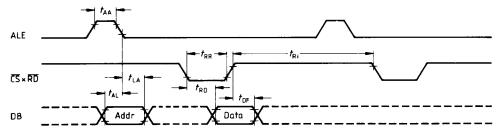

#### Microprocessor Interface Read Cycle

|                        |                 | L    | Limit Values |      |

|------------------------|-----------------|------|--------------|------|

| Parameter              | Symbol          | min. | max.         | Unit |

| Address hold after ALE | t <sub>LA</sub> | 20   |              | ns   |

| Address to ALE setup   | t <sub>AL</sub> | 30   |              | ns   |

| Data delay from RD     | t <sub>RD</sub> |      | 120          | ns   |

| RD pulse width         | t <sub>RR</sub> | 120  |              | ns   |

| Output float delay     | t <sub>DF</sub> |      | 25           | ns   |

| RD control interval    | t <sub>RI</sub> | 80   |              | ns   |

| ALE pulse width        | t <sub>AA</sub> | 60   |              | ns   |

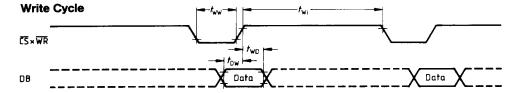

## Write cycle

| WR pulse width      | t <sub>ww</sub> | 100 | ns |

|---------------------|-----------------|-----|----|

| Data setup to WR    | t <sub>DW</sub> | 50  | ns |

| Data hold after WR  | t <sub>WD</sub> | 25  | ns |

| WR control interval | t <sub>WI</sub> | 50  | ns |

## **Read Cycle**

Siemens Components, Inc.

## **Clock Timing**

|                                       |                     | Lim      |                  |      |

|---------------------------------------|---------------------|----------|------------------|------|

| Parameter                             | Symbol              | min.     | max.             | Unit |

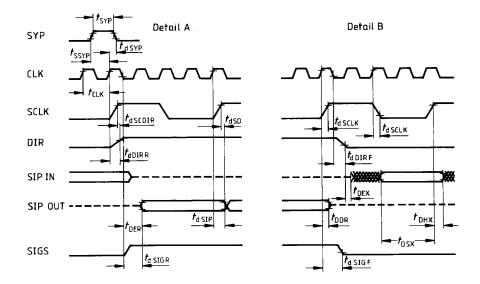

| System Clock                          |                     |          |                  |      |

| System clock frequency                | f <sub>CLK</sub>    |          | 4.2              | MHz  |

| Duty cycle                            |                     | 40       | 60               | %    |

| Sync pulse period                     | t <sub>SPP</sub>    | 125      | N x 125          | μs   |

| Sync pulse width                      | t <sub>SYP</sub>    | 60       | t <sub>CLK</sub> | ns   |

| Pulse delay to CLK                    | t <sub>dSYP</sub>   | 10       |                  | ns   |

| Setup time to CLK                     | t <sub>sSYP</sub>   | 50       |                  | ns   |

| Slave Clock                           |                     |          |                  |      |

| Clock frequency                       | f <sub>SCLK</sub>   | 512      | 512              | kHz  |

| Clock delay time                      | t <sub>dSCLK</sub>  |          | 150              | ns   |

| DIR Clock                             |                     |          |                  |      |

| Delay time to CLK (rising edge)       | t <sub>dDIR R</sub> |          | 150              | ns   |

| Delay time to CLK (falling edge)      | t <sub>dDIR</sub> F |          | 110              | ns   |

| SIU Interface                         |                     |          |                  |      |

| SIP data delay                        | t <sub>dSIP</sub>   |          | 200              | ns   |

| Data enable receive                   | t <sub>DER</sub>    |          | 120              | ns   |

| Data disable receive                  | t <sub>DDR</sub>    |          | 120              | ns   |

| Data enable transmit                  | t <sub>DEX</sub>    | 0        |                  | ns   |

| Data hold transmit                    | t <sub>DHX</sub>    | 0        |                  | ns   |

| Data setup transmit (control data)    | t <sub>DSX</sub>    | CP/2+200 |                  | ns   |

| Data setup transmit                   | t <sub>DSX</sub>    | 100      |                  | ns   |

| Signaling strobe delay (falling edge) | t <sub>DSIG F</sub> |          | 150              | ns   |

| Signaling strobe delay (rising edge)  | t <sub>DSIG R</sub> |          | 150              | ns   |

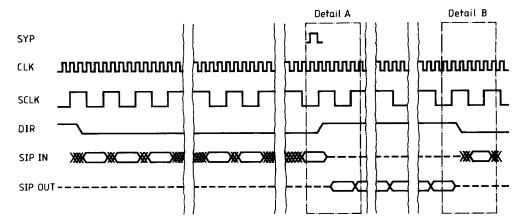

#### **SIP Interface Timing**

## **Serial Port Timing**

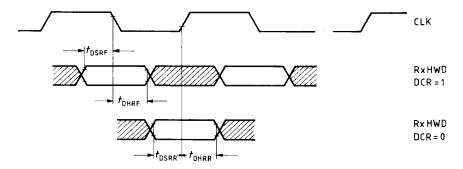

#### **PCM** Interface

|                            |                    | Limit Values |      |      |

|----------------------------|--------------------|--------------|------|------|

| Parameter                  | Symbol             | min.         | max. | Unit |

| Receive Timing             |                    |              |      |      |

| Receive data setup DCR = 1 | t <sub>DSRF</sub>  | 20           |      | ns   |

| Receive data setup DCR = 0 | t <sub>DS RR</sub> | 40           |      | ns   |

| Receive data hold DCR = 1  | t <sub>DH RF</sub> | 40           |      | ns   |

| Receive data hold DCR = 0  | t <sub>DH RR</sub> | 10           |      | ns   |

## **Receive Timing**

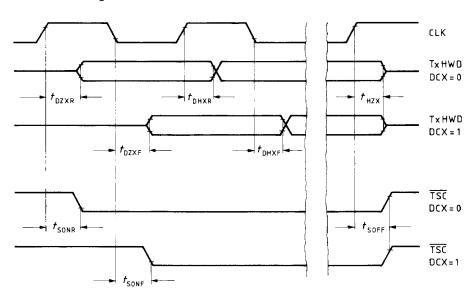

## PCM Interface (cont'd)

| Parameter                     | Symbol            | Limit Values |      |      |                          |

|-------------------------------|-------------------|--------------|------|------|--------------------------|

|                               |                   | min.         | max. | Unit | Test Conditions          |

| Transmit Timing               |                   |              |      |      | e                        |

| Data enable DCX = 0           | t <sub>DZXR</sub> |              | 160  | ns   | C <sub>L</sub> = 200 pF  |

| Data enable DCX = 1           | t <sub>DZXF</sub> |              | 100  | ns   | C <sub>L</sub> = 200 pF  |

| Data hold time DCX = 0        | t <sub>DHXR</sub> |              | 160  | ns   | C <sub>L</sub> = 200 pF  |

| Data hold time DCX = 1        | t <sub>DHXF</sub> |              | 100  | ns   | C <sub>L</sub> = 200 pF  |

| Data float on TS EXIT         | t <sub>HZX</sub>  |              | 80   | ns   | $C_{L} = 150 \text{ pF}$ |

| Time slot x to enable DCX = 0 | t <sub>SONR</sub> |              | 130  | ns   | $C_{L} = 150 \text{ pF}$ |

| Time slot x to enable DCX = 1 | t <sub>SONF</sub> |              | 100  | ns   | C <sub>L</sub> = 150 pF  |

| Time slot x to disable        | t <sub>SOFF</sub> |              | 100  | ns   | C <sub>L</sub> = 150 pF  |

Siemens Components, Inc.

#### **Transmit Timing**

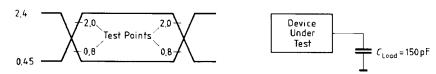

#### **AC Testing Input, Output Waveform**

#### **AC Testing Load Circuit**

AC testing: inputs are driven at 2.4 V for a logic "1" and at 0.45 V for a logic "0". Timing measurements are made at 2.0 V for a logic "1" and at 0.8 V for a logic "0".