#### **Features**

- Master/Slave clock selection in a backplane application

- 160 MHz operation (typical)

- 100ps duty cycle distortion (typical)

- 50ps channel to channel skew (typical)

- 3.3V power supply design

- Glitch-free power on at CLKI/O pins

- Low Power design (16mA @ 3.3V static)

- Accepts small swing (300mV typical) differential signal levels

- Industrial temperature operating range  $(-40^{\circ}\text{C to} + 85^{\circ}\text{C})$

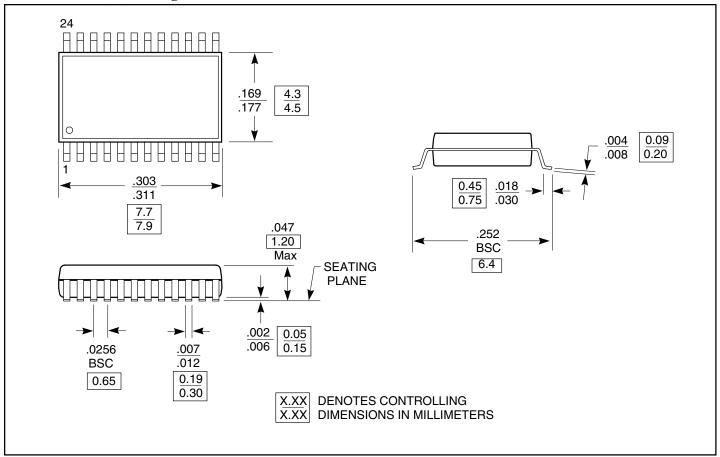

- Available in 24-pin TSSOP Packaging (L)

# 3V Bus LVDS 1-to-6 Clock Buffer/Bus Transceiver

## **General Description**

PI90LVB16 is a six-channel LVTTL clock distribution driver with 50 picosecond channel-to-channel skew. It translates one BLVDS (Bus Low-Voltage Differential Signaling) input signal into six LVTTL-compatible output signals for distribution to adjacent chips on the same board. The PI90LVB16 accepts BLVDS (300mV typical) differential input levels, and translates them to 3V CMOS output levels. The 160MHz PI90LVB16 can be the master clock, driving inputs of other clock I/O pins in a multipoint environment. It can also drive the BLVDS backplane with a separate channel acting as a return/source LVTTL clock source. The master/slave clock selection of the driving source is controlled by the CrdCLK and the  $\overline{\rm DE}$  pins. An output enable pin  $\overline{\rm OE}$ , when high, forces all CLK out pins high. A backplane clock distribution network must be able to drive many

A backplane clock distribution network must be able to drive many transmission line stubs. The Bus LVDS feature of the PI90LVB16 is ideal for driving data transfers in large, high-performance backplane system applications. The device can be used as a source synchronous driver to distribute clock signals within data and telecommunications systems.

#### **Driver Mode Truth Table**

|    | Input |                      |         | Output  |                    |  |

|----|-------|----------------------|---------|---------|--------------------|--|

| ŌĒ | DE    | CrdCLK <sub>IN</sub> | CLKI/O+ | CLKI/O- | CLK <sub>OUT</sub> |  |

| L  | L     | L                    | L       | Н       | L                  |  |

| L  | L     | Н                    | Н       | L       | Н                  |  |

| Н  | L     | L                    | L       | Н       | Н                  |  |

| Н  | L     | Н                    | Н       | L       | Н                  |  |

| Н  | Н     | X                    | Z       | Z       | Н                  |  |

#### **Receive Mode Truth Table**

|    | Output                                                                                                                       |   |                    |   |

|----|------------------------------------------------------------------------------------------------------------------------------|---|--------------------|---|

| ŌĒ | $\overline{\text{DE}}$ $\overline{\text{DE}}$ $\overline{\text{CrdCLK}_{\text{IN}}}$ $\overline{\text{(CLKI/O+)-(CLKI/O-)}}$ |   | CLK <sub>OUT</sub> |   |

| Н  | Н                                                                                                                            | X | X                  | Н |

| L  | Н                                                                                                                            | X | VID ≥ 0.07V        | Н |

| L  | Н                                                                                                                            | X | VID ≤ -0.07V       | L |

L = Low Logic State; H = High Logic State; X = Irrelevant Z = High Impedance

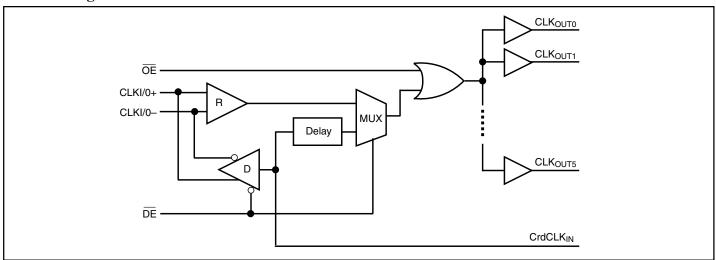

#### **Function Diagram**

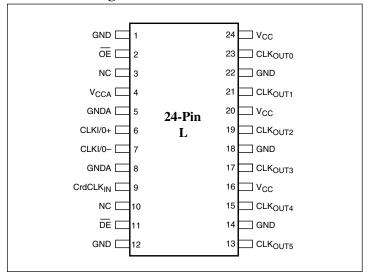

## **Connection Diagram**

# TSSOP Package Pin Description

| Pin Name             | Pin #             | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------|-------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI/O+              | 6                 | I/O    | True (Positive) side of the differential clock input.                                                                                                                                                                                                                                                                                                                                                         |

| CLKI/O-              | 7                 | I/O    | Complementary (Negative) side of the differential clock input.                                                                                                                                                                                                                                                                                                                                                |

| ŌE                   | 2                 | I      | $\overline{OE}$ ; this pin is active Low. When High, this pin forces all CLK <sub>OUT</sub> pin High. When Low, CLK <sub>OUT</sub> pins logic state is determined by either the CrdCLKIN or VID at the CLKI/O pins with respect to the logic level at the $\overline{DE}$ pin. This pin has a weak pullup device to $V_{CC}$ . If $\overline{OE}$ is floating, then all CLK <sub>OUT</sub> pins will be High. |

| DE                   | 11                | I      | $\overline{DE}$ ; this pin is active Low. When Low, this pin enables the CardCLK <sub>IN</sub> signal to the CLKI/O pins and CLK <sub>OUT</sub> . When High the Driver is 3-State, the CLKI/O pins are inputs and determine the state of the CLK <sub>OUT</sub> pins. This pin has a weak pullup device to $V_{CC}$ . If $\overline{DE}$ is floating, then all CLKI/O pins are 3-State.                       |

| CLK <sub>OUT</sub>   | 13,15,17,19,21,23 | О      | Six Buffered clock (CMOS) outputs.                                                                                                                                                                                                                                                                                                                                                                            |

| CrdCLK <sub>IN</sub> | 9                 | I      | Input clock from Card (CMOS level or TTL level).                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>CC</sub>      | 16,20,24          | Power  | $V_{CC}$ ; Analog $V_{CCA}$ (Internally separate from $V_{CC}$ , connect externally or use separate power supplies). No special power sequencing required. Either $V_{CCA}$ or $V_{CC}$ can be applied first, or simultaneously apply both power supplies.                                                                                                                                                    |

| GND                  | 1,12,14,18,22     | Ground | GND                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>CCA</sub>     | 4                 | Power  | Analog $V_{CCA}$ (Internally separate from $V_{CC}$ , connect externally or use separate power supplies). No special power sequencing required. Either $V_{CCA}$ or $V_{CC}$ can be applied first, or simultaneously apply both power supplies.                                                                                                                                                               |

| GNDA                 | 5,8               | Ground | Analog Ground (Internally separate from Ground must be connected externally.                                                                                                                                                                                                                                                                                                                                  |

| NC                   | 3,10              |        | No Connects.                                                                                                                                                                                                                                                                                                                                                                                                  |

2

# ${\bf Absolute\,Maximum\,Ratings}^{(1)}$

| Supply Voltage Range, V <sub>CC</sub> 0.3V to +4V             |

|---------------------------------------------------------------|

| $EnableInputVoltage(DE,OE,CrdCLK_{IN})\\ -0.3Vto+4V$          |

| $Voltage (CLK_{OUT}) \qquad \qquad -0.3V to (V_{CC} + 0.3V)$  |

| $Voltage(CLKI/O\pm) \\ -0.3V to(V_{CC}+0.3V)$                 |

| Driver Short Circuit Current momentary                        |

| Receiver Short Circuit Current momentary                      |

| Maximum Package Power Dissipation at +25°C                    |

| TSSOP Package                                                 |

| Derate TSSOP Package                                          |

| θ <sub>JA</sub> 95°C/W                                        |

| θ <sub>JC</sub> 30°C/W                                        |

| Storage Temperature Range $65^{\circ}$ C to +150 $^{\circ}$ C |

| Lead Temperature Range (Soldering, 4s)                        |

| ESD Ratings: HBM <sup>(2)</sup> 9kV                           |

| $CLK_{OUT(0-5)}$ $\geq 2kV$                                   |

| CDM <sup>(2)</sup> >1000V                                     |

| Machine Model <sup>(2)</sup> >200V                            |

# **Recommended Operating Conditions**

|                                                           | Min.  | Тур. | Max      | Units                   |  |

|-----------------------------------------------------------|-------|------|----------|-------------------------|--|

| Supply Voltage (V <sub>CC)</sub>                          | +3.0  | +3.3 | +3.6     | V                       |  |

| $CrdCLK_{IN}, \overline{DE}, \overline{OE}$ Input Voltage | 0     |      | $V_{CC}$ | V                       |  |

| Operating Free Air Temperature (T <sub>A</sub>            | ) -40 | 24   | +85      | $^{\circ}\! \mathbb{C}$ |  |

3

#### **DC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specificed  $^{(3,4)}$

| Symbol             | Parameter                                                                         | Conditions                                                                                                                                                                                            | Pin                             | Min.                 | Тур. | Max.                            | Units |

|--------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------|------|---------------------------------|-------|

| $V_{TH}$           | Input Threshold High                                                              |                                                                                                                                                                                                       |                                 |                      | 25   | 75                              | ***   |

| V <sub>TL</sub>    | Input Threshold Low                                                               |                                                                                                                                                                                                       |                                 | -70                  | -35  |                                 | mV    |

| VCMR               | Common Mode Voltage<br>Range <sup>(5)</sup>                                       | VID = 250mV peak-to-peak                                                                                                                                                                              | CLKI/O+,<br>CLKI/O–             | V <sub>ID</sub>  /2  |      | 2.8 –<br>  V <sub>ID</sub>   /2 | V     |

| I <sub>IN</sub>    | Input Current                                                                     | $V_{IN} = OV \text{ to } V_{CC}, \overline{DE} = V_{CC}, \overline{OE} = V_{CC},$<br>Other Input = 1.2V ±50mV                                                                                         |                                 | -10                  | ±5   | +10                             | μA    |

| V <sub>OH1R</sub>  | Output High Voltage                                                               | VID =250mV, $I_{OH} = -1.0$ mA                                                                                                                                                                        |                                 | V <sub>CC</sub> -0.2 | 2.9  |                                 |       |

| V <sub>OH2R</sub>  | Output High Voltage                                                               | VID =250mV, $I_{OH} = -6mA$                                                                                                                                                                           |                                 | V <sub>CC</sub> -0.6 | 2.5  |                                 | V     |

| V <sub>OL1R</sub>  | Output Low Voltage                                                                | $I_{OL} = 1.0 \text{mA}, \text{ VID} = -250 \text{mV}$                                                                                                                                                | CLK <sub>OUT</sub>              |                      | 0.04 | 0.1                             | •     |

| V <sub>OL2R</sub>  | Output Low Voltage                                                                | $I_{OL}$ =6mA, VID = -250mV                                                                                                                                                                           | CLKOUT                          | 0                    | 0.22 | 0.4                             |       |

| I <sub>ODHR</sub>  | CLK <sub>OUT</sub> Dynamic                                                        | $VID = +250mV, V_{OUT} = V_{CC}-1V$                                                                                                                                                                   |                                 | -16                  | -24  | -33                             | mA    |

| I <sub>ODLR</sub>  | Output Current <sup>(6)</sup>                                                     | $VID = -250mV, V_{OUT} = 1V$                                                                                                                                                                          |                                 | 14                   | 25   | 36                              |       |

| $V_{\mathrm{IH}}$  | Input High Voltage                                                                |                                                                                                                                                                                                       | DE, OE,                         | 2.0                  |      | V <sub>CC</sub>                 | · V   |

| V <sub>IL</sub>    | Input Low Voltage                                                                 |                                                                                                                                                                                                       | CrdCLK <sub>IN</sub>            | GND                  |      | 0.8                             |       |

| $I_{IH}$           | Input High Current                                                                | $V_{IN} = V_{CC}$ or 2.4V                                                                                                                                                                             | <u> </u>                        | -6                   | 4    | 6                               |       |

| $I_{IL}$           | Input Low Current                                                                 | $V_{IN} = GND \text{ or } 0.4V$                                                                                                                                                                       | OE, DE                          | -20                  | 11   | +20                             | μA    |

| I <sub>INCRD</sub> | Input Current                                                                     | $V_{IN} = 0V$ to $V_{CC}$ , $\overline{OE} = V_{CC}$                                                                                                                                                  | CrdCLK <sub>IN</sub>            | -5                   |      | 5                               |       |

| $V_{CL}$           | Input Voltage Clamp                                                               | $I_{OUT} = -1.5$ mA                                                                                                                                                                                   | OE, DE,<br>CrdCLK <sub>IN</sub> | -0.8                 |      |                                 | V     |

| $I_{CC}$           | No Load Supply<br>Current<br>Outputs Enabled,<br>No VID Applied                   | $\overline{OE} = \overline{DE} = 0V$ ,<br>$CrdCLK_{IN} = V_{CC}$ or GND,<br>$CLKI/O(\pm) = Open$<br>$CLK_{OUT}$ (0:5) = Open Circuit                                                                  |                                 |                      |      | 10                              |       |

| I <sub>CC1</sub>   | No Load Supply<br>Current<br>Outputs Enabled,<br>VID over Common<br>Voltage Range | $\overline{OE}$ = GND, $\overline{DE}$ = V <sub>CC</sub> ,<br>CrdCLK <sub>IN</sub> = V <sub>CC</sub> or GND,<br>VID = 250mV (0.125V VCM 2.275V)<br>CLK <sub>OUT</sub> (0:5) = Open Circuit            | V <sub>CC</sub>                 |                      |      | 6                               | mA    |

| I <sub>CCD</sub>   | Driver Loaded Supply<br>Current                                                   | $\begin{array}{l} \overline{DE} = \overline{OE} = 0V, \\ CrdCLK_{IN} = V_{CC} \text{ or GND,} \\ R_L = 37.5\Omega \text{ between CLKI/O+} \\ and CLKI/O-, CLK_{OUT} (0:5) = Open Circuit \end{array}$ |                                 | 16                   |      | 21                              |       |

4

## DC Electrical Characteristics (continued)

Over Supply Voltage and Operating Temperature ranges, unless otherwise  $specificed^{(3,4)}$

| Symbol                   | Parameter                                                   | Conditions                                                                                                        | Pin      | Min. | Тур. | Max. | Units                  |

|--------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------|------|------|------|------------------------|

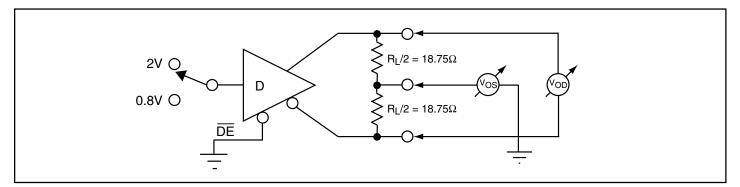

| V <sub>OD</sub>          | Driver Output Differential<br>Voltage                       |                                                                                                                   |          | 250  | 350  | 450  | - mV                   |

| $\Delta V_{\mathrm{OD}}$ | Driver V <sub>OD</sub> Magnitude<br>Change                  |                                                                                                                   |          |      | 2    | 20   | mv                     |

| Vos                      | Driver Offset Voltage                                       | $ \frac{R_L}{DE} = 37.5\Omega, \text{ Figure 5} $ $ \frac{R_L}{DE} = 0V $                                         |          | 1.1  | 1.25 | 1.5  | V                      |

| $\Delta V_{OS}$          | Driver Offset Voltage<br>Multitude Change                   |                                                                                                                   |          |      | 1    | 20   | mV                     |

| $V_{OHD}$                | Driver Output High                                          |                                                                                                                   |          |      | 1.4  | 1.8  | $\bigcup_{\mathbf{V}}$ |

| V <sub>OLD</sub>         | Driver Output Low                                           |                                                                                                                   | CLKI/O+, | 0.8  | 1.05 |      |                        |

| I <sub>OS1D</sub>        | Driver Differential Short<br>Circuit Current <sup>(6)</sup> |                                                                                                                   | CLKI/O-  |      | ±13  | ±17  |                        |

| I <sub>OS2D</sub>        | Driver Differential Short                                   | $CrdCLK_{IN} = GND, \overline{DE} = 0V, CLKI/O+ = V_{CC}$                                                         |          |      | 11   | 17   |                        |

| I <sub>OS3D</sub>        | Circuit Current to V <sub>CC</sub> <sup>(6)</sup>           | $CrdCLK_{IN} = V_{CC}$ , $\overline{DE} = 0V$ , $CLKI/O-=V_{CC}$                                                  |          |      | 10   | 17   | mA                     |

| I <sub>OS4D</sub>        | Driver Differential Short                                   | $CrdCLK_{IN} = V_{CC}, \overline{DE} = 0V, CLKI/O + = 0V$                                                         |          |      | -15  | -17  |                        |

| I <sub>OS5D</sub>        | Circuit Current to GND <sup>(6)</sup>                       | $\overline{\text{CrdCLK}_{\text{IN}} = \text{GND}}, \overline{\text{DE}} = 0\text{V}, \text{CLKI/O-} = 0\text{V}$ |          |      | -15  | -17  |                        |

| I <sub>OFF</sub>         | Power Off Leakage<br>Current                                | $V_{CC} = 0V$ or Open, $V_{APPLIED} = 3.6V$                                                                       |          |      |      | ±20  | μА                     |

## **Switching Characteristics**

#### **Differential Receiver Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specificed (7,8)

| Symbol              | Parameter                                                                            | Conditions    | Min. | <b>Typ.</b> (1) | Max. | Units |

|---------------------|--------------------------------------------------------------------------------------|---------------|------|-----------------|------|-------|

| t <sub>PHLDR</sub>  | Differential Propagation Delay High to Low. CLK <sub>I/O</sub> to CLK <sub>OUT</sub> |               | 1.3  | 2.6             | 3.8  |       |

| t <sub>PLHDR</sub>  | Differential Propagation Delay Low to High. CLK <sub>I/O</sub> to CLK <sub>OUT</sub> |               | 1.3  | 2.6             | 3.8  | ns    |

| t <sub>SK1R</sub>   | Duty Cycle Distortion <sup>(10)</sup> pulse skew,   tPLH - tPHL                      | $C_L = 15pF$  |      | 5               | 400  | ps    |

| t <sub>SK2R</sub>   | Channel-to-Channel Skew; Same Edge(11)                                               | VID = 250mV   |      | 5               | 80   | -     |

| t <sub>SK3R</sub>   | Part-to-Part Skew <sup>(12)</sup>                                                    | Figures 1 & 2 |      |                 | TBD  |       |

| t <sub>TLHR</sub>   | Transition Time Low-to-High <sup>(9)</sup> , (20% to 80%)                            |               | 1.0  | 1.4             | 2.4  |       |

| t <sub>THLR</sub>   | Transition Time High-to-Low <sup>(9)</sup> , (80% to 20%)                            |               | 1.0  | 1.3             | 2.4  | ns    |

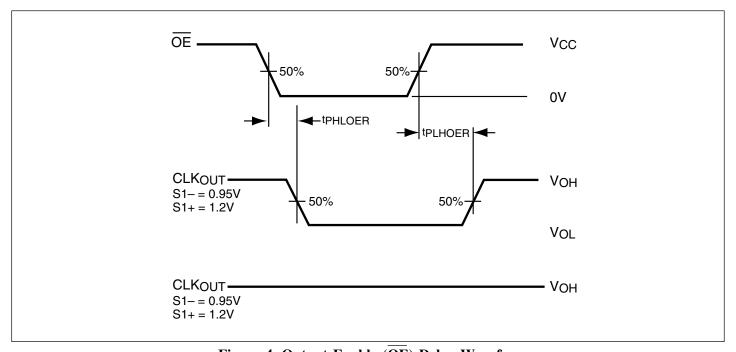

| t <sub>PLHOER</sub> | Propagation Delay Low-to-High (OE to CLK <sub>OUT</sub> )                            | $C_L = 15pF$  | 1.0  | 2.1             | 3.2  |       |

| t <sub>PHLOER</sub> | Propagation Delay High-to-Low (OE to CLK <sub>OUT</sub> )                            | Figures 3 & 4 | 1.0  | 2.1             | 3.2  |       |

| $f_{MAX}$           | Maximum Operating Frequency <sup>(15)</sup>                                          |               | 100  | 160             | ·    | MHz   |

5

#### **Switching Characteristics**

#### **Differential Driver Timing Requuirements**

(Over supply voltage and operating temperature ranges, unless otherwise specificed<sup>(7,8)</sup>

| Symbol              | Parameter                                                                  | Conditions                          | Min. | <b>Typ.</b> (1) | Max. | Units |

|---------------------|----------------------------------------------------------------------------|-------------------------------------|------|-----------------|------|-------|

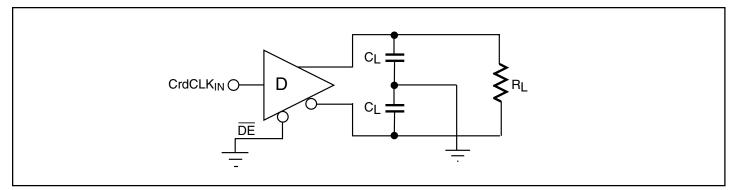

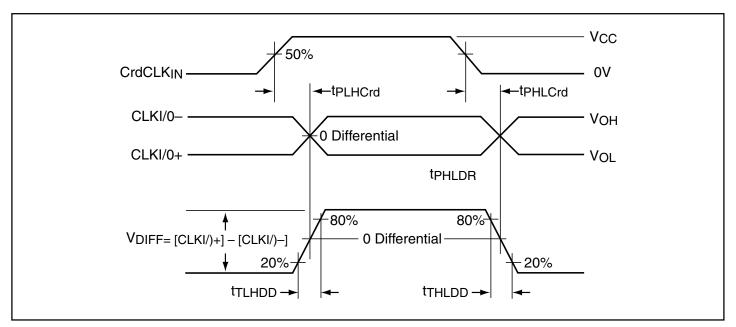

| t <sub>PHLDD</sub>  | Differential Propagation Delay High to Low. CrdCLK <sub>IN</sub> to CLKI/O | $C_L = 15pF$                        | 1.0  | 1.5             | 2.2  |       |

| t <sub>PLHDD</sub>  | Differential Propagation Delay Low to High. CrdCLK <sub>IN</sub> to CLKI/O | $R_L = 37.5\Omega$<br>Figures 6 & 7 | 1.0  | 1.3             | 2.2  | ns    |

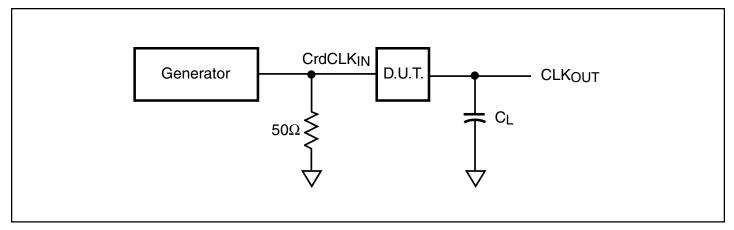

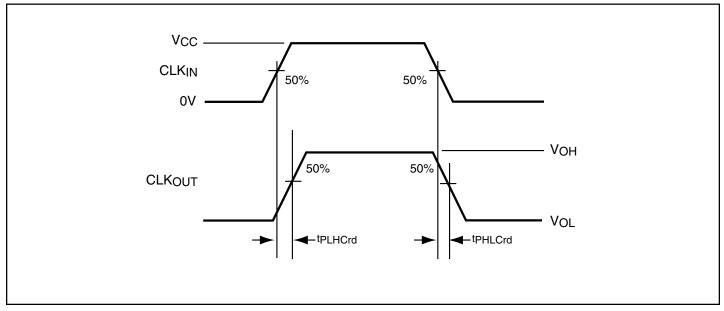

| t <sub>PHLCrd</sub> | CrdCLK <sub>IN</sub> to CLK <sub>OUT</sub> Propagation Delay High to Low   | $C_L = 15pF$                        | 2.0  | 2.8             | 4.5  | 113   |

| t <sub>PLHCrd</sub> | CrdCLK <sub>IN</sub> to CLK <sub>OUT</sub> Propagation Delay Low to High   | Figures 8 & 9                       | 2.0  | 2.8             | 4.5  |       |

| t <sub>SK1D</sub>   | Differential Skew   t <sub>PLH</sub> - t <sub>PHL</sub>   (13)             |                                     |      |                 | 600  | ps    |

| t <sub>SK2D</sub>   | Differential Part-to-Part Skew <sup>(14)</sup>                             | $C_L = 15pF$                        |      |                 | TBD  |       |

| t <sub>TLHD</sub>   | Differential Transition Time <sup>(9)</sup> , (20% to 80%)                 | Figures 6 & 7                       | 0.2  | 0.35            | 0.65 |       |

| t <sub>THLD</sub>   | Differential Transition Time <sup>(9)</sup> , (80% to 20%)                 |                                     | 0.2  | 0.35            | 0.65 |       |

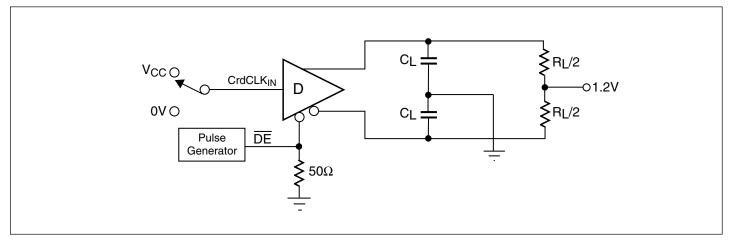

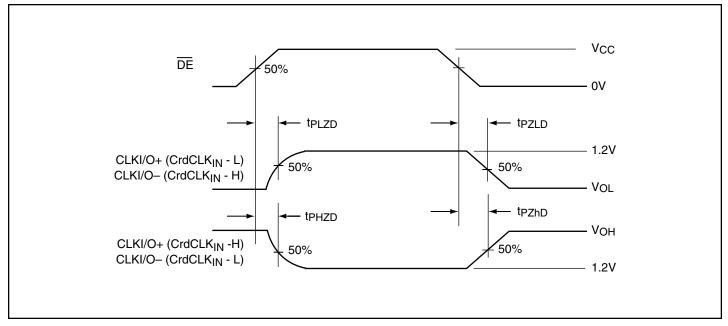

| t <sub>PHZD</sub>   | Transition Time Low to 3-State. $\overline{DE}$ to CLKI/O                  | $V_{IN} = 0V$ to $V_{CC}$           |      |                 | 2.6  | ns    |

| t <sub>PLZD</sub>   | Transition Time Low to 3-State. $\overline{DE}$ to CLKI/O                  | $C_L = 15pF$                        |      |                 | 2.6  |       |

| t <sub>PZHD</sub>   | Transition Time 3-State-to-High. $\overline{\rm DE}$ to CLKI/O             | $R_L = 37.5\Omega$                  |      |                 | 4.3  |       |

| t <sub>PZLD</sub>   | Transition Time 3-State-to-Low. $\overline{DE}$ to CLKI/O                  | Figures 10 & 11                     |      |                 | 3.6  |       |

| $f_{MAX}$           | Maximum Operating Frequency <sup>(15)</sup>                                |                                     | 100  | 160             |      | MHz   |

#### **Notes:**

- 1. "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. These ratings are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

- 2. ESD Rating: ESD qualification is performed per the following: HBM (1.5kΩ, 100pF), Machine Model (250V, 0Ω), IEC 1000-4-2. All V<sub>CC</sub> pins connected together, all ground pins connected together.

- 3. Current into device pins are defined as positive. Current out of device pins defined as negative. All voltages are referenced to ground except VID, VOD, VTH, and VTL

- 4. All typicals are given for:  $V_{CC} = +3.3V$  and  $T_A = +25$ °C.

- 5. The VCMR range is reduced for larger VID. Example: If VID=400 mV, then VCMR is 02V to 2.2VAVID up to  $|V_{CC}-0V|$  may be applied between the CLKI/O+ and CLKI/O- inputs, with the Common Mode set to  $V_{CC}/2$ .

- 6. Only one output should be momentarily shorted at a time. Do not exceed package power dissipation rating.

- 7. C<sub>L</sub> includes probe and fixture capacitance.

- 8. Generator waveform for all tests unless otherwise specified: f = 25 MHz,  $Zo = 50\Omega$ ,  $t_r = 1$ ns,  $t_f = 1$ ns (10%–90%). To ensure fastest propagation delay and minimum skew, clock input edge rates should not be slower than 1ns/V; control signals not slower than 3ns/V. In general, the faster the input edge rate, the better the AC performance,

- 9. All device output transition times are based on characterization measurements and are guaranteed by design.

- 10. t<sub>SKIR</sub> is the difference in receiver propagation delay |t<sub>PLH</sub>-t<sub>PHL</sub>| of one device, and is the duty cycle distortion of the output at any given temperature and V<sub>CC</sub>. The propagation delay specification is a device-to-device worst case over process, voltage and temperature.

- 11.  $t_{SK2R}$  is the difference in receiver propagation delay between channels in the same device of any outputs switching in the same direction. This parameter is guaranteed by design and characterization.

- 12. t<sub>SK3R</sub> part-to-part skew, is the difference in receiver propagation delay between devices of any outputs switching in the same direction. This specification applies to devices over recommended operating temperature and voltage ranges, and across process distribution. t<sub>SK3R</sub> is defined as Max-Min differential propagation delay. This parameter is guaranteed by design and characterization.

- 13. t<sub>SK1D</sub> is the difference in driver propagation delay t<sub>PLH</sub>-t<sub>PHL</sub> and is the duty cycle distortion of the CLKI/O outputs.

- 14. t<sub>SK2D</sub> part-to-part skew, is the difference in driver propagation delay between devices of any outputs switching in the same direction. This specification applies to devices over recommended operating temperature and voltage ranges, and across process distribution. t<sub>SK2D</sub> is defined as Max-Min differential propagation delay.

6

15. Generator input conditions:  $t_r t_f < 1 ns$ , 50% duty cycle, differential (1.10V to 1.35V pk-pk). Output Criteria: 60%/40% duty cycle,  $V_{OL}(max)$  0.4V,  $V_{OH}(min)$  2.7V, Load - 7pF (stray plus probes).

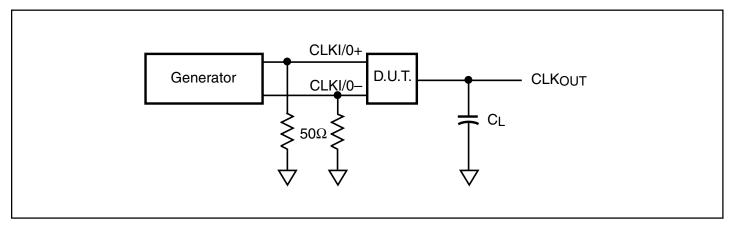

Figure 1. Receiver Propagation Delay and Transition Time Test Circuit

Figure 2. Receiver Propagation Delay and Transition Time Waveforms

7

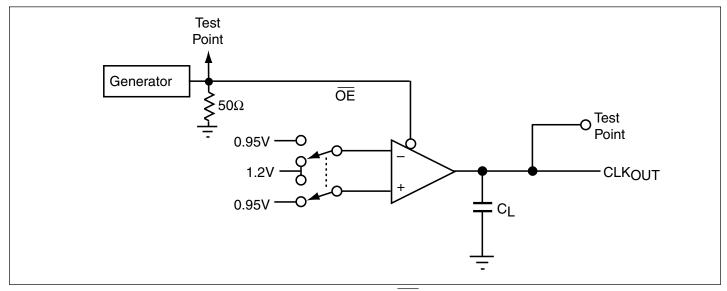

Figure 3. Output Enable (OE) Test Circuit

Figure 4. Output Enable (OE) Delay Waveforms

Figure 5. Differential Driver DC Test

Figure 6. Driver Propagation Delay Test Circuit

Figure 7. Driver Propagation Delay and Transition Time Waveforms

Figure 8. CrdCLK<sub>IN</sub> Propagation Delay Time Test Circuit

Figure 9. CrdCLK<sub>IN</sub> Propagation Delay Time Waveforms

Figure 10. Driver 3-State Test Circuit

Figure 11. Driver 3-State Waveforms

11

## 24-Pin TSSOP (L) Package

## **Ordering Information**

| Ordering Code | Package Name | Package Type | Operating Range |

|---------------|--------------|--------------|-----------------|

| PI90LVB16L    | L24          | 24-pin TSSOP | −40°C to 85°C   |

**Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com 12