# 12.5 MIPS DSP Microprocessor

/NOSTP=21100//NDSTP=21100V

#### **FEATURES**

Pin- and Code-Compatible DSP Microprocessors

ADSP-2100, 6.144MHz and 8.192MHz

ADSP-2100A, 10.24MHz and 12.5MHz

Separate Program and Data Buses, Extended Off-Chip

Single-Cycle Direct Access to 16K×16 of Data Memory

Single-Cycle Direct Access to 32K×24 of Program

Memory

Dual Purpose Program Memory for Both Instruction

and Data Storage

Three Independent Computational Units: ALU,

Multiplier/Accumulator and Barrel Shifter

Two Independent Data Address Generators

Powerful Program Sequencer

Internal Instruction Cache

Provisions for Multiprecision Computation and

Saturation Logic

Single-Cycle Instruction Execution

Multifunction Instructions

Four External Interrupts

80ns Cycle Time (ADSP-2100A)

790mW Maximum Power Dissipation (ADSP-2100A,

J and K Grades)

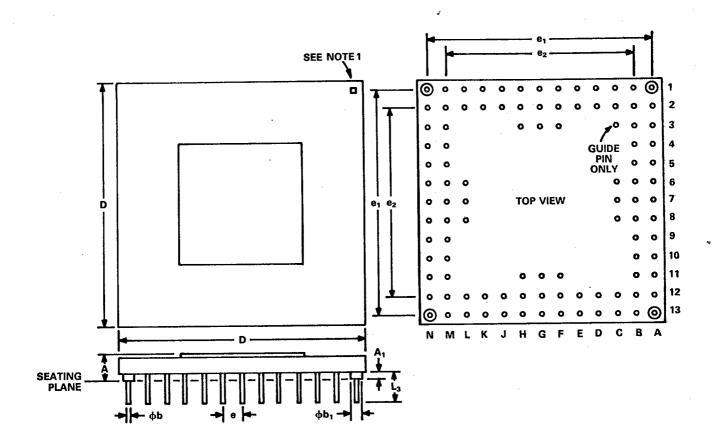

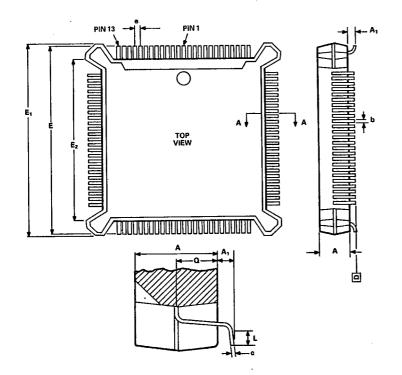

100-Pin Grid Array, 100-Lead PQFP (JEDEC Style),

APPLICATIONS

Optimized for DSP Algorithms Including

Digital Filtering

Fast Fourier Transforms

Applications Include

Image Processing

Radar, Sonar

Speech Processing

# **GENERAL DESCRIPTION**

**Telecommunications**

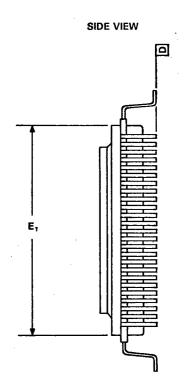

100-Lead CQFP

The ADSP-2100 and ADSP-2100A are pin- and code-compatible single-chip microprocessors optimized for digital signal processing (DSP) and other high-speed numeric processing applications. The ADSP-2100 and ADSP-2100A are both fabricated in a low-power double-layer metal CMOS process. Together, they offer a span of performance from 6MHz to 12.5MHz. All descriptions of the ADSP-2100 in the text of this data sheet refer to both the ADSP-2100A and the ADSP-2100 versions since they have identical architectures and instruction sets. Timing and electrical specifications differ as shown in those sections of the data sheet.

Both processors integrate computational units, data address generators and a program sequencer in a single device. The ADSP-2100 architecture makes efficient use of external memories for program and data storage, freeing silicon area for increased

processor performance. The resulting processor combines the functions and performance of a bit-slice/building block system with the ease of design and development support of a general purpose microprocessor.

The ADSP-2100A (K grade) operates at 12.5MHz. Every instruction executes in a single 80ns cycle. The ADSP-2100A (J and K grades) dissipates less than 790mW while the ADSP-2100 dissipates less than 475mW.

The ADSP-2100's flexible architecture and comprehensive instruction set support a high degree of operational parallelism. Because all instructions execute in a single cycle, MHz=MIPS. In one cycle the ADSP-2100 can:

- generate the next program address

- fetch the next instruction

- perform one or two data moves

- update one or two data address pointers

- perform a computational operation.

#### **DEVELOPMENT SYSTEM**

The ADSP-2100 and ADSP-2100A are supported by a complete set of tools for software and hardware system development. The Cross-Software System provides a System Builder for defining the architecture of simulated systems under development, an Assembler, a Linker and a interactive Simulator. An ANSI (draft) Standard C Compiler supports program development in this widely used programming language, producing ADSP-2100 Assembly code which may be assembled, linked and simulated with the other development system tools. A PROM Splitter generates PROM burner compatible files. An In-Circuit Emulator is available for hardware debugging.

An Evaluation Board is available for quick assessment of actual processor performance in a prepackaged hardware environment.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way; P. O. Box 9106; Norwood, MA 02062-9106 U.S.A.

Tel: 617/329-4700 Twx: 710/394-6577

Telex: 924491 Cables: ANALOG NORWOODMASS

#### ADDITIONAL INFORMATION

For additional information on the architecture and instruction set of the processor, refer to the ADSP-2100 User's Manual. For more information about programming and the Development System, refer to the ADSP-2100 Cross-Software Manual and the ADSP-2100 Emulator Manual. For examples of applications routines, refer to the ADSP-2100 Applications Handbook, Volume 1, 2 or 3. Manuals are available only from your local Analog Devices sales office. There is also a quarterly newsletter, DSPatch<sup>TM</sup>, supporting Analog Devices' digital signal processing customers.

#### ARCHITECTURE OVERVIEW

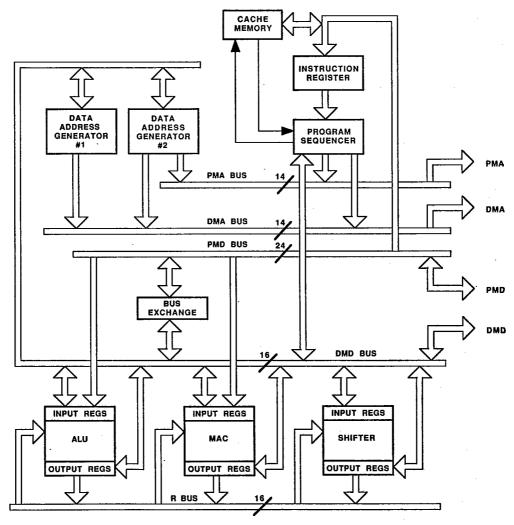

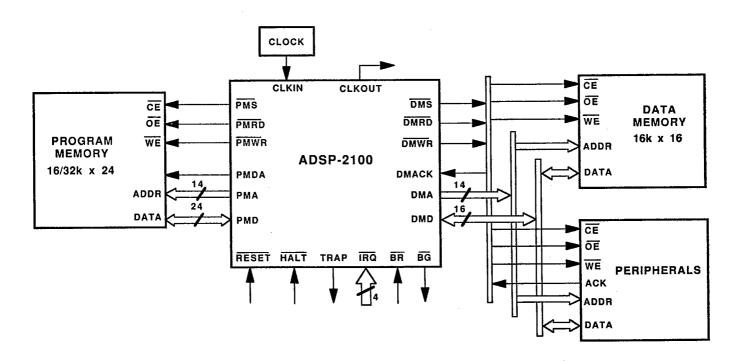

Figure 1 is an overall block diagram of the ADSP-2100. The processor contains three independent computational units: the ALU, the multiplier/accumulator (MAC) and the Shifter. The computational units process 16-bit data directly and have provisions to support multiprecision computations. The ALU performs a standard set of arithmetic and logic operations; division primitives are also supported. The MAC performs single-cycle multiply, multiply/add and multiply/subtract operations. The Shifter performs logical and arithmetic shifts, normalization, denormalization and derive exponent operations. The Shifter can be used to efficiently implement any degree of numeric format control, up to and including full floating point representations. The computational units are arranged side-by-side instead of serially for flexible operation sequencing. The internal result (R) bus

directly connects the computational units so that the output of any unit may be the input of any unit on the next cycle.

A powerful program sequencer and two dedicated data address generators ensure efficient use of these computational units. The program sequencer generates the next instruction address. To minimize overhead cycles, the sequencer supports conditional jumps, subroutine calls and returns in a single cycle. With internal loop counters and loop stacks, the ADSP-2100 executes looped code with zero overhead; no explicit jump instructions are required to maintain the loop.

The data address generators (DAGs) handle address pointer updates. Each DAG keeps track of up to four address pointers. Whenever the pointer is used to access external data (indirect addressing), it is modified by a prespecified value. A length value may be associated with each pointer to implement automatic modulo addressing for circular buffers. With two independent DAGs, the processor can generate two addresses simultaneously for dual operand fetches.

Efficient data transfer is achieved with the use of five internal buses.

- Program Memory Address (PMA) bus

- Program Memory Data (PMD) bus

- Data Memory Address (DMA) bus

- Data Memory Data (DMD) bus

- Result (R) bus

Figure 1. ADSP-2100 Block Diagram

The program memory (PMD, PMA) buses and data memory (DMA, DMD) buses extend off-chip to provide direct connections to external memories. The DMD bus is the primary bus for routing data internally and to/from external data memory. The 14-bit DMA bus provides direct addressing of  $16K \times 16$  of external memory. Although the primary function of the program memory is for storing instructions, it can also store data. In this case, the PMD bus provides a path for routing data to/from program memory, permitting dual operand fetches. The 14-bit PMA bus provides direct addressing of  $16K \times 24$  of external memory, expandable to  $32K \times 24$  by using the program memory data access (PMDA) signal as the 15th address line.

When a data fetch from program memory is required, an extra memory cycle is automatically appended to enable the next instruction fetch. To avoid this extra cycle, the ADSP-2100 has an internal instruction cache (16 instructions deep) which serves as an alternate source for the next instruction. The cache monitor circuit transparently determines when the cache contents are valid. When the next instruction is in the cache, no extra cycle is necessary.

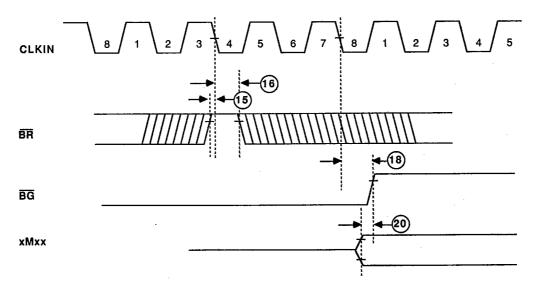

The data memory interface supports slower memories and memory-mapped peripherals with wait states. The data memory acknowledge (DMACK) signal provides the necessary handshake. External devices can gain control of program or data buses independently with bus request/grant signals (BR, and BG).

The ADSP-2100 can respond to four external interrupts, which are internally prioritized, maskable and independently programmable as either edge- or level-sensitive. Additional external controls are provided by the  $\overline{RESET}$ ,  $\overline{HALT}$  and  $\overline{TRAP}$  signals. With both  $\overline{BR}$  and  $\overline{RESET}$  recognized, the ADSP-2100 idles, consuming the least possible current.

The ADSP-2100 instruction set provides flexible data moves and multifunction (data moves with a computation) instructions. Every instruction can be executed in a single processor cycle. The ADSP-2100 assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools supports program development.

A pin description and detailed discussion of each section of the ADSP-2100 follows.

# Pin Description

This section summarizes the pin description of the processor by interface. In this data sheet, when groups of pins are identified with subscripts, as in  $PMD_{23-0}$ , the highest numbered pin  $(PMD_{23})$  is the MSB.

| Pin Name               | Туре           | Function                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks:                |                |                                                                                                                                                                                                                                                                                                                                                                                   |

| CLKIN                  | Input          | Master input clock operating at four times the processor instruction rate. Nominally 50% duty cycle. The phases of CLKIN define the eight internal processor states making up one instruction cycle.                                                                                                                                                                              |

| CLKOUT                 | Output         | Output clock operating at the processor instruction rate with a 50% duty cycle. Synchronized to the internal processor states.                                                                                                                                                                                                                                                    |

| Interrupt Re           | quest Lines:   |                                                                                                                                                                                                                                                                                                                                                                                   |

| $\overline{IRQ}_{3-0}$ | Input          | Interrupt Request lines that may be either edge triggered or level sensitive. Interrupts are prioritized and individually maskable.                                                                                                                                                                                                                                               |

| Control Inte           | rface:         |                                                                                                                                                                                                                                                                                                                                                                                   |

| RESET                  | Input          | Master Reset must be asserted long enough to assure proper reset. When RESET is released, execution begins at program memory location 0004.                                                                                                                                                                                                                                       |

| HALT                   | Input          | Used to halt the processor. All control signals become inactive and the address and data buses are driven for observation.                                                                                                                                                                                                                                                        |

| TRAP                   | Output         | Used to indicate the execution of a TRAP instruction. Remains asserted until HALT is asserted by an external device.                                                                                                                                                                                                                                                              |

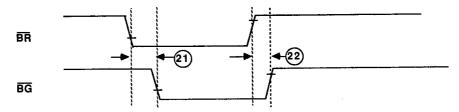

| BR                     | Input          | Bus Request used by an external device to request control of the program and data memory interface. Upon receiving BR the processor halts execution at the completion of the current cycle and relinquishes the program and data memory interface by tristating PMA, PMD, PMS, PMWR, PMRD, PMDA, DMA, DMD, DMS, DMRD and DMWR. The processor regains control when BR is released. |

| BG                     | Output         | Bus Grant. Acknowledges a bus request $(\overline{BR})$ , indicating that the external device may take control. $\overline{BG}$ is held asserted until $\overline{BR}$ is released.                                                                                                                                                                                               |

| Program Me             | mory Interface |                                                                                                                                                                                                                                                                                                                                                                                   |

| DMA                    | Outnut         | Program Mamory Address Pust triotstad when RG is asserted                                                                                                                                                                                                                                                                                                                         |

| $PMA_{13-0}$ | Output        | Program Memory Address Bus; tristated when BG is asserted.                                                                                                                                                                                                                                                          |

|--------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $PMD_{23-0}$ | Bidirectional | Program Memory Data Bus; tristated when $\overline{BG}$ is asserted.                                                                                                                                                                                                                                                |

| PMS          | Output        | Program Memory Select signals a program memory access on the PM interface. Usable as a chip select signal for external memories. Remains asserted on successive program memory accesses. HI only when the processor is halted or after execution of a TRAP instruction. Tristated when $\overline{BG}$ is asserted. |

#### **Program Memory Interface:**

Output

| <b>PMRD</b> | Output | Program Memory Read indicates a read operation on the PM interface. Also usable as a read strobe or output enable signal. Tristated when $\overline{BG}$ is asserted. |

|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>PMWR</b> | Output | Program Memory Write establishes the direction of data transfer on the PM interface. Also usable                                                                      |

Program Memory Data Access used to distinguish instruction and data fetches from PM. Asserted high when data, as opposed to instruction, are accessed. Also usable as a fifteenth PM address bit.

Tristated when  $\overline{BG}$  is asserted.

#### Data Memory Interface:

**PMDA**

| $DMA_{13-0}$ | Output        | Data Memory Address Bus; tristated when BG is asserted.                                   |

|--------------|---------------|-------------------------------------------------------------------------------------------|

| $DMD_{15-0}$ | Bidirectional | Data Memory Data Bus; tristated when BG is asserted.                                      |

| DMS          | Output        | Data Memory Select signals a Data Memory Access on the Data Memory interface. Usable as a |

chip select signal for external memories. Remains asserted on successive data memory accesses. HI only when the processor is halted or after execution of a TRAP instruction. Tristated when BG is asserted.

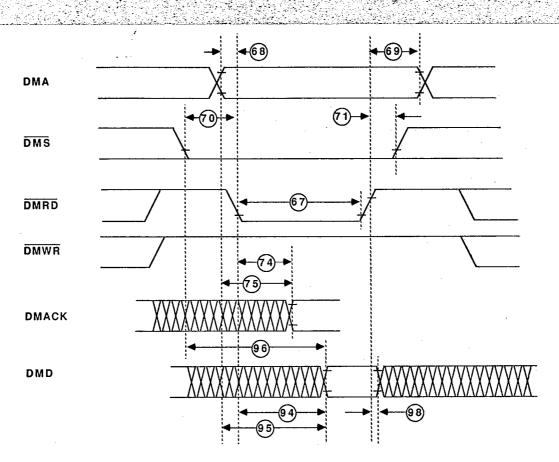

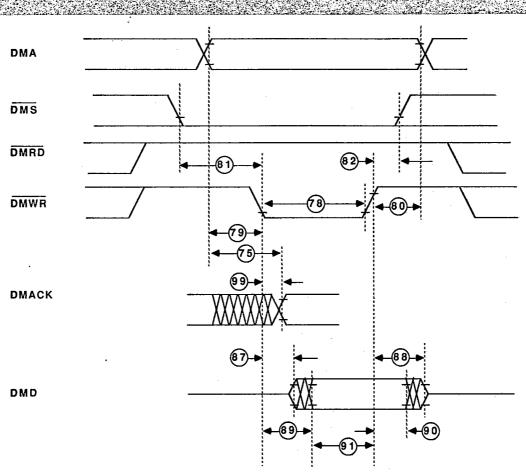

Data Memory Read indicates a read operation on the Data Memory interface. Also usable as a DMRD Output read strobe or output enable signal. Tristated when  $\overline{BG}$  is asserted.

Data Memory Write indicates a write operation on the Data Memory interface. Also usable as a

write strobe. Tristated when  $\overline{BG}$  is asserted.

Data Memory Acknowledge signal used for asynchronous transfers across the DM interface. Indicates that data memory or memory-mapped peripherals are ready for data transfer. If DMACK is not

asserted when checked by the processor, wait states are automatically generated until DMACK is

asserted.

Output

Input

#### Supply Rails:

**DMWR**

DMACK

| $V_{DD}$ | Supply | Power supply rail nominally $+5$ VDC. There are four $V_{\rm DD}$ pins. |

|----------|--------|-------------------------------------------------------------------------|

| GND      | Ground | Power supply return. There are nine GND pins.                           |

PMD BUS 16 (UPPER) DMD BUS MUX AX REGISTERS AY REGISTERS 2 x 16 MUX MUX AF REGISTER ALU MUX REGISTER R . BUS

Figure 2. ALU Block Diagram

# Arithmetic/Logic Unit

Figure 2 shows a block diagram of the Arithmetic/Logic Unit (ALU).

The ALU provides a standard set of general purpose arithmetic

and logic functions: add, subtract, negate, increment, decrement, absolute value, AND, OR, Exclusive OR and NOT. Two divide primitives are also provided to facilitate division. The ALU takes two 16-bit inputs, X and Y, and generates one 16-bit output, R. It accepts the carry (AC) bit in the arithmetic status register (ASTAT) as the carry-in (CI) bit. The carry-in feature enables multiprecision computations. Six arithmetic status bits are generated: AZ (zero), AN (negative), AV (overflow), AC (carry), AS (sign) and AQ (quotient). These status bits are latched in ASTAT.

The X input port can be fed by either the AX register file or any result registers on the R-bus (AR, MR0, MR1, MR2, SR0, or SR1). The AX register file contains two registers, AX0 and AX1. The AX registers can be loaded from the DMD bus. The Y input port can be fed by either the AY register file or the ALU feedback (AF) register. The AY register file contains two registers, AYO and AY1. The AY registers can be loaded from either the DMD bus or the PMD bus.

The register file outputs are dual ported so that one register can drive the ALU input while either one simultaneously drives the DMD bus. The ALU output can be latched in either the AR register or the AF register.

The AR register has a saturation capability; it can automatically output plus or minus the maximum value if an overflow or underflow occurs. The saturation mode is enabled by a bit in the mode status register (MSTAT). The AR register can drive both the R-bus and the DMD bus and can be loaded from the DMD bus.

The ALU contains a duplicate bank of registers shown in Figure 2 as a "shadow" behind the primary registers. The secondary set contains all the registers described above (AX0, AX1, AY0, AY1, AF, AR). Only one set is accessible at a time. The two sets of registers allow fast context switching for interrupt servicing. The active set is determined by a bit in MSTAT.

T-49-17-16

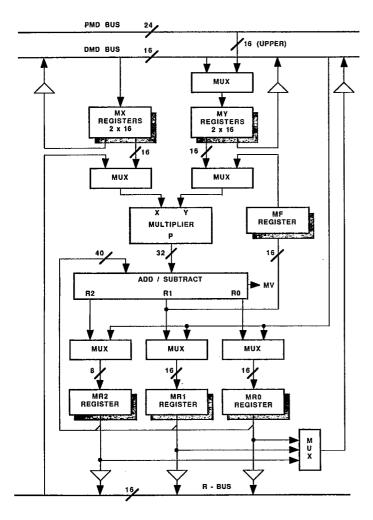

# Multiplier/Accumulator

The multiplier/accumulator (MAC) implements high-speed multiply, multiply/add and multiply/subtract operations. Figure 3 shows a block diagram of the MAC section.

Figure 3. MAC Block Diagram

The multiplier takes two 16-bit inputs, X and Y, and generates one 32-bit output, P. The 32-bit output is routed to a 40-bit accumulator which can add or subtract the P output from the value in MR. MR is a 40-bit register which is divided into three sections: MR0 (bits 0-15), MR1 (bits 16-31), and MR2 (bits 32-39). The result of the accumulator is either loaded into the MR register or into the 16-bit MAC feedback (MF) register. The multiplier accepts the X and Y inputs in either signed or unsigned formats. The result is shifted one bit to the left automatically to remove the redundant sign bit for fractional justification. The accumulator generates one status bit, MV, which is set when the accumulator result overflows the 32-bit boundary. A saturate command is available to change the content of the MR register to the maximum or minimum 32-bit value when MV is set. The accumulator also has the capability for rounding the 40-bit result at the boundary between bit 15 and bit 16.

The MAC and ALU registers are similar. The X input port can be fed by either the MX register file (MX0, MX1) or any result registers on the R-bus (AR, MR0, MR1, MR2, SR0 or SR1).

The MX register file is readable and loadable from the DMD bus and has dual-ported outputs.

The Y input port can be fed by either the MY register file (MY0, MY1) or the MF register. The MY register file is readable from the DMD bus and readable and loadable from both the DMD and the PMD bus. Its outputs are dual ported.

The accumulator output can be latched in either the MR register or the MF register. The MR register is connected to both the R-bus and the DMD-bus. Like the ALU section, the MAC section contains two complete banks of registers (MX0, MX1, MY0, MY1, MF, MR0, MR1, MR2) to allow fast context switching.

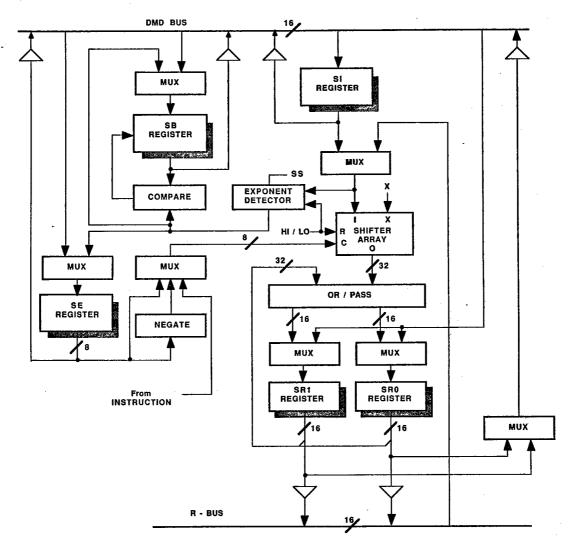

#### Shifter

The Shifter gives the ADSP-2100 its unique capability to handle data formatting and numeric scaling. Figure 4 shows a block diagram of the Shifter.

The Shifter can be divided into the following components: the shifter array, the OR/PASS logic, the exponent detector and the exponent compare logic. These components give the Shifter its six basic functions: arithmetic shift, logical shift, normalization, denormalization, derive exponent and derive block exponent.

The shifter array is a 16×32-barrel shifter. It accepts a 16-bit input and can place it anywhere in the 32-bit output field, from off-scale right to off-scale left. The Shifter can perform arithmetic shifts (shifter output is sign-extended to the left) or logical shifts (shifter output is zero-filled to the left). The placement of the 16-bit input is determined by the control code (C) and the HI/LO reference signal. The control code can come from one of three sources: directly from the instruction (immediate arithmetic or logical shift), from the SE register (denormalization) or the negated value of the SE register (normalization). The shifter input can come from either the 16-bit SI register or any result register on the R-bus. The 32-bit output of the shifter array is fed to the OR/PASS circuit. The result can be either logically OR-ed with the current contents of the SR register or passed directly to the SR register. The SR register is divided into two 16-bit sections: SR0 (bits 0-15) and SR1 (bits 16-31).

The shifter input is also routed to the exponent detector circuitry. The exponent detector generates a value to indicate how many places the input must be up-shifted to eliminate all but one of the sign bits. This value is effectively the base 2 exponent of the number. The result of the exponent detector can be latched into the SE register (for a normalize operation) or can be sent to the exponent compare logic. The exponent compare logic compares the derived exponent with the value in the SB register and updates the SB register only when the derived exponent value is larger than the current value in the SB register. Therefore, the exponent compare logic can be used to find the largest exponent value in an array of shifter inputs.

The Shifter includes the following registers: the SI register, the SE register, the SB register and the SR register. All these registers are readable and loadable from the DMD-bus. The SR register can also drive the R-bus. Like the ALU and MAC, the Shifter contains two complete banks of registers for context switching. Each set contains all the registers described above, but only one set is accessible at a time. The active set is determined by a bit in MSTAT.

Figure 4. Shifter Block Diagram

#### **Data Address Generators**

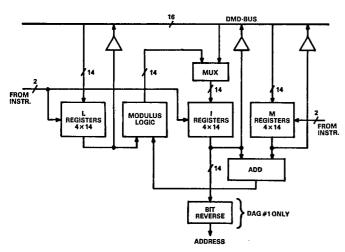

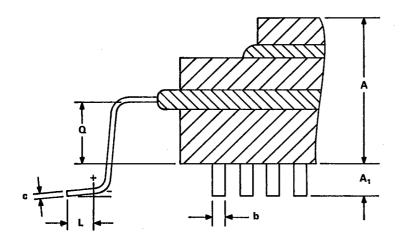

Figure 5 shows a block diagram of a data address generator.

The data address generators (DAGs) provide indirect addressing for data stored in external memories. The processor contains two independent DAGs so that two data operands (one in program memory and one in data memory) can be addressed simultaneously. The two data address generators are identical except that DAG1 has a bit reversal option on the output and can only generate

Figure 5. Data Address Generator

data memory addresses, while DAG2 can generate both program and data memory addresses but has no bit reversal capability.

There are three register files in each DAG: the modify (M) register file, the indirect (I) register file, and the length (L) register file. Each of these register files contain four 14-bit registers which are readable and loadable from the DMD-bus. The I registers hold the actual addresses used to access external memory. When using the indirect addressing mode, the selected I register content is driven onto either the PMA or DMA bus. This value is post-modified by adding the content of the selected M register. The modified address is passed through the modulus logic. Associated with each I register is an L register which may contain the length of the buffer addressed by the I register. The L register and the modulus logic together enable circular buffer addressing with automatic wrap around at the buffer boundary. The modulus logic is disabled by setting the length of the associated buffer to zero.

# Program Sequencer

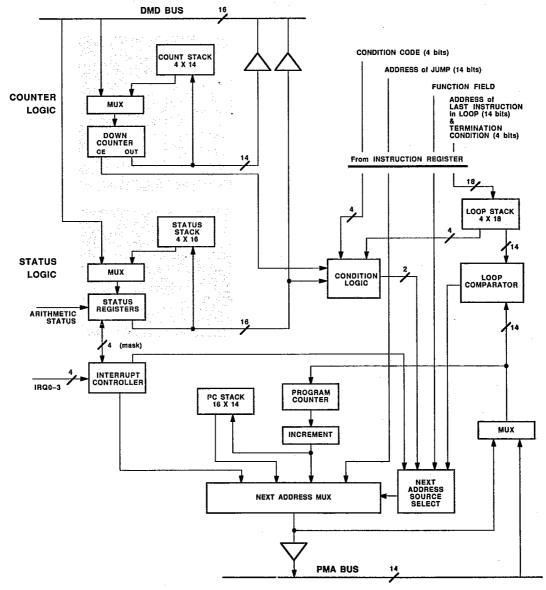

The program sequencer incorporates powerful and flexible mechanisms for program flow control such as zero-overhead looping, single-cycle branching (both conditional and unconditional), and automatic interrupt processing. Figure 6 shows a block diagram of the program sequencer.

The sequencing logic controls the flow of the program execution. It outputs a program memory address onto the PMA bus from

one of four sources: the PC incrementer, PC stack, instruction register or interrupt controller. The next address source selector controls which of these four sources are selected based on the current instruction word and the processor status. A fifth possible source for the next program memory address is provided by DAG2 when a register indirect jump is executed.

The program counter (PC) is a 14-bit register which contains the address of the currently executing instruction. The PC output goes to the incrementer. The incremented output is selected as the next program memory address if program flow is sequential. The PC value is pushed onto the  $16 \times 14$  PC stack when a CALL instruction is executed or when an interrupt is processed. The PC stack is popped when a return from subroutine or interrupt is executed. The PC stack is also used in zero-overhead looping.

The program sequencer section contains five status registers. These are the Arithmetic Status register (ASTAT), the Stack Status register (SSTAT), the Mode Status register (MSTAT), the Interrupt Control register (ICNTL) and the Interrupt Mask register (IMASK). These registers are described in detail in the next section.

The interrupt controller allows the processor to respond to one of four external interrupts with a minimum of overhead. The interrupts are internally prioritized and are individually maskable. Each interrupt can be set to be either edge- or level-sensitive. Depending on a bit in the interrupt control register (ICNTL), interrupt routines can either be nested, with higher priority interrupts taking precedence, or processed sequentially, with only one interrupt service active at a time. When responding to an interrupt, the status registers ASTAT, MSTAT, IMASK are pushed onto the status stack and the PC counter is loaded with the appropriate vectored address. The status stack is four levels deep to allow four levels of interrupt nesting. The stack is automatically popped when return from interrupt is executed.

The vector addresses for each interrupt are fixed at the lowest four addresses in the program memory space. Single-word, single-cycle branch instructions may be placed at these locations to transfer control to the appropriate interrupt service routine.

The down counter and the count stack implement a powerful looping mechanism. The down counter is a 14-bit register with

TPE D

Figure 6. Program Sequencer

ANALOG DEVICES INC

auto-decrement capability. It is loaded from the DMD bus with the loop count. The count is decremented every time the counter value is checked; when the count expires, the counter expired (CE) flag is set. The count stack allows the nesting of loops by storing temporarily dormant loop counts. When a new value is loaded into the counter from the DMD bus, the current counter value is automatically pushed onto the count stack as program flow enters a loop. The count stack is automatically popped whenever the CE flag is tested and is true, thereby resuming execution of the code outside the loop.

The DO UNTIL instruction executes a zero-overhead loop using the loop stack and the loop comparator. For a DO UNTIL instruction, a 14-bit termination address and a 4-bit termination condition are pushed onto the 18-bit loop stack. The address of the next instruction (which identifies the top of the loop) is pushed onto the PC stack. The loop comparator continuously compares the current PC value against the termination address on the top of the loop stack. When the termination address is detected, the processor checks if the termination condition is met. If the termination condition is not met, then the top of the PC stack is used as the next PC address, returning program flow to the beginning of the loop. If the termination condition is met, then the PC stack is popped, the current PC is incremented by one, and program flow falls out of the loop. The loop stack is four levels deep, permitting four levels of zero-overhead loop nesting.

### **Instruction Cache Memory**

The instruction cache memory is 16 levels deep and one instruction (24 bits) wide. The cache memory maintains a short history of previously executed instructions so they can be fetched internally if they are needed again.

Every time an instruction is fetched from external memory, it is also written into the cache memory. When the program enters a loop which fits within the cache, all the instructions in the loop are stored in cache during the first pass. On subsequent passes, the instructions can be fetched from the instruction cache when a program memory data access is required. This allows the program memory to be used for data access without penalty. The ADSP-2100 then becomes, in effect, a three-bus system with two data buses and one program bus. For the multiply/accumulate operations typical of digital signal processing algorithms, this gives significant speed advantages.

Instructions are fetched from cache memory only when a program memory data fetch is required. The cache monitor circuit automatically keeps track of when the next instruction is contained in the cache. No maintenance or overhead is needed to store externally fetched instructions in the cache or to read previously fetched instructions from cache.

#### PMD-DMD Bus Exchange

The PMD-DMD bus exchange circuit couples the PMD and DMD buses. The PMD bus is 24 bits wide and the DMD bus is 16 bits wide. The upper 16 bits of PMD are connected to the DMD bus. An 8-bit register (PX) allows transfer of the full width of the PMD bus. When data is read from the PMD bus, the lower 8 bits of the PMD bus are loaded into PX. When writing to the PMD bus, the contents of PX are appended to the upper 16 bits, forming a 24-bit value. The PX register is readable and loadable from the DMD bus.

#### STATUS REGISTERS

The ADSP-2100 maintains five status registers, each of which can be read over the DMD bus and four of which can be written. These registers are:

Arithmetic Status register ASTAT SSTAT Stack Status register (read-only) **MSTAT** Mode Status register

**ICNTL** Interrupt Control register **IMASK** Interrupt Mask register

#### ASTAT

ASTAT is 8 bits wide and holds the status information generated by the computational sections of the processor. The bits in ASTAT are defined as follows:

0 AZ (ALU result zero) (ALU result negative) 1 AN (ALU overflow) 2 AV

3 (ALU carry) AC 4 (ALUX input sign) AS 5 (ALU quotient flag) AQ 6 MV (MAC overflow)

(Shifter input sign)

The bits which express a particular condition (AZ, AN, AV, AC, MV) are all positive sense (1 = true, 0 = false). Each of the bits are automatically updated whenever a new status is generated by an arithmetic operation. As such, each bit is affected only by a certain subset of arithmetic operations, as defined by the following table:

Status Bit Updated on: AZ, AN, AV, AC Any ALU operation except division ALU absolute value operation AS AO **ALU** divide operations MV Any MAC operation except saturate MR

#### SSTAT

SS

SSTAT is 8 bits wide and holds the status of the four internal stacks. The bits in SSTAT are:

Shifter exponent detect operation

PC Stack Empty

PC Stack Overflow .1

2 Count Stack Empty

3 Count Stack Overflow

4 Status Stack Empty

5 Status Stack Overflow

6 Loop Stack Empty

7 Loop Stack Overflow

All of the bits are positive sense (1 = true, 0 = false). The *empty* status bits indicate that the number of pop operations for the stack is greater than or equal to the number of push operations (if no stack overflow has occurred) since the last reset. The overflow status bits indicate that the number of push operations for the stack has exceeded the number of pop operations by an amount that is greater than the depth of the stack. When this occurs, the item(s) most recently pushed will be missing from the stack (old data is considered more important than new). The stack overflow status bits "stick" once they are set, so that subsequent pop operations have no effect on them. A processor reset must be executed to clear the stack overflow status.

#### **MSTAT**

MSTAT is a 4-bit register that defines various operating modes of the processor. The Mode Control instruction enables or disables the four operating modes. The bits in MSTAT are:

- 0 Data Register Bank Select

- 1 Bit Reverse Mode (DAG1 only)

- 2 ALU Overflow Latch Mode

- 3 AR Saturation Mode

The data register bank select bit determines which set of data registers is currently active (0 = primary, 1 = secondary). The data registers include all of the result and input registers to the ALU, MAC, and Shifter (AXO, AX1, AYO, AY1, AF, AR, MXO, MX1, MYO, MY1, MF, MRO, MR1, MR2, SB, SE, SI, SRO and SR1). At initialization, the data register bank select bit is cleared.

The bit reverse mode, when enabled, bit-wise reverses all addresses generated by DAG1. This is most useful for reordering the input or output data in a radix-2 FFT algorithm.

The ALU overflow latch mode causes the AV (ALU overflow) status bit to "stick" once it is set. In this mode, when an ALU overflow occurs, AV will be set and remain set, even if subsequent ALU operations do not generate overflows. AV can then only be cleared by writing a zero into it from the DMD bus.

The AR saturation mode, when set, causes ALU results to be saturated to the maximum positive (H#7FFF) or negative (H#8000) values when an ALU overflow occurs.

#### **IMASK**

IMASK is four bits wide and allows the four interrupt inputs to be individually enabled or disabled. The bits in IMASK are:

- 0 IRQ0 Enable

- 1 IRQ1 Enable

- 2 IRQ2 Enable

- 3 IRQ3 Enable

The bits are all positive sense (0 = disabled, 1 = enabled). IMASK is set to zero upon a processor reset so that all interrupts are disabled initially.

#### **ICNTL**

ICNTL is a 5-bit register configuring the interrupt modes of the processor. The bits in ICNTL are:

- 0 IRO0 Sensitivity

- 1 IRQ1 Sensitivity

- 2 IRQ2 Sensitivity

- 3 IRQ3 Sensitivity

- 4 Interrupt Nesting Mode

The IRQ sensitivity bits determine whether a given interrupt input is edge- or level-sensitive (0 = level-sensitive, 1 = edge-sensitive). These bits are all undefined after a processor reset.

The interrupt nesting mode determines whether nesting of interrupt service routines is allowed. When set to zero, all interrupt levels will be masked automatically when an interrupt service routine is entered. When set to one, IMASK will be set so that only equal and lower priority interrupts will be masked, permitting higher priority interrupts to interrupt the current interrupt service routine. This bit is undefined after a processor reset.

#### **CONDITION CODES**

The condition codes are used to determine whether a conditional instruction, such as a jump, trap, call, return, MAC saturation or arithmetic operation, is performed. The sixteen composite status conditions and their derivations are given in Table I. Since arithmetic status is latched into ASTAT at the end of a processor cycle, the condition logic outputs represent conditions generated on a previous cycle.

| Code   | Status Condition               | True If:            |

|--------|--------------------------------|---------------------|

| EQ     | ALU Equal Zero                 | AZ=1                |

| NE     | ALU Not Equal Zero             | AZ=0                |

| LT     | ALU Less Than Zero             | AN.XOR.AV=1         |

| GE     | ALU Greater Than or Equal Zero | AN.XOR.AV=0         |

| LE .   | ALU Less Than or Equal Zero    | (AN.XOR.AV).OR.AZ=1 |

| GT     | ALU Greater Than Zero          | (AN.XOR.AV).OR.AZ=0 |

| AC     | ALU Carry                      | AC=1                |

| NOTAC  | Not ALU Carry                  | AC=0                |

| AV     | ALU Overflow                   | AV = 1              |

| NOT AV | Not ALU Overflow               | AV = 0              |

| MV     | MAC Overflow                   | MV = 1              |

| NOT MV | Not MAC Overflow               | MV = 0              |

| NEG    | ALU X Input Sign Negative      | AS=1                |

| POS    | ALU X Input Sign Positive      | AS=0                |

| NOTCE  | Not Counter Expired            | CE≠0                |

| TRUE   | True                           | Always True         |

Table I. Condition Codes

#### SYSTEM INTERFACE

Figure 7 shows a basic system configuration with the ADSP-2100.

#### **Clock Signals**

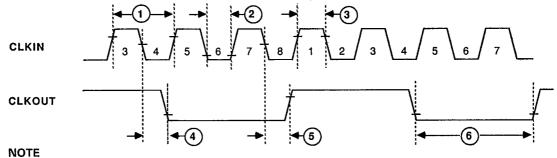

The ADSP-2100 takes a TTL-compatible clock signal, CLKIN, running at four times the basic processor cycle time as an input. Using this clock input, the processor divides the internal processor cycle into eight states, defined by the edges of the input clock. The active processor cycle consists of states 1 through 7. State 8 is a dead zone to provide a neutral stopping point for halting the processor.

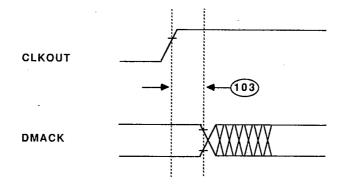

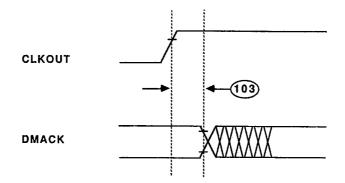

A clock output (CLKOUT) signal is generated by the processor to synchronize external devices to the processor's internal cycles. CLKOUT is high during states 8, 1, 2 and 3, and low during states 4, 5, 6 and 7. Its frequency is one-fourth of that of CLKIN. Except during RESET, the CLKOUT signal runs continuously.

#### **Bus Interface**

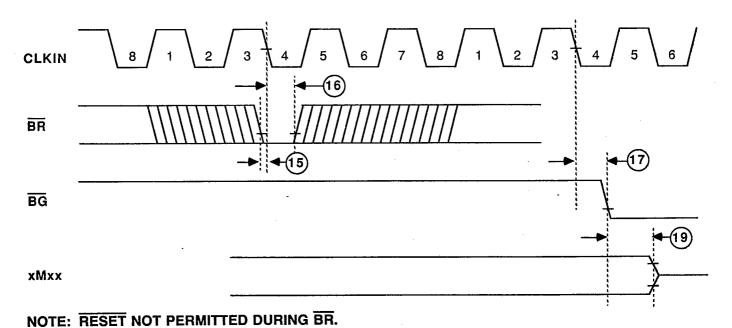

The ADSP-2100 can relinquish control of the memory buses to an external device. When the external device requires access to memory, it asserts the Bus Request  $(\overline{BR})$  signal. After completing the current instruction, the processor halts program execution, tristates the PMA, PMD,  $\overline{PMS}$ ,  $\overline{PMRD}$ ,  $\overline{PMWR}$  and PMDA output drivers and the DMA, DMD,  $\overline{DMS}$ ,  $\overline{DMRD}$  and  $\overline{DMWR}$  output drivers, and asserts the Bus Grant  $(\overline{BG})$  signal. When the  $\overline{BR}$  signal is released, the processor re-enables the output drivers, releases the  $\overline{BG}$  signal, and continues program execution from the point where it stopped.

#### Program Memory Interface

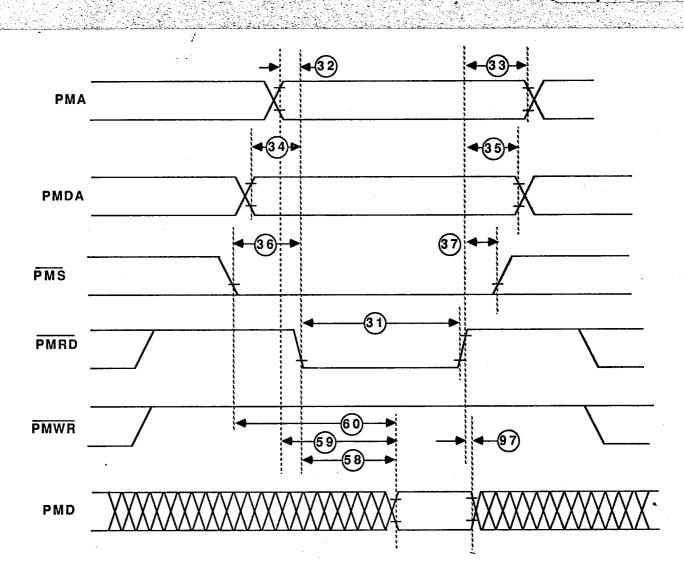

The Program Memory Interface supports two buses: the program memory address bus (PMA) and the program memory data bus (PMD). The 14-bit PMA bus directly addresses up to 16K words. The PMD bus is bidirectional and 24 bits wide.

Since program memory can be used for both instruction code and data storage, the Program Memory Data Access (PMDA) signal is asserted whenever data, as opposed to an instruction code, is fetched. There is no placement restriction for instruction code and data in program memory area if less than 16K words are used. Since the timing of PMDA is compatible with that of the PMA lines, it may be used as a 15th address line if desired. This effectively doubles the program memory area to 32K, which must be split into 16K dedicated to instruction codes and 16K to data.

The program memory data lines are bidirectional. The Program Memory Select  $(\overline{PMS})$  signal indicates access to the Program Memory and can be used as a chip select signal. The Program Memory Write  $(\overline{PMWR})$  signal indicates a write operation and can be used as a write strobe. The Program Memory Read  $(\overline{PMRD})$  signal indicates a read operation and can be used as a read strobe or output enable signal.

Although the processor internal data bus is only 16 bits, the ADSP-2100 can write to the full 24-bit program memory using the PX register.

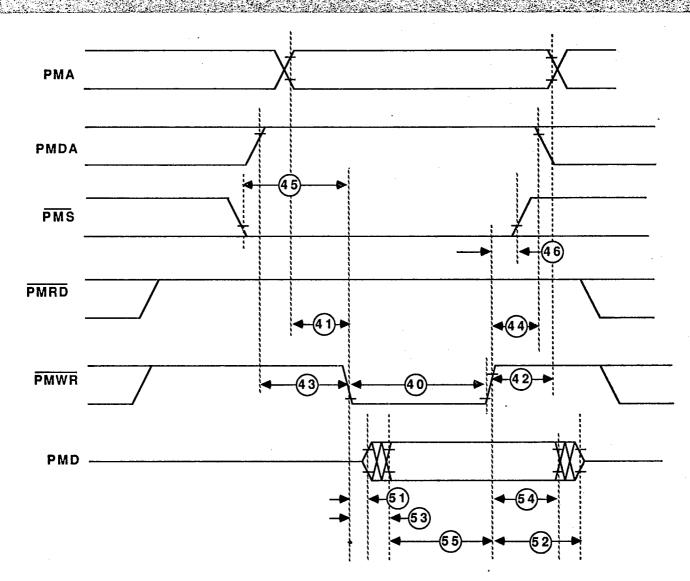

#### **Data Memory Interface**

The Data Memory Interface supports two buses: the Data Memory Address bus (DMA) and the Data Memory Data bus (DMD). The 14-bit DMA bus directly addresses up to 16K words of data. The DMD bus is bidirectional and 16 bits wide. The Data Memory Select (DMS) signal indicates access to the Data Memory and can be used as a chip select signal. The Data Memory Write (DMWR) signal indicates a write operation and can be used as a write strobe. The Data Memory Read (DMRD) signal indicates a read operation and can be used as a read strobe or output enable signal.

The ADSP-2100 supports memory-mapped I/O, with the peripherals memory mapped into the data memory address space and accessed by the processor in the same manner as data memory.

Figure 7. Basic System Configuration

To allow interfacing to slower peripherals, the data memory acknowledge (DMACK) signal is provided. The ADSP-2100 checks the status of the DMACK signal at the end of each processor cycle. If the DMACK signal is not asserted, the processor extends the current cycle by another full cycle. This extension occurs as many times as necessary until the DMACK signal is asserted and the access is completed.

### Interrupt Handling

The ADSP-2100 provides four direct interrupt input pins,  $\overline{IRQ_0}$  to  $\overline{IRQ_3}$ . Each interrupt pin corresponds to a particular interrupt priority level from 3 (highest) to 0 (lowest). The four interrupt levels are internally prioritized and individually maskable. These input pins can be programmed to be either level- or edge-sensitive.

The ADSP-2100 supports a vectored interrupt scheme: when an external interrupt is acknowledged, the processor switches program control to the interrupt vector address corresponding to the interrupt level (program memory locations 0000 to 0003). Interrupts can optionally be nested so that a higher priority interrupt can preempt the currently executing interrupt service routine.

#### **Processor Control Interface**

The processor control interface provides external control over the activity of the processor. The control signals are RESET, HALT and TRAP.

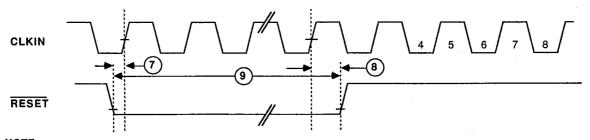

The  $\overline{RESET}$  signal initiates a master reset of the ADSP-2100. The  $\overline{RESET}$  signal must be asserted after the chip is powered up to assure proper initialization. The master reset performs the following:

- 1 Initialize internal clock circuitry

- 2 Reset all internal stack pointers

- 3 Clear the cache memory monitor

- 4 If there is no pending bus request, PMA is driven with 0004

- 5 Mask all interrupts

- 6 Clear MSTAT register.

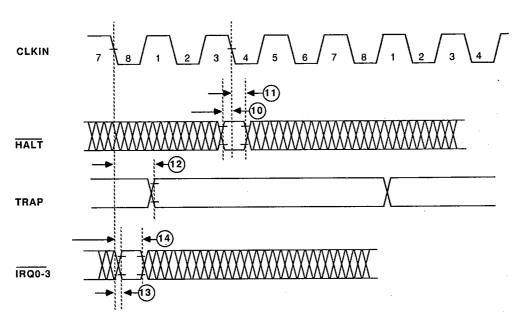

The HALT signal is used to suspend program execution temporarily. When HALT is asserted, the processor stops at the end of the current instruction. To ensure that the processor always halts after completion of an instruction fetch, an external fetch of the next instruction is forced even if the instruction is available from internal cache memory. Since the processor always stops after an external instruction fetch cycle, the controlling device is able to observe the instruction address where the program was stopped. The halt condition can be sustained for any length of time, during which all signals generated by the processor will remain static (maintaining the output at state 8). The processor will continue normal execution when the HALT line is released.

The TRAP signal is generated by the processor whenever a TRAP instruction is executed. Assertion of the TRAP signal indicates that the processor has stopped instruction execution just after the end of the cycle which executed the TRAP instruction. The TRAP state is identical to the HALT state, with the processor output frozen in state 8. In this case, the processor PMA bus contains the address of the instruction following the TRAP instruction. The TRAP signal remains asserted until the HALT signal is asserted externally. When the HALT signal assertion is sensed, the processor releases the TRAP signal. However, the processor remains in the halt condition until the HALT line is released.

# **Multiprocessor Synchronization**

Even when multiple ADSP-2100s are driven from the same CLKIN signal, there is a phase ambiguity between the various processors. This ambiguity can be prevented by using a single master RESET signal synchronized to CLKIN. When the master RESET is released, all the processors begin state 5 on the same edge of CLKIN. Once initialized in this manner, the cycle states of the processors remain synchronized with each other.

#### INSTRUCTION SET DESCRIPTION

The ADSP-2100 assembly language uses an algebraic syntax for ease of coding and readability. The sources and destinations of computations and data movements are written explicitly in each assembly statement, eliminating cryptic assembler mnemonics. Nevertheless, every instruction assembles into a single 24-bit word and executes in a single cycle. The instructions encompass a wide variety of instruction types along with a high degree of operational parallelism. There are five basic categories of instructions: data move instructions, computational instructions, multifunction instructions, program flow control instructions and miscellaneous instructions. Each of these instruction types is described briefly. The complete instruction set is summarized in Table IV at the end of this section.

#### **Data Move Instructions**

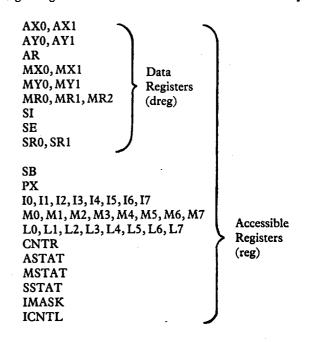

Table II gives a list of all registers that are accessible using the data move instructions. (Only the program counter (PC), the instruction register, the arithmetic feedback register (AF) and the multiplier feedback register (MF) are not on this list.) This set of registers is denoted as reg in the instruction set summary given in Table IV. A subset of the reg group associated with the computational units, which generally hold data as opposed to address or status information, is denoted as dreg.

The data move instructions include transfers between internal registers, between data memories and internal registers, between program memories and internal registers, and immediate value loading of registers and data memories. The content of every reg

Table II. Register Classification

can also be loaded to any other reg. Every reg can be loaded with an immediate value which is the full width of the particular register being loaded.

Two addressing modes are supported for data memory transfers: direct addressing and indirect addressing. In direct addressing, the memory address is supplied from the instruction word. In indirect addressing, one of the data address generators provides the address. Using direct addressing, the content of a data memory location can be written and read by any reg. Using indirect addressing, the content of a data memory location can only be written and read by a dreg. Immediate data load to data memory is permitted with indirect addressing. Only the indirect addressing mode is supported for program memory data transfers, and contents of a program memory location can be read and written to any dreg.

#### **Computational Instructions**

There are three types of operations associated with the computational units: ALU operations, MAC operations and shifter operations. With few exceptions, all these computational instructions can be made conditional. (The permissible conditions are specified in Table I.) Each computational unit has a set of input registers and output registers. A list of permissible input operands and result registers for each of the units is given in Table III.

#### **Multifunction Instructions**

Multifunction instructions execute one computational operation with one or two data moves. All of the multifunction instructions utilize various combinations of the computational and data move operations described above. Since the instruction word is only 24 bits wide, only certain combinations are valid. In general, the following rules are followed.

- 1 Only one unconditional computational operation can be specified

- 2 Any memory transfer must use the indirect addressing mode

- 3 Data move operations can only involve data registers (dregs)

- 4 Only an ALU or a MAC operation can be specified with two operand fetches, one from program memory and one from data memory.

#### **Program Flow Control Instructions**

**■** 0816800 0019449 9

Program flow control instructions include JUMP, CALL, return from subroutine, return from interrupt, DO UNTIL and TRAP. All of these instructions can be made conditional. The JUMP and CALL instructions support both direct addressing, with the destination address specified by the instruction word, and indirect addressing, with the destination address specified by one of the I registers in DAG2.

#### Miscellaneous Instructions

Miscellaneous instructions include indirect register modify, stack control, mode control and NOP operations.

| ALU                 |                    |                    |

|---------------------|--------------------|--------------------|

| Source for          | Source for         | Destination for    |

| X input port (xop)  | Y input port (yop) | output port R      |

| AX0, AX1            | AY0, AY1           | AR                 |

| AR                  | AF                 | AF -               |

| MR0, MR1, MR2       | ·                  | ,                  |

| SR0, SR1            |                    |                    |

| MAC                 |                    |                    |

| MAC<br>Source for   | Source for         | Destination for    |

| X input port (xop)  | Y input port (yop) | output port R      |

|                     |                    |                    |

| MX0, MX1            | MY0, MY1           | MR (MR2, MR1, MR0) |

| ,AR                 | MF                 | MF                 |

| MR0, MR1, MR2       |                    |                    |

| SR0, SR1            |                    |                    |

| Shifter             |                    |                    |

| Source for          |                    | Destination for    |

| Shifter input (xop) |                    | Shifter output     |

|                     | <u> </u>           | SR(SR1, SR0)       |

| SI                  |                    | 3K(3K1,3K0)        |

| AR                  |                    |                    |

| MR0, MR1, MR2       |                    |                    |

| SR0, SR1            |                    |                    |

Table III. Computational Input/Output Registers

#### These conventions are used in Table IV:

- 1. All keywords are shown in capital letters.

- 2. Brackets enclose optional parts of the syntax.

- Vertical lines indicate that one parameter must be chosen from those enclosed.

- 4. Table I defines the conditions for condition.

- 5. Table II defines the set of registers for dreg and reg.

- 6. Table III defines the set of registers for xop and yop.

- 7. <data> represents an immediate value.

- 8. <address> may be an immediate value or label.

- <comp>, in a multifunction instruction, represents all legal ALU, MAC or Shifter operations with these restrictions:

- All operations are performed unconditionally

- Shift Immediate operations are not allowed

- -ALU division (DIVS, DIVQ) is not allowed

#### DATA MOVE INSTRUCTIONS

#### Register Move

reg = reg;

### Load Register Immediate

reg = < data >;

#### Data Memory Read (direct address)

reg = DM (<address>);

# Data Memory Read (indirect address)

| ata mici | mory | ncaul | шчп        | CCI | auui | coo, |

|----------|------|-------|------------|-----|------|------|

| dreg     | =    | DM(   | 10         | ,   | M0   | );   |

|          |      |       | I1         |     | Ml   |      |

|          |      |       | 12         |     | M2   |      |

|          |      |       | 13         |     | M3   | 1    |

|          |      |       | <b>I</b> 4 |     | M4   |      |

|          |      |       | <b>I</b> 5 |     | M5   |      |

|          |      |       | <b>I</b> 6 |     | M6   | ŀ    |

|          |      |       | I7         |     | M7   |      |

#### Program Memory Read (indirect address)

# Data Memory Write (direct address)

$DM(\langle address \rangle) = reg;$

#### Data Memory Write (indirect address)

| ata Mic | morj       | . ** | rire (i | nan | CCL | auuressy      |   |

|---------|------------|------|---------|-----|-----|---------------|---|

| DM(     | 10         | , ,  | MO      | )   | =   | dreg          | ; |

|         | I1         |      | M1      |     | ĺ   | <data></data> |   |

|         | I2         |      | M2      |     |     |               |   |

|         | I3         |      | M3      |     |     |               |   |

|         |            |      |         |     |     |               |   |

|         | I4         |      | M4      |     |     |               |   |

|         | <b>I</b> 5 |      | M5      |     |     |               |   |

|         | <b>I</b> 6 |      | M6      |     |     |               |   |

|         | I7         |      | M7      |     |     |               |   |

|         |            |      |         |     |     |               |   |

#### Program Memory Write (indirect address)

#### COMPUTATIONAL INSTRUCTIONS: ALU

#### Add/Add with Carry

[IF condition]

$$\begin{vmatrix} AR \\ AF \end{vmatrix} = xop \begin{vmatrix} +yop \\ +C \\ +yop+C \end{vmatrix}$$

;

#### Subtract X-Y/Subtract X-Y with Borrow

| [IF condition] | AR<br>AF | -yop<br>-yop+C-1 | ; |

|----------------|----------|------------------|---|

| +              |          | 1 7-1 - 1        |   |

#### Subtract Y-X/Subtract Y-X with Borrow

[IF condition]

$$\begin{vmatrix} AR \\ AF \end{vmatrix} = yop \begin{vmatrix} -xop \\ -xop + C - 1 \end{vmatrix}$$

;

#### AND, OR, Exclusive OR

[IF condition]

$$\begin{vmatrix} AR \\ AF \end{vmatrix} = xop \begin{vmatrix} AND \\ OR \\ XOR \end{vmatrix}$$

yop

#### Pass/Clear

| [IF condition] | AR | = PASS | xop | ; |

|----------------|----|--------|-----|---|

|                | AF |        | yop | l |

#### Negate

| - 10Baro         |    | i i |     |   |

|------------------|----|-----|-----|---|

| [ IF condition ] | AR | = - | хор | , |

|                  | AF |     | yop |   |

#### NOT

#### **Absolute Value**

| [IF condition] | AR | = ABS | хор | ; |

|----------------|----|-------|-----|---|

|                | AF |       | yop |   |

# Increment

# Decrement

[IF condition]

$$\begin{vmatrix} AR \\ AF \end{vmatrix} = yop -1$$

# Divide

#### COMPUTATIONAL INSTRUCTIONS: SHIFTER

#### Arithmetic Shift

[IF condition]

$$SR = [SR OR] ASHIFT xop | (HI) | (LO) |$$

# Logical Shift

| [IF condition] | SR | = | [SR OR] LSHIFT xop | (HI) |  |

|----------------|----|---|--------------------|------|--|

|                |    |   |                    | (LO) |  |

#### Normalize

| [IF condition] | SR = | [SR OR] NORM xop | (HI) | ١, |

|----------------|------|------------------|------|----|

|                |      |                  | (LO) |    |

#### **Derive Exponent**

# **Block Exponent Adjust**

[IF condition]

$$SB = EXPADJ \times p$$

;

(HI) ;

(HI)

(LO)

**Arithmetic Shift Immediate**

$$SR = [SR OR] \quad ASHIFT \quad xop BY < data >$$

(HI)

**Conditional MR Saturation** IFMVSATMR;

Logical Shift Immediate

<address>

PROGRAM FLOW CONTROL INSTRUCTIONS

COMPUTATIONAL INSTRUCTIONS: MAC

# **Multiply Accumulate**

# **Return from Interrupt** [IF condition] RTI;

**Multiply Subtract**

# Trap

Clear

[IF condition]

$$\begin{vmatrix} MR \\ MF \end{vmatrix} = 0$$

;

# Transfer MR

[IF condition]

$$| MR | = MR [(RND)];$$

# **MULTIFUNCTION INSTRUCTIONS**

# Computation with Data Register Move <comp> , dreg = dreg;

# Computation with Memory Read

|      | I1<br>I2<br>I3             | M1<br>M2<br>M3       |  |

|------|----------------------------|----------------------|--|

|      | 14<br>15<br>16<br>17       | M4<br>M5<br>M6<br>M7 |  |

| PM ( | 14 ,<br>15  <br>16  <br>17 | M4 )<br>M5 M6 M7     |  |

**Data & Program Memory Read** |AX0| = DM (|I0|,|M0|), = PM ( |I4|, |M4| );AY0 AY1 **I**5 M5 AX1 11 M1 MY0 16 M6 MX0 12 M2 MY1 MX1 I3 M3

ALU/MAC Operation with Data & Program Memory Read\*  $|\langle ALU \rangle|$ , |AX0| = DM(|I0|, |M0|), | AY0 | = PM ( | I4 |M4);**I**5 M5 AY1 <MAC> AX1 **I**1 M1 MY0 16 M6 MX0 12 M2 17 M7 MX1 M3

#### MISCELLANEOUS INSTRUCTIONS

Stack Control

[|PUSH | STS] [,POPCNTR] [,POPPC] [,POPLOOP];

[|POP |

Mode Control

[| ENA | BIT\_REV | [, | ENA | AV\_LATCH ] [, | ENA | AR\_SAT ] [, | ENA | SEC\_REG ]

DIS | DIS | DIS | ENA | SEC\_REG |

Modify Address Register

MODIFY ( | IO | M0|);11 M1 12 M2 **I3** M3 **I**4 M4 **I**5 M5 **I**6 M6 17 M7

No Operation NOP;

Table IV. Instruction Set Summary

<sup>\*</sup>ALU Division operations not allowed.

# **SPECIFICATIONS RECOMMENDED OPERATING CONDITIONS**

#### ADSP-2100/ADSP-2100A

|                                                | J, K, | AJ, AK<br>rades | S, AS, | S, AS, AT, AU<br>Grades |      |  |

|------------------------------------------------|-------|-----------------|--------|-------------------------|------|--|

| Parameter                                      | Min   | Max             | Min    | Max                     | Unit |  |

| V <sub>DD</sub> Supply Voltage                 | 4.75  | 5.25            | 4.50   | 5.50                    | V    |  |

| T <sub>AMB</sub> Ambient Operating Temperature | 0     | +70             | -55    | + 125                   | °C   |  |

# **ELECTRICAL CHARACTERISTICS**

#### **ADSP-2100**

|                  |                                       |                                            |     |     | Gr  |     |          |

|------------------|---------------------------------------|--------------------------------------------|-----|-----|-----|-----|----------|

| Param            | eter                                  | Test Conditions                            | Min | Max | Min | Max | Unit     |

| $V_{IH}$         | Hi-Level Input Voltage <sup>1</sup>   | @V <sub>DD</sub> =max                      | 2,0 |     | 2.2 |     |          |

| $V_{IL}$         | Lo-Level Input Voltage <sup>1</sup>   | @V <sub>DD</sub> =min                      |     | 0.8 |     | 0.8 | V        |

| V <sub>OH</sub>  | Hi-Level Output Voltage <sup>2</sup>  | $@V_{DD} = min, I_{OH} = -1mA$             | 2.4 |     | 2.4 |     | V        |

| $V_{OL}$         | Lo-Level Output Voltage <sup>2</sup>  | $@V_{DD} = min, I_{OL} = 4mA$              |     | 0.4 |     | 0.6 | <b>V</b> |

| I <sub>IH</sub>  | Hi-Level Input Current <sup>3</sup>   | $@V_{DD} = \max, V_{IN} = \max$            |     | 10  |     | 10  | μΑ       |

| I <sub>IL</sub>  | Lo-Level Input Current <sup>3</sup>   | $@V_{DD} = \max_{i} V_{IN} = 0V$           |     | 10  |     | 10  | μA       |

| I <sub>OZH</sub> | Tristate Leakage Current <sup>4</sup> | $@V_{DD} = \max_{i} V_{IN} = \max_{i}^{7}$ |     | 10  |     | 10  | μA       |

| I <sub>OZL</sub> | Tristate Leakage Current <sup>5</sup> | $@V_{DD} = \max_{i} V_{IN} = 0V^7$         |     | 10  |     | 10  | μΑ       |

| I <sub>OZL</sub> | Tristate Pullup Current <sup>6</sup>  | $@V_{DD} = \max_{i} V_{IN} = 0V^7$         |     | 150 |     | 150 | μΑ       |

| $I_{DD}$         | Supply Current (Power-Down)9          | $@V_{DD} = max, V_{IN} = 0V^{6,7}$         |     | 10  |     | 15  | mA       |

| $I_{DD}$         | Supply Current (Dynamic)              | $@V_{DD} = max, max clock rate^8$          |     | 90  |     | 100 | mA       |

#### ADSP-2100A

|                     |                                       |                                                     | AJ&<br>Gra | AK  | A<br>Gra | S<br>ade | A'<br>Gra |     | 3   | .U<br>ade |      |

|---------------------|---------------------------------------|-----------------------------------------------------|------------|-----|----------|----------|-----------|-----|-----|-----------|------|

| Param               | eter                                  | Test Conditions                                     | Min        | Max | Min      | Max      | Min       | Max | Min | Max       | Unit |

| $\overline{V_{IH}}$ | Hi-Level Input Voltage <sup>i</sup>   | @V <sub>DD</sub> =max                               | 2.0        | 1   | 2.2      |          | 2.2       |     | 2.2 |           | V    |

| $\overline{V_{IH}}$ | Hi-Level Input Voltage at CLKIN       | @V <sub>DD</sub> =max                               | 2.2        |     | 2.4      |          | 2.4       |     | 2,4 |           | V    |

| $\overline{V_{IL}}$ | Lo-Level Input Voltage <sup>1</sup>   | @V <sub>DD</sub> =min                               |            | 0.8 |          | 0.8      |           | 0.8 |     | 0.8       | V    |

| $\overline{V_{IL}}$ | Lo-Level Input Voltage at CLKIN       | @V <sub>DD</sub> =min                               |            | 0.8 |          | 0.8      |           | 0.8 |     | 0.8       | V    |

| $V_{OH}$            | Hi-Level Output Voltage <sup>2</sup>  | $@V_{DD} = min, I_{OH} = -1mA$                      | 2.4        |     | 2.4      |          | 2.4       |     | 2.4 |           | V    |

| $\overline{V_{OL}}$ | Lo-Level Output Voltage <sup>2</sup>  | $@V_{DD} = min, I_{OL} = 4mA$                       |            | 0.4 |          | 0.6      |           | 0.6 |     | 0.6       | v    |

| I <sub>IH</sub>     | Hi-Level Input Current <sup>3</sup>   | $@V_{DD} = max, V_{IN} = max$                       |            | 10  |          | 10       |           | 10  | 1   | 10        | μΑ   |

| Ĭ <sub>IL</sub>     | Lo-Level Input Current <sup>3</sup>   | $@V_{DD} = max, V_{IN} = 0V$                        |            | 10  |          | 10       |           | 10  |     | 10        | μA   |

| I <sub>OZH</sub>    | Tristate Leakage Current <sup>4</sup> | $@V_{DD} = \max_{i} V_{IN} = \max_{i}^{7}$          |            | 10  |          | 10       |           | 10  |     | 10        | μΑ   |

| I <sub>OZL</sub>    | Tristate Leakage Current <sup>5</sup> | $@V_{DD} = \max_{i} V_{IN} = 0V^7$                  |            | 10  |          | 10       |           | 10  |     | 10        | μΑ   |

| I <sub>OZL</sub>    | Tristate Pullup Current <sup>6</sup>  | $@V_{DD} = \max_{i} V_{IN} = 0V^7$                  |            | 180 |          | 180      |           | 180 |     | 180       | μΑ   |

| $I_{DD}$            | Supply Current (Power-Down)9          | $@V_{DD} = \max_{i, V_{IN}} = 0V^{6,7}$             |            | 10  |          | 15       |           | 15  |     | 15        | mA   |

| $I_{DD}$            | Supply Current (Dynamic)              | @V <sub>DD</sub> = max, max clock rate <sup>8</sup> |            | 150 |          | 130      |           | 180 |     | 200       | mA   |

NOTES

Applies to pins: PMD<sub>0-23</sub>, DMD<sub>0-15</sub>, BR, IRQ<sub>0-3</sub>, DMACK, RESET, HALT, (48 input pins for ADSP-2100A). Includes CLKIN for ADSP-2100 (49 input pins).

Applies to pins: PMA<sub>0-13</sub>, PMS, PMD<sub>0-23</sub>, PMRD. PMWR, PMDA, BG, DMA<sub>0-13</sub>, DMS, DMD<sub>0-15</sub>, DMRD. DMWR, TRAP, CLKOUT (78 output pins).

Applies to pins: PMA<sub>0-13</sub>, PMS, PMD<sub>0-23</sub>, PMRD. PMWR, PMDA, DMA<sub>0-13</sub>, DMS, DMD<sub>0-15</sub>, DMRD. DMWR(75 tristateable pins).

Applies to pins: PMA<sub>0-13</sub>, PMS, PMD<sub>0-23</sub>, PMRD. PMWR, PMDA, DMA<sub>0-13</sub>, DMS, DMD<sub>0-15</sub>, DMRD. DMWR(75 tristateable pins).

Applies to pins: PMA<sub>0-13</sub>, PMDA, DMA<sub>0-13</sub>, DMS, DMD<sub>0-15</sub>, DMS, DMD<sub>0-15</sub>, DMWR(46 tristateable pins w/pullup).

Applies to pins: PMD<sub>0-23</sub>, PMS, PMRD. PMWR, DMD<sub>0-15</sub>, DMS, DMRD. DMWR(46 tristateable pins w/pullup).

<sup>&</sup>lt;sup>7</sup>Additional Test Conditions:  $V_{IN} = 0V$  on  $\overline{BR}$  and  $\overline{RESET}$ , CLKIN active, forces tristate condition.

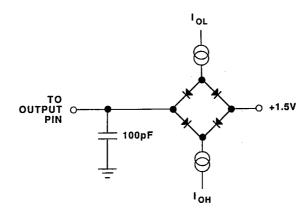

Additional Test Conditions: Outputs loaded TTL loads w/100pF capacitance, V<sub>III</sub> = 2.4V, Clock rate = max.

9"Power-down" refers to an idle state. While the processor does not have any special standby or low-power mode, these conditions represent the

#### ABSOLUTE MAXIMUM RATINGS\*

| Supply Voltage $\dots \dots \dots$ |

|------------------------------------------------------------------------------------------------------------------------------------|

| Input Voltage $-0.3V$ to $V_{\rm DD}$ $+0.3V$                                                                                      |

| Output Voltage Swing0.3V to V <sub>DD</sub> +0.3V                                                                                  |

| Operating Temperature Range (Ambient)55°C to +125°C                                                                                |

| Storage Temperature Range65°C to +150°C                                                                                            |

| Lead Temperature (10sec) PGA. |   |   |  |  |  |  |   | +300°C |

|-------------------------------|---|---|--|--|--|--|---|--------|

| Lead Temperature (5sec) POFP  | _ | _ |  |  |  |  | _ | +280°C |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING INFORMATION**

| Part Number       | Speed (MHz) | Temperature Range | Package            |

|-------------------|-------------|-------------------|--------------------|

| ADSP-2100JG       | 6.144       | 0 to +70°C        | 100-Pin Grid Array |

| ADSP-2100KG       | 8.192       | 0 to +70°C        | 100-Pin Grid Array |

| ADSP-2100AJG      | 10.24       | 0 to +70°C        | 100-Pin Grid Array |

| ADSP-2100AKG      | 12.50       | 0 to +70°C        | 100-Pin Grid Array |

| ADSP-2100JP       | 6.144       | 0 to +70°C        | 100-PQFP           |

| ADSP-2100KP       | 8.192       | 0 to +70°C        | 100-PQFP           |

| ADSP-2100AJP      | 10.24       | 0 to +70°C        | 100-PQFP           |

| ADSP-2100AKP      | 12.50       | 0 to +70°C        | 100-PQFP           |

| ADSP-2100SG       | 6.144       | - 55°C to + 125°C | 100-Pin Grid Array |

| ADSP-2100ASG      | 8.192       | - 55°C to + 125°C | 100-Pin Grid Array |

| ADSP-2100ATG      | 10.24       | - 55°C to + 125°C | 100-Pin Grid Array |

| ADSP-2100AUG      | 12.50       | - 55°C to + 125°C | 100-Pin Grid Array |

| ADSP-2100SG/883B  | 6.144       | - 55°C to + 125°C | 100-Pin Grid Array |

| ADSP-2100ASG/883B | 8.192       | - 55°C to + 125°C | 100-Pin Grid Array |

| ADSP-2100ATG/883B | 10.24       | - 55°C to + 125°C | 100-Pin Grid Array |

| ADSP-2100AUG/883B | 12.50       | - 55°C to + 125°C | 100-Pin Grid Array |

| ADSP-2100SZ       | 6.144       | - 55°C to + 125°C | 100-CQFP           |

| ADSP-2100ASZ      | 8.192       | - 55°C to + 125°C | 100-CQFP           |

| ADSP-2100ATZ      | 10.24       | - 55°C to + 125°C | 100-CQFP           |

| ADSP-2100AUZ      | 12.50       | - 55°C to + 125°C | 100-CQFP           |

| ADSP-2100SZ/883B  | 6.144       | - 55°C to + 125°C | 100-CQFP           |

| ADSP-2100ASZ/883B | 8.192       | - 55°C to + 125°C | 100-CQFP           |

| ADSP-2100ATZ/883B | 10.24       | - 55°C to + 125°C | 100-CQFP           |

| ADSP-2100AUZ/883B | 12.50       | - 55°C to + 125°C | 100-CQFP           |

#### ADSP-2100/ADSP-2100A Development Tools

| Part Number                                        | Description                                                                                                                                                               |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDS-2110<br>ADDS-2121<br>ADDS-2122<br>ADDS-2123-C | Cross-Software and Simulator (VAX/VMS) Cross-Software (IBM PC/DOS) Simulator (IBM PC/DOS) Cross-Software and Simulator (Sun 2/3, Unix BSD 4.2)                            |

| ADDS-2130<br>ADDS-2131<br>ADDS-2133-C              | C Compiler, Cross-Software and Simulator (VAX/VMS) C Compiler, Cross-Software and Simulator (IBM PC/DOS) C Compiler, Cross-Software and Simulator (Sun 2/3, Unix BSD 4.2) |

| ADDS-2150A-8<br>ADDS-2150AE-8                      | ADSP-2100A 8MHz In-Circuit Emulator (110V)<br>ADSP-2100A 8MHz In-Circuit Emulator (220V)                                                                                  |

| ADDS-2160-8                                        | ADSP-2100A 8MHz Evaluation Board                                                                                                                                          |

| ADDS-2169<br>ADDS-2190<br>ADDS-2190E               | University Package (ADDS-2131 and ADDS-2160) Three Day ADSP-2100 Workshop (U.S.) Three Day ADSP-2100 Workshop (Europe)                                                    |

# **ESD SENSITIVITY**

The ADSP-2100 and ADSP-2100A feature proprietary input protection circuitry. Per Method 3015 of MIL-STD-883, the ADSP-2100 has been classified as a Class 1 device and the ADSP-2100A as a Class 2 device.

Proper ESD precautions are strongly recommended to avoid functional damage or performance degradation. Charges as high as 4000 volts readily accumulate on the human body and test equipment and discharge without detection. Unused devices must be stored in conductive foam or shunts, and the foam should be discharged to the destination socket before devices are removed. For further information on ESD precautions, refer to Analog Devices' ESD Prevention Manual.

# **SWITCHING CHARACTERISTICS**

#### **GENERAL NOTES**

Use the exact timing information given. Do not attempt to derive parameters from the addition or subtraction of others. While this addition or subtraction would yield meaningful results for an individual part, the values given in this data sheet reflect statistical variations and worst cases. Consequently, you cannot meaningfully add up parameters to derive or "verify" longer times.

#### **TIMING NOTES**

Switching characteristics specify how the processor is switching its signals. The user has no control over this operation. It is dependent on the internal design. Timing requirements specify the timing of signals that the user has control over such as the placement of data on the DMD bus as input for a read operation.

Timing requirements are used by a designer to guarantee that the processor operates correctly with another device while switching characteristics inform the designer what the device is doing under any given circumstance. Switching characteristics are also referenced to ensure that any timing requirement of a device connected to the processors (such as a memory) is satisfied.

#### MEMORY REQUIREMENTS

This chart links common memory device specification names and ADSP-2100/ADSP-2100A timing parameters for your convenience.

| Parameter<br>Numbér | Parameter<br>Name                                            | Common Memory Device Specification Name                        |

|---------------------|--------------------------------------------------------------|----------------------------------------------------------------|

| 41<br>79            | PMA Valid to PMWR Low DMA Valid to DMWR Low                  | Address Set Up to Write Start<br>Address Set Up to Write Start |

| 42<br>80            | PMWR High to PMA Invalid DMWR High to DMA Invalid            | Address Hold Time<br>Address Hold Time                         |

| 55<br>91            | PMD Out Valid to PMWR High<br>DMD Out Valid to DMWR High     | Data Set Up Time<br>Data Set Up Time                           |

| 54<br>90            | PMWR High to PMD Out Invalid DMWR High to DMD Out Invalid    | Data Hold Time<br>Data Hold Time                               |

| 58<br>94            | PMRD Low to PMD Input Valid DMRD Low to DMD Input Valid      | OE to Data Valid OE to Data Valid                              |

| 59<br>95            | PMA Valid to PMD Input Valid<br>DMA Valid to DMD Input Valid | Address Access Time Address Access Time                        |

| 41 + 40             | PMA Valid to PMWR Low<br>+ PMWR Width Low                    | Address Set Up to Write End                                    |

| 79 + 78             | DMA Valid to DMWR Low<br>+ DMWR Width Low                    | Address Set Up to Write End                                    |

| ADSP-2100<br>Clock Signals       | Test | , ,  | rade |      | rade |      | rade | **    | Derating |

|----------------------------------|------|------|------|------|------|------|------|-------|----------|

| <del></del>                      | Code | Min  | Max  | Min  | Max  | Min  | Max  | Units | Factor   |