Multiplier/Divider and ALU

# 64-Bit IEEE Floating-Point Chipset

# ADSP-3212/ADSP-3222

#### **FEATURES**

Fully Compatible with IEEE Standard 754 Arithmetic Operations on Four Data Formats: 32-Bit Single-Precision Floating-Point 64-Bit Double-Precision Floating-Point 32-Bit Twos-Complement Fixed-Point 32-Bit Unsigned-Magnitude Fixed-Point Only One Internal Pipeline Stage 20 MFLOPS Pipelined Throughput For Multiplication and Standard ALU Operations Exact Division: 300ns Single Precision and 600ns **Double Precision** Low Latency for Scalar Operations 130ns for 32-Bit Multiplication or Standard ALU Operations 155ns for 64-Bit Multiplication or Standard ALU Operations **Exact Square Root ALU Instruction** 2.5W Maximum Power Dissipation per Chip with 1.0 µm CMOS Technology 144-Lead Pin Grid Array Available Specified to MIL-STD-883, Class B Pin-Compatible Upgrades From ADSP-3211/ADSP-3

Complete 40 MFLOPS Floating-Point Chipset

APPLICATIONS

High Performance Digital Signal Processin

Engineering Workstations

Floating-Point Accelerators

Array Processors

Mini-Supercomputers

RISC Processors

#### GENERAL DESCRIPTION

The ADSP-3212 Floating-Point Multiplier/Divider and the ADSP-3222 Floating-Point ALU are high speed, low power arithmetic processors conforming to IEEE Standard 754. The multiplier/divider and ALU comprise the basic computational elements for implementing a high speed numeric processor. Operations are supported on four data formats: 32-bit IEEE single-precision floating-point, 64-bit IEEE double-precision floating-point, 32-bit twos-complement fixed-point and 32-bit unsigned-magnitude fixed-point.

The high throughput of the ADSP-3212/ADSP-3222 is achieved with only a single level of internal pipelining, greatly simplifying program development. Theoretical MFLOPS rates are much easier to approach in actual systems with this chip architecture than with alternative, more heavily pipelined chipsets. Also, the minimal internal pipelining in the ADSP-3212/ADSP-3222 results in very low latency, important in scalar processing and in algorithms with data dependencies.

Both chips have internal feedback paths from the output to four of the eight input registers and feedforward paths from all input registers to the output register. Feedback to both banks of input registers facilitates interleaving partial sums and partial products for maximum throughput.

In conforming to IEEE Standard 754, these chips assure complete software portability for computational algorithms adhering to the Sondard. All four rounding modes are supported for all floating-point data formats and conversions. Five IEEE exception conditions—overflow, underflow, invalid operation, inexact result and division-by-zero—are available externally on four status pins. The IEEE gradual underflow provisions are also supported, with special instructions for handling denormals. Alternatively, each chip offers a FAST mode which sets results less than the smallest IEEE normalized values to zero, thereby eliminating underflow exception handling when full conformance to the Standard is not essential.

IEEE floating-point division is supported by both the ADSP-3212 and the ADSP-3222. The ADSP-3212 is the faster of the two, performing single-precision division in six cycles and double-precision division in 12 cycles. The division operation is initiated by the assertion of the multiplier/divider's DIVMUL input. On the ADSP-3222 ALU two instructions, SDIV and DDIV, calculate single-precision division (16 cycles) and double-precision division (30 cycles), respectively. ADSP-3222 division instructions are supported for compatibility with the ADSP-3221.

The instruction set of the ADSP-3212/ADSP-3222, a superset of the ADSP-3210/3211/3220/3221 instruction set, is oriented to system-level implementations of function calculations. Specific instructions are included to facilitate such operations as floating-point division and square root, table lookup, quadrant normalization for trigonometric functions, extended-precision integer operations, logical operations and conversions between all data formats.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

Both chips have two input ports and eight input registers (two banks of four registers) and are always in a two-input-port configuration; data can always be input on both ports simultaneously. In the 32-bit data loading mode, input can be directed to registers in either bank, although both ports may not input to the same bank at once. If 64-bit parallel data loading is enabled, 64-bit data from both ports may be directed to one of four register pairs.

In addition to double- and single-precision floating-point multiplication and division, the ADSP-3212 Floating-Point Multiplier/Divider supports 32-bit fixed-point multiplications: twos-complement, unsigned-magnitude and mixed-mode. The ADSP-3212 also has a HOLD control that prevents the updating of the output data and status registers.

#### TABLE OF CONTENTS

| GENERAL DESCRIPTION                                                  |

|----------------------------------------------------------------------|

| FUNCTIONAL DESCRIPTION OVERVIEW                                      |

| PIN DEFINITIONS AND FUNCTIONAL BLOCK                                 |

| DIAGRAMS                                                             |

| METHOD OF OPERATION4-90                                              |

| Data Formats                                                         |

| IEEE Single-Precision Floating-Point Data Format 4-90                |

| IEEE Double-Precision Floating-Point Data Format . 4-9               |

| Supported Floating-Point Data Types                                  |

| 32-Bit Fixed-Point Data Formats.                                     |

| Supporter Floating-Point Data Types  32-Bit Fixed-Point Data Formats |

| PESET Control 4-94                                                   |

| Port Configuration - IPORT Control                                   |

| Input Pegister Loading and Operand Storage -                         |

| Input Register Loading and Operand Storage – SELA/B Controls         |

| Data Format Selection - SP & DP Controls                             |

| (ADSP-3212)                                                          |

| Input Data Register Read Selection - RDA/B Controls.4-96             |

| Feedback and Feedforward - FDBK Controls 4-96                        |

| Absolute Value - ABSA/B Controls                                     |

| Wrapped Input - WRAPA/B Controls (and INEXIN                         |

| and RNDCARI on the ADSP-3222) 4-97                                   |

| Twos-Complement Input - TCA/B Controls                               |

| (ADSP-3212)                                                          |

| Rounding - RND Controls                                              |

| Status Flags                                                         |

| Denormal                                                             |

| Invalid Operation and NAN Results                                    |

| Division-by-Zero                                                     |

| Overflow                                                             |

| Underflow                                                            |

| Inexact                                                              |

| Zero                                                                 |

| Special Flags for Unwrapping                                         |

| Instructions and Operations                                          |

| Fixed-Point Arithmetic ALU Operations                                |

| Logical ALU Operations                                               |

| Floating-Point ALU Operations                                        |

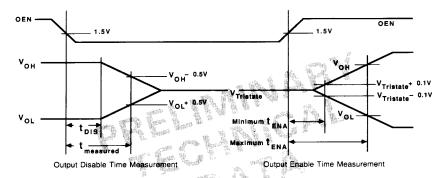

| Output Control-SHLP, OEN, MSWSEL, and HOLD .4-112                    |

| TIMING                                                               |

| GRADUAL UNDERFLOW AND IEEE EXCEPTIONS .4–113                         |

| SPECIFICATIONS                                                       |

| PINOUTS                                                              |

|                                                                      |

The instruction set of the ADSP-3222 Floating-Point ALU includes exact IEEE floating-point division and square-root operations. The ADSP-3222 is pin-compatible with the ADSP-3220/ADSP-3221. It also includes a HOLD control that is enabled through an overhead instruction.

The ADSP-3212/ADSP-3222 chipset is fabricated in doublemetal 1.0µm CMOS. Each chip consumes 2.5W maximum, significantly less than comparable bipolar solutions. The differential between the chipset's junction temperature and the ambient temperature stays small because of this low power dissipation. Thus, the ADSP-3212/ADSP-3222 can be safely specified for operation at environmental temperatures over its extended temperature range (-55°C to +125°C ambient).

The ADSP-3212/ADSP-3222 are available for both commercial and extended temperature ranges. Extended temperature range parts are available processed fully to MIL-STD-883, Class B. The ADSP-3212 and ADSP-3222 are packaged in a ceramic 144lead pin grid array.

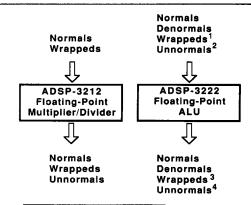

#### FUNCTIONAL DESCRIPTION OVERVIEW

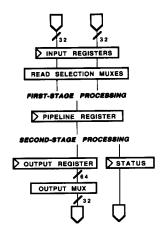

The ADSP-3212/ADSP-3222 share a common architecture (Figure 1) in which elb input data is loaded to a set of input registers with both sing and falling clock edges. Two 32-bit operates can be loaded simultaneously; alternatively, the ADSP-3212/ADSP-3222 can operate in a mode in which both halves of 66-bit operand are loaded in parallel. The input registers can be read to the child's non-metational circuitry as they are loaded on a sisting edge. At the end of first processing clock cycle, paraults and most controls are clocked into a set of internal pipeline registers. In most cases, only a second clock cycle is required to conclude processing. (The exceptions are division and square root.) At the end of this second processing cycle, results are clocked into an output register. The contents of the output register can then be driven off-chip. An output multiplexer allows driving both halves of a 64-bit double-precision result off-chip through the 32-bit output port in one output cycle.

Because all input and output data is internally registered and because of the single level of internal pipeline registers, operations can be overlapped for high levels of pipelined throughput.

Figure 1. ADSP-32XX Generic Architecture

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

#### 4-86 FLOATING-POINT COMPONENTS

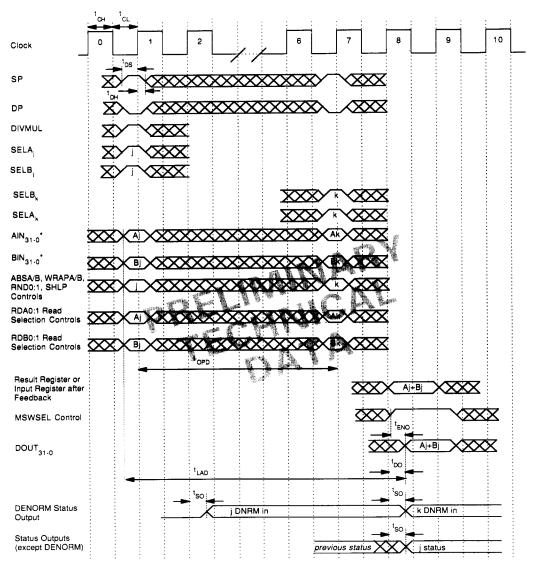

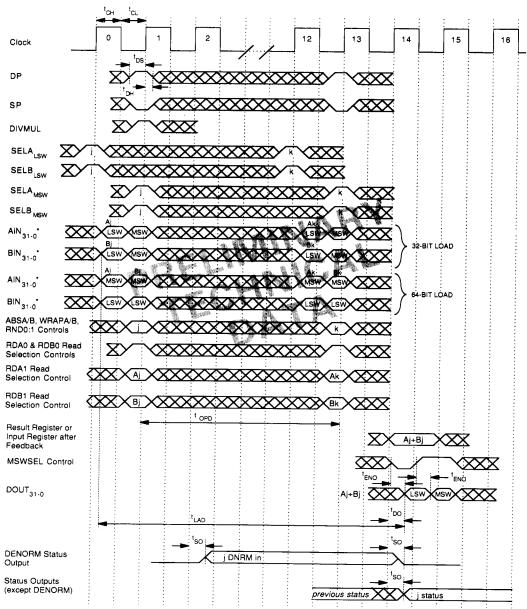

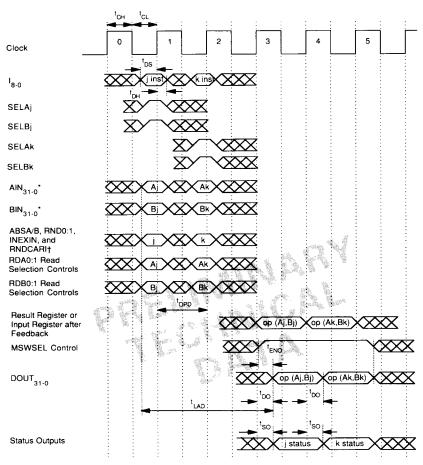

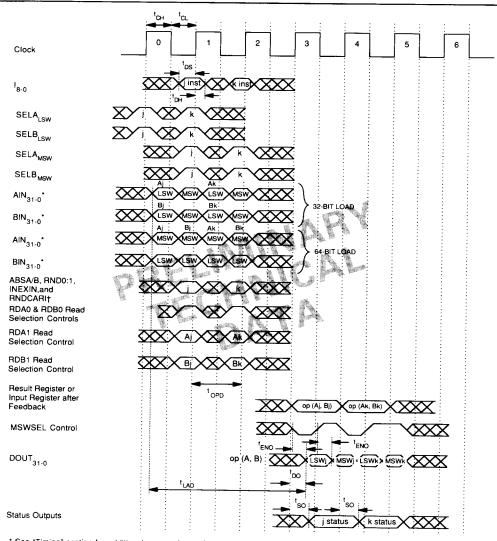

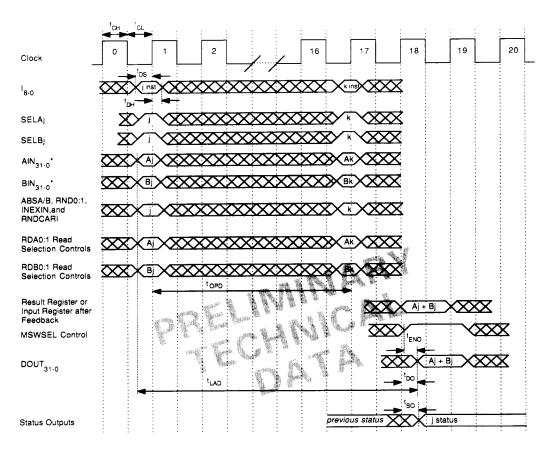

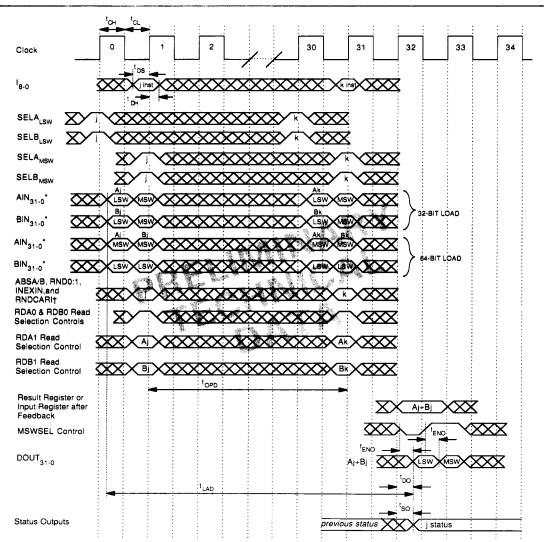

Figure 2 illustrates a typical sequence of pipelined operations. Note cycle #4 of Figure 2 after the data transfer and internal pipelines are full. While the final A results of the first operation are being driven off-chip, B processing can be concluding at the second stage, C processing beginning at the first stage and D data loading to the input registers.

| time<br>(cycles) |     | Load<br>Input Data | First-Stage<br>Processing | Second-Stage<br>Processing | Output<br>Result |  |

|------------------|-----|--------------------|---------------------------|----------------------------|------------------|--|

|                  | 1   | Data Set A         |                           |                            |                  |  |

|                  | 2   | Data Set B         | Data Set A                |                            |                  |  |

|                  | 3   | Data Set C         | Data Set B                | Data Set A                 |                  |  |

|                  | 4   | Data Set D         | Data Set C                | Data Set B                 | Data Set A       |  |

|                  | 5   | Data Set E         | Data Set D                | Data Set C                 | Data Set B       |  |

| 1                | , 1 |                    |                           |                            |                  |  |

Figure 2. Typical Pipelining with the ADSP-3212/ADSP-3222

The ADSP-3212/ADSP-3222 can load data on rising edges of the clock and on falling edges of the clock, subject to constraints described in "Method of Operation." The ADSP-3212/ADSP-3222 can also operate in a mode in which all 64 bits of a double-precision word are loaded into an input register pair in parallel. This mode allows direct connection to a 64-bit input bus. All input registers have their own independent load selection controls, allowing the same data to be loaded to multiple registers simultaneously.

A set of read selection multiplexers feeds input data from the input registers to the computational circuitry. These multiplexers can select data that was just loaded at the clock's rising edge, if desired, with no throughput or cycle-time penalty.

All control signals need only be supplied to the chips at their cycle rate. This approach avoids requiring that the sequencing control cycle time be faster than the chipset's major processing cycle rate. Less expensive microcode memory can therefore be used. For this reason, load selection controls for registers to be loaded on the clock's falling edge need only be valid at the previous rising edge. (The designer may choose to supply the asynchronous port configuration, output multiplexer and tristate controls at a higher rate, however.)

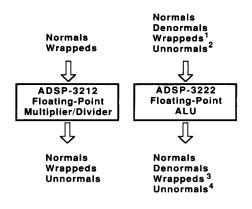

The ADSP-3212/ADSP-3222 fully supports the gradual underflow provisions of IEEE Standard 754 for floating-point arithmetic. The Floating-Point ALU can operate directly on both normals and denormals (except division and square root). The Floating-Point Multiplier/Divider operates on normals but cannot operate on denormals directly. Denormals must first be "wrapped" (converted to a format acceptable for multiplication, division or square root) by an ALU. Several flags are available for detecting and handling exceptions caused by loading a denormal into a Floating-Point Multiplier/Divider. Information about rounding and inexact results generated by the multiplier/divider is needed by the ALU to produce results in conformance to Standard 754. Both ADSP-3212/ADSP-3222 chips include a

"FAST" control that flushes all denormalized results to zero, avoiding the system delays of IEEE exception processing for gradual underflow.

All status output flags except denormal detection are registered at the output in parallel with their associated results. The asynchronous denormal flag allows an early detection of a denormalized number loaded to a Floating-Point Multiplier/Divider, speeding exception processing.

# PIN DEFINITIONS AND FUNCTIONAL BLOCK DIAGRAMS

All control pins are active HI (positive true logic naming convention), except RESET and HOLD. Some controls are registered at the clock's rising edge (REG); other controls are latched in clock HI and transparent in clock LO (LAT), and others are asynchronous (ASYN).

# ADSP-3212 FLOATING-POINT MULTIPLIER/DIVIDER PIN LIST

|     | Pin Name             | Description                            | Туре |

|-----|----------------------|----------------------------------------|------|

| 1   | DATA PINS            | S                                      | -32- |

|     | AIN <sub>31-0</sub>  | 32-Bit Data Input                      |      |

| *   | BIN <sub>31-0</sub>  | 32-Bit Data Input                      |      |

| æ   | DOUT <sub>11-0</sub> | 32-Bit Data Output                     |      |

|     | CONTROL              | · •                                    |      |

| *   | RESET                | Reset                                  | ASYN |

|     | HOLD                 | Hold Control                           | LAT  |

|     | IPORT                | Input Port Configuration Control       | ASYN |

| þ   | SELA0                | Load Selection for A0                  | LAT  |

| 811 | SELA1                | Load Selection for A1                  | LAT  |

|     | SELA2                | Load Selection for A2                  | LAT  |

|     | SELA3                | Load Selection for A3                  | LAT  |

|     | SELB0                | Load Selection for B0                  | LAT  |

|     | SELB1                | Load Selection for B1                  | LAT  |

|     | SELB2                | Load Selection for B2                  | LAT  |

|     | SELB3                | Load Selection for B3                  | LAT  |

|     | RDA0                 | Register Ax Read Selection Control 0   | REG  |

|     | RDA1                 | Register Ax Read Selection Control 1   | REG  |

|     | RDB0                 | Register Bx Read Selection Control 0   | REG  |

|     | RDB1                 | Register Bx Read Selection Control 1   | REG  |

|     | WRAPA                | Wrapped Contents in Register Ax        | REG  |

|     | WRAPB                | Wrapped Contents in Register Bx        | REG  |

|     | TCA                  | Twos-Complement Integer in Register Ax | REG  |

|     | TCB                  | Twos-Complement Integer in Register Bx | REG  |

|     | ABSA                 | Read Absolute Value of Ax              | REG  |

|     | ABSB                 | Read Absolute Value of Bx              | REG  |

|     | SP                   | Single-Precision Mode                  | REG  |

|     | DP                   | Double-Precision Mode                  | REG  |

|     | RND0                 | Rounding Mode Control 0                | REG  |

|     | RND1                 | Rounding Mode Control 1                | REG  |

|     | FAST<br>SHLP         | Fast Mode                              | REG  |

|     | SHLP<br>FDBK0        | Shift Left Fixed-Point Product         | REG  |

|     | FDBK1                | Feedback Control 0                     | REG  |

|     | LOAD64               | Feedback Control 1                     | REG  |

|     | DIVMUL               | Enable 64-Bit Parallel Input           | REG  |

|     | MSWSEL               | Divide/Multiply                        | REG  |

| _   | DEN                  | Select MSW of Output Register          | ASYN |

| ١,  | JUIN                 | Output Data Enable                     | ASYN |

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

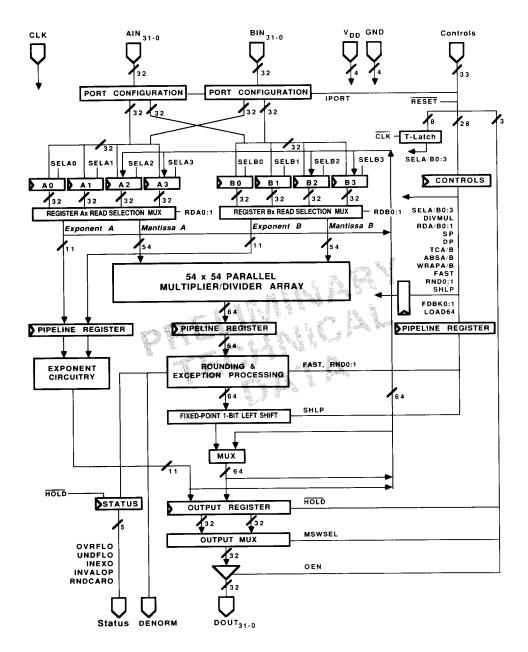

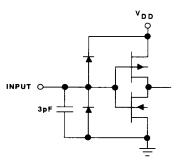

Figure 3. ADSP-3212 Block Diagram

#### 4-88 FLOATING-POINT COMPONENTS

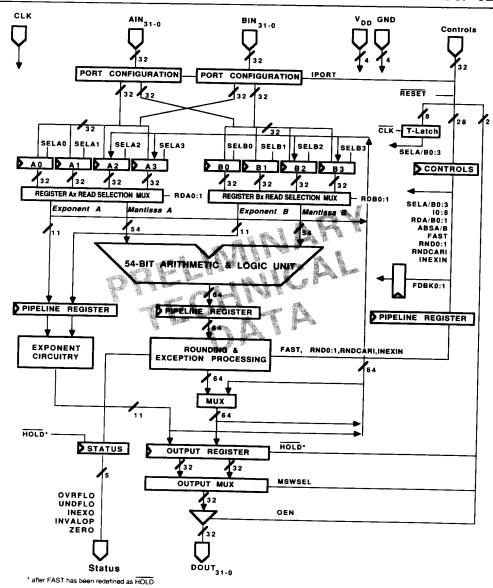

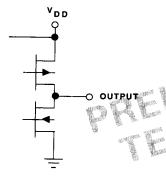

Figure 4. ADSP-3222 Block Diagram

| Pin Name  | Description                   | Туре |

|-----------|-------------------------------|------|

| STATUS OU | TT                            |      |

| INEXO     | Inexact Result                |      |

| OVRFLO    | Overflowed Result             |      |

| UNDFLO    | Underflowed Result            |      |

| INVALOP   | Invalid Operation             |      |

| DENORM    | Denormal Output               |      |

| RNDCARO   | Round Carry Propagation Out   |      |

| MISCELLA  | NEOUS                         |      |

| CLK       | Clock Input                   |      |

| $V_{DD}$  | +5V Power Supply (four lines) |      |

| GND       | Ground Supply (four lines)    |      |

#### ADSP-3222 FLOATING-POINT ALU PIN LIST

| ADSP-3222 F          | LOATING-POINT ALU PIN LIST           |      |

|----------------------|--------------------------------------|------|

| Pin Name             | Description                          | Type |

| DATA PINS            |                                      |      |

| AIN <sub>31-0</sub>  | 32-Bit Data Input                    |      |

| BIN <sub>31-0</sub>  | 32-Bit Data Input                    |      |

| DOUT <sub>31-0</sub> | 32-Bit Data Output                   |      |

| CONTROL P            | INS                                  |      |

| RESET                | Reset                                | ASYN |

| IPORT                | Input Port Configuration Control     | ASYN |

| SELA0                | Load Selection for A0                | LAT  |

| SELA1                | Load Selection for Al                | LAT  |

| SELA2                | Load Selection for A2                | LAT  |

| SELA3                | Load Selection for A3                | LAT  |

| SELBO                | Load Selection for B0                | LAT  |

| SELBI                | Load Selection for B1                | LAT  |

| SELB1                | Load Selection for B2                | LAT  |

| SELB2                | Load Selection for B3                | LAT  |

| RDA0                 | Register Ax Read Selection Control 0 | REG  |

| RDA1                 | Register Ax Read Selection Control 1 | REG  |

| RDB0                 | Register Bx Read Selection Control 0 | REG  |

| RDB1                 | Register Bx Read Selection Control 1 | REG  |

| ABSA                 | Read Absolute Value of Ax            | REG  |

| ABSB                 | Read Absolute Value of Bx            | REG  |

| I <sub>8-0</sub>     | ALU Instruction                      | REG  |

| RND0                 | Rounding Mode Control 0              | REG  |

| RND1                 | Rounding Mode Control 1              | REG  |

| FAST                 | Fast Mode/HOLD Control               | REG  |

| FDBK0                | Feedback Control 0                   | REG  |

| FDBK1                | Feedback Control 1                   | REG  |

| MSWSEL               | Select MSW of Output Register        | ASYN |

| OEN                  | Output Data Enable                   | ASYN |

| STATUS IN            |                                      |      |

| INEXIN               | Inexact Data In                      | REG  |

| RNDCARI              | Round Carry Propagation In           | REG  |

| STATUS OU            | * * -                                |      |

|                      | Inexact Result                       |      |

| INEXO<br>OVRFLO      | Overflowed Result                    |      |

| UNDFLO               | Underflowed Result                   |      |

| INVALOP              | Invalid Operation                    |      |

| ZERO                 | Zero Result                          |      |

|                      |                                      |      |

| MISCELLAN            |                                      |      |

| CLK                  | Clock Input                          |      |

| $V_{DD}$             | +5V Power Supply (four lines)        |      |

#### METHOD OF OPERATION

#### Data Formats

The ADSP-3212/ADSP-3222 chipset supports both single- and double-precision floating-point data formats and operations as defined in IEEE Standard 754-1985. Both chips support 32-bit twos-complement fixed-point as well as 32-bit unsigned-magnitude data formats and operations (the ADSP-3212 supports fixed-point multiplication but not fixed-point division). Both chips operate directly on 32-bit fixed-point data. No time consuming conversions to and from floating-point formats are required.

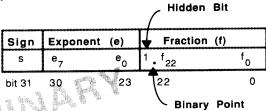

# IEEE Single-Precision Floating-Point Data Format IEEE Standard 754 specifies a 32-bit single-precision floating-point format, which consists of a sign bit s, a 24-bit significand

Figure 5. IEEE Single-Precision Floating-Point Format

and an 8-bit unsigned-magnitude exponent e. For normalized numbers, this significand consists of a 23-bit fraction f and a "hidden" bit of 1 that is implicitly presumed to precede  $f_{22}$  in the significand. The binary point is presumed to lie between this hidden bit and  $f_{22}$ . The least significant bit of the fraction is  $f_0$ ; the LSB of the exponent is  $e_0$ . The hidden bit effectively increases the precision of the floating-point significand to 24 bits from the 23 bits actually stored in the data format. It also insures that the significand of any number in the IEEE normalized-number format is always greater than or equal to 1 and less than 2.

The unsigned exponent e for normals can range between  $1 \le e \le 254$  in the single-precision format. This exponent is biased by +127 (254+2) in the single-precision format. This means that to calculate the "true" unbiased exponent, 127 must be subtracted from e.

The IEEE Standard also provides for several special data types. In the single-precision floating-point format, an exponent value of 255 (all ones) with a non-zero fraction is a not-a-number (NAN). NANs are usually used as flags for data flow control, for the values of uninitialized variables and for the results of invalid operations such as 0.000. Infinity is represented as an exponent of 255 and a zero fraction. Note that because the fraction is signed, both positive and negative INF can be represented.

The IEEE Standard requires the support of denormalized data formats and operations. A denormalized number, or "denormal," is a number with a magnitude less than the minimum normalized ("normal") number in the IEEE format. Denormals have a zero exponent and a non-zero fraction. Denormals have no hidden "one" bit. (Equivalently, the hidden bit of a denormal is zero.) The unbiased (true) value of a denormal's exponent is -126 in the single-precision format, i.e., one minus the exponent bias. Note that because denormals are not required to have a significant leading one bit, the precision of a denormal's significand can be as little as one bit for the minimum representable denormal.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

#### 4-90 FLOATING-POINT COMPONENTS

Ground Supply (four lines)

GND

## ADSP-3212/ADSP-3222

ZERO is represented by a zero exponent and a zero fraction. As with INF, both positive ZERO and negative ZERO can be represented.

The IEEE single-precision floating-point data types and their interpretations are summarized:

| Mnemonic | Exponent      | Fraction | Value                                     | Name         | IEEE Format? |  |

|----------|---------------|----------|-------------------------------------------|--------------|--------------|--|

| NAN      | 255           | non-zero | undefined                                 | not-a-number | yes          |  |

| INF      | 255           | zero     | (-1)*(infinity)                           | infinity     | yes          |  |

| NORM     | 1 thru 254    | any      | (-1)*(1.f)2*-127                          | normal       | yes          |  |

| DNRM     | 0             | non-zero | (-1) <sup>8</sup> (0.f)2 <sup>-126</sup>  | denormal     | yes          |  |

| ZERO     | 0             | zero     | (-1) <sup>8</sup> 0.0                     | zero         | yes          |  |

| WRAP     | -22 thru 0    | any      | (-1) <sup>6</sup> (1.f)2 <sup>6-127</sup> | wrapped      | no           |  |

| UNRM     | -171 thru -23 | any      | (-1) <sup>e</sup> (1.f)2 <sup>e-127</sup> | unnormal     | no           |  |

Table I. IEEE Single-Precision Floating-Point Data Types and Interpretations

The ADSP-3212/ADSP-3222 chipset also supports two data types not included in the IEEE Standard, "wrapped" and "unnormal." These data types are necessitated by the fact that the ADSP-3222 ALU (during division and square root) and the ADSP-3212 Multiplier/Divider do not operate directly on denormals. (To do so, they would need shifting hardware that would slow them significantly.) Denormal operate is use first be translated by the ADSP-3222 ALU to the problem of the pr

The interpretation of wrapped numbers differs from normal only in that the exponent is treated as a twos-complement number. Single-precision wrapped numbers have a hidden bit of one and an exponent bias of +127. All single-precision denormals can be mapped into wrapped numbers where the exponent e ranges between  $-22 \le e \le 0$ . WRAPA and WRAPB controls on the ADSP-3212 tell the multiplier/divider to interpret a data value as a wrapped number.

The ranges of the various single-precision IEEE floating-point data formats supported by the ADSP-3212/ADSP-3222 are summarized in Table II.

The multiplication of a wrapped number by a normal number or another wrapped number can produce a number smaller than can be represented as a wrapped number. Such numbers are called "unnormals." Unnormals are interpreted exactly as are wrapped numbers. They differ only in the range of their exponents, which is  $-171 \le e \le -23$  for single-precision unnormals. The smallest unnormal is the result of multiplying WRAP.MIN by itself. Unnormals, because they are smaller than DRNM.MIN, generally unwrap to ZERO. (Unnormals can unwrap to DRNM.MIN, depending on the rounding mode.)

The underflow flag should be thought of as an implicit most significant ninth bit, the sign bit. For unnormals for which  $-171 \le e < -128$ , the most significant bit in the eight-bit exponent field (e<sub>7</sub>, Bit 30) will be zero, but the underflow flag understood as weighted by -256 allows their representation without ambiguity. This sign bit is implicitly assumed by the ALU to be present when unwrapping unnormals, making this convention for very small unnormals transparent to the user.

| Data name<br>(positive) | Exponent | Exp. date<br>type | Exponent<br>blas | Hidden<br>bit | Fraction<br>(binary) | Unbiased absolute value |

|-------------------------|----------|-------------------|------------------|---------------|----------------------|-------------------------|

| NORM.MAX                | 254      | unsigned          | +127             | 1             | 11111                | 2+127 (2-2-23)          |

| NORM.MIN                | 1        | unsigned          | +127             | 1             | 00000                | 2-126                   |

| DNRM.MAX                | 0        | unsigned          | +126             | 0             | 11111                | 2-126 - (1-2 -23        |

| DNRM.MIN                | 0        | unsigned          | +126             | 0             | 00001                |                         |

| WRAP.MAX                | 0        | 2scmplmt          | +127             | 1             | 11111                | 2-127 (2-2-23)          |

| WRAP.MIN                | -22      | 2scmplmt          | +127             | 1             | 00000                | 2-149                   |

| UNRM.MAX                | -23      | 2scmplmt          | +127             | 1             | 11111                | 2-150 (2-2-23)          |

| UNRM.MIN                | -171     | 2scmplmt          | +127             | 1             | 00000                | 2-298                   |

Table II. IEEE Single-Precision Floating-Point Range Limits

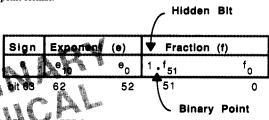

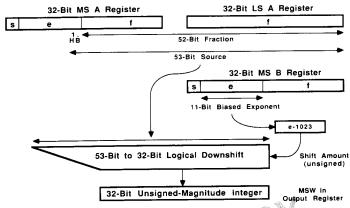

IEEE Double-Precision Floating-Point Data Format IEEE Standard 754 specifies a 64-bit double-precision floatingpoint format:

Figure 6. IEEE Double-Precision Floating-Point Format

The key differences with the single-precision format are that the expenente in now 11 bits in length and the fraction f is now 52 bits in length, yielding a 53-bit significand for double-precision normals. Double-precision, like single-precision, has an implicit hidden bit; in this case the hidden bit precedes  $f_{51}$ . The binary point comes between the hidden bit and  $f_{51}$ . The exponent bias for double-precision floating-point normals is +1023 (2046+2).

In other respects, IEEE double-precision floating-point is exactly analogous to single-precision, with the same data types whose values are summarized in Table III.

The unbiased value of a denormal's exponent is -1022 for double-precision denormals, i.e., one minus the bias. Because of the extended width of the double-precision fraction, the exponent of double-precision wrapped numbers can range from  $-51 \le e \le 0$ . The exponent of unnormals can range from  $-1125 \le e \le -52$ . Again, the smallest unnormal is the result of multiplying the smallest wrapped number by itself. Note that e = -1024 is the smallest double-precision exponent that is directly representable in the eleven-bit IEEE twos-complement exponent field. The underflow flag should be thought of as a most significant twelfth bit, the sign bit, as explained above for single-precision unnormals.

| Mnemonic | Exponent       | Fraction | Value                                      | Name         | IEEE Format? |

|----------|----------------|----------|--------------------------------------------|--------------|--------------|

| NAN      | 2047           | non-zero | undefined                                  | not-a-number | yes          |

| INF      | 2047           | zero     | (-1) <sup>S</sup> (infinity)               | infinity     | yes          |

| NORM     | 1 thru 2046    | any      | (-1) <sup>8</sup> (1.f)2 <sup>e-1023</sup> | normal       | yes          |

| DNRM     | 0              | non-zero | (-1) <sup>s</sup> (0.f)2 <sup>-1022</sup>  | denormal     | yes          |

| ZERO     | 0              | zero     | (-1) <sup>S</sup> 0.0                      | zero         | yes          |

| WRAP     | -51 thru 0     | any      | (-1) <sup>s</sup> (1.f)2 <sup>e-1023</sup> | wrapped      | no           |

| UNRM     | -1125 thru -52 | any      | (-1) <sup>8</sup> (1.f)2 <sup>e-1023</sup> | unnormal     | no           |

Table III. IEEE Double-Precision Floating-Point Data Types and Interpretations

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

The ranges for the various double-precision data types are:

| Data name<br>(positive) | Exponent | Exp. data<br>type | Exponent<br>bias | Hidden<br>bit | Fraction<br>(binary) | Unbiased absolute value                  |

|-------------------------|----------|-------------------|------------------|---------------|----------------------|------------------------------------------|

| NORM.MAX                | 2046     | unsigned          | +1023            | 1             | 11111                | 2+1023 (2-2-52)                          |

| NORM.MIN                | 1        | unsigned          | +1023            | 1             | 00000                | 2-1022                                   |

| DNRM.MAX                | 0        | unsigned          | +1022            | 0             | 11111                | 2-1022 • (1-2-52)                        |

| DNRM.MIN                | 0        | unsigned          | +1022            | 0             | 00001                | 2-1022 -2-52                             |

| WRAP.MAX                | 0        | 2scmplmt          | +1023            | 1             | 11111                | 2 <sup>-1023</sup> (2-2 <sup>-52</sup> ) |

| WRAP.MIN                | -51      | 2scmplmt          | +1023            | 1             | 00000                | 2-1074                                   |

| UNRM.MAX                | -52      | 2scmplmt          | +1023            | 1             | 11111                | 2 <sup>-1075</sup> (2-2 <sup>-52</sup> ) |

| UNRM.MIN                | -1125    | 2scmplmt          | +1023            | 1             | 00000                | 2 <sup>-2148</sup>                       |

Table IV. IEEE Double-Precision Floating-Point Range Limits

#### Supported Floating-Point Data Types

The floating-point data types supported directly by the ADSP-3212/ADSP-3222 chipset are summarized in Figure 7.

Not all the data types described above are supported directly. See the section below, "Gradual Underflow and IEEE Exceptions" for a full description of how the chips work together to implement the IEEE Standard. For systems not requiring full conformance to Standard 754, the section below, "FAST/IEEE Control," describes a simplified operation for this chipset that avoids denormals, wrappeds, and unnormals altogether.

#### 32-Bit Fixed-Point Data Formats

The ADSP-3212/ADSP-3222 chipset supports two 32-bit fixed-point formats: twos-complement and unsigned-magnitude. With the ALU, the output data format is identical with the input data format, i.e., 32 bits wide. In contrast, the multiplicydivider produces a 64-bit product from two 32-bit inputs. Fixed-point division and fixed-point square root are not supported directly. However, they can be accomplished using the fixed-point/floating-point conversions.

I. for unwrapping, division, and square root

Figure 7. Data Types Directly Supported by the ADSP-3212/ADSP-3222

The 32-bit twos-complement data format for ALU inputs and outputs and multiplication inputs is:

| WEIGHT   | Sign<br>- 2 <sup>k+31</sup> | 2 <sup>k+30</sup> | 2 <sup>k+29</sup> | ••• | _k<br>2        |

|----------|-----------------------------|-------------------|-------------------|-----|----------------|

| VALUE    | i <sub>31</sub>             | i <sub>30</sub>   | i <sub>29</sub>   | ••• | i <sub>o</sub> |

| POSITION | 3 1                         | 3 0               | 29                |     | 0              |

Figure 8. 32-Bit Twos-Complement Fixed-Point Data Format

The MSB is  $i_{31}$ , which is also the sign bit; the LSB is  $i_0$ . Note that the sign bit is negatively weighted in twos-complement format. The position of the binary point for fixed-point data is represented here in full generality by the integer k. Integers (binary point to right of bit position 0) are represented when k=0; signed fractional numbers (binary point between bit positions 31 and 30) are represented when k=-31. The value of k is for user interpretation only and in general does not affect the operation of the chips. The only exceptions are the ALU conversion operations between floating-point and fixed-point. For these operations, the fixed-point format is presumed to be twos-complement integers, i.e., k=0.

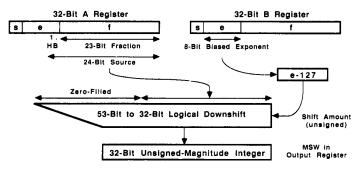

The ADSP 3212 Multiplies/Divider can produce a 64-bit product at its output register. The ADSP-3212 will produce results in the format of Figure 9 at the DOUT port if the Shift Left Fixed-Point Product (SHLP) control (described below in "Output Control") is LO:

| WEIGHT   | Sign<br>-2 <sup>r+63</sup> | 2 <sup>r+62</sup> | <br>2 + 32 | 2 <sup>r+31</sup> | <br>2 r+1 | 2  |

|----------|----------------------------|-------------------|------------|-------------------|-----------|----|

| VALUE    | 1 <sub>63</sub>            | 1 <sub>62</sub>   | <br>132    | 131               | <br>1,    | 10 |

| POSITION | 63                         | 62                | <br>3 2    | 31                | <br>1     | 0  |

Most Significant Product

Least Significant Product

Figure 9. 64-Bit Twos-Complement Fixed-Point Data Format at Multiplier/Divider Output Register with SHLP LO

The weighting of the product bits is given by the integer r. When  $k_A$  represents the weighting of operand A and  $k_B$  the weighting of operand B, then  $r = k_A + k_B$ .

When HI, the SHLP control shifts all bits left one position as they are loaded to the output register. The results will then be in the format:

| WEIGHT   | Sign<br>- 2 <sup>r+62</sup> | r+61<br>2        | <br>2 <sup>r+31</sup> | 2 +30 | <br>2  | 2'-1 |

|----------|-----------------------------|------------------|-----------------------|-------|--------|------|

| VALUE    | i <sub>6 2</sub>            | i <sub>6 1</sub> | <br>i <sub>31</sub>   | 130   | <br>10 | 0    |

| POSITION | 63                          | 62               | <br>3 2               | 3 1   | <br>1  | 0    |

Most Significant Product

Least Significant Product

Figure 10. 64-Bit Twos-Complement Fixed-Point Data Format at Multiplier/Divider Output Register with SHLP HI

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

#### 4-92 FLOATING-POINT COMPONENTS

<sup>2.</sup> for unwrapping only

<sup>3.</sup> from wrapping and division

<sup>4.</sup> from division

## ADSP-3212/ADSP-3222

The LSB becomes zero and  $i_{62}$  moves into the sign bit position. Normally  $i_{63}$  and  $i_{62}$  will be identical in twos-complement products. (The only exception is full-scale negative multiplied by itself.) Hence, a one-bit left-shift normally removes a redundant sign bit, thereby increasing the precision of the most significant product. Also, if the fixed-point data format is fractional (k=-31 in Figure 8), then a single-bit left-shift will renormalize the MSP to a fractional format (because r=2\*k=2\*(-31)=-62).

For unsigned-magnitude data formats, inputs to the ADSP-3212 Multiplier/Divider and inputs and outputs for the ADSP-3222 ALU will be 32-bits wide. The 32-bit unsigned-magnitude data format is:

| WEIGHT   | 2 k+31          | 2k+30           | 2 <sup>k+29</sup> | <br>2 <sup>k</sup> |

|----------|-----------------|-----------------|-------------------|--------------------|

| VALUE    | l <sub>31</sub> | <sup>i</sup> 30 | i <sub>29</sub>   | <br>i <sub>o</sub> |

| POSITION | 3 1             | 30              | 29                | <br>0              |

Figure 11. 32-Bit Unsigned-Magnitude Fixed-Point Data Format

Again, the position of the binary point for fixed-point data is represented here in full generality by the integer k. Integers (binary point to the right of bit position 0) are represented when k=0; unsigned fractional numbers (binary point left of bit position 31) are represented when k=-32. The value of k is for user interpretation only and, except for conversions to fixed-point, does not affect the operation of the chips.

The ADSP-3212 Multiplier/Divider discriminates twoscomplement from unsigned-magnitude inputs with TCA and TCB controls (see "Controls"). When TCA and TCB are both LO, the ADSP-3212 produces a 64-bit unsigned-magnitude product at its output register. The ADSP-3212 will produce results in this format if SHLP is LO:

| WEIGHT   | 2 *+63          | 2 +62           |         | 2 +32            | 2 <sup>r+31</sup> | <br>2 r+1          | 2  |

|----------|-----------------|-----------------|---------|------------------|-------------------|--------------------|----|

| VALUE    | l <sub>63</sub> | 1 <sub>62</sub> | <b></b> | i <sub>3 2</sub> | l <sub>31</sub>   | <br>i <sub>1</sub> | 10 |

| POSITION | 63              | 6 2             | T       | 3 2              | 3 1               | <br>1              | 0  |

Most Significant Product

Least Significant Product

Figure 12. 64-Bit Unsigned-Magnitude Fixed-Point Data Format at Multiplier/Divider Output Register with SHLP LO

Again, the weighting of the product bits is given by the integer r. When  $k_A$  represents the weighting of operand A and  $k_B$  the weighting of operand B, then  $r = k_A + k_B$ .

If SHLP is HI, the data at the output register will have been shifted left one position and zero-filled in the format shown in Figure 13.

| WEIGHT   | 2 r+62           | r+61<br>2       | <br>2 <sup>r+31</sup> | 2 r+30          | ••• | 2 <sup>r</sup> | 2 r-1  |

|----------|------------------|-----------------|-----------------------|-----------------|-----|----------------|--------|

| VALUE    | i <sub>6 2</sub> | i <sub>61</sub> | <br><sup>j</sup> 31   | i <sub>30</sub> |     | 10             | 0      |

| POSITION | 63               | 6 2             | <br>3 2               | 3 1             |     | 1              | 0      |

|          |                  |                 |                       | ·               |     | *              | ······ |

Most Significant Product

Least Significant Product

Figure 13. 64-Bit Unsigned-Magnitude Fixed-Point Data Format at Multiplier/Divider Output Register with SHLP HI

The ADSP-3212 also supports mixed-mode multiplications, i.e., twos-complement by unsigned-magnitude. These are valuable in extended-precision fixed-point multiplications, e.g., 64×64 and 128×128. The result of a mixed-mode multiplication will be in a twos-complement format. Unlike twos-complement multiplications, however, mixed-mode results do not in general have a redundant sign bit in i<sub>62</sub>. Hence, mixed-mode results should be read out with SHLP LO as in Figure 9.

#### Controls

The controls for the ADSP-3212/ADSP-3222 (see Pin Definitions above) are all active HI, with the exceptions of RESET and HOLD. The controls are either registered into the input control register at the clock's rising edge, latched into the input control register with clock HI and transparent in clock LO, or asynchronous. The controls are discussed below in the order in which they affect data flowing through the chipset.

Registered controls, in general, are pipelined to match the flow of data. All data and control pipelines advance with the rising edge of each clock cycle. For example, to perform an optional fixed-point one-bit left-shift on output with the product of X and Y, you would assert the registered, pipelined control SHLP on the rising edge that causes X and Y inputs to be read into the multiplier array. Just before the result was ready to be loaded to the output register, the pipelined SHLP control would perform the proper shift. After the initiation of a multi-cycle operation, registered control inputs are ignored until the end of the operation time. (See "Timing" below for a precise definition of "operation time.")

Because this chipset uses CMOS static logic throughout and controls are pipelined, the clock can be stopped as long as desired for generating wait-states, diagnostic analysis, or whatever. These chips can also be easily adapted to "state-push" implementations. The machine's state can be pushed forward one stage by simply providing a rising edge to the clock input when desired.

The only controls that are latched (as opposed to registered) are the Load Selection Controls. They are transparent in clock LO and latched with clock HI. Load selection controls are set up to the chips exactly as if they were registered, with the same setup time. The fact that they are transparent in clock LO allows them to select input registers in parallel with the setup of data to be loaded on the rising edge. Because they are latched with clock HI, microcode need only be presented at the clock rate, though data is loaded on both clock rising and falling edges.

A few controls are asynchronous. These controls take effect immediately and are thus neither registered nor pipelined. Each has an independently specified setup time.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

#### FAST/IEEE Control (REG)

FAST is a pipelined, registered control. It affects the interpretation of data read into processing circuitry immediately after having been loaded to the input control register. FAST affects the format of results in the rounding and exception processing pipeline stage. FAST also affects the definition of some exception flags (see "Status Flags").

IEEE Standard 754 requires a system to perform operations on denormal operands (which are smaller in magnitude than the minimum representable normalized number). This capability to accommodate these numbers is known as "gradual underflow." For floating-point systems not requiring strict adherence to the IEEE Standard, the ADSP-3212/ADSP-3222 provides a FAST mode (FAST control pin HI) which consistently flushes postrounded results less than NORM.MIN to ZERO. This approach greatly simplifies exception processing and avoids generating the denormal, wrapped, and unnormal data types described above. When in FAST mode, the multiplier/divider will treat denormal inputs as ZERO. The ALU will treat denormal inputs exactly as it does in IEEE mode but still flush post-rounded results less than NORM.MIN to ZERO.

Systems implementing gradual underflow with the ADSP-3212/ ADSP-3222 must treat the multiplication of operands that include a denormal as an exception to normal process flow. FAST should be LO on all chips. See the section below, "Gradual Viderflow and IEEE Exceptions," for a fuller discussion of the details of implementing an IEEE system with the section below.

On the ADSP-3222, the FAST input on be tedefined after reset as a HOLD input through the HOLDEN instruction (see Table XIII). The mode (IEEE or FAST) that it active when the instruction is executed remains in effect. To resture the FAST function, you must reset the ADSP-3222.

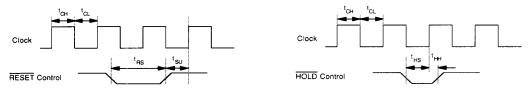

#### RESET Control (ASYN)

The asynchronous, active LO RESET control clears all control functions in the ADSP-3212/ADSP-3222. RESET should be asserted on power up to insure proper initialization. (RESET will abort any multicycle operation in progress.) Status flags are cleared by RESET. No input register contents are affected by RESET; however, the output register can be invalidated if RESET is asserted LO during a multicycle operation. All load selection controls (SELA/B) must be LO at RESET.

On reset, the ADSP-3222 is set for 32-bit input data loads and for the IEEE/FAST function on its FAST input.

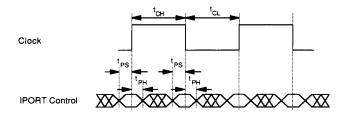

#### Port Configuration - IPORT Control (ASYN)

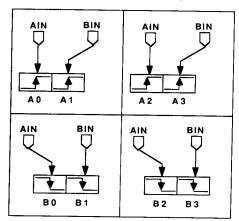

This chipset offers two options on input port configuration. Both configurations in Figure 14 are "two-port" configurations. The options are controlled by the asynchronous input IPORT, which allows you to switch the port configuration dynamically—as often as every half cycle. Take care that IPORT is at valid logic levels at all clock edges at which data is loaded. IPORT must meet setup and hold times at every point at which data is loaded—a rising edge or falling edge of the clock. Proper data loading cannot be guaranteed unless this requirement is observed.

| IPORT | PORT CONF       | IGURATION          |

|-------|-----------------|--------------------|

| 0     | AIN A registers | BIN<br>B registers |

| 1     | AIN A registers | BIN<br>B registers |

Figure 14. ADSP-3212/ADSP-3222 Input Port Configurations

# Input Register Loading and Operand Storage - SELA/B Controls (LAT)

The chipset's 2-b. is out ligisters are selected for data loading with the late edited selection controls, SELA0:3 and SELB0:3. Since each imput register has its own control, the load selection to a rots are independent of one another. Multiple registers can be selected for parallel lacks of the same input data, if desired. The load election controls' effects on data loading are summanated in signific 15.

| SEL control | register<br>loaded |  |

|-------------|--------------------|--|

| SELA0       | A0                 |  |

| SELA1       | A1                 |  |

| SELA2       | A2                 |  |

| SELA3       | A3                 |  |

| SELBO       | B0                 |  |

| SELB1       | B1                 |  |

| SELB2       | B2                 |  |

| SELB3       | B3                 |  |

Figure 15. ADSP-3212/ADSP-3222 Load Selection Controls

For 32-bit data loading, even-numbered registers load data on rising edges and odd-numbered registers on falling edges, as shown in Figure 16. However, you should not load a 32-bit register on the clock's falling edge in the same cycle that the register is read into the chip's processing circuits (see "Restrictions on Register Storage," below).

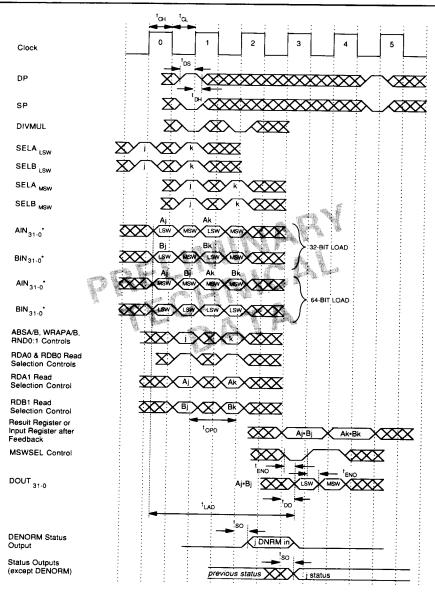

In the 64-bit parallel loading mode, inputs from both ports can be directed to appropriate register pairs (see "Restrictions on Register Storage," below). This mode is enabled by the LOAD64 pin on the ADSP-3212; on the ADSP-3222, the LOAD64 instruction sets 64-bit loading until the next reset. If

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

4-94 FLOATING-POINT COMPONENTS

A registers are selected, they are loaded on the rising edge of the clock; B registers are loaded on the falling clock edge. LOAD64 is pipelined for one cycle on both parts; that is, the 64-bit load option will become effective at the *next* rising edge after the pin is asserted or the instruction is presented.

Figure 16. ADSP-3212/ADSP-3222 Clock Edge for 32-Bit Data Loading

#### Restrictions on Register Storage

For single-precision and fixed-point data, any convenient register can be used. The only restriction is that the register being loaded is not currently in use by the chip's processing elements. For all multiplications and most ALU operations, input registers are only read into the computational circuits for one cycle. Do not load a register for 32-bit operations on the clock's falling edge when that register has been selected to feed the chip's processing circuits in that same cycle (with the RDA/B controls described in "Input Data Register Read Selection"). Pick a register not in use.

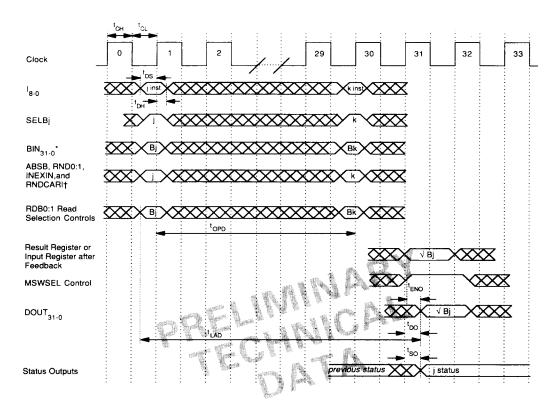

The ADSP-3222 ALU is capable of two multicycle operations: IEEE floating-point division (16 cycles for single precision and 30 cycles for double precision) and square root (29 cycles for single precision and 58 cycles for double precision). The ADSP-3212 Multiplier/Divider performs multicycle (6 and 12 cycles for single precision and double precision, respectively) floating-point division. For single-precision floating-point division, the dividend can be stored in any A register and the divisor can be stored in any B register. The registers selected to the computational circuits for these operations must be

Figure 17. ADSP-3212/ADSP-3222 64-Bit Parallel Load

stable until the end of the operation time, whether singleprecision or double-precision. (See "Timing" and the timing diagrams below for a precise definition of "operation time.")

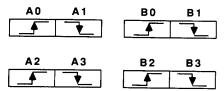

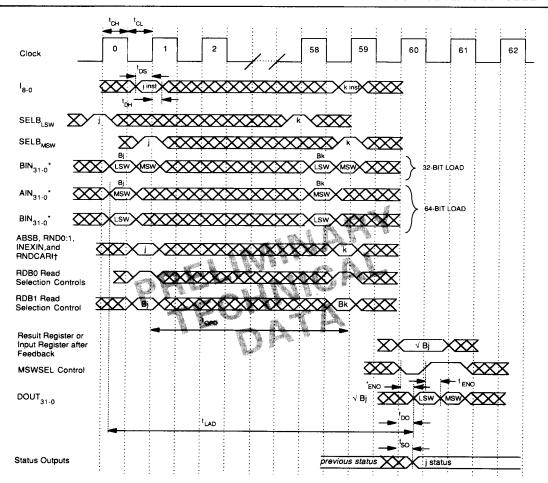

With 64-bit double-precision data, there are constraints on which registers hold which 32-bit halves of operands. You must load 64-bit data in adjacent pairs of 32-bit registers as shown in Figure 18. The 32-bit most significant word (MSW) will be in one even register and the 32-bit least significant word (LSW) in its odd neighbor.

| A0               | A1               | В0       | B1               |

|------------------|------------------|----------|------------------|

| MSW <sub>A</sub> | LSWA             | MSWB     | LSW <sub>B</sub> |

| <u> </u>         |                  | <u> </u> |                  |

| A 2              | A3               | B2       | B3               |

| MSW <sub>C</sub> | LSW <sub>C</sub> | MSWD     | LSW <sub>D</sub> |

|                  |                  |          |                  |

Figure 18. ADSP-3212/ADSP-3222 Operand Storage for Double-Precision Operations

#### Restrictions on Register Stability

With 64-bit data—as with 32-bit data—registers should not be loaded that are currently in use by the processing elements (i.e., selected by the RDA/B controls). Half the 32-bit registers in any pair of 64-bit operands will loaded on the falling edge with both members of this chipset.

To operate the ALU at full throughput in single-cycle double-precision operations, 64-bit register sets should be alternated every cycle. For example,  $A_0/A_1$  and  $B_2/B_3$  could be loaded with new operands while  $A_2/A_3$  and  $B_0/B_1$  were feeding the computational circuits (and were not changing). In this way, data loading will not disturb the contents of registers in use.

The ADSP-3222 ALU includes two double-precision multicycle operations in its instruction set: IEEE division (30 cycles) and square root (58 cycles). The ADSP-3212 performs a 12-cycle double-precision floating-point division. For double-precision floating-point division, the 64-bit dividend can be stored in either pair of A registers consistent with Figure 18. The divisor can be stored in either pair of B registers, also consistent with Figure 18. Double-precision operands for IEEE square root can be stored in either pair of B registers consistent with Figure 18. Registers containing operands in use must remain unchanged until the end of the operation time.

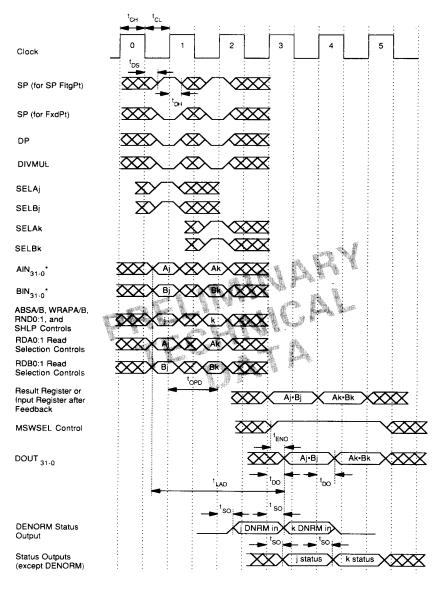

# Data Format Selection – SP and DP Controls (REG) The three data formats processed by the ADSP-3212/ADSP3222 chipset are single-precision floating-point, double-precision floating-point, and fixed-point. With the ADSP-3212 Multiplier/ Divider, the data format is indicated explicitly by the states of the DP and the SP registered controls:

| SP | DΡ | Data Format Selection |  |  |

|----|----|-----------------------|--|--|

| 0  | 0  | fixed                 |  |  |

| 0  | 1  | double-precision      |  |  |

| 1  | 0  | single-precision      |  |  |

| 1  | 1  | illegal mode          |  |  |

Figure 19. ADSP-3212 Multiplier/Divider Data Format Selection

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

The state of the SP and DP controls at the rising edge when data is read into the multiplier array determines whether the data is interpreted as single-precision floating-point, double-precision floating-point, or fixed-point. Fixed-point division is not supported; fixed-point numbers should be converted to floating-point format for division and the result converted back to fixed-point format. Division is a multicycle operation (6 cycles for single precision and 12 cycles for double-precision); once initiated, the states of SP and DP don't matter until the next data is read to the processing circuitry.

For the ADSP-3222 ALU, data format selection is implicit in the ALU instruction, I<sub>8-0</sub>. (See "Instructions and Operations" section below.)

Input Data Register Read Selection – RDA/B Controls (REG) The register read selection controls, RDA0:1 and RDB0:1, are registered controls which select the input registers that are read into the chipset's processing circuitry. Any pair of input registers can be read into the processing circuitry. (For single-operand operations, the state of the selection controls for the unused register bank doesn't matter.) Data loaded to an input register on a rising edge can be read into the processing circuitry on that same edge.

The data format selected affects the interpretation of the RDA/B controls as follows:

| RDA1 | RDAO | SP & Fixed:<br>A register<br>selected | DP:<br>A registers<br>selected |

|------|------|---------------------------------------|--------------------------------|

| 0    | 0    | <b>A</b> 2                            | illegæl state                  |

| 0    | 1    | A3 <sup>33</sup>                      | A2, A3                         |

| 1 1  | 0    | <b>A</b> 0                            | illegal state                  |

| 1    | 1    | <b>A</b> 1                            | A0, A1                         |

| RDB1 | RDB0 | SP & Fixed:<br>B register<br>selected | DP:<br>B registers<br>selected |

|------|------|---------------------------------------|--------------------------------|

| 0    | 0    | <b>B</b> 2                            | illegal state                  |

| 0    | 1    | <b>B</b> 3                            | B2, B3                         |

| 1    | 0    | <b>B</b> 0                            | illegal state                  |

| 1    | 1    | B1                                    | B0, B1                         |

Figure 20. ADSP-3212/ADSP-3222 Input Register Read Selection

Note that when feedforward is activated, the definitions of the RDA/B controls change. See "Feedback and Feedforward," below

After the initiation of multicycle operations, the RDA/B controls are ignored.

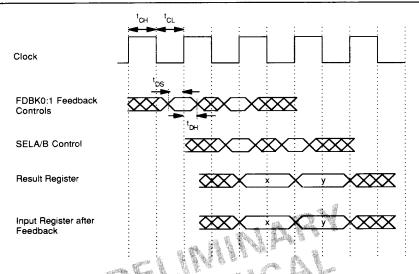

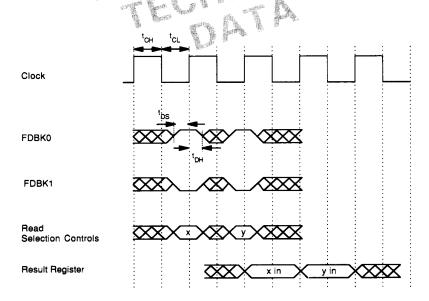

#### Feedback and Feedforward - FDBK Controls (REG)

The ADSP-3212/ADSP-3222 have feedback paths to  $A_2$ ,  $A_3$ ,  $B_2$ , and  $B_3$  and feedforward paths from all registers to the output register. The feedback controls FDBK0:1 determine whether the device is in normal operation, whether the feedback data goes to the A registers or the B registers, and whether feedforward is activated, as shown below:

| FDBK1 | FDBK0 | Interpretation    |

|-------|-------|-------------------|

| 0     | 0     | normal operation  |

| 0     | 1     | feedforward       |

| 1     | 0     | feedback to A reg |

| 1     | 1     | feedback to B reg |

Figure 21. Feedback and Feedforward Controls

These controls are pipelined for one cycle; that is, they take effect at the next rising clock edge from the one at which they are presented. For feedback operations from the 64-bit result (before the output register), each register to receive data must also be selected for loading in the usual way, by asserting the corresponding SELA or SELB; thus, you would assert the FDBK controls in one cycle and the SELA or SELB controls in the next cycle. For feedback, all input registers are loaded in parallel on the rising clock edge.

Both SP and DP feedback transfers are supported. In DP feedback transfers, the MSW is written to A<sub>2</sub> or B<sub>2</sub>, and the LSW is written to A<sub>3</sub> or B<sub>3</sub>. In SP feedback transfers, the 32-bit result is written to A<sub>2</sub> or B<sub>2</sub>; A<sub>3</sub> or B<sub>3</sub> should not be selected in this case. The registers in the bank not selected by FDBK0:1 can be loaded concurrently in the normal manner. Also, the low-order (0 and 1) registers in the selected bank can be loaded concurrently in the normal manner. You should not, however, load registers intended to receive feedback data in the cycle before the feedback data is written (the same cycle in which you assert the FDBK controls). In theory, such an action would serve no purpose, because the newly loaded data would be overwritten by the fed-back data before it could be passed to the processing circuits; in practice, the data load will actually inhibit the feedback.

When feedforward is selected, a pair of input registers will be fed directly to the output port in the same cycle. RDA0 determines whether A registers (HI) or B registers (LO) are fed forward. The pair is selected by the register read selection controls, RDA1/B1, as shown in Figure 22.

|   | RDA0 | RDA1 | RDB1 | Feedforward Registers |  |

|---|------|------|------|-----------------------|--|

|   | 0    | Х    | 0    | B2/B3                 |  |

| ı | 0    | Х    | 1    | B0/B1                 |  |

| ı | 1    | 0    | Х    | A2/A3                 |  |

| ı | 1    | 1    | Х    | A0/A1                 |  |

Figure 22. Feedforward Register Selection

The pair fedforward must have been in input registers from a previous cycle but will reach the output register on the rising edge following the cycle in which the FDBK controls are set up for a feedforward operation (and the read selection controls are also set up). There is no cycle time or output delay penalty for feedforward operations.

For normal operation, FDBK0:1 must both be LO. Feedback and feedforward timing is shown in Figures T5 and T6 in the Timing section.

#### Absolute Value - ABSA/B Controls (REG)

The registered absolute value controls convert an operand selected by the read selection controls to its absolute value before processing. Asserting ABSA (HI) causes the A operand to be converted to its absolute value; asserting ABSB (HI) causes the B operand to be converted to its absolute value. The contents of the input registers remain unaffected.

With the ADSP-3222 ALU, the ABSA/B controls are effective with most fixed-point and all single-precision and double-precision operations. If the ABSA/B controls are asserted in logical operations, the results will be undefined.

For the ADSP-3212 Multiplier/Divider, the absolute value operation is available on single-precision and double-precision

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

4-96 FLOATING-POINT COMPONENTS

# ADSP-3212/ADSP-3222

floating-point operands only. If the ABSA/B controls are asserted with a multiplier/divider for a fixed-point operation, the results will be undefined.

# Wrapped Input - WRAPA/B Controls (REG) (and INEXIN and RNDCARI on the ADSP-3222)

The ADSP-3212 cannot operate directly on denormals; denormals to be multiplied must first be converted by an ALU to the "wrapped" format. (See "Gradual Underflow and IEEE Exceptions" below.) The multiplier/divider must be told that an input is in the wrapped format so that its exponent can be interpreted properly as a twos-complement number.

The registered WRAPA/B controls inform the multiplier/divider that a wrapped number has been selected as an operand (RDA/B controls) to the multiplier/divider array. WRAPA indicates (HI) that the selected A register contains a wrapped number; WRAPB, that the selected B register contains a wrapped number.

The ALU in general operates directly on denormals and hence doesn't need a similar set of controls. However, for IEEE division and square root operations, the ALU cannot operate directly on denormals. Like the multiplier/divider, it needs denormals to be converted to wraps before processing. To indicate that the dividend in the A register is a wrapped, INEXIN should be asserted (HI) exactly as WRAPA would be asserted on a multiplier/divider. To indicated that either the divisor in a B register or a square root operand in a B register is wrapped, RNDCARI should be asserted (HI). Except for unwrap, division, and square root operations, both INEXIN and RNDCARI should be held LO.

#### Twos-Complement Input - TCA/B Controls (REG)

The registered ADSP-3212's Twos-Complement Input Controls inform the multiplier/divider to interpret the selected fixed-point inputs in the twos-complement data format. (See "32-Bit Fixed-Point Data Formats" above.) TCA HI indicates that the selected A register is twos-complement; TCB HI indicates a twos-complement B register. A LO value on either control for fixed-point multiplication indicates that the selected input is in unsigned-magnitude format. Mixed-mode (twos-complement times unsigned-magnitude) multiplications are permitted. The TCA/B controls are operative in fixed-point mode only; in floating-point mode, they are ignored.

#### Rounding - RND Controls (REG)

For floating-point operations, the ADSP-3212/ADSP-3222 chipset supports all four rounding modes of IEEE Standard 754. These are: Round-to-Nearest, Round-toward-Zero, Round-toward-Plus-Infinity and Round-toward-Minus-Infinity. For fixed-point operations, two rounding modes are available: Round-to-Nearest and Unrounded.

Rounding is involved in all operations in which the precision of the destination format is less than the precision of the intermediate results from the operation. Multiplications internally generate twice as many bits in the intermediate result significand as can be stored in the destination format. Data conversions to a destination format of lesser precision than the source also always force rounding unless the source value fits exactly.

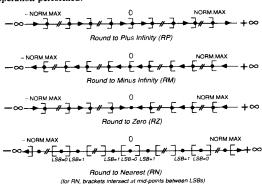

Rounding with the ADSP-3212/ADSP-3222 chipset is controlled by a pair of pipelined, registered round controls, RND0:1. They should be set up with the input data whose result is to be rounded. Rounding is performed in the last stage of processing; the output register always contains rounded results. The effects of the round controls are defined as:

| Mnemonic | RND1 | RNDO | Floating-Point              | Fixed-Point      |

|----------|------|------|-----------------------------|------------------|

| RN       | 0    | 0    | Round-to-Nearest            | Round-to-Nearest |

| RZ       | 0    | 1    | Round-toward-Zero           | Unrounded        |

| RP       | 1    | 0    | Round-toward-Plus-Infinity  | illegal state    |

| RM       | 1    | 1    | Round-toward-Minus-Infinity | illegal state    |

Figure 23. Round Controls

The four floating-point modes of the IEEE Standard can be summarized as follows. In all cases, if the result before rounding can be expressed exactly in the destination format without loss of accuracy, then that will be the destination format result, regardless of specified rounding mode.

Round-toward-Plus-Infinity (RP): "When rounding toward  $+\infty$ , the result shall be the format's value (possibly  $+\infty$ ) closest to and no less than the infinitely precise result." (Standard 754-1985, Sec. 4.2.) If the result before rounding (the "infinitely precise result") is not exactly representable in the destination format, then the result will be that number which is nearer to positive infinity. Round-toward-Plus-Infinity is available in floating-point operations only. If the result before rounding is greater than NORM.MAX but not equal to Plus Infinity, the result will be Plus Infinity. If the result before rounding is less than -NORM.MAX but not equal to Minus Infinity, the result will be -NORM.MAX. For fixed-point destination formats, the results of RP are undefined.

Round-toward-Minus-Infinity (RM): "When rounding toward  $-\infty$ , the result shall be the format's value (possibly  $-\infty$ ) closest to and no greater than the infinitely precise result." (Standard 754-1985, Sec. 4.2.) If the result before rounding is not exactly representable in the destination format, the result will be that number which is nearer to Minus Infinity. Round-toward-Minus-Infinity is available in floating-point operations only. If the result before rounding is greater than NORM.MAX but not equal to Plus Infinity, the result will be NORM.MAX but not equal to Minus Infinity, the result will be Minus Infinity. For fixed-point destination formats, the results of RM are undefined.

Round-toward-Zero and Unrounded (RZ): "When rounding toward 0, the result shall be the format's value closest to and no greater in magnitude than the infinitely precise result." (Standard 754-1985, Sec. 4.2.) If the result before rounding is not exactly representable in the destination format, the result will be that number which is nearer to zero. The Round-toward-Zero operation is available in floating-point operations only. It is equivalent to truncation of the (unsigned-magnitude) significand. If the result before rounding has a magnitude greater than NORM.MAX but not equal to Infinity, the result will be NORM.MAX of the same sign.

For fixed-point destination formats, the RZ mode is *Unrounded*. For fixed-point operations, RZ has no effect on the result at the output register and should be specified whenever unmodified fixed-point results are desired. (Treating the unrounded most significant product as the final result and throwing away the LSP is logically equivalent to Round-toward-Minus-Infinity for

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

twos-complement numbers and equivalent to Round-toward-Zero [truncation] for unsigned-magnitude numbers.)

Round-to-Nearest (RN): When rounding to nearest, "... the representable value nearest to the infinitely precise result shall be delivered; if the two nearest representable values are equally near, the one with its least significant bit zero shall be delivered." (Standard 754-1985, Sec. 4.1). If the result before rounding is not exactly representable in the destination format, the result will be that number which is nearer to the result before rounding. In the case that the result before rounding is exactly half way between two numbers in the destination format differing by an LSB, the result will be that number which has an LSB equal to zero. If the result before rounding overflows, i.e., has a magnitude greater than or equal to NORM.MAX + 1/2 LSB in the destination format, the result will be the Infinity of the same sign.

Round-to-Nearest is available in both floating-point and fixed-point operations. In fixed-point, Round-to-Nearest treats the most significant product after having been shifted in accordance with SHLP (see Figures 9, 10, 12, and 13) as the destination format.

The four rounding modes are illustrated by number lines in Figure 24. The direction of rounding is indicated by an arrow. Numbers exactly representable in the destination format are indicated by "•\*s. In subdividing the number lines, square brackets are inclusive of the points on the line they intersect. Note that brackets intersect points representable in the destination format except for Round-to-Nearest, where they intersect the line midway between representable points. Slashes are used to indicate a break in the number line of arbitrary size.

Note that Round-to-Nearest is unique among the rounding modes in that it is *unbiased*. The large-sample statistical mean from a set of numbers rounded in the other modes will be displaced from the true mean. The other three modes will exhibit a large-sample statistical bias in the direction of the rounding operation performed.

Figure 24. IEEE Rounding Modes

#### Status Flags

The ADSP-3212/ADSP-3222 chipset generates on dedicated pins the following exception flags specified in the IEEE Standard: Overflow (OVRFLO), Underflow (UNDFLO), Inexact Result (INEXO), and Invalid Operation (INVALOP). The IEEE exception condition Division-by-Zero is flagged by the simultaneous assertion of both OVRFLO and INVALOP pins. The five IEEE exceptions are defined in accordance to the default

assumption of Standard 754 of non-trapping exceptions. The ADSP-3222 also generates a ZERO flag to indicate that the result of the ALU operation is ZERO.

Flag results are registered in the status output register when the results they reflect are clocked to the output register. They are held valid until the next rising clock edge. The IEEE Standard specifies that exception flags when set remain set until reset by the user. For full conformance to the Standard, the status outputs from this chipset should be individually latched externally.

#### Denormal

In addition to the IEEE status flags, the ADSP-3212 Multiplier/ Divider has a DENORM output flag that signals the presence of a denormalized number at one of the input registers being read into the multiplier array. This denormal must be wrapped by the ALU before the multiplier/divider can read it. To minimize the system response time to a denormal input exception, the DENORM flag comes out earlier than the associated IEEE status flags. For both multiplication and division, DENORM goes HI during the cycle after a denormal was read into the array (with the RDA/B controls). See Figures T7 through T10. In the cycle following the assertion of DENORM, the INEXO status flag (see "Inexact," below) indicates which operand was denormal; INEXO is HI if the B operand or both operands were denormal and LO if only the A operand was denormal. The DENORM flag is asserted in both IEEE and FAST modes.

Some multiplications with denormal operands do not require wrapping and therefore do not cause the assertion of the DENORM flag. These are DNRM•ZERO, DNRM•INF, and DNRM•NAN. Multiplication of a finite number by zero always yields zero—the result the multiplier/divider will produce anyway—so there is no need to signal an exception. Any finite nonzero number multiplied by INF should yield INF, and in the IEEE mode, the ADSP-3212 Multiplier/Divider will produce this result with a DNRM operand, hence no wrapping is required. In FAST mode, DNRM is treated as ZERO, so a NAN results, and no wrapping is needed. And multiplication of any number by a NAN produces a NAN (and the INVALOP flag); no wrapping is necessary for the multiplier/divider to produce this correct IEEE result.

Similarly, divisions that have a denormal operand and ZERO, INF, or NAN as the other operand do not require wrapping and do not cause the assertion of the DENORM flag on the multiplier/divider (or the INVALOP and UNDFLO combination on the ALU, which flags a denormal operand for division or square root). Zero divided by a finite number always yields zero, so in IEEE mode, ZERO + DNRM yields ZERO without signalling an exception. DNRM ÷ ZERO results in INF, because any finite nonzero number divided by zero should yield INF. In FAST mode, DNRM is treated as ZERO, so ZERO + DNRM and DNRM + ZERO both yield a NAN (and IN-VALOP). Any finite number divided by INF should yield ZERO, and INF divided by any finite number should yield INF. In both IEEE and FAST modes, INF ÷ DNRM results in INF and DNRM ÷ INF results in ZERO, without generating any flags. Division of any number by a NAN or division of a NAN by any number produces a NAN (and the INVALOP flag); therefore, the multiplier/divider and the ALU generate this result without flagging a denormal and without wrapping.

Note that the ALU in general operates directly on denormals and therefore does not flag any exception. However, it cannot operate directly on denormals in its division and square root operations. For these operations, denormal inputs will cause the