# Am27C191/Am27C291

Advanced Micro Devices

16,384-Bit (2048x8) High-Performance CMOS PROM

# DISTINCTIVE CHARACTERISTICS

- High-speed (25 ns)/Low-Power (60 mA) CMOS EPROM Technology

- Direct plug-in replacement for Bipolar PROMs JEDEC-approved pinout

- Silm 300-mil DIP (Am27C291) or standard 600-mil DIP (Am27C191) packaging available

- 5-Volt ±10% power supplies for both Commercial and Military

- UV-erasable and reprogrammable provides exceptionally high programming yields (Typ. > 99.9%)

- ESD immunity > 2000 V

# **GENERAL DESCRIPTION**

The Am27C191 (2048 words by 8 bits) is a high-performance CMOS programmable read-only memory (PROM).

This device has three-state outputs compatible with lowpower Schottky bus standards capable of satisfying the requirements of a variety of microprogrammable controls, mapping functions, code conversion, or logic replace-

10176A-1

ment. Word-depth expansion is facilitated by both active LOW (\$\overline{G}\_1\$) and active HIGH (\$\overline{G}\_2\$ and \$\overline{G}\_3\$) output enables. This device utilizes proven floating-gate EPROM technology to ensure high reliability, ease of programming, and exceptionally high programming yields. This device is also available in 300-mil lateral center DIP (Am27C291).

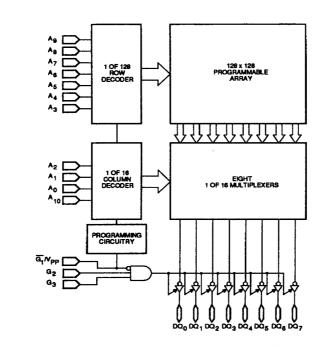

# **BLOCK DIAGRAM**

Publication # Rev. Amendment 10176 B /0 Issue Date: January 1989

# **PRODUCT SELECTOR GUIDE**

| Part Number         | Am27C191-25<br>Am27C291-25 | Am27C191-35<br>Am27C291-35 | Am27C191-45<br>Am27C291-45 |

|---------------------|----------------------------|----------------------------|----------------------------|

| Address Access Time | 25 ns                      | 35 ns                      | 45 ns                      |

| Operating Range     | COM'L                      | COM, FWIF,                 | COM'L/MIL*                 |

<sup>\*</sup> Advance Information—Military Products Only.

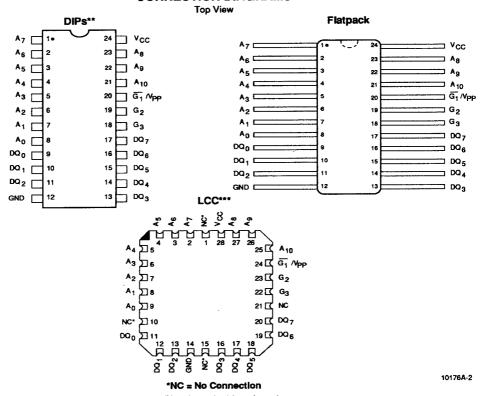

# **CONNECTION DIAGRAMS**

# Note: Pin 1 is marked for orientation

- \*\* Also available in a 24-Pin ceramic windowed DIP. Pinout identical to DIPs.

- \*\*\* Also available in a 28-Pin ceramic windowed LCC. Pinout identical to LCC.

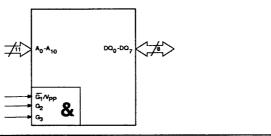

# LOGIC SYMBOL

10176A-3

Am27C191/Am27C291

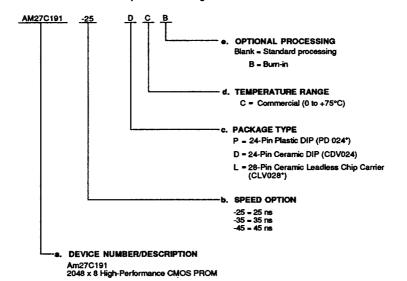

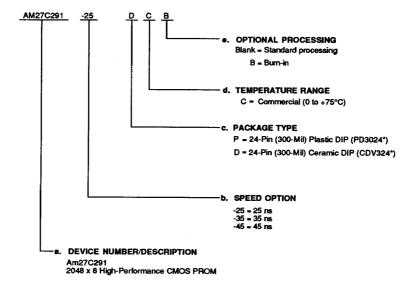

# ORDERING INFORMATION Am27C191 Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

a. Device Number

b. Speed Option (if applicable)

c. Package Type

d. Temperature Range

e. Optional Processing

。在1950年中的1950年中,1950年中,1950年中,1950年中,1950年中,1950年中,1950年中,1950年中,1950年中,1950年中,1950年中,1950年中,1950年中,1950年中,195

| Valid Combinations |                              |  |  |  |  |

|--------------------|------------------------------|--|--|--|--|

| AM27C191-25        |                              |  |  |  |  |

| AM27C191-35        | PC, PCB, DC,<br>DCB, LC, LCB |  |  |  |  |

| AM27C191-45        |                              |  |  |  |  |

\* Product version in Development, contact HPP Product Marketing.

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

# ORDERING INFORMATION (Cont'd.) Am27C291 Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) Amb statistical products are available in several packages and op is formed by a combination of: a. Device Number

b. Speed Option (if applicable)

c. Package Type

d. Temperature Range

e. Optional Processing

| Valid Combinations |                     |  |  |  |

|--------------------|---------------------|--|--|--|

| AM27C291-25        |                     |  |  |  |

| AM27C291-35        | PC, PCB, DC,<br>DCB |  |  |  |

| AM27C291-45        |                     |  |  |  |

\*Product version in Development, contact HPP Product Marketing.

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

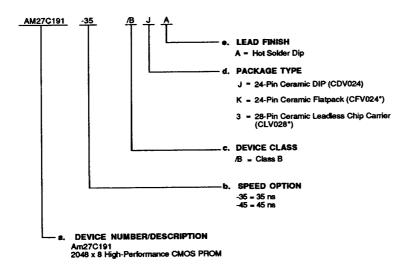

# **MILITARY ORDERING INFORMATION** Am27C191 APL Products

The second of th

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of: s. Device Number

b. Speed Option (if applicable)

c. Device Class

- Package Type Lead Finish

# Valid Combinations AM27C191-35 /BJA, /BKA, /B3A AM27C191-45

\*Preliminary; Package in Development.

## **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

# Group A Tests

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

# MILITARY BURN-IN

Military burn-in is in accordance with the current revision of MIL-STD-883, Test Method 1015, Conditions A through E. Test conditions are selected at AMD's option.

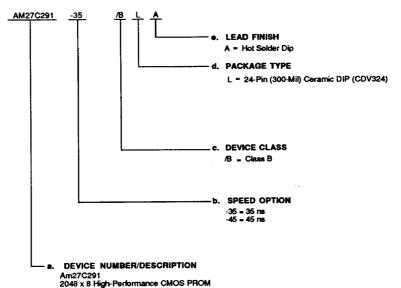

# MILITARY ORDERING INFORMATION (Cont'd.) Am27C291 APL Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of:

a. Device Number

b. Speed Option (if applicable)

c. Device Class

- d. Package Type e. Lead Finish

| Valid Con   | nbinations |

|-------------|------------|

| AM27C291-35 | /BLA       |

| AM27C291-45 | 1 ""       |

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

# **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

# MILITARY BURN-IN

Military burn-in is in accordance with the current revision of MIL-STD-883, Test Method 1015, Conditions A through E. Test conditions are selected at AMD's option.

# PIN DESCRIPTION

# Address Lines (Inputs)

The 11-bit field presented at the address inputs selects one of 2048 memory locations to be read from.

# DQ<sub>a</sub>-DQ, Data Port (input/Outputs; Three State)

The outputs whose state represents the data read from the selected memory locations. These outputs are threestate buffers which, when disabled, are in a floating or high-impedance state. These pins provide the data input for programming the memory array.

# G, Npp. G2, G1 Output Enable/(Vpp) Programming

Provides direct control of the DQ output three-state buffers. When raised to a voltage > 12.0 V, the G, Npp pin provides the programming power to program the memory array.

Enable =

$$\overline{G}_1 \cdot G_2 \cdot G_3$$

Disable =  $\overline{G}_1 \cdot G_2 \cdot G_3$

=  $G_1 + \overline{G}_2 + \overline{G}_3$

# **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                | 65 to +150°C    |

|------------------------------------|-----------------|

| Ambient Temperature                |                 |

| with Power Applied                 | 55 to +125°C    |

| Supply Voltage                     | 0.5 V to +7.0 V |

| DC Voltage Applied to Outputs      |                 |

| in High-Impedance State            | 0.5 V to +7.0 V |

| DC Programming Voltage (Vpp)       | 14 V            |

| DC Input Voltage                   | 0.5 V to +7.0 V |

| Electrostatic Discharge Protection |                 |

| (per MIL-STD-883 Method 3015.2)    | > 2000 V        |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

| Commercial (C) Devices                |                  |

|---------------------------------------|------------------|

| Ambient Temperature (T <sub>a</sub> ) | 0 to +75°C       |

| Supply Voltage (V <sub>cc</sub> )     | +4.5 V to +5.5 V |

| Military (M) Devices*                 |                  |

| Case Temperature (T <sub>c</sub> )    | 55 to +125°C     |

| Supply Voltage (V                     |                  |

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter<br>Description        | Test C                                                                                                  | conditions                   | Min. | Max.        | Unit |

|---------------------|---------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------|------|-------------|------|

| V <sub>IH</sub>     | Input HIGH Voltage              | Guaranteed Input HIGH Voltage (Note 1)                                                                  |                              | 2.0  |             | v    |

| V <sub>IL</sub>     | Input LOW Voltage               | Guaranteed Ir<br>(Note 1)                                                                               | nput LOW Voltage             |      | 0.8         | ٧    |

| V <sub>oH</sub>     | Output HIGH Voltage             | V <sub>cc</sub> = Min., 1 <sub>oH</sub><br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>         |                              | 2.4  |             | v    |

| V <sub>oL</sub>     | Output LOW Voltage              | V <sub>cc</sub> = Min., I <sub>oL</sub> = 16 mA<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |                              |      | 0.4         | v    |

| V <sub>CL</sub>     | Input Clamp<br>Diode Voltage    | V <sub>cc</sub> = Min., I <sub>IN</sub> = -18 mA                                                        |                              | -1.2 |             | V    |

| l <sub>m</sub>      | Input HIGH Current              | V <sub>cc</sub> = Max., V <sub>IN</sub> = 5.5 V                                                         |                              |      | 10          | μА   |

| I,_                 | Input LOW Current               | V <sub>cc</sub> = Max., V <sub>IN</sub> = 0.0 V                                                         |                              |      | -10         | μА   |

| l <sub>sc</sub>     | Output Short-Circuit<br>Current | V <sub>cc</sub> = Max.<br>V <sub>out</sub> = 0.0 V (Note 2)                                             |                              | -20  | -90         | mA   |

| 1                   | Output Leakage Current          | V <sub>cc</sub> = Max.,                                                                                 | V <sub>our</sub> = 5.5 V     |      | 40          | μА   |

| CEX                 | Output Learage Outlett          | V <sub>g1</sub> = 2.4 V                                                                                 | V <sub>out</sub> = 0.4 V     |      | <b>-4</b> 0 | μА   |

|                     | Operating Supply Current        | V <sub>cc</sub> = Max.                                                                                  |                              |      | 60          | mA   |

| l <sub>cc</sub>     | Operating Supply Current        | (Note 3)                                                                                                | All Inputs = V <sub>IL</sub> |      |             |      |

Notes: 1. V<sub>IL</sub> and V<sub>IH</sub> are input conditions of output tests and are not themselves directly tested. V<sub>IL</sub> and V<sub>IH</sub> are absolute voltages with respect to device ground and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

- 2. Not more than one output should be shorted at a time. Duration of the short-circuit test should not exceed one second.

- Operating I<sub>cc</sub> is measured with all inputs execpt G

<sub>I</sub> switching between V

<sub>IL</sub> and V

<sub>IH</sub> at a timing interval equal to TAVDQV. The outputs are disabled via G

<sub>I</sub> held at 3.0 V.

<sup>\*</sup> Military product 100% tested at T<sub>c</sub> = +25°C, +125°C, and -55°C.

# Capacitance\*

| Parameter<br>Symbol | Parameter<br>Description                             | Test Conditions                                                                                              | Тур. | Unit |

|---------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|

|                     | Input Capacitance (G <sub>1</sub> /V <sub>pp</sub> ) |                                                                                                              | 9    |      |

| C <sub>M</sub>      | Input Capacitance (All Others)                       | $V_{cc} = 5.0 \text{ V}, T_{s} = 25^{\circ}\text{C}$<br>$V_{ts}/V_{out} = 2.0 \text{ V @ f} = 1 \text{ MHz}$ | 5    | pF   |

| Cour                | Output Capacitance                                   |                                                                                                              | 8    | p₹   |

<sup>\*</sup>These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

# **SWITCHING CHARACTERISTICS** over operating range unless otherwise specified (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted\*)

|     |                                            |                                                                        | Am27C191/Am27C291 |        |      |                  |      |      |      |

|-----|--------------------------------------------|------------------------------------------------------------------------|-------------------|--------|------|------------------|------|------|------|

|     |                                            | -25 -35 COM'L Only COM'L/MIL                                           |                   | j -35  |      | -45<br>COM'L/MIL |      |      |      |

|     |                                            |                                                                        |                   | 'L/MIL |      |                  |      |      |      |

| No. | Parameter Parameter No. Symbol Description |                                                                        | Min.              | Max.   | Min. | Max.             | Min. | Max. | Unit |

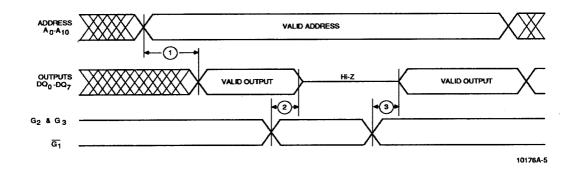

| 1   | TAVDQV                                     | Address Valid to Output<br>Valid Access Time                           |                   | 25     |      | 35               |      | 45   | ns   |

| 2   | TGVDQZ                                     | Delay from Output Enable<br>Valid to Output High<br>Impedance (Note 2) |                   | 20     |      | 20               |      | 25   | ns   |

| 3   | TGVDQV                                     | Delay from Output Enable<br>Valid to Output Valid (Note 3)             |                   | 20     |      | 20               |      | 25   | ns   |

See Switching Test Circuits.

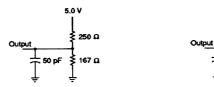

Notes: 1. Tests are performed with input transition time of 5 ns or less, timing reference levels of 1.5 V, and input pulse levels of 0 to 3.0 V using test load in diagram A.

TGVDQZ is measured at steady-state HIGH output voltage -0.5 V and steady-state LOW output voltage +0.5 V output levels using the test load in diagram B.

TGVDQV is measured at steady-state output voltage minus 0.5 V for Hi–Z to LOW and steady-state output voltage plus 0.5 V for Hi–Z to HIGH output levels using the test load in diagram A.

\* Subgroups 7 and 8 apply to functional tests.

# **SWITCHING TEST CIRCUITS**

A. Output Load for all AC tests except TGVDQZ

B. Output Load for TGVDQZ

250 Ω

Notes: 1. All device test loads should be located within 2" of device output pin.

2. Load capacitance includes all stray and fixture capacitance.

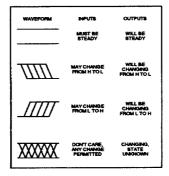

# SWITCHING WAVEFORMS KEY TO SWITCHING WAVEFORMS

KS000010

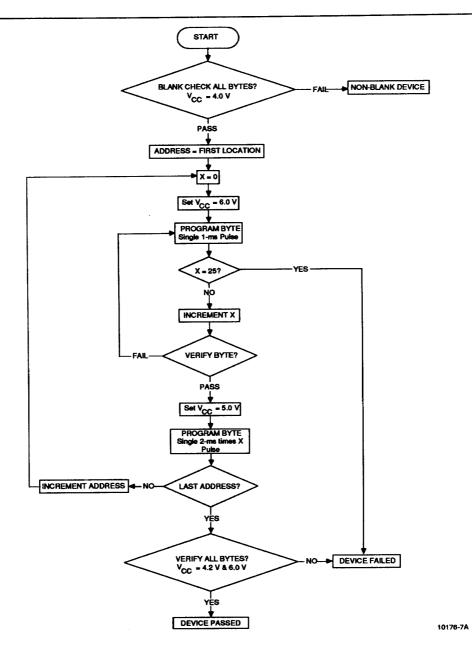

# Am27C191/Am27C291 CMOS PROM PROGRAMMING PROCEDURE

# Programming Technique

Advanced Micro Devices' high-performance CMOS PROM circuits have been designed to use a programming algorithm which minimizes the requirements on the programmer, yet allows the circuit to be programmed quickly and reliably. Specifically, the following sequence of events must take place:

- 1) V<sub>cc</sub> power is applied to the device;

- 2) The device outputs are disabled;

- 3) The appropriate address is selected;

- 4) The appropriate byte-wide pattern is applied to all outputs:

- 5) The G, N<sub>pp</sub> pin is pulsed to 13.5 V for 1 ms;

- The device is enabled and the byte sensed to verify that correct programming has occurred.

- In the event that the data does not verify, the sequence of 4 through 6 could be repeated up to 25 times;

- 8) At the conclusion of initial programming, the sequence of 4 and 5 should be repeated for over-programming using a V<sub>cc</sub> = 5.0 V, and G,V<sub>pp</sub> pulse width equal to twice the sum of initial programming pulse times;

- The sequence of 2 through 6 must be repeated for each address to be programmed;

- At the conclusion of programming, the device should be verified for correct data at all addresses with two V<sub>cc</sub> supply voltages (V<sub>cc</sub> = 6.0 and V<sub>cc</sub> = 4.2 V).

# **Notes on Programming**

- The unprogrammed or erased state of all enabled outputs is HIGH.

- All delays between edges are specified from the completion of the first edge to the beginning of the second edge; i.e., not the midpoints (10% or 90% of specified waveform).

- During t<sub>v</sub>, the output may be switched to appropriate loads for proper verification of specified V<sub>ot</sub> and V<sub>ot</sub> levels.

- 4) Due to the potential for fast voltage transitions of the outputs, it is advisable to provide low-impedance connections to the device's V<sub>cc</sub> and ground pins and to ensure adequate decoupling at the device pins.

# **Erasure Characteristics**

In order to fully erase all memory locations, it is necessary to expose the memory array to an ultraviolet light source having a wavelength of 2537Å. The minimum recommended dose (UV intensity times exposure time) is 15 Wsec/cm². For a UV lamp with a 12 mW/cm² power rating, the exposure time would be approximately 30 minutes. The device should be located within 1 inch of the source in direct line.

It should be noted that erasure may begin with exposure to light having wavelengths less than 4000Å. To prevent exposure to sunlight or fluorescent lighting from resulting in partial erasure, an opaque label should be affixed over the window after programming.

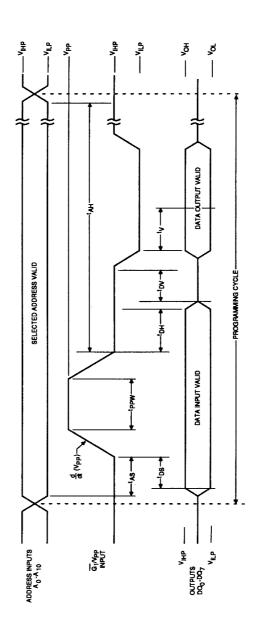

# PROGRAMMING PARAMETERS (T<sub>A</sub> = 25°C ±5°C)

| Parameter<br>Symbol  | Parameter<br>Description                                                       |                           | Min. | Max. | Unit |

|----------------------|--------------------------------------------------------------------------------|---------------------------|------|------|------|

|                      |                                                                                | Initial Programming       | 5.75 | 6.25 | v    |

| V <sub>ccP</sub>     | Power Supply during Programming                                                | Over-Programming          | 4.75 | 5.25 | ]    |

| I <sub>ccr</sub>     | V <sub>cc</sub> Supply Current during Programmi                                | ng                        |      | 90   | mA   |

| V <sub>pp</sub>      | Programming Voltage                                                            |                           | 13.0 | 14.0 | V    |

| I <sub>pp</sub>      | V <sub>PP</sub> Supply Current during Programmi                                | ng                        |      | 30   | mA   |

| V <sub>HP</sub>      | Input HIGH Level during Programming and Verify                                 |                           | 2.4  | 5.5  | V    |

| V <sub>ILP</sub>     | Input LOW Level during Programming and Verify                                  |                           | 0    | 0.45 | V    |

| Vol                  | Output LOW Voltage during Verify                                               |                           |      | 0.45 | v    |

| V <sub>oH</sub>      | Output HIGH Voltage during Verify                                              |                           | 2.40 |      | V    |

| dV <sub>pp</sub> /dt | Rate of $\overline{G}_i \mathcal{N}_{pp}$ Voltage Change (Rise and Fall Times) |                           | 5    | 10   | V/µs |

| t <sub>PPW</sub>     | V <sub>PP</sub> Programming Pulse Width                                        | Initial Programming Pulse | 0.95 | 1.05 | ms   |

| t <sub>AS</sub>      | Address Valid to V <sub>PP</sub> (HIGH) Setup Ti                               | me                        | 1.0  |      | μs   |

| t <sub>an</sub>      | V <sub>pp</sub> (LOW) to Address Change Hold 1                                 | lime .                    | 1.0  |      | μs   |

| t <sub>os</sub>      | Data Valid to V <sub>pp</sub> (HIGH) Setup Time                                |                           | 1.0  |      | μs   |

| t <sub>on</sub>      | V <sub>PP</sub> (LOW) to Data Change Hold Time                                 |                           | 1.0  |      | μs   |

| t <sub>DV</sub>      | Delay from Data to Output Enable (LOW) for Verification                        |                           | 1.0  |      | μs   |

| ţ,                   | Delay from Output Enable (LOW) to Verification Strobe                          |                           | 100  |      | ns   |

# PROGRAMMING WAVEFORMS

Figure 1. Programming Flow

TECHDOC 794C

Am27C191/Am27C291