# PM5372

# TSE™

# **TRANSMISSION SWITCH ELEMENT**

# DATASHEET

Proprietary and Confidential Released Issue 7: November, 2001

# Legal Information

### Copyright

© 2001 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, you cannot reproduce any part of this document, in any form, without the express written consent of PMC-Sierra, Inc.

### Disclaimer

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

### Trademarks

S/UNI is a registered trademark of PMC-Sierra, Inc.

SPECTRA is a trademark of PMC-Sierra, Inc.

SPECTRA-2488 is a trademark of PMC-Sierra, Inc.

TBS is a trademark of PMC-Sierra, Inc.

TSE is a trademark of PMC-Sierra, Inc.

CHESS is a trademark of PMC-Sierra, Inc.

Other product and company names mentioned herein may be the trademarks of their respective owners.

## **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000 Fax: (604) 415-6200

Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Technical Support: apps@pmc-sierra.com Web Site: <u>http://www.pmc-sierra.com</u>

# **Revision History**

| lssue<br>No. | lssue<br>Date  | Details of Change                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 7            | November       | Changed signoff page.                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|              | 2001           | Fixed Initialization procedure instruction referencing addresses 0N83h, 0N8Bh, 0N93h, 0N9Bh                                                                                                             |  |  |  |  |  |  |  |  |  |

|              |                | Updated voltage limits on digital/LVDS pins in Absolute Maximum Ratings table. Deleted Ambient Temperature spec. Fixed 1.8V Supply Voltage spec.                                                        |  |  |  |  |  |  |  |  |  |

|              |                | Added note to LCVI that it is change from no LCV to LCV that cause LCVI. A string of LCVs will only produce 1 LCVI.                                                                                     |  |  |  |  |  |  |  |  |  |

|              |                | Consolidated power information (sequencing/filtering) to Power Information<br>Section. Added power requirements section. Removed IDDOP for the power<br>supplies from the D.C Characteristics table.    |  |  |  |  |  |  |  |  |  |

|              |                | Updated Thermal section. Thermal section now indicates device suitable industrial applications when used with heat sink.                                                                                |  |  |  |  |  |  |  |  |  |

|              |                | Updated LVDS Hot Swap Section.                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

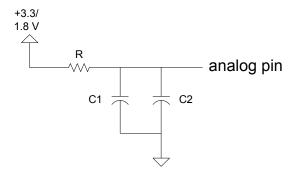

|              |                | Added RC filter example schematic in Power Filtering section                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|              |                | Updated TelecomBus Control Character Table                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|              | August<br>2001 | Reworded DLCV description: Added warning of LCV counter saturation if DLCV set high, and clarified to indicate that inverted data would have valid and invalid 8B/10B characters as result of DLCV high |  |  |  |  |  |  |  |  |  |

|              |                | Changed the name of the IDLESEL control signal ECHAR_OVWR, and made corresponding changes to the description of the ID[9:0] data bits                                                                   |  |  |  |  |  |  |  |  |  |

|              |                | Updated thermal information in sec 18                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|              |                | Revised power sequencing information, added max junction temp, Theta JA and Theta JC information, and chart of Theta JA vs. airflow                                                                     |  |  |  |  |  |  |  |  |  |

|              |                | Added sections for LVDS hot swap information, power down calculations, and trace length versus FIFO depth calculation                                                                                   |  |  |  |  |  |  |  |  |  |

|              |                | Changed name of ETSE register bit in register 0NAAH to EACTIVE, hid references to TCBMODE in sec 9.2 and in description of register 0NB0H                                                               |  |  |  |  |  |  |  |  |  |

|              |                | The device ID field is now "0001 instead of "0000" in register 0010H.                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|              |                | The JTAG Version number has been changed to 1H in Table 16.                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|              |                | The J0MASK bit has been added to registers 0N80H, 0N88H, 0N90H, 0N98H to support applications which require floating input links to remain activated.                                                   |  |  |  |  |  |  |  |  |  |

|              |                | Added the IJ0RORDR bit to register 0NA2.                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|              |                | Added the EJ0R0RDR bit to register ONAA.                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 5            | March<br>2001  | Added warning of LCV counter saturation if DLCV set high.in register descriptions                                                                                                                       |  |  |  |  |  |  |  |  |  |

|              |                | Changed the name of the IDLESEL control signal to CHARACTER<br>OVERWRITE, and made corresponding changes to the description of the<br>ID[9:0] data bits                                                 |  |  |  |  |  |  |  |  |  |

| lssue<br>No. | Issue<br>Date   | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                 | Updated Reliability information (sec 23), and thermal information in sec 18.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              |                 | Revised power sequencing information, added max junction temp, Theta JA and Theta JC information, and chart of Theta JA vs. airflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |                 | Added sections for LVDS hot swap information, power down calculations, and trace length versus FIFO depth calculation .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              |                 | Changed name of ETSE register bit in register 0NAAH to EACTIVE, removed references to TCBMODE in sec 9.2 and in description of register 0NB0H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              |                 | Revised sec 9.2 and 9.2.1 to further de-document TeleCombus mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |                 | Changed VIL(max) to 0.8V and VT+ to 2.2V based on characterization report.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              |                 | Revised Theta JA vs. Airflow table and Theta JC value with 560UBGA information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              |                 | Updated operating power to 9.86W.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |                 | Changed operating temperature range to $T_{C}$ = -40°C to Tj=120C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              |                 | Revised section on J0 Synchronization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4            | October<br>2000 | Added instructions to check CSU lock status and to center transmit<br>FIFOs in Section 12.5. Added Section 12.8. Added diagnostic note<br>in TJ0FP pad description, amended TDI pad description to indicate<br>there is no pull up resistor on the pad, removed part of RES/RESK<br>pad description from datasheet, removed ATMSB, and DTMSB<br>register bits from datasheet, redocumented clear behavior of<br>indication register bits when WCIMODE=1, amended legal range of<br>values for RJ0DLY: 1 to 9719, added explanatory text to BUSY<br>register bits, removed RXLBSEL from datasheet, added functional<br>timing diagram for page switching using SPSEL, IPSEL, and EPSEL<br>register bits, corrected TJ0DLY description to indicate that the time<br>to TJ0FP is TJ0DLY+2, amended DLCV register bit description,<br>amended CENTER register bit description, to indicate that FIFO<br>depth is 3-4 deep following centering operation, removed RDC mode<br>from J0INS register bit description, corrected Boundary Scan<br>Register Table: previously reverse ordered, and OEB_D(I)<br>incorrectly identified as IO_CELL, updated System "J0" Timing<br>diagram, added input pad tolerance, output pad overshoot, latchup<br>current for RESK in Absolute Maximum Ratings table, added typical<br>and max operating currents to D.C Characteristics table, corrected<br>mechanical information table with respect to package thickness. |

| 3            | April<br>2000   | Finalized pin out, register setting and functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2            | January<br>2000 | Register Description modification, package and pinout information,<br>added functional timing descriptions and scan test registers,<br>changed tolerances of 1.8V supply to +-5%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1            | June 1999       | Document created                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers' Internal Use Document ID: PMC-1991258, Issue 7

# **Table of Contents**

| Leę | gal Inf  | ormation                                  | 2  |

|-----|----------|-------------------------------------------|----|

|     |          | Copyright                                 | 2  |

|     |          | Disclaimer                                | 2  |

|     |          | Trademarks                                | 2  |

| Со  | ntactir  | ng PMC-Sierra                             | 3  |

| Re  | vision   | History                                   | 4  |

| Tab | ole of   | Contents                                  | 7  |

| Lis | t of Fig | gures                                     | 10 |

| Lis | t of Ta  | ables                                     | 11 |

| Lis | t of Re  | egisters                                  | 13 |

| 1   | Fea      | tures                                     | 15 |

| 2   | Арр      | lications                                 | 16 |

| 3   | Refe     | erences                                   | 17 |

| 4   | Арр      | lication Examples                         | 18 |

|     | 4.1      | Motivating Applications                   | 18 |

|     | 4.2      | TSE Fabric Scaling                        | 19 |

|     | 4.3      | Redundant Fabrics                         | 23 |

|     | 4.4      | Non-STS-48 Loads                          | 23 |

|     | 4.5      | TSE Fabric Packaging                      | 23 |

| 5   | Bloc     | ck Diagram                                | 24 |

| 6   | Des      | scription                                 | 25 |

| 7   | Pin      | Diagram                                   | 27 |

| 8   | Pin      | Description                               | 31 |

| 9   | Fun      | ctional Description                       | 45 |

|     | 9.1      | LVDS Overview                             | 45 |

|     |          | 9.1.1 LVDS Receiver (RXLV)                | 46 |

|     |          | 9.1.2 LVDS Transmitter (TXLV)             | 46 |

|     |          | 9.1.3 LVDS Transmit Reference (TXREF)     | 47 |

|     |          | 9.1.4 Data Recovery Unit (DRU)            | 47 |

|     |          | 9.1.5 Parallel to Serial Converter (PISO) | 48 |

PMC PMC-Sierra

|    |       | 9.1.6 Clock Synthesis Unit (CSU)                              |     |

|----|-------|---------------------------------------------------------------|-----|

|    | 9.2   | Receive 8B/10B Frame Aligner (R8FA)                           |     |

|    |       | 9.2.1 Character Alignment                                     |     |

|    |       | 9.2.2 Frame Alignment                                         | 50  |

|    |       | 9.2.3 FIFO Buffer                                             | 51  |

|    |       | 9.2.4 Frame Counter                                           | 51  |

|    | 9.3   | Ingress Time Switch Element (ITSE)                            | 51  |

|    | 9.4   | Space Switch Stage (SSWT)                                     | 51  |

|    | 9.5   | Egress Time Switch Element (ETSE)                             | 52  |

|    | 9.6   | Transmit 8B/10B Disparity Encoder (T8DE)                      | 52  |

|    | 9.7   | Clock Synthesis and Transmit Reference Digital Wrapper (CSTR) | 53  |

|    | 9.8   | Fabric Latency                                                | 53  |

|    | 9.9   | JTAG Support                                                  | 53  |

|    | 9.10  | Microprocessor Interface                                      | 54  |

| 10 | Norr  | nal Mode Register Description                                 | 59  |

| 11 | Test  | Features Description                                          | 121 |

|    | 11.1  | JTAG Test Port                                                | 122 |

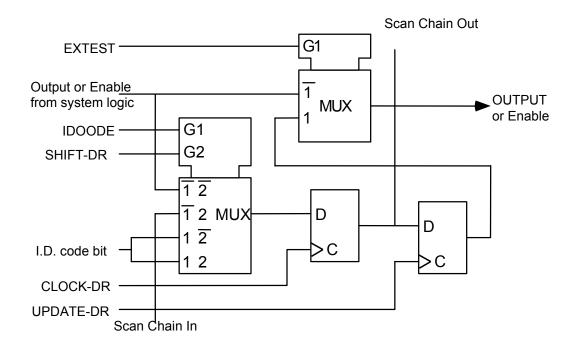

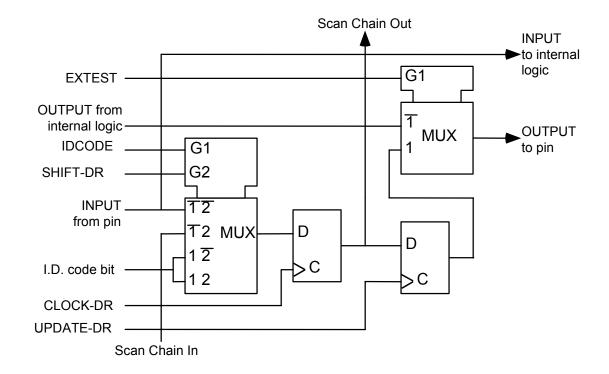

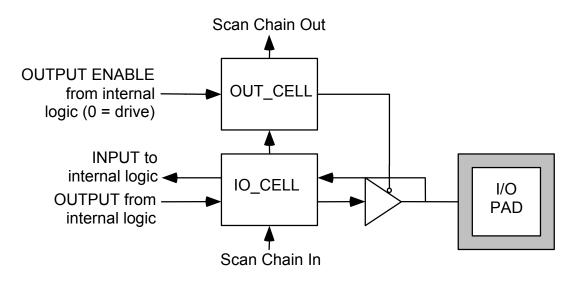

|    |       | 11.1.1 Boundary Scan Cells                                    | 123 |

| 12 | Ope   | ration                                                        | 126 |

|    | 12.1  | Power Conservation                                            | 126 |

|    | 12.2  | LVDS Optimizations                                            | 127 |

|    | 12.3  | LVDS Hot Swapping                                             | 128 |

|    | 12.4  | LVDS Trace Lengths                                            | 128 |

|    | 12.5  | JTAG Support                                                  | 129 |

|    |       | 12.5.1 TAP Controller                                         | 131 |

|    |       | 12.5.2 States                                                 | 133 |

|    |       | 12.5.3 Instructions                                           | 134 |

|    | 12.6  | Initialization Procedure                                      | 135 |

|    | 12.7  | Interrupt Service Routine                                     | 136 |

|    | 12.8  | Interpreting the Status of Receive Decoders                   | 136 |

|    | 12.9  | Accessing Indirect Registers                                  | 137 |

|    | 12.10 | ) Using the Performance Monitoring Features                   | 137 |

|    | 12.11 | "J0" Sync    | hronization of the TSE in a CHESS™ System |     |

|----|-------|--------------|-------------------------------------------|-----|

|    | 12.12 | Synchron     | ized Control Setting Changes              |     |

|    | 12.13 | B Fabric Ru  | Iles of Composition.                      |     |

|    |       | 12.13.1      | Interconnections                          | 142 |

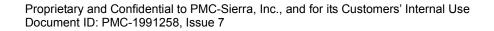

|    |       | 12.13.2      | Behavioural Descriptions of Components    |     |

|    |       | 12.13.3      | Rules of Composition                      | 143 |

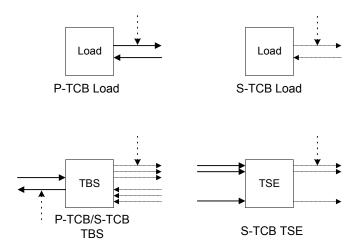

|    |       | 12.13.4      | Examples of Legal Composition             |     |

| 13 | Fund  | ctional Tim  | ing                                       | 148 |

|    | 13.1  | Receive I    | nterface Timing                           |     |

|    | 13.2  | Transmit     | Interface Timing                          | 149 |

| 14 | Abso  | olute Maxir  | num Ratings                               | 151 |

| 15 | Pow   | er Informa   | tion                                      | 152 |

|    | 15.1  | Power Re     | equirements                               | 152 |

|    | 15.2  | Power Se     | equencing                                 | 153 |

|    | 15.3  | Power Su     | upply Filtering                           | 153 |

| 16 | D.C.  | Character    | ristics                                   | 155 |

| 17 |       | -            | r Interface Timing Characteristics        |     |

| 18 | A.C.  | Timing Ch    | naracteristics                            | 161 |

|    | 18.1  | Input Tim    | ing                                       |     |

|    | 18.2  | Output Ti    | ming                                      | 162 |

|    | 18.3  | Reset Tin    | ning                                      | 163 |

|    | 18.4  | Serial Tel   | ecomBus Interface                         |     |

|    | 18.5  | JTAG Po      | rt Interface                              |     |

| 19 | Orde  | ering Inforr | nation                                    | 166 |

| 20 | Ther  | mal Inform   | nation                                    | 167 |

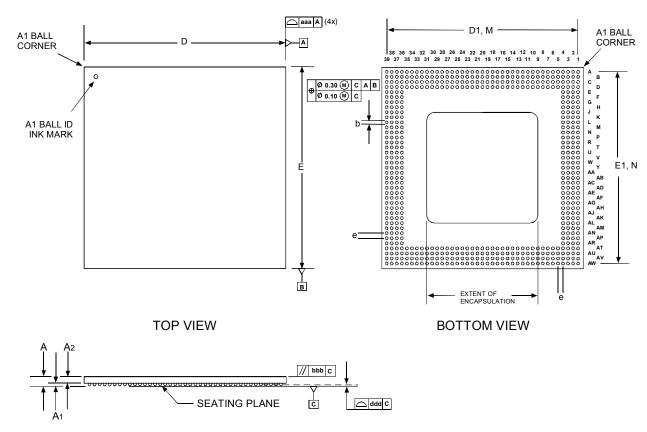

| 21 | Mec   | hanical Inf  | ormation                                  |     |

# **List of Figures**

| Figure 1 Representative TSE Application                             | 18  |

|---------------------------------------------------------------------|-----|

| Figure 2 Fabric with One Plane of Depth One                         | 19  |

| Figure 3 Fabric with Two Planes of Depth One.                       | 20  |

| Figure 4 Fabric with Four Planes of Depth One.                      | 20  |

| Figure 5 Fabric with One Plane of Depth Three and Height Thirty-Two | 21  |

| Figure 6 Fabric with One Plane of Depth Three and Height Sixty-Four | 22  |

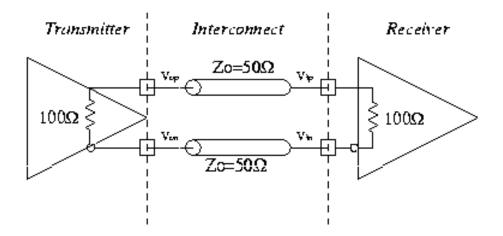

| Figure 7 Generic LVDS Link Block Diagram                            | 45  |

| Figure 8 Input Observation Cell (IN_CELL)                           | 124 |

| Figure 9 Output Cell (OUT_CELL)                                     | 124 |

| Figure 10 Bidirectional Cell (IO_CELL)                              | 125 |

| Figure 11 Layout of Output Enable and Bidirectional Cells           | 125 |

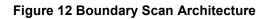

| Figure 12 Boundary Scan Architecture                                | 130 |

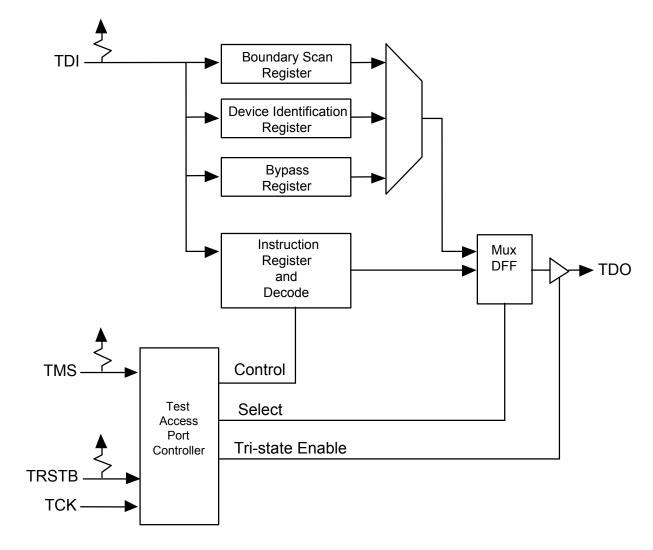

| Figure 13 TAP Controller Finite State Machine                       | 132 |

| Figure 14 "J0" Synchronization Control                              | 141 |

| Figure 15 Fabric Components                                         | 143 |

| Figure 16 LOAD:LOAD Null Fabrics.                                   | 144 |

| Figure 17 TBS Fabrics (non-redundant).                              | 145 |

| Figure 18 TSE Fabric (redundant).                                   | 146 |

| Figure 19 TSE Fabric with Differing Path Lengths                    | 147 |

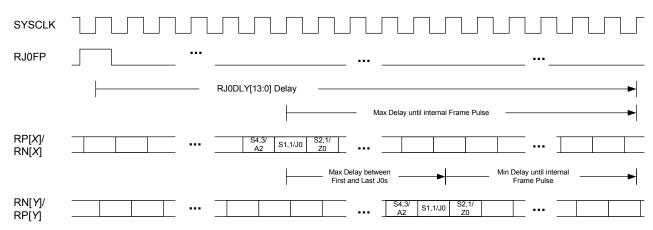

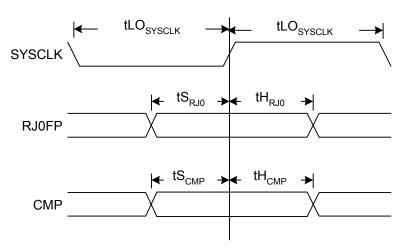

| Figure 20 Receive Interface Timing                                  | 148 |

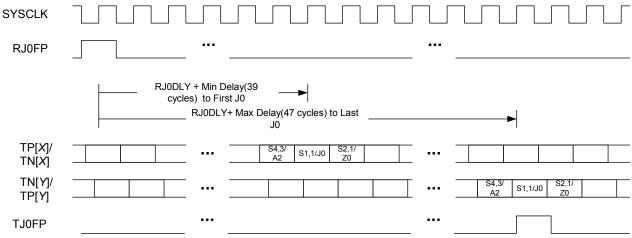

| Figure 21 Transmit Interface Timing                                 | 149 |

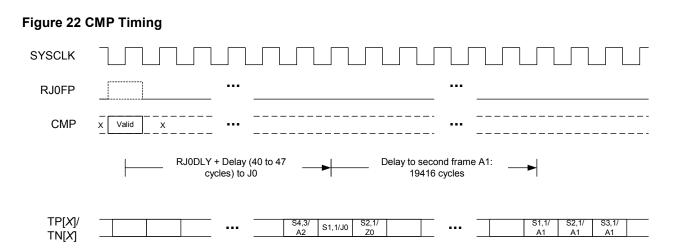

| Figure 22 CMP Timing                                                | 150 |

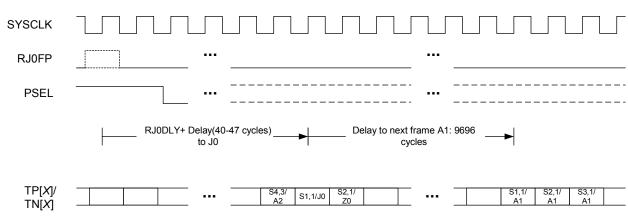

| Figure 23 PSEL Timing                                               | 150 |

| Figure 24 Sample RC Filter                                          | 154 |

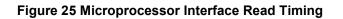

| Figure 25 Microprocessor Interface Read Timing                      | 158 |

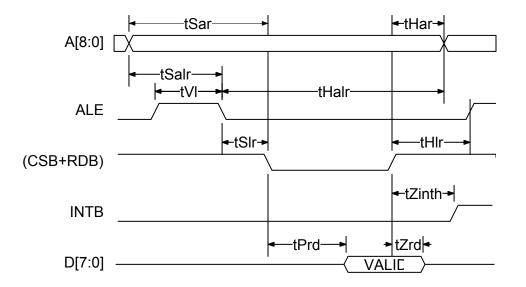

| Figure 26 Microprocessor Interface Write Timing                     | 159 |

| Figure 27 TSE Input Timing                                          | 161 |

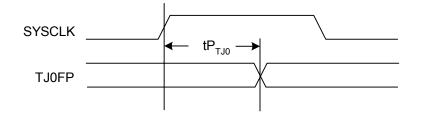

| Figure 28 TSE Output Timing                                         | 162 |

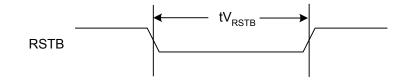

| Figure 29 RSTB Timing                                               | 163 |

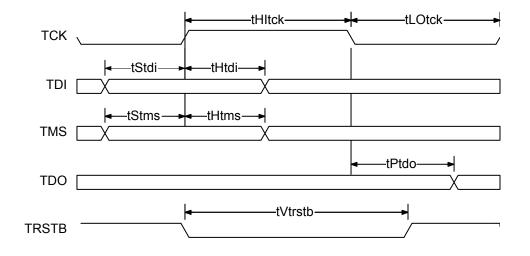

| Figure 30 JTAG Port Interface Timing                                | 165 |

### **List of Tables**

| Table 1 Pin Description LVDS Ports (256 Signals)              | 31  |

|---------------------------------------------------------------|-----|

| Table 2 Pin Description TSE Control and Clocking (5 Signals)  |     |

| Table 3 Pin Description Microprocessor Interface (34 Signals) |     |

| Table 4 Pin Description JTAG Port (5 Signals)                 |     |

| Table 5 Pin Description External Resistors (8 Signals)        |     |

| Table 6 Pin Description Analog Test Bus (8 Signals)           |     |

| Table 7 Pin Description Digital I/O Power (36 Signals)        | 40  |

| Table 8 Pin Description Analog Low Voltage Power (28 signals) | 41  |

| Table 9 Pin Description Analog Power                          | 41  |

| Table 10 Pin Description Ground (76 signals)                  |     |

| Table 11 Pin Description No Connect (20 signals)              | 43  |

| Table 12 TelecomBus Control Characters                        |     |

| Table 13 Control Word Index                                   |     |

| Table 14 Instruction Register (Length – 3 bits)               | 122 |

| Table 15 Identification Register                              | 122 |

| Table 16 Boundary Scan Register Length – 57 bits              | 122 |

| Table 17 Power Reduction for Disabled Links                   | 126 |

| Table 18 Absolute Maximum Ratings                             | 151 |

| Table 19 Power Requirements                                   | 152 |

| Table 20 D.C. Characteristics                                 | 155 |

| Table 21 Microprocessor Interface Read Access                 | 157 |

| Table 22 Microprocessor Interface Write Access                | 159 |

| Table 23 TSE Input Timing (Figure 27)                         | 161 |

| Table 24 TSE Output Timing (Figure 28)                        | 162 |

| Table 25 RSTB Timing (Figure 29)                              | 163 |

| Table 26 Serial TelecomBus Interface                          | 164 |

| Table 27 JTAG Port Interface (Figure 30)                      | 164 |

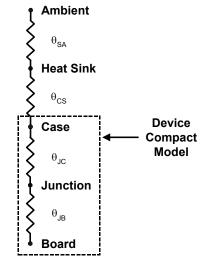

| Table 28 Outside Plant Thermal Information                    | 167 |

| Table 29 Device Compact Model <sup>3</sup>                    | 167 |

| Table 30 Heat Sink Requirements                               | 167 |

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers' Internal Use Document ID: PMC-1991258, Issue 7

### **List of Registers**

| Register 0000H: TSE Master Reset, Identity                                                | 60  |

|-------------------------------------------------------------------------------------------|-----|

| Register 0001H: TSE Master Clock Activity and Accumulation Trigger                        | 61  |

| Register 0002H: TSE Master Configuration                                                  | 63  |

| Register 0003H: TSE Master Interrupt Block Identifier                                     | 65  |

| Register 0004H: TSE Master R8FA Interrupt Source #1                                       | 67  |

| Register: 0005H: TSE Master R8FA Interrupt Source #2                                      | 68  |

| Register 0006H: TSE Master R8FA Interrupt Source #3                                       | 69  |

| Register 0007H: TSE Master R8FA Interrupt Source #4                                       | 70  |

| Register 0008H: TSE Master T8DE Interrupt Source #1                                       | 71  |

| Register 0009H: TSE Master T8DE Interrupt Source #2                                       | 72  |

| Register 000AH: TSE Master T8DE Interrupt Source #3                                       | 73  |

| Register 000BH: TSE Master T8DE Interrupt Source #4                                       | 74  |

| Register 000CH: TSE Master ITSE Interrupt Source                                          | 75  |

| Register 000DH: TSE Master ETSE Interrupt Source                                          | 76  |

| Register 000EH: TSE Master CSTR Interrupt Source                                          | 77  |

| Register 000FH: TSE Master User Defined                                                   | 78  |

| Register 0010H: TSE Master JTAG ID High                                                   | 79  |

| Register 0011H: TSE Master JTAG ID Low                                                    | 80  |

| Register 0020H, 00024H, 0028H, 002CH: CSTR #1 – #4 Control                                | 81  |

| Register 0021H, 00025H, 0029H, 002DH: CSTR #1 – #4 Interrupt Enable and                   | ~~~ |

|                                                                                           |     |

| Register 0022H, 00026H, 002AH, 002EH: CSTR #1 – #4 Interrupt Indication                   |     |

| Register 0040H: SSWT RJ0FP Delay                                                          |     |

| Register 0041H: SSWT Indirect Control Address                                             |     |

| Register 0042H: SSWT Indirect Control Data                                                |     |

| Register 0043H: SSWT Interrupt Enable                                                     |     |

| Register 0044H: SSWT Interrupt Status                                                     |     |

| Register 0047H: SSWT TJ0FP Delay                                                          | 92  |

| Register 0N80H, 0N88H, 0N90H, 0N98H: Port Set #1 - #16 R8FA #1 - #4 Control<br>and Status | 93  |

|                                                                                           |     |

| Register 0N81H, 0N89H, 0N91H, 0N99H: Port Set #1 - #16 R8FA #1 - #4<br>Interrupt Status          | 96  |

|--------------------------------------------------------------------------------------------------|-----|

| Register 0N82H, 0N8AH, 0N92H, 0N9AH: Port Set #1 - #16 R8FA #1 - #4 Line<br>Code Violation Count | 98  |

| Register 0N83H, 0N8BH, 0N93H, 0N9BH: Port Set #1 - #16 RXLV and DRU #1 -<br>#4 Control           | 99  |

| Register 0NA0H: Port Set #1 - #16, ITSE Indirect Address                                         | 101 |

| Register 0NA1H: Port Set #1 - #16 ITSE Indirect Data                                             | 103 |

| Register 0NA2H: Port Set #1 - #16 ITSE Configuration                                             | 105 |

| Register 0NA3H: Port Set #1 - #16, ITSE Interrupt Status                                         | 107 |

| Register 0NA8H: Port Set #1 - #16, ETSE Indirect Address                                         | 108 |

| Register 0NA9H: Port Set #1 - #16, ETSE Indirect Data                                            | 110 |

| Register 0NAAH: Port Set #1 - #16, ETSE Configuration                                            | 112 |

| Register 0NABH: Port Set #1 - #16, ETSE Interrupt Status                                         | 114 |

| Register 0NB0H, 0NB8H, 0NC0H, 0NC8H: Port Set #1 - #16, T8DE #1 - #4<br>Control and Status       | 115 |

| Register 0NB1H, 0NB9H, 0NC1H, 0NC9H: Port Set #1 - # 16 T8DE #1 - #4<br>Interrupt Status         | 117 |

| Register 0NB4H, 0NBCH, 0NC4H, 0NCCH: Port Set #1 - #16 T8DE #1 - #4 Test<br>Pattern              | 118 |

| Register 0NB5H, 0NBDH, 0NC5H, 0NCDH: Port Set #1 - #16, TXLV and PISO<br>Control                 | 119 |

|                                                                                                  |     |

### 1 Features

- Implements a Time-Space-Time fabric with STS-1/AU-3 granularity

- Provides 64 ingress STS-12 links for a total of 64\*12 = 768 STS-1 streams

- Provides 64 egress STS-12 links consisting of 768 STS-1 streams

- Supports non-blocking permutation switching of 768 STS-1 flows at STS-1 granularity

- Interfaces to STS-48 and STS-192 devices by aggregating 4 and 16 STS-12 flows respectively

- Supports multicast and broadcast of STS-1 streams

- Supports multi-plane (inverse multiplexed) switch architectures in conjunction with the PM5310 TBS<sup>™</sup> device and PM7390 S/UNI®-MACH48

- Recovers clock and data at each ingress port, synchronizes with an internal 77.76 MHz clock, and produces egress streams with a common 777.6 MHz clock

- Detects and reports inactive or errored LVDS links via the microprocessor interface

- Supports two sets of switch settings and a controlled method of changing settings on STS-1 frame boundaries

- Supports multiple fabric architectures that range from 40 Gb/s (one device) to 160 Gb/s (four devices) in a single stage, and up to 2.5 Tb/s using multi-stage fabrics

- Ingress to egress STS-1 switching latency of approximately 840ns

- Supported by an efficient algorithm to compute control settings for all permutation loads for all supported fabric architectures. Algorithms are also available for multicast/broadcast allocation

- 1.8V CMOS core and 3.3V CMOS/LVDS input/output

- Requires no external RAMs or logic parts

- Provides a standard IEEE 1149.1 JTAG port

- Power Consumption of 8.3 W (typical)

- Packaged in a 560 pin 40mm by 40mm UltraBGA

- Supports a 16-bit microprocessor interface that is used to initialize the device, to write switch settings into on-chip control tables, and to monitor device performance

## 2 Applications

- Optical Cross Connects

- STS-1 Cross Connects

- Multi-service provisioning platforms

- SONET/SDH Add/Drop Multiplexers

- SONET/SDH Digital Cross Connects

### 3 References

- 1. ANSI T1.105-1995, "Synchronous Optical Network (SONET) Basic Description including Multiplex Structure, Rates, and Formats", 1995

- 2. Bell Communications Research SONET Transport Systems: Common Generic Criteria, GR-253-CORE, Issue 2, Revision 2, January 1999

- 3. ITU, Recommendation G.707 "Digital Transmission Systems Terminal equipments General", March 1996

- 4. IEEE 802.3, "Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications", Section 36.2, 1998

- A.X. Widmer and P.A. Franaszek, "A DC-Balanced, Partitioned-Block, 8B/10B Transmission Code," IBM Journal of Research and Development, Vol. 27, No 5, September 1983, pp 440-451

- 6. U.S. Patent No. 4,486,739, P.A. Franaszek and A.X. Widmer, "Byte Oriented DC Balanced (0,4) 8B/10B Partitioned Block Transmission Code," December 4, 1984

- 7. IEEE Std 1596.3-1996, "IEEE Standard for Low-Voltage Differential Signals (LVDS) for Scalable Coherent Interface (SCI)", Approved March 21, 1996

- 8. L.R. Ford, D.R. Fulkerson, "Flows in Networks", Maximum Cardinality Matchings in Bipartite Graphs

# 4 Application Examples

### 4.1 Motivating Applications

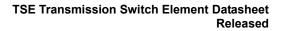

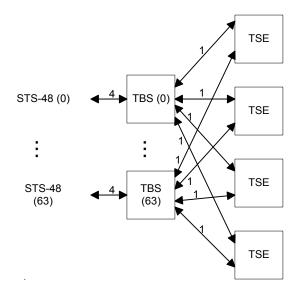

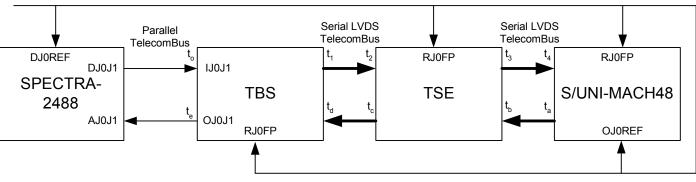

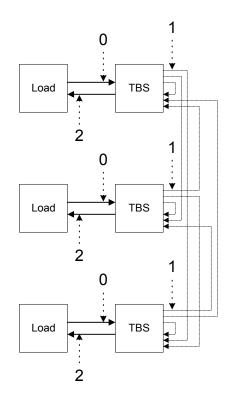

The PM5372 device is principally used in applications where cross-connecting of STS-1/AU-3 streams is required. Such applications include Add-Drop Multiplexers, STS-1 Cross-Connects, Optical Cross-Connects and Multi-Service Provisioning Platforms. Multi-Service Provisioning Platforms may also use an STS-1 cross-connect fabric to decouple the physical layer from the service layer. These products may integrate the DCS, ADM, switching, routing and broadcast capabilities. Part of an example architecture is illustrated in Figure 1. In this application, the cross-connect fabric consists of the TSE<sup>TM</sup> devices. The TSE devices support a Time-Space-Time switch architecture. Note that the following example has two complete TSE fabrics to support "1+1" fabric redundancy. The TSEs labeled *Fab A* compose the primary or working fabric. The TSEs labeled *Fab B* compose the secondary or protect fabric.

#### Figure 1 Representative TSE Application

### 4.2 TSE Fabric Scaling

Independent of the application described above, the TSE is a general STS-1/AU-3 granularity fabric. As a fabric, it supports multiple architectures which scale in aggregate bandwidth from 40 Gb/s to 2.5 Tb/s (and larger, until limited by packaging concerns). Fabrics up to 160 Gb/s (i.e. 4 TSE devices) are supported in a single stage architecture. All fabrics are rearrangably non-blocking under all 100% loaded permutations of unicast traffic. Scaling of these TSE architectures is accomplished by two mechanisms: division of the fabric into multiple *planes*, and deepening of the fabric into multiple *stages*, where each stage may be of some power-of-two *height*, up to a maximum depending on the number of *stages*. A plane of TSEs within a fabric is defined as a group of connected TSEs unconnected to other TSE groups in the fabric. A multiple plane fabric requires distributing the connections of each serializer's I/O to all planes. The PM5310 TBS device with its four serial streams, can be used to implement a one, two, or four plane fabric.

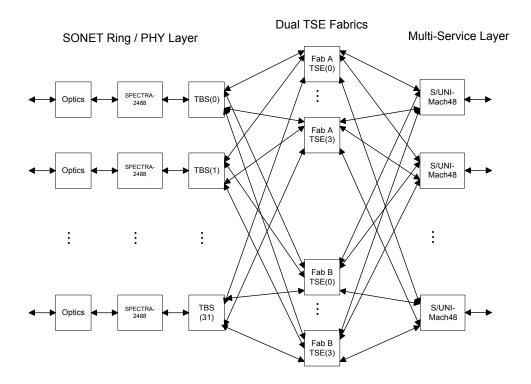

Figure 2 illustrates the simplest TSE fabric. One TSE is connected to 16 full-duplex STS-48 loads via 16 TBS devices, providing an aggregate switch bandwidth of 40 Gb/s using one TSE and 16 TBS devices. The TBS devices in Figure 2 are used only to serialize Parallel TelecomBuses (P-TCB). Where OC-48 load devices have Serial TelecomBuses (S-TCB) interfaces, the TBS devices are unnecessary. Each STS-48 load is connected by four full-duplex links. The links from the Loads to the TBS devices are Parallel TelecomBuses (P-TCB), which are 4 \* 8 bits at 77.76 MHz; all links to/from TSE devices are Serial TelecomBuses (S-TCB), which are 4 \* 777.6 MHz LVDS links. In each *depth* one TSE fabric, the TSE devices form non-blocking Time-Space-Time fabrics.

#### Figure 2 Fabric with One Plane of Depth One.

(STS-48 Sources = 16; Aggregate Bandwidth = 40 Gb/s; TSE Chip Count = 1; TBS Chip Count = 16)

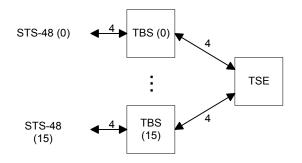

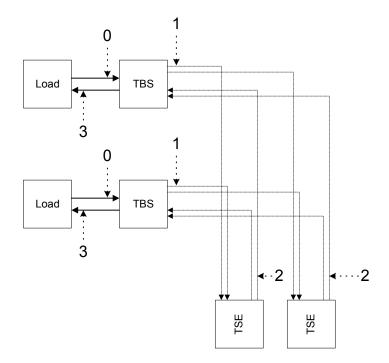

Figure 3 illustrates a two-plane TSE fabric. Each of 32 full-duplex STS-48 loads on 32 TBS devices are connected by two LVDS links each to each of two TSE devices. The aggregate switch bandwidth is 80 Gb/s at a cost of two TSE devices and 32 TBS devices.

#### Figure 3 Fabric with Two Planes of Depth One.

(STS-48 Sources = 32; Aggregate Bandwidth = 80 Gb/s; TSE Chip Count = 2; TBS Chip Count = 32)

In multi-plane TSE fabrics, TBS devices (or Load devices with equivalent S-TCB ports) perform the load balancing required by the inverse-multiplexed (i.e., multi-plane) TSE fabric.

Figure 4 illustrates a four-plane TSE fabric, representing the largest STS-48 fabric with a *depth* of one. Each of 64 full-duplex STS-48 loads on 64 TBS devices are connected by one LVDS link each to each of four TSE devices. The aggregate switch bandwidth is 160 Gb/s at a cost of four TSE devices.

#### Figure 4 Fabric with Four Planes of Depth One.

(STS-48 Sources = 64; Aggregate Bandwidth = 160 Gb/s; TSE Chip Count = 4; TBS Chip Count = 64)

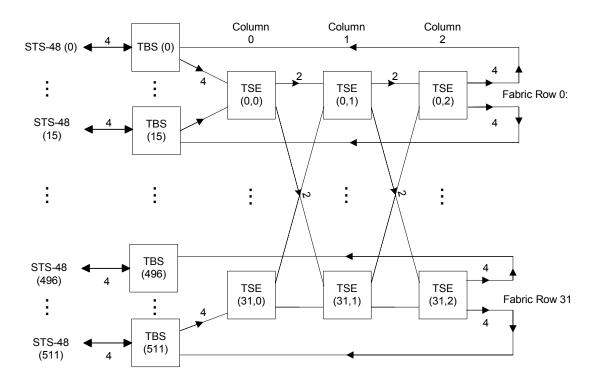

Figure 5 illustrates a three *stage* TSE fabric (*depth* = 3), with a *height* of 32. Each of 512 fullduplex STS-48 loads on 512 TBS devices are connected by four LVDS links each to a TSE. The receive ports for each TSE in Column 0 is connected to the 4 transmit LVDS links of 16 TBS devices, for example TSE(0,0) receives from TBS(0) through TBS(15). The transmit LVDS links of each TSE in column 0 fan out to all 32 TSEs in column 1, with 2 links per transmit/receive device pair. Transmit links for column 1 TSEs fan out similarly to column 2 TSEs. Transmit links of column 2 TSEs connect back to the TBS devices. Each column 2 TSE connects with 16 TBS devices, with 4 transmit LVDS links per device pair, for example TSE(0,2) transmits to TBS(0) through TBS(15).The aggregate switch bandwidth is 1,280 Gb/s using 96 TSE devices and 512 TBS devices.

#### Figure 5 Fabric with One Plane of Depth Three and Height Thirty-Two.

(STS-48 Sources = 512; Aggregate Bandwidth 1280 Gb/s; TSE Chip Count = 96; TBS Chip Count = 512)

Fabrics with *depth* greater than one have redundant internal time stages where TSE devices communicate with TSE devices. These redundant stages can be set to the identity mapping at startup, and then ignored during system operation.

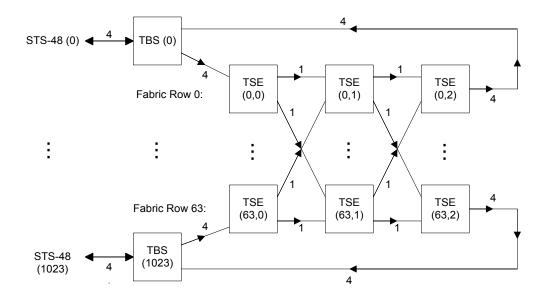

Figure 6 illustrates the largest single-plane, three-stage fabric that has an aggregate bandwidth of 2560 Gb/s. The difference between this example and the one shown in Figure 5 is that this one extends the fabric to its full *height* of 64 TSE devices, whereas the fabric in Figure 5 limited the *height* to 32 TSE devices.

Figure 6 Fabric with One Plane of Depth Three and Height Sixty-Four

(STS-48 Sources = 1024; Aggregate Bandwidth = 2560 Gb/s; TSE Chip Count = 192; TBS Chip Count = 1024)

Larger TSE fabrics can be constructed in several ways by extending the architectural techniques shown above. In particular, the fabric shown in Figure 6 can be sliced into two or four *planes* (for STS-48), yielding fabrics up to 5120 Gb/s or 10,240 Gb/s, respectively. Furthermore, five stages of TSE devices can be used to build *deeper* fabrics (which permit greater *height*). Additionally, STS-192 fabrics with up to 16 planes of TSE devices can be constructed.

### 4.3 Redundant Fabrics

All of the TSE fabrics discussed above can be replicated to form dual redundant fabrics (as shown in Figure 1) for 1+1 Equipment Protection. Support for this feature is independent of the TSE - it requires error detection and dual ports in the feeder devices (e.g. TBS and the S/UNI-MACH48) as well as dual LVDS ports and failure switch-over logic in the TBS.

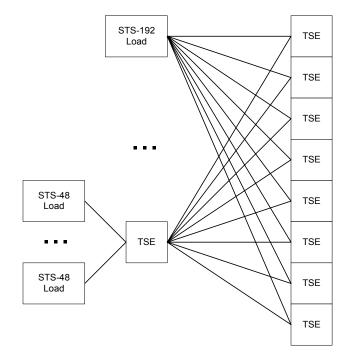

### 4.4 Non-STS-48 Loads

The TSE also supports both STS-12 and STS-192 loads. Each STS-12 device consumes only one parallel port (8 bits at 77.76 MHz) on a TBS or S/UNI-MACH48, whereas an STS-48 device consumes all four parallel ports (4 \* 8 bits at 77.76 MHz) on a TBS or S/UNI-MACH48. Each STS-192 device consumes all four parallel ports on four TBS or S/UNI-MACH48 devices. The TSE/TBS (or S/UNI-MACH48) fabric sees only sets of STS-12 ports; as the TSE/TBS (S/UNI-MACH48) fabric supports any STS-1 to STS-1 permutation, the possible collection of STS-1s or STS-12s into STS-48s or STS-192s is immaterial to the fabric.

STS-192 loads permit TSE fabrics to grow to eight or sixteen planes, in which two or one STS-12 LVDS links are used to communicate between the STS-192 sources and the multiple planes of the fabric. In such fabrics, TSE devices can be used to gather/scatter traffic from lower aggregate rate devices into the multi-plane fabric (it is necessary that all such lower rate devices be able to communicate with all planes of any fabric).

Where STS-12 loads are used in multi-plane fabrics, the TBS is used to distribute and gather traffic across the multiple planes of the fabric. It is also possible to use an additional TSE to perform this STS-12 grooming function for up to 32 STS-12 sources.

### 4.5 TSE Fabric Packaging

TSE fabrics can be packaged on PCBs in a variety of ways. The 777.6 MHz LVDS serial links are used to communicate between the port cards and the fabric cards. With careful PCB, connector, and back-plane design, no bus drivers will be required.

In such packaging of TSE fabrics, the concentration of all the TSE devices onto special fabric cards, and the non-involvement of the TBS devices in the switching function (they only serialize the TelecomBus and provide the fan-out to (possible) dual fabrics) permit all Automatic Protection Switching (APS) switch setting changes to be concentrated on the fabric cards; general connection establishment setup requires access to the connected TBS devices.

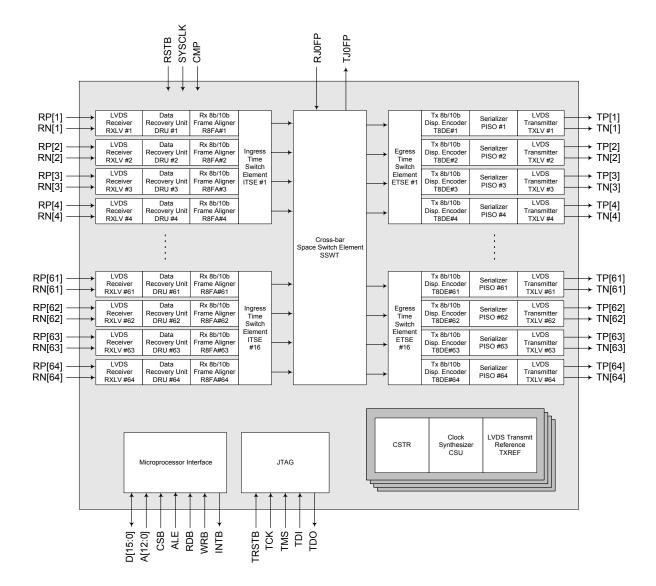

### 5 Block Diagram

#### **Block Diagram**

## 6 Description

The PM5372 TSE is a monolithic CMOS integrated circuit that performs STS-1 granularity cross-connecting.

The TSE receives data on 64 777.6 MHz LVDS links. Each link contains a STS-12/STM-4 stream. Bytes on the links are carried as 8B/10B characters. At minimum, each stream must include a 8B/10B special framing character to allow the TSE to character and frame align the stream. Additionally, the TSE can support a serial TelecomBus protocol, in which TelecomBus control signals are encoded as 8B/10B special characters. Data is switched through the TSE in 8B/10B code words. The TSE performs character and frame alignment on each stream. The TSE aligns data from multiple sources prior to switching the data. Data alignment is achieved by synchronizing the Frame Aligners in transmitting their aligned frame data. The TSE switches the STS-12 aligned data streams at STS-1 granularity through Time, Space, and then Time switch stages. The time switch stages perform timeslot interchange on the STS-12 data stream. The Space switch stage switches data from one STS-12 pipe to another. Each time slot is switched independently in the Space switch stage.

The TSE supports software configurable dual-page switch settings. This permits new switch settings to be stored in the inactive page of control settings, while the TSE operates on the active page of control settings. The TSE switches between control setting pages on STS-1 frame boundaries for hitless switchover through the device page select pin CMP. Block-by-block switchover is facilitated by software configurable page select bits.

The TSE transmits data on 64 777.6 MHz LVDS links. As on the receive side, a link contains a STS-12/STM-4 stream, encoded as 8B/10B characters. Prior to transmission and following switching, the TSE must reprocess each stream for correct 8B/10B disparity.

The function of the TSE is explained with respect to the block diagram. The flow in the block diagram is left-to-right. The left-most three units on each of the 64 STS-12 flows (LVDS Receiver, Data Recovery Unit, and Receive 8B/10B Frame Aligner) receive, decode and align the incoming flows. The Ingress Time Switch Elements perform timeslot interchange on the STS-12 stream. The Space Switch Element permits arbitrary permutations over space during each time step. The Egress Time Switch Elements implements another STS-12 timeslot interchange. The right-most three units (Transmit 8B/10B Disparity Encoder, Serializer, and LVDS Transmitter) reencode, serialize and transmit the output streams. Switch control is distributed among the time and space switching modules. Switch control is organized into pages of control words which determine what permutations are implemented for each of the twelve STS-1 positions (in time) at each of the 64 ports (in space) for the switching stage. The Microprocessor Interface is used to initialize the TSE and to access the switch control settings. JTAG is supported on non-LVDS signal for board testing. The three modules (CSTR, CSU, and TXREF) provide clock and voltage references for the other LVDS modules.

Multiple fabric architectures can be supported, although the focus is on fabrics which are nonblocking under 100% permutation loads. The TSE also supports multicast capabilities.

## 7 Pin Diagram

The TSE is packaged in a custom Ultra-BGA with 560 balls.

#### Pin Diagram Top Left Corner

|   | 39      | 38         | 37       | 36       | 35   | 34   | 33    | 32      | 31      | 30        | 29   | 28      | 27        | 26     | 25     | 24      | 23     | 22     | 21   |

|---|---------|------------|----------|----------|------|------|-------|---------|---------|-----------|------|---------|-----------|--------|--------|---------|--------|--------|------|

| A | VSS     | VSS        | VSS      | VSS      | A[4] | A[7] | A[10] | VDDI    | VSS     | TP[50]    | VSS  | TP[52]  | VSS       | RN[51] | VSS    | TP[53]  | VSS    | TP[56] | VSS  |

| в | VSS     | VDDO       | VDDO     | VDDO     | A[5] | A[8] | A[11] | NC      | TP[49]  | TN [ 50 ] | NC   | TN [52] | RN [ 50 ] | RP[51] | RN[52] | TN [53] | TP[55] | TN[56] | AVDL |

| с | VSS     | VDDO       | VDDO     | VDDO     | A[6] | VDDI | VDDI  | NC      | TN[49]  | TP[51]    | VDDI | RN[49]  | RP[50]    | AVDL   | RP[52] | TP[54]  | TN[55] | RN[53] | VDDI |

| D | VSS     | VDDO       | VDDO     | VDDO     | VDDI | A[9] | VDDI  | ATB0[4] | ATB1[4] | TN[51]    | AVDH | RP[49]  | VDDI      | VDDI   | AVDH   | TN[54]  | VDDI   | RP[53] | AVDH |

| Е | A[3]    | A[2]       | A[0]     | A[1]     |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| F | VSS     | VDDI       | NC       | AVDH     |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| G | RESK    | RES        | RN[48]   | RP[48]   |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| н | VSS     | RN[47]     | RP[47]   | AVDL     |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| J | RN[46]  | RP[46]     | RN[45]   | RP[45]   |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| ĸ | VSS     | TP[48]     | TN [48]  | AVDH     |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| L | TP[47]  | TN [47]    | TP[46]   | TN [46]  |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| М | VSS     | TP[45]     | TN [45]  | VDDI     |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| N | RN [44] | RP[44]     | RN[43]   | RP[43]   |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| P | vss     | RN[42]     | RP[42]   | AVDH     |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| R | VDDI    | AVDL       | RN[41]   | RP[41]   |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| т | VSS     | TP[44]     | TN [44]  | VDDI     |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| U | TP[43]  | TN [ 4 3 ] | TP[42]   | TN[42]   |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| v | TP[41]  | TN [ 41 ]  | CSU_AVDI | CSU_AVDL |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| W | RN[40]  | RP[40]     | CSU_AVDI | csu_avdh |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

| Y | RN[38]  | RP[38]     | RN[39]   | RP[39]   |      |      |       |         |         |           |      |         |           |        |        |         |        |        |      |

#### Pin Diagram Top Right Corner

| 20      | 19       | 18       | 17     | 16      | 15     | 14     | 13     | 12        | 11      | 10      | 9      | 8      | 7      | 6    | 5             | 4       | 3     | 2      | 1      |   |

|---------|----------|----------|--------|---------|--------|--------|--------|-----------|---------|---------|--------|--------|--------|------|---------------|---------|-------|--------|--------|---|

| RN [54] | RN [56]  | TP[57]   | TP[59] | VSS     | VDDI   | VSS    | RN[60] | VSS       | TP[63]  | VSS     | RN[62] | VSS    | RESK   | VSS  | A[12]/TR<br>S | VSS     | VSS   | VSS    | VSS    | 1 |

| RP[54]  | RP[56]   | TN [57]  | TN[59] | TP[60]  | AVDL   | RN[58] | RP[60] | TP[61]    | TN [63] | TP[64]  | RP[62] | RN[63] | RES    | NC   | SYSCLK        | VDDO    | VDDO  | VDDO   | VSS    | 1 |

| RN [55] | CSU_AVDL | CSU_AVDL | TP[58] | TN [60] | RN[57] | RP[58] | RN[59] | TN [ 61 ] | TP[62]  | TN [64] | RN[61] | RP[63] | RN[64] | NC   | RJÛFP         | VDDO    | VDDO  | VDDO   | VSS    | 0 |

| RP[55]  | csu_avdh | CSU_AVDL | TN[58] | VDDI    | RP[57] | AVDH   | RP[59] | VDDI      | TN [62] | AVDH    | RP[61] | AVDL   | RP[64] | AVDH | VDDI          | VDDO    | VDDO  | VDDO   | VSS    | 1 |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | CMP     | CSB   | TDO    | VDDI   | 1 |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | WRB     | ALE   | RDB    | VDDI   | 1 |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | VDDI    | VDDI  | TJOFP  | INTB   |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | ATB0[1] | NC    | NC     | VDDI   |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | ATB1[1] | TN[1] | TP[1]  | VSS    |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | TN[3]   | TP[3] | TN [2] | TP[2]  |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | AVDH    | VDDI  | NC     | VSS    |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | RP[1]   | RN[1] | TN [4] | TP[4]  |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | VDDI    | RP[2] | RN[2]  | VSS    |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | VDDI    | AVDL  | RP[3]  | RN[3]  |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | AVDH    | RP[4] | RN [4] | VSS    |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | TN[6]   | TP[6] | TN [5] | TP[5]  |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | VDDI    | TN[7] | TP[7]  | VSS    |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | RP[5]   | RN[5] | TN[8]  | TP[8]  |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | AVDH    | VDDI  | AVDL   | VSS    |   |

|         |          |          |        |         |        |        |        |           |         |         |        |        |        |      |               | RP[7]   | RN[7] | RP[6]  | RN [6] |   |

AA VSS AVDL VDDI AVDH

|    | 39     | 38     | 37     | 36      | 35    | 34   | 33     | 32     | 31     | 30     | 29     | 28     | 27     | 26     | 25     | 24     | 23     | 22           | 21           |

|----|--------|--------|--------|---------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------------|--------------|

| AW | VSS    | VSS    | VSS    | VSS     | NC    | VSS  | RESK   | VSS    | RN[30] | VSS    | TP[31] | VSS    | RN[28] | VSS    | VDDI   | VSS    | TP[27] | TP[25]       | RN[24]       |

| AV | VSS    | VDDO   | VDDO   | VDDO    | TRSTB | NC   | RES    | RN[31] | RP[30] | TP[32] | TN[31] | TP[29] | RP[28] | RN[26] | AVDL   | TP[28] | TN[27] | TN[25]       | RP[24]       |

| AU | VSS    | VDDO   | VDDO   | VDDO    | RSTB  | NC   | RN[32] | RP[31] | RN[29] | TN[32] | TP[30] | TN[29] | RN[27] | RP[26] | RN[25] | TN[28] | TP[26] | CSU_AVD<br>L | CSU_AVD<br>L |

| AT | VSS    | VDDO   | VDDO   | VDDO    | VDDI  | AVDH | RP[32] | AVDL   | RP[29] | AVDH   | TN[30] | VDDI   | RP[27] | AVDH   | RP[25] | VDDI   | TN[26] | CSU_AVD<br>L | CSU_AV<br>DH |

| AR | VDDI   | D[8]   | D[10]  | D[9]    |       |      |        |        |        |        |        |        | 1      |        |        |        |        |              |              |

| AP | VDDI   | D[11]  | D[13]  | D[12]   |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AN | D[14]  | VDDI   | VDDI   | D[15]   |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AM | VDDI   | NC     | NC     | ATB0[3] |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AL | VSS    | TP[33] | TN[33] | ATB1[3] |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AK | TP[34] | TN[34] | TP[35] | TN[35]  |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AJ | VSS    | NC     | VDDI   | AVDH    | Į     |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AH | TP[36] | TN[36] | RN[33] | RP[33]  |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AG | VSS    | RN[34] | RP[34] | VDDI    |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AF | RN[35] | RP[35] | AVDL   | VDDI    |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AE | VSS    | RN[36] | RP[36] | AVDH    |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AD | TP[37] | TN[37] | TP[38] | TN[38]  |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AC | VSS    | TP[39] | TN[39] | VDDI    |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

| AB | TP[40] | TN[40] | RN[37] | RP[37]  |       |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

|    |        |        |        |         | Į     |      |        |        |        |        |        |        |        |        |        |        |        |              |              |

#### Pin Diagram Bottom Left Corner

RP[23]

RN [23]

RP[22]

RN [ 22 ]

20

AVDH

VDDI

AVDL

VSS

19

RP[21]

RN[21]

TN[24]

TP[24]

18

VDDI

TN[23]

TP[23]

VSS

17

TN[22]

TP[22]

TN[21]

TP[21]

16

AVDH

RP[20]

RN[20]

VSS

15

VDDI

AVDL

RP[19]

RN[19]

14

VDDI

RP[18]

RN[18]

VSS

13

RP[17]

RN[17]

TN[20]

TP[20]

12

AVDH

VDDI

NC

VSS

11

TN[19]

TP[19]

TN[18]

TP[18]

10

#### Pin Diagram Bottom Right Corner

| ٦  |        |        |          |          |      |      |      |         |         |

|----|--------|--------|----------|----------|------|------|------|---------|---------|

| АА | RN[8]  | RP[8]  | CSU_AVDL | CSU_AVDH |      |      |      |         |         |

| АВ | TP[9]  | TN [9] | CSU_AVDL | CSU_AVDL |      |      |      |         |         |

| ас | TP[11] | TN[11] | TP[10]   | TN [10]  |      |      |      |         |         |

| AD | VSS    | TP[12] | TN[12]   | VDDI     |      |      |      |         |         |

| AE | VDDI   | AVDL   | RN[9]    | RP[9]    |      |      |      |         |         |