DATA SHEET PMC-1990267

ISSUE 2

SATURN USER NETWORK INTERFACE FOR J2, E3, T3

# PM7347

# S/UNI-JET

# SATURN USER NETWORK INTERFACE FOR J2/E3/T3

DATA SHEET

ISSUE 2: MARCH 2000

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE

DATA SHEET PMC-1990267

ISSUE 2

SATURN USER NETWORK INTERFACE FOR J2, E3, T3

# **CONTENTS**

| 1  | APPLICATIONS                         | 6  |

|----|--------------------------------------|----|

| 2  | REFERENCES                           | 7  |

| 3  | DATASHEET OVERVIEW                   | 9  |

| 4  | BLOCK DIAGRAM                        |    |

| 5  | PIN DIAGRAM                          | 11 |

| 6  | PIN DESCRIPTION                      |    |

|    | 6.1 JTAG TEST ACCESS PORT            |    |

|    | 6.2 MICROPROCESSOR INTERFACE         |    |

| 7  | TEST FEATURES DESCRIPTION            |    |

|    | 7.1 TEST MODE 0 DETAILS              |    |

|    | 7.2 JTAG TEST PORT                   |    |

| 8  | OPERATION                            | 60 |

|    | 8.1 SOFTWARE INITIALIZATION SEQUENCE |    |

| 9  | ABSOLUTE MAXIMUM RATINGS             |    |

| 1( | 0 D.C. CHARACTERISTICS               | 63 |

| 11 | 1 ORDERING AND THERMAL INFORMATION   | 65 |

| 12 | 2 MECHANICAL INFORMATION             | 66 |

**ISSUE 2**

#### **FEATURES**

- Single chip ATM User Network Interface operating at 44.736 Mbit/s, 34.368 Mbit/s, and 6.312 Mbit/s conforming to af-phy-0054.000, af-phy-0034.000 and AF-PHY-0029.000.

- Implements ATM Direct Cell Mapping into DS1, DS3, E1, E3, and J2 transmission systems according to ITU-T Recommendation G.804.

- Provides a UTOPIA Level 2 compatible ATM-PHY Interface.

- Implements the Physical Layer Convergence Protocol (PLCP) for DS1 and DS3 transmission systems according to the ATM Forum User Network Interface Specification and ANSI TA-TSY-000773, TA-TSY-000772, and E1 and E3 transmission systems according to the ETSI 300-269 and ETSI 300-270.

- Support is provided for SMDS and ATM mappings into various rate transmission systems as follows:

| Rate                | Format       | Framer<br>Only | SMDS PLCP<br>Mapping | ATM Direct<br>Mapping |

|---------------------|--------------|----------------|----------------------|-----------------------|

| Т3                  | C-bit Parity | YES            | YES                  | YES                   |

| (44.736 Mbit/s)     | M23          | YES            | YES                  | YES                   |

| E3                  | G.751        | YES            | YES                  | YES                   |

| (34.368 Mbit/s)     | G.832        | YES            | n/a                  | YES                   |

| J2                  | G.704 & NTT  | YES            | n/a                  | YES                   |

| (6.312 Mbit/s)      |              |                |                      |                       |

| E1                  | CRC-4        | external       | YES                  | YES                   |

| (2.048 Mbit/s)      | PCM30        | external       | YES                  | YES                   |

| T1                  | ESF          | external       | YES                  | YES                   |

| (1.544 Mbit/s)      | SF           | external       | YES                  | YES                   |

| Arbitrary Cell Rate |              | bypass         | n/a                  | YES                   |

| (up to 52 Mbit/s)   |              |                |                      |                       |

#### Table 1 - Supported Operating Formats

- Implements the ATM physical layer for Broadband ISDN according to ITU-T Recommendation I.432.

- Provides on-chip DS3, E3 (G.751 and G.832), and J2 framers.

- Can be configured to be used solely as a DS3, E3, or J2 Framer.

ISSUE 2

SATURN USER NETWORK INTERFACE FOR J2, E3, T3

- When configured to operate as a DS3, E3, or J2 Framer, gapped transmit and receive clocks can be optionally generated for interface to devices which only need access to payload data bits.

- Provides support for an arbitrary rate external transmission system interface up to a maximum rate of 52 Mbit/s which enables the S/UNI-JET to be used as an ATM cell delineator.

- Uses the PMC-Sierra PM4351 COMET, PM4341 T1XC and PM6341 E1XC T1 and E1 framer/line interface chips for DS1 and E1 applications.

- Provides programmable pseudo-random test pattern generation, detection, and analysis features.

- Provides integral transmit and receive HDLC controller with 128-byte FIFO depth.

- Provides performance monitoring counters suitable for accumulation periods of up to 1 second.

- Provides an 8-bit microprocessor interface for configuration, control and status monitoring.

- Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

- Low power 3.3V CMOS technology with 5V tolerant inputs.

- Available in a 256-pin SBGA package (27mm x 27mm).

## The receiver section:

- Provides frame synchronization for the M23 or C-bit parity DS3 applications, alarm detection, and accumulates line code violations, framing errors, parity errors, path parity errors and FEBE events. In addition, far end alarm channel codes are detected, and an integral HDLC receiver is provided to terminate the path maintenance data link.

- Provides frame synchronization for the G.751 or G.832 E3 applications, alarm detection, and accumulates line code violations, framing errors, parity errors, and FEBE events. In addition, in G.832, the Trail Trace is detected, and an integral HDLC receiver is provided to terminate either the Network Requirement or the General Purpose data link.

- Provides frame synchronization for G.704 and NTT 6.312 Mbit/s J2 applications, alarm detection, and accumulates line code violations, framing errors, and CRC parity errors. An integral HDLC receiver is provided to terminate the data link.

- Provides frame synchronization, cell delineation and extraction for DS3, G.751 E3, G.832 E3, and G.704 and NTT J2 ATM direct-mapped formats.

- Provides PLCP frame synchronization, path overhead extraction, and cell extraction for DS1 PLCP, DS3 PLCP, E1 PLCP, and G.751 E3 PLCP formatted streams.

- Provides a 50 MHz 8-bit wide or 16-bit wide Utopia FIFO buffer in the receive path with parity support, and multi-PHY (Level 2) control signals.

- Provides ATM framing using cell delineation. ATM cell delineation may optionally be disabled to allow passing of all cell bytes regardless of cell delineation status.

- Provides cell descrambling, header check sequence (HCS) error detection, idle cell filtering, header descrambling (for use with PPP packets), and accumulates the number of received idle cells, the number of received cells written to the FIFO, and the number of HCS errors.

- Provides a four cell FIFO for rate decoupling between the line, and a higher layer processing entity. FIFO latency may be reduced by changing the number of operational cell FIFOs.

- Provides a receive HDLC controller with a 128-byte FIFO to accumulate data link information.

- Provides detection of yellow alarm and loss of frame (LOF), and accumulates BIP-8 errors, framing errors and FEBE events.

- Provides programmable pseudo-random test-sequence detection (up to 2<sup>32</sup>-1 bit length patterns conforming to ITU-T O.151 standards) and analysis features.

#### The transmitter section:

- Provides frame insertion for the M23 or C-bit parity DS3 applications, alarm insertion, and diagnostic features. In addition, far end alarm channel codes may be inserted, and an integral HDLC transmitter is provided to insert the path maintenance data link.

- Provides frame insertion for the G.751 or G.832 E3 applications, alarm insertion, and diagnostic features. In addition, for G.832, the Trail Trace is inserted, and an integral HDLC transmitter is provided to insert either the Network Requirement or the General Purpose data link.

- Provides frame insertion for G.704 6.312 Mbit/s J2 applications, alarm insertion, and diagnostic features. An integral HDLC transmitter is provided to insert the path maintenance data link.

- Provides frame insertion and path overhead insertion for DS1, DS3, E1 or E3 based PLCP formats. In addition, alarm insertion and diagnostic features are provided.

- Provides a 50 MHz 8-bit wide or 16-bit wide Utopia FIFO buffer in the transmit path with parity support and multi-PHY (Level 2) control signals.

- Provides optional ATM cell scrambling, header scrambling (for use with PPP packets), HCS generation/insertion, programmable idle cell insertion, diagnostics features and accumulates transmitted cells read from the FIFO.

| PMC     | PMC-Sierra, Inc. |

|---------|------------------|

| ISSUE 2 | SATURN US        |

- Provides a four cell FIFO for rate decoupling between the line and a higher layer processing entity. FIFO latency may be reduced by changing the number of operational cells in the FIFO.

- Provides a transmit HDLC controller with a 128-byte FIFO.

- Provides an 8 kHz reference input for locking the transmit PLCP frame rate to an externally applied frame reference.

- Provides programmable pseudo-random test sequence generation (up to 2<sup>32</sup>-1 bit length sequences conforming to ITU-T O.151 standards). Diagnostic abilities include single bit error insertion or error insertion at bit error rates ranging from 10<sup>-1</sup> to 10<sup>-7</sup>.

#### Bypass and Loopback features:

- Allows bypassing of the DS3, E3, and J2 framers to enable transmission system sublayer processing by an external device.

- Allows bypassing of the PLCP and ATM functions to enable use of the S/UNI-JET as a DS3, E3, or J2 framer.

- Provides for diagnostic loopbacks, line loopbacks, and payload loopbacks.

ISSUE 2

SATURN USER NETWORK INTERFACE FOR J2, E3, T3

### 1 APPLICATIONS

- ATM or SMDS Switches, Multiplexers, and Routers

- SONET/SDH Mux E3/DS3 Tributary Interfaces

- PDH Mux J2/E3/DS3 Line Interfaces

- DS3/E3/J2 Digital Cross Connect Interfaces

- DS3/E3/J2 PPP Internet Access Interfaces

- DS3/E3/J2 Frame Relay Interfaces

SATURN USER NETWORK INTERFACE FOR J2, E3, T3

# 2 **REFERENCES**

- 1. ANSI T1.627 1993, "Broadband ISDN ATM Layer Functionality and Specification".

- 2. ANSI T1.107a 1990, "Digital Hierarchy Supplement to Formats Specifications (DS3 Format Applications)".

- 3. ANSI T1.107 1995, "Digital Hierarchy Formats Specifications".

- 4. ANSI T1.646 1995, "Broadband ISDN Physical Layer Specification for User-Network Interfaces Including DS1/ATM".

- 5. ATM Forum ATM User-Network Interface Specification, V3.1, October, 1995.

- 6. ATM Forum "UTOPIA, An ATM PHY Interface Specification, Level 2, Version 1", June, 1995.

- 7. ATM Forum, af-phy-0034.000, "E3 (34,368 kbps) Physical Layer Interface", August, 1995.

- 8. ATM Forum, af-phy-0054.000, "DS3 Physical Layer Interface Specification", January, 1996.

- 9. ATM Forum, af-phy-0029.000, "6,312 Kbps UNI Specification, Version 1.0", June 1995.

- Bell Communications Research, TA-TSY-000773 "Local Access System Generic Requirements, Objectives, and Interface in Support of Switched Multi-megabit Data Service" Issue 2, March 1990 and Supplement 1, December 1990.

- 11. ETS 300 269 Draft Standard T/NA(91)17 "Metropolitan Area Network Physical Layer Convergence Procedure for 2.048 Mbit/s", April 1994.

- 12. ETS 300 270 Draft Standard T/NA(91)18 "Metropolitan Area Network Physical Layer Convergence Procedure for 34.368 Mbit/s", April 1994.

- 13. ITU-T Recommendation O.151 "Error Performance Measuring Equipment Operating at the Primary Rate and Above", October, 1992.

- 14. ITU-T Recommendation I.432 "B-ISDN User-Network Interface Physical Layer Specification", 1993

- 15. ITU-T Recommendation G.703 "Physical/Electrical Characteristics of Hierarchical Digital Interfaces", 1991.

- ITU-T Recommendation G.704 "General Aspects of Digital Transmission Systems; Terminal Equipments - Synchronous Frame Structures Used At 1544, 6312, 2048, 8488 and 44 736 kbit/s Hierarchical Levels", July, 1995.

- 17. ITU-T Recommendation G.751 CCITT Blue Book Fasc. III.4, "Digital Multiplex Equipments Operating at the Third Order Bit Rate of 34,368 kbit/s and the Fourth Order Bit Rate of 139,264 kbit/s and Using Positive Justification", 1988.

| PMC     | PMC-Sierra, Inc. |

|---------|------------------|

| ISSUE 2 | SATURN U         |

- 18. ITU-T Draft Recommendation G.775 "Loss of Signal (LOS) and Alarm Indication Signal (AIS) Defect Detection and Clearance Criteria", October 1993.

- 19. ITU-T Recommendation G.804 "ATM Cell Mapping into Plesiochronous Digital Hierarchy (PDH)", 1993.

- 20. ITU-T Recommendation G.832 "Transport of SDH Elements on PDH Networks: Frame and Multiplexing Structures", 1993.

- ITU-T Recommendation Q.921 "ISDN User-Network Interface Data Link Layer Specification", March, 1993.

- 22. NTT Technical Reference, "NTT Technical Reference for High-Speed Digital Leased Circuit Services", 1991.

DATA SHEET PMC-1990267

SATURN USER NETWORK INTERFACE FOR J2, E3, T3

# 3 DATASHEET OVERVIEW

The PM7347 S/UNI-JET is functionally equivalent to a single channel PM7346 S/UNI-QJET. The devices are software compatible and pin compatible. This datasheet provides a complete pin-out description for the S/UNI-JET, as well as any differences between these devices (including boundary scan register, test mode 0 register, 006H register and the Device Identification register). For a complete functional and register description, please refer to the PMC-96-0835 S/UNI-QJET datasheet.

ISSUE 2

PMC-Sierra, Inc.

SATURN USER NETWORK INTERFACE FOR J2, E3, T3

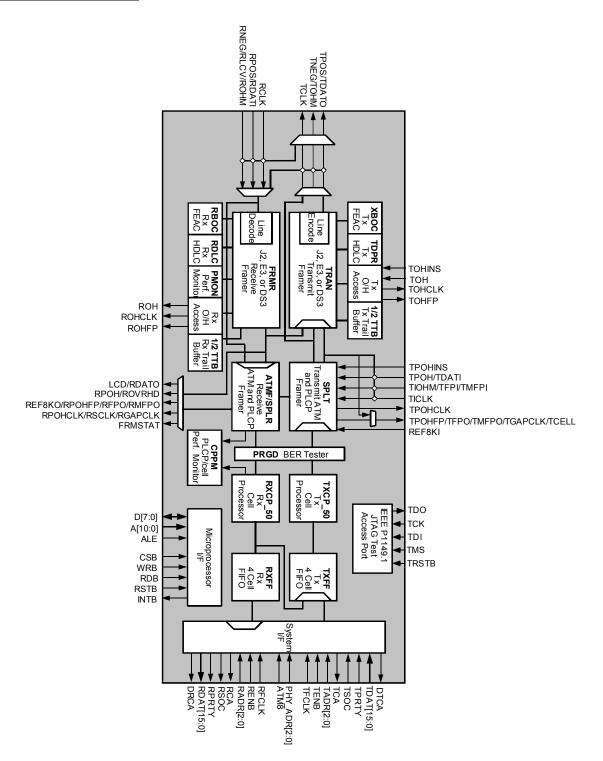

#### 4 BLOCK DIAGRAM

DATA SHEET PMC-1990267

ISSUE 2

SATURN USER NETWORK INTERFACE FOR J2, E3, T3

## 5 PIN DIAGRAM

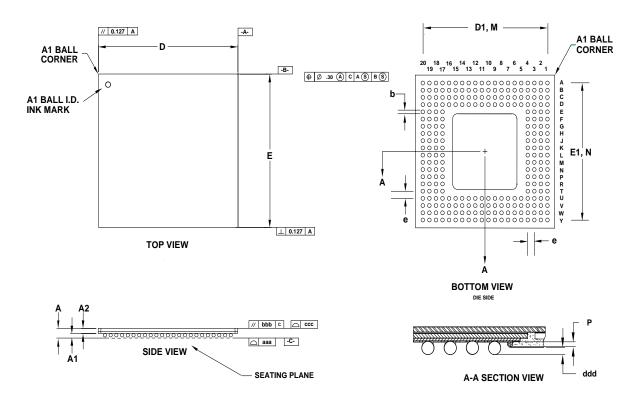

The S/UNI-JET is packaged in a 256-pin SBGA package having a body size of 27mm by 27mm and a pin pitch of 1.27 mm.

|   | 20         | 19         | 18         | 17       | 16       | 15       | 14      | 13      | 12     | 11   | 10      | 9     | 8      | 7     | 6     | 5     | 4      | 3      | 2      | 1       |  |     |    |    |     |

|---|------------|------------|------------|----------|----------|----------|---------|---------|--------|------|---------|-------|--------|-------|-------|-------|--------|--------|--------|---------|--|-----|----|----|-----|

| А | VSS        | VSS        | VSS        | TDAT[10] | TDAT[14] | D[1]     | D[5]    | VSS     | A[3]   | A[7] | VSS     | VSS   | ALE    | INTB  | TRSTB | TNEG  | RCLK   | VSS    | VSS    | VSS     |  |     |    |    |     |

| в | VSS        | VDD        | VDD        | TDAT[9]  | TDAT[13] | D[0]     | D[4]    | A[0]    | A[2]   | A[6] | A[9]    | A[10] | WRB    | TDO   | тск   | TCLK  | NC     | VDD    | VDD    | VSS     |  |     |    |    |     |

| с | VSS        | VDD        | VDD        | TDAT[7]  | TDAT[11] | TDAT[15] | D[2]    | D[6]    | A[1]   | A[5] | A[8]    | CSB   | RSTB   | TMS   | TPOS  | RNEG  | NC     | VDD    | VDD    | VSS     |  |     |    |    |     |

| D | TDAT[3]    | TDAT[4]    | TDAT[6]    | NC       | TDAT[8]  | TDAT[12] | VDD     | D[3]    | D[7]   | A[4] | VDD     | RDB   | TDI    | VDD   | RPOS  | NC    | BIAS   | NC     | NC     | VSS     |  |     |    |    |     |

| E | TFCLK      | TDAT[0]    | TDAT[2]    | TDAT[5]  |          |          |         |         |        |      |         |       |        |       |       |       | NC     | VSS    | VSS    | VSS     |  |     |    |    |     |

| F | TADR[0]    | TADR[1]    | TADR[2]    | TDAT[1]  |          |          |         |         |        |      |         |       |        |       |       |       | VSS    | VSS    | NC     | NC      |  |     |    |    |     |

| G | TSOC       | TPRTY      | VDD        | VDD      |          |          |         |         |        |      |         |       |        |       |       |       | VDD    | NC     | VSS    | VSS     |  |     |    |    |     |

| н | BIAS       | TCA        | TENB       | VDD      |          |          |         |         |        |      |         |       |        |       |       |       | VSS    | тон    | TOHCLK | VSS     |  |     |    |    |     |

| J | VSS        | NC         | NC         | DTCA     |          |          |         |         |        |      |         |       | TOHINS | TOHFP | ROH   | ROHFP |        |        |        |         |  |     |    |    |     |

| к | VSS        | NC         | PHY_ADR[2] | VDD      |          |          |         |         |        | во   | TTOM VI | EW    |        |       |       |       | ROHCLK | VSS    | VSS    | NC      |  |     |    |    |     |

| L | PHY_ADR[1] | PHY_ADR[0] | ATM8       | DRCA     |          |          |         |         |        |      |         |       |        |       |       |       | VDD    | NC     | NC     | VSS     |  |     |    |    |     |

| м | NC         | NC         | NC         | RSOC     |          |          |         |         |        |      |         |       |        |       |       |       |        |        |        |         |  | VSS | NC | NC | VSS |

| N | VSS        | RCA        | RENB       | RADR[1]  |          |          |         |         |        |      |         |       |        |       |       |       | NC     | NC     | NC     | VSS     |  |     |    |    |     |

| Ρ | RFCLK      | RADR[2]    | RADR[0]    | VDD      |          |          |         |         |        |      |         |       |        |       |       |       | VDD    | VSS    | NC     | NC      |  |     |    |    |     |

| R | VDD        | VDD        | RPRTY      | RDAT[13] |          |          |         |         |        |      |         |       |        |       |       |       | NC     | NC     | NC     | VSS     |  |     |    |    |     |

| т | RDAT[15]   | RDAT[14]   | RDAT[12]   | RDAT[9]  |          |          |         |         |        |      |         |       |        |       |       |       | NC     | REF8KI | NC     | NC      |  |     |    |    |     |

| U | RDAT[11]   | RDAT[10]   | RDAT[8]    | BIAS     | RDAT[6]  | RDAT[2]  | VDD     | TPOHCLK | REF8KO | VDD  | NC      | VSS   | NC     | VDD   | NC    | NC    | BIAS   | NC     | NC     | FRMSTAT |  |     |    |    |     |

| v | VSS        | VDD        | VDD        | RDAT[7]  | RDAT[3]  | TICLK    | TPOHINS | RPOH    | VSS    | NC   | NC      | VSS   | NC     | NC    | VSS   | NC    | NC     | VDD    | VDD    | VSS     |  |     |    |    |     |

| w | VSS        | VDD        | VDD        | RDAT[5]  | RDAT[1]  | TIOHM    | TPOHEP  | RPOHCLK | VSS    | VSS  | NC      | VSS   | VSS    | NC    | VSS   | VSS   | NC     | VDD    | VDD    | VSS     |  |     |    |    |     |

| Y | VSS        | VSS        | VSS        | RDAT[4]  | RDAT[0]  | TPOH     | LCD     | VSS     | VSS    | VSS  | NC      | NC    | VSS    | NC    | NC    | VSS   | NC     | VSS    | VSS    | VSS     |  |     |    |    |     |

|   | 20         | 19         | 18         | 17       | 16       | 15       | 14      | 13      | 12     | 11   | 10      | 9     | 8      | 7     | 6     | 5     | 4      | 3      | 2      | 1       |  |     |    |    |     |

DATA SHEET PMC-1990267

ISSUE 2

SATURN USER NETWORK INTERFACE FOR J2, E3, T3

# 6 PIN DESCRIPTION

| Pin Name | Туре   | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPOS     | Output | C6      | Transmit Digital Positive Pulse (TPOS). TPOS<br>contains the positive pulses transmitted on the<br>B3ZS-encoded DS3, HDB3-encoded E3, or B8ZS-<br>encoded J2 transmission system when the dual-rail<br>output format is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TDATO    |        |         | Transmit Data (TDATO). TDATO contains the transmit data stream when the single-rail (unipolar) output format is enabled or when a non-DS3/E3/J2 based transmission system is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |        |         | The TPOS/TDATO pin function selection is<br>controlled by the TFRM[1:0] and the TUNI bits in<br>the S/UNI-JET Transmit Configuration Register.<br>Output signal polarity control is provided by the<br>TPOSINV bit in the S/UNI-JET Transmit<br>Configuration Register. Both TPOS and TDATO<br>are updated on the falling edge of TCLK by default,<br>and may be configured to be updated on the rising<br>edge of TCLK through the TCLKINV bit in the<br>S/UNI-JET Transmit Configuration Register.<br>Finally, both TPOS and TDATO can be updated on<br>the rising edge of TICLK, enabled by the TICLK bit<br>in the S/UNI-JET Transmit Configuration Register. |

| TNEG     | Output | A5      | Transmit Digital Negative Pulse (TNEG). TNEG<br>contains the negative pulses transmitted on the<br>B3ZS-encoded DS3, HDB3-encoded E3, or B8ZS-<br>encoded J2 transmission system when the dual-rail<br>NRZ output format is selected.                                                                                                                                                                                                                                                                                                                                                                                                                             |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре   | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТОНМ     | Output | A5      | Transmit Overhead Mask (TOHM). TOHM<br>indicates the position of overhead bits (non-payload<br>bits) in the transmission system stream aligned with<br>TDATO. TOHM indicates the location of the M-<br>frame boundary for DS3, the position of the frame<br>boundary for E3, and the position of the multi-frame<br>boundary for J2 when the single-rail (unipolar) NRZ<br>input format is enabled.                                                                                                                                                                                                                                                                                    |

|          |        |         | When a PLCP formatted signal is transmitted,<br>TOHM is set to logic 1 once per transmission<br>frame, and indicates the DS1 or E1 frame<br>alignment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |        |         | When a non-PLCP, non-DS3, non-E3, non-J2<br>based signal is transmitted, TOHM is a delayed<br>version of the TIOHM input, and indicates the<br>position of each overhead bit in the transmission<br>frame. TOHM is updated on the falling edge of<br>TCLK.                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |        |         | The TNEG/TOHM pin function selection is<br>controlled by the TFRM[1:0] and the TUNI bits in<br>the S/UNI-JET Transmit Configuration Register.<br>Output signal polarity control is provided by the<br>TNEGINV bit in the S/UNI-JET Transmit<br>Configuration Register. Both TNEG and TOHM are<br>updated on the falling edge of TCLK by default, and<br>may be enabled to be updated on the rising edge of<br>TCLK. This sampling is controlled by the TCLKINV<br>bit in the S/UNI-JET Transmit Configuration<br>Register. Finally, both TNEG and TOHM can be<br>updated on the rising edge of TICLK, enabled by<br>the TICLK bit in the S/UNI-JET Transmit<br>Configuration Register. |

| TCLK     | Output | B5      | Transmit Output Clock (TCLK). TCLK provides the transmit direction timing. TCLK is a buffered version of TICLK and can be enabled to update the TPOS/TDATO and TNEG/TOHM outputs on its rising or falling edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RPOS     | Input  | D6      | Receive Digital Positive Pulse (RPOS). RPOS<br>contains the positive pulses received on the B3ZS-<br>encoded DS3, the HDB3-encoded E3, or the B8ZS-<br>encoded J2 transmission system when the dual-rail<br>NRZ input format is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре  | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDATI    |       |         | Receive Data (RDATI). RDATI contains the data<br>stream when the single-rail (unipolar) NRZ input<br>format is enabled or when a non-DS3/E3/J2 based<br>transmission system is being processed (for<br>example RDATI may contain a DS1 or E1 stream).                                                                                                                                                                                                                                                                                                                                                 |

|          |       |         | The RPOS/RDATI pin function selection is<br>controlled by the RFRM[1:0] bits in the S/UNI-JET<br>Configuration Register and by the UNI bits in the<br>DS3 FRMR, the E3 FRMR, or the J2 FRMR<br>Configuration Register. Both RPOS and RDATI are<br>sampled on the rising edge of RCLK by default, and<br>may be enabled to be sampled on the falling edge<br>of RCLK. This sampling is controlled by the<br>RCLKINV bit in the S/UNI-JET Receive<br>Configuration Register. In addition, signal polarity<br>control is provided by the RPOSINV bit in the<br>S/UNI-JET Receive Configuration Register. |

| RNEG     | Input | C5      | Receive Digital Negative Pulse (RNEG). RNEG<br>contains the negative pulses received on the B3ZS<br>encoded DS3, the HDB3-encoded E3, or the B8ZS-<br>encoded J2 transmission system when the dual-rail<br>NRZ input format is selected.                                                                                                                                                                                                                                                                                                                                                              |

| RLCV     |       |         | Receive Line Code Violation (RLCV). RLCV<br>contains line code violation indications when the<br>single-rail (unipolar) NRZ input format is enabled for<br>DS3, E3, or J2 applications. Each line code<br>violation is represented by an RCLK period-wide<br>pulse.                                                                                                                                                                                                                                                                                                                                   |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре  | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROHM     | Input | C5      | Receive Overhead Mask (ROHM). When a DS1<br>or E1 PLCP or ATM direct-mapped signal is<br>received, ROHM is pulsed once per transmission<br>frame, and indicates the DS1 or E1 frame<br>alignment relative to the RDATI data stream. When<br>an alternate frame-based signal is received, ROHM<br>indicates the position of each overhead bit in the<br>transmission frame.                                                                                                                                                                                                                                                                                              |

|          |       |         | The RNEG/RLCV/ROHM pin function selection is<br>controlled by the RFRM[1:0] bits in the S/UNI-JET<br>Receive Configuration Register, the UNI bits in the<br>DS3 FRMR, E3 FRMR, or J2 FRMR Configuration<br>Register, and the PLCPEN and EXT bits in the<br>SPLR Configuration register. RNEG, RLCV, and<br>ROHM are sampled on the rising edge of RCLK by<br>default, and may be enabled to be sampled on the<br>falling edge of RCLK. This sampling is controlled<br>by the RCLKINV bit in the S/UNI-JET Receive<br>Configuration Register. In addition, signal polarity<br>control is provided by the RNEGINV bit in the<br>S/UNI-JET Receive Configuration Register. |

| RCLK     | Input | A4      | Receive Clock (RCLK). RCLK provides the receive<br>direction timing. RCLK is the externally recovered<br>transmission system baud rate clock that samples<br>the RPOS/RDATI and RNEG/RLCV/ROHM inputs<br>on its rising or falling edge.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TOHINS   | Input | J4      | Transmit DS3/E3/J2 Overhead Insertion (TOHINS).<br>TOHINS controls the insertion of the DS3, E3, or J2<br>overhead bits from the TOH input. When TOHINS<br>is high, the associated overhead bit in the TOH<br>stream is inserted in the transmitted DS3, E3, or J2<br>frame. When TOHINS is low, the DS3, E3, or J2<br>overhead bit is generated and inserted internally.<br>TOHINS is sampled on the rising edge of TOHCLK.<br>If TOHINS is a logic 1, the TOH input has<br>precedence over the internal datalink transmitter, or<br>any internal register bit setting.                                                                                                |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре   | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТОН      | Input  | НЗ      | Transmit DS3/E3/J2 Overhead Data (TOH). When configured for DS3 operation, TOH contains the overhead bits (C, F, X, P, and M) that may be inserted in the transmit DS3 stream.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |        |         | When configured for G.832 E3 operation, TOH contains the overhead bytes (FA1, FA2, EM mask, TR, MA, NR, and GC) that may be inserted in the transmit G.832 E3 stream.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |        |         | When configured for G.751 E3 operation, TOH contains the overhead bits (RAI, National Use, Stuff Indication, and Stuff Opportunity) that may be inserted in the transmit G.751 E3 stream.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |        |         | When configured for J2 operation, TOH contains the overhead bits (TS97, TS98, Framing, $X_{1-3}$ , A, M, $E_{1-5}$ ) that may be inserted in the transmit J2 stream.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |        |         | If TOHINS is a logic 1, the TOH input has<br>precedence over the internal datalink transmitter, or<br>any other internal register bit setting. TOH is<br>sampled on the rising edge of TOHCLK.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TOHFP    | Output | J3      | Transmit DS3/E3/J2 Overhead Frame Position<br>(TOHFP). TOHFP is used to align the individual<br>overhead bits in the transmit overhead data stream,<br>TOH, to the DS3 M-frame or the E3 frame. For<br>DS3, TOHFP is high during the X1 overhead bit<br>position in the TOH stream. For G.832 E3, TOHFP<br>is high during the first bit of the FA1 byte. For<br>G.751 E3, TOHFP is high during the RAI overhead<br>bit position in the TOH stream. For J2, TOHFP is<br>high during the first bit of timeslot 97 in the first<br>frame of a 4-frame multiframe). TOHFP is updated<br>on the falling edge of TOHCLK. |

| TOHCLK   | Output | H2      | Transmit DS3/E3/J2 Overhead Clock (TOHCLK).<br>TOHCLK is active when a DS3, E3, or J2 stream is<br>being processed. TOHCLK is nominally a 526 kHz<br>clock for DS3, a 1.072 MHz clock for G.832 E3, a<br>1.074 MHz clock for G.751 E3, and a gapped 6.312<br>MHz clock with an average frequency of 168 kHz<br>for J2. TOHFP is updated on the falling edge of<br>TOHCLK. TOH, and TOHINS are sampled on the<br>rising edge of TOHCLK.                                                                                                                                                                             |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре  | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REF8KI   | Input | Т3      | Reference 8 kHz Input (REF8KI). The PLCP frame<br>rate is locked to an external 8 kHz reference<br>applied on this input . An internal phase-frequency<br>detector compares the transmit PLCP frame rate<br>with the externally applied 8 kHz reference and<br>adjusts the PLCP frame rate.                                                                                                                                                                   |

|          |       |         | The REF8KI input must transition high once every 125 µs for correct operation. The REF8KI input is treated as an asynchronous signal and must be "glitch-free". If the LOOPT register bit is logic 1, the PLCP frame rate is locked to the RPOHFP signal instead of the REF8KI input.                                                                                                                                                                         |

| TPOHINS  | Input | V14     | Transmit Path Overhead Insertion (TPOHINS).<br>TPOHINS controls the insertion of PLCP overhead<br>octets on the TPOH input. When TPOHINS is logic<br>1, the associated overhead bit in the TPOH stream<br>is inserted in the transmit PLCP frame. When<br>TPOHINS is logic 0, the PLCP path overhead bit is<br>generated and inserted internally. TPOHINS is<br>sampled on the rising edge of TPOHCLK.                                                        |

|          |       |         | Note, when operating in G.751 E3 PLCP mode, bits 8, 7 and 6 of the C1 octet should not be manipulated.                                                                                                                                                                                                                                                                                                                                                        |

| ТРОН     | Input | Y15     | Transmit PLCP Overhead Data (TPOH). TPOH is valid when the FRMRONLY bit in the S/UNI-JET Configuration 1 register is logic 0. TPOH contains the PLCP path overhead octets (Zn, F1, B1, G1, M1, M2, and C1) which may be inserted in the transmit PLCP frame. The octet data on TPOH is shifted in order from the most significant bit (bit 1) to the least significant bit (bit 8). TPOH is sampled on the rising edge of TPOHCLK.                            |

| TDATI    |       |         | Framer Transmit Data (TDATI). TDATI contains the serial data to be transmitted when the S/UNI-JET is configured as a DS3, E3, or J2 framer device for non-ATM applications by setting the FRMRONLY bit in the S/UNI-JET Configuration 1 Register. TDATI is sampled on the rising edge of TICLK if the TXGAPEN register bit in the S/UNI-JET Configuration 2 register is logic 0. If TXGAPEN is logic 1, then TDATI is sampled on the falling edge of TGAPCLK. |

DATA SHEET PMC-1990267

ISSUE 2

| <b>D</b> : 11 |        | <b>D:</b> N |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name      | Туре   | Pin No.     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TPOHFP        | Output | W14         | Transmit Path Overhead Frame Position<br>(TPOHFP). TPOHFP is valid when the<br>FRMRONLY bit in the S/UNI-JET Configuration 1<br>Register is logic 0. The TPOHFP output locates the<br>individual PLCP path overhead bits in the transmit<br>overhead data stream, TPOH. TPOHFP is logic 1<br>while bit 1 (the most significant bit) of the path user<br>channel octet (F1) is present in the TPOH stream.<br>TPOHFP is updated on the falling edge of<br>TPOHCLK.                                                                                                                          |

| TFPO          | Output | W14         | Framer Transmit Frame Pulse/Multi-frame Pulse<br>Reference (TFPO/TMFPO). TFPO/TMFPO is valid<br>when the S/UNI-JET is configured as a DS3, E3, or<br>J2 framer for non-ATM applications by setting the<br>FRMRONLY bit in the S/UNI-JET Configuration 1<br>Register to logic 1 and the TXGAPEN bit in the<br>S/UNI-JET Configuration Register to logic 0.                                                                                                                                                                                                                                  |

|               |        |             | TFPO pulses high for 1 out of every 85 clock cycles<br>when configured for DS3, giving a free-running<br>mark for all overhead bits in the frame. TFPO<br>pulses high for 1 out of every 1536 clock cycles<br>when configured for G.751 E3, giving a free-running<br>reference G.751 indication. TFPO pulses high for 1<br>out of every 4296 clock cycles when configured for<br>G.832 E3, giving a free-running reference G.832<br>frame indication. TFPO pulses high for 1 out of<br>every 789 clock cycles when configured for J2,<br>giving a free-running reference frame indication. |

| TMFPO         |        |             | TMFPO pulses high for 1 out of every 4760 clock<br>cycles when configured for DS3, giving a free-<br>running reference M-frame indication. TMFPO<br>pulses high for 1 out of every 3156 clock cycles<br>when configured for J2, giving a free-running<br>reference multi-frame indication. TMFPO behaves<br>the same as TFPO for E3 applications.                                                                                                                                                                                                                                          |

|               |        |             | TFPO/TMFPO is updated on the rising edge of TICLK or RCLK if loop-timed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре   | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TGAPCLK  | Output | W14     | Framer Gapped Transmit Clock (TGAPCLK).<br>TGAPCLK is valid when the S/UNI-JET is<br>configured as a DS3, E3, or J2 framer for non-ATM<br>applications by setting the FRMRONLY bit in the<br>S/UNI-JET Configuration 1 Register and the<br>TXGAPEN bit in the S/UNI-JET Configuration 2<br>Register.                                                                                                                                   |

|          |        |         | TGAPCLK is derived from the transmit reference<br>clock TICLK or from the receive clock if loop-timed.<br>The overhead bit (gapped) positions are generated<br>internal to the device. TGAPCLK is held high<br>during the overhead bit positions. This clock is<br>useful for interfacing to devices which source<br>payload data only. TGAPCLK is used to sample<br>TDATI.                                                            |

| TCELL    |        |         | Transmit Cell Indication (TCELL). TCELL is valid<br>when the TCELL bit in the S/UNI-JET Misc. register<br>is set. TCELL pulses once for every cell (idle or<br>assigned) transmitted. TCELL is updated using<br>timing derived from the transmit input clock<br>(TICLK), and is active for a minimum of 8 TICLK<br>periods (or 8 RCLK periods if loop-timed).                                                                          |

| TPOHCLK  | Output | U13     | Transmit PLCP Overhead Clock (TPOHCLK).<br>TPOHCLK is active when PLCP processing is<br>enabled. TPOHCLK is nominally a 26.7 kHz clock<br>for a DS1 PLCP frame, a 768 kHz clock for a DS3<br>PLCP frame, a 33.7 kHz clock for an E1 based<br>PLCP frame, and a 576 kHz clock for an G.751 E3<br>based PLCP frame. TPOHFP is updated on the<br>falling edge of TPOHCLK. TPOH, and TPOHINS<br>are sampled on the rising edge of TPOHCLK. |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре  | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТІОНМ    | Input | W15     | Transmit Input Overhead Mask (TIOHM). TIOHM<br>is valid only if the FRMRONLY bit in the S/UNI-JET<br>Configuration 1 register is logic 0. TIOHM indicates<br>the position of overhead bits when not configured<br>for DS1, DS3, E1, E3, or J2 transmission system<br>streams. TIOHM is delayed internally to produce<br>the TOHM output. When configured for operation<br>over a DS1, a DS3, an E1, an E3, or a J2<br>transmission system sublayer, TIOHM is not<br>required, and should be set to logic 0. When<br>configured for other transmission systems, TIOHM<br>is set to logic 1 for each overhead bit position.<br>TIOHM is set to logic 0 if the transmission system<br>contains no overhead bits. TIOHM is sampled on<br>the rising edge of TICLK. |

| TFPI     | Input | W15     | Framer Transmit Frame Pulse/Multiframe Pulse<br>(TFPI/TMFPI). TFPI/TMFPI is valid when the<br>S/UNI-JET is configured as a DS3, E3, or J2 framer<br>for non-ATM applications by setting the<br>FRMRONLY bit in the S/UNI-JET Configuration 1<br>Register to logic 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |       |         | TFPI indicates the position of all overhead bits in<br>each DS3 M-subframe, the first bit in each G.751<br>E3 or G.832 E3 frame, or the first framing bit in<br>each J2 frame. TFPI is not required to pulse at<br>every frame boundary in E3 or J2 modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TMFPI    |       |         | TMFPI indicates the position of the first bit in each DS3 M-frame, the first bit in each E3 frame, or the first framing bit in each J2 multiframe. TMFPI is not required to pulse at every multiframe boundary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |       |         | TFPI/TMFPI is sampled on the rising edge of TICLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TICLK    | Input | V15     | Transmit Input Clock (TICLK). TICLK provides the transmit direction timing. TICLK is the externally generated transmission system baud rate clock. It is internally buffered to produce the transmit clock output, TCLK, and can be enabled to update the TPOS/TDATO and TNEG/TOHM outputs on the TICLK rising edge. The TICLK maximum frequency is 52 MHz.                                                                                                                                                                                                                                                                                                                                                                                                    |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре   | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROHFP    | Output | J1      | Receive DS3/E3/J2 Overhead Frame Position<br>(ROHFP). ROHFP locates the individual overhead<br>bits in the received overhead data stream, ROH.<br>ROHFP is high during the X1 overhead bit position<br>in the ROH stream when processing a DS3 stream.<br>ROHFP is high during the first bit of the FA1 byte<br>when processing a G.832 E3 stream. ROHFP is<br>high during the RAI overhead bit position when<br>processing a G.751 E3 stream. ROHFP is high<br>during the first bit in Timeslot 97 in the first frame of<br>the 4-frame multiframe when processing a J2<br>stream. ROHFP is updated on the falling edge of<br>ROHCLK. |

| ROH      | Output | J2      | Receive DS3/E3/J2 Overhead Data (ROH). ROH<br>contains the overhead bits (C, F, X, P, and M)<br>extracted from the received DS3 stream; ROH<br>contains the overhead bytes (FA1, FA2, EM, TR,<br>MA, NR, and GC) extracted from the received<br>G.832 E3 stream; ROH contains the overhead bits<br>(RAI, National Use, Stuff Indication, and Stuff<br>Opportunity) extracted from the received G.751 E3<br>stream; ROH contains the overhead bits (Framing,<br>X <sub>1-3</sub> , A, M, E <sub>1-5</sub> ) extracted from the received J2<br>stream. ROH is updated on the falling edge of<br>ROHCLK.                                  |

| ROHCLK   | Output | К4      | Receive DS3/E3/J2 Overhead Clock (ROHCLK).<br>ROHCLK is active when a DS3, E3, or J2 stream is<br>being processed. ROHCLK is nominally a 526 kHz<br>clock when processing DS3, a 1.072 MHz clock<br>when processing G.832 E3, a 1.074 MHz clock<br>when processing G.751 E3, and a gapped 6.312<br>MHz clock with an average frequency of 168 kHz<br>for J2. ROH, and ROHFP are updated on the<br>falling edge of ROHCLK.                                                                                                                                                                                                              |

| REF8KO   | Output | U12     | Reference 8kHz Output (REF8KO). REF8KO is an<br>8kHz reference derived from the receive clock<br>(RCLK). A free-running divide-down counter is<br>used to generate REF8KO so it will not glitch on<br>reframe actions. REF8KO will pulse high for<br>approximately 1 RCLK cycle every 125 µs.<br>REF8KO should be treated as a glitch-free<br>asynchronous signal.                                                                                                                                                                                                                                                                     |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре   | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPOHFP   |        |         | Receive PLCP Overhead Frame Position<br>(RPOHFP). RPOHFP locates the individual PLCP<br>path overhead bits in the receive overhead data<br>stream, RPOH. RPOHFP is logic 1 while bit 1 (the<br>most significant bit) of the path user channel octet<br>(F1) is present in the RPOH stream. RPOHFP is<br>updated on the falling edge of RPOHCLK.<br>RPOHFP is available when the PLCPEN register bit<br>is logic 1 in the SPLR Configuration Register.                      |

| RFPO     | Output | U12     | Framer Receive Frame Pulse/Multi-frame Pulse<br>(RFPO/RMFPO). RFPO/RMFPO is valid when the<br>S/UNI-JET is configured to be in framer only mode.<br>The 8KREFO bit must be set to logic 0 in the<br>S/UNI-JET Configuration Register.                                                                                                                                                                                                                                      |

|          |        |         | RFPO is aligned to RDATO and indicates the position of the first bit in each DS3 M-subframe, the first bit in each G.751 E3 or G.832 E3 frame, or the first framing bit in each J2 frame                                                                                                                                                                                                                                                                                   |

| RMFPO    |        |         | RMFPO is aligned to RDATO and indicates the position of the first bit in each DS3 M-frame, the first bit in each G.751 or G.832 E3 multiframe, or the first framing bit in each J2 multiframe.                                                                                                                                                                                                                                                                             |

|          |        |         | RFPO/RMFPO is updated on either the falling or rising edge of RSCLK depending on the setting of the RSCLKR bit in the S/UNI-JET Receive Configuration register.                                                                                                                                                                                                                                                                                                            |

| RPOH     | Output | V13     | Receive PLCP Overhead Data (RPOH). RPOH<br>contains the PLCP path overhead octets (Zn, F1,<br>B1, G1, M1, M2, and C1) extracted from the<br>received PLCP frame when the PLCP layer is in-<br>frame. When the PLCP layer is in the loss of frame<br>state, RPOH is forced to all ones. The octet data<br>on RPOH is shifted out in order from the most<br>significant bit (bit 1) to the least significant bit (bit 8).<br>RPOH is updated on the falling edge of RPOHCLK. |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Turce  | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Туре   |         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ROVRHD   | Output | V13     | Framer Receive Overhead Indication (ROVRHD).<br>ROVRHD is valid when the S/UNI-JET is<br>configured as a DS3, E3, or J2 framer for non-ATM<br>applications by setting the FRMRONLY bit in the<br>S/UNI-JET Configuration 1 Register. ROVRHD will<br>be high whenever the data on RDATO corresponds<br>to an overhead bit position. ROVRHD is updated<br>on the either the falling or rising edge of RSCLK<br>depending on the setting of the RSCLKR bit in the<br>S/UNI-JET Receive Configuration register. |

| RPOHCLK  | Output | W13     | Receive PLCP Overhead Clock (RPOHCLK).<br>RPOHCLK is active when PLCP processing is<br>enabled. The frequency of this signal depends on<br>the selected PLCP format. RPOHCLK is nominally<br>a 26.7 kHz clock for a DS1 PLCP frame, a 768 kHz<br>clock for a DS3 PLCP frame, a 33.7 kHz clock for<br>an E1 based PLCP frame, or a 576 kHz clock for a<br>G.751 E3 based PLCP frame. RPOHFP and RPOH<br>are updated on the falling edge of RPOHCLK.                                                          |

| RSCLK    |        |         | Framer Recovered Clock (RSCLK). RSCLK is valid<br>when the S/UNI-JET is configured as a DS3, E3, or<br>J2 framer for non-ATM applications by setting the<br>FRMRONLY bit in the S/UNI-JET Configuration<br>Register.                                                                                                                                                                                                                                                                                        |

|          |        |         | RSCLK is the recovered clock and timing reference for RDATO, RFPO/RMFPO, and ROVRHD.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RGAPCLK] | Output | W13     | Framer Recovered Gapped Clock (RGAPCLK).<br>RGAPCLK is valid when the S/UNI-JET is<br>configured as a DS3, E3, or J2 framer for non-ATM<br>applications by setting the FRMRONLY bit in the<br>S/UNI-JET Configuration 1 Register and the<br>RXGAPEN bit in the S/UNI-JET Configuration 2<br>Register.                                                                                                                                                                                                       |

|          |        |         | RGAPCLK is the recovered clock and timing reference for RDATO. RGAPCLK is held high for bit positions which correspond to overhead.                                                                                                                                                                                                                                                                                                                                                                         |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре   | Pin No.  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | туре   | FIII NO. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LCD      | Output | Y14      | Loss of Cell Delineation (LCD). LCD is an active<br>high signal which is asserted while the ATM cell<br>processor has detected a Loss of Cell Delineation<br>defect. The FRMRONLY bit in the S/UNI-JET<br>Configuration 1 Register must be set to logic 0 for<br>LCD to be valid.                                                                                                                                                                                                                                                                                  |

| RDATO    |        |          | Framer Receive Data (RDATO). RDATO is valid<br>when the S/UNI-JET is configured as a DS3, E3, or<br>J2 framer for non-ATM applications by setting the<br>FRMRONLY bit in the S/UNI-JET Configuration 1<br>Register.                                                                                                                                                                                                                                                                                                                                                |

|          |        |          | RDATO is the received data aligned to<br>RFPO/RMFPO and ROVRHD. RDATO is updated<br>on the active edge (as set by the RSCLKR register<br>bit) of RSCLK or RGAPCLK.                                                                                                                                                                                                                                                                                                                                                                                                 |

| FRMSTAT  | Output | U1       | Framer Status (FRMSTAT). FRMSTAT is an active<br>high signal which can be configured to show when<br>one of the J2, E3, DS3, or PLCP framers have<br>detected certain conditions. The FRMSTAT output<br>can be programmed via the STATSEL[2:0] bits in<br>the S/UNI-JET Configuration 2 Register to indicate:<br>E3/DS3 Loss of Frame or J2 extended Loss of<br>Frame, E3/DS3 Out of Frame or J2 Loss of Frame,<br>PLCP Loss of Frame, PLCP Out of Frame, AIS,<br>Loss of Signal, and DS3 Idle. FRMSTAT should be<br>treated as a glitch free asynchronous signal. |

| ATM8     | Input  | L18      | ATM Interface Bus Width Selection (ATM8). The ATM8 input pin determines whether the S/UNI-JET works with a 8-bit wide interface (RDAT[7:0] and TDAT[7:0]) or a 16-bit wide interface (RDAT[15:0] and TDAT[15:0]). If ATM8 is set to logic 1, then the 8-bit wide interface is chosen. If ATM8 is set to logic 0, then the 16-bit wide interface is chosen.                                                                                                                                                                                                         |

DATA SHEET PMC-1990267

ISSUE 2

| Pin Name | Туре  | Pin No.                                                                                                                                                               | Function                                                                                                                                                                                                                                                                                                  |