# Am2916A

Quad Three-State Bus Transceiver with Interface Logic

#### DISTINCTIVE CHARACTERISTICS

- Quad high-speed LSI bus-transceiver

- Two-port input to D-type register on driver

- Three-state bus driver output can sink 48mA at 0.5V max.

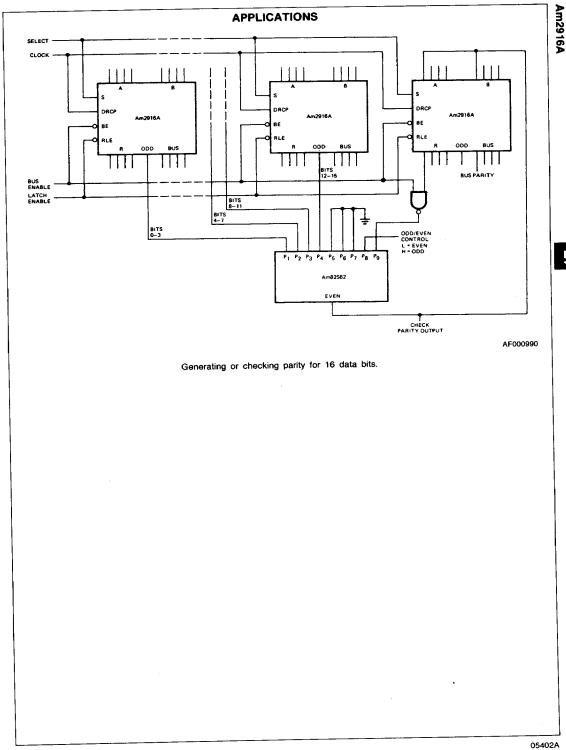

- Internal 4-bit odd parity checker/generator

- Receiver output latch can sink 12mA

- 3.5V minimum output high voltage for direct interface to MOS microprocessors

#### **GENERAL DESCRIPTION**

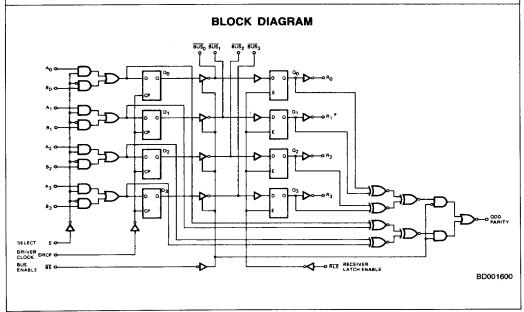

The Am2916A is a high-performance, low-power Schottky bus transceiver intended for bipolar or MOS microprocessor system applications. The device consists of four D-type edge-triggered flip-flops with a built-in two-input multiplexer on each. The flip-flop outputs are connected to four three-state bus drivers. Each bus driver is internally connected to the input of a receiver. The four receiver outputs drive four D-type latches. The device also contains a four-bit odd parity checker/generator.

The LSI bus transceiver is fabricated using advanced low-power Schottky processing. All inputs (except the BUS inputs) are one LS unit load. The three-state bus output can sink up to 48mA at 0.5V maximum. The bus enable input  $(\overline{\rm BE})$  is used to force the driver outputs to the high-impedance state. When  $\overline{\rm BE}$  is HIGH, the driver is disabled.

The input register consists of four D-type flip-flops with a buffered common clock and two-input multiplexer at the input of each flip-flop. A common select input (S) controls the four multiplexers. When S is LOW, the A<sub>i</sub> data is stored in the register and when S is HIGH, the B<sub>i</sub> data is stored.

The buffered common clock (DRCP) enters the data into this driver register on the LOW-to-HIGH transition.

Data from the A or B input is inverted at the BUS output. Likewise, data at the BUS input is inverted at the receiver output. Thus, data is non-inverted from driver input to receiver output. The four receivers each feature a built-in D-type latch that is controlled from the buffered receiver latch enable (RLE) input. When the RLE input is LOW, the latch is open and the receiver outputs will follow the bus inputs (BUS data inverted). When the RLE input is HIGH, the latch will close and retain the present data regardless of the bus input.

The Am2916A features a built-in four-bit odd parity checker/generator. The bus enable input (BE) controls whether the parity output is in the generate or check mode. When the bus enable is LOW (driver enabled), odd parity is generated based on the A or B field data input to the driver register. When BE is HIGH, the parity output is determined by the four latch outputs of the receiver. Thus, if the driver is enabled, parity is generated and if the driver is in the high-impedance state, the BUS parity is checked.

05402A

5-138

Refer to Page 13-1 for Essential Information on Military Devices

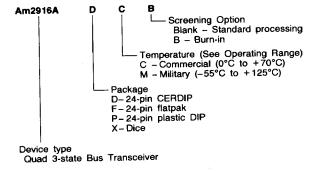

## **CONNECTION DIAGRAM Top View** D-24-1 24 VCC DRCP B<sub>3</sub> BUS<sub>3</sub> GND, [ Am2916A BUS, ODD CD003020 Note: Pin 1 is marked for orientation METALLIZATION AND PAD LAYOUT LOGIC SYMBOL 23 DRCP BO Rο 21 83 Βn 20 A<sub>3</sub> Αn 19 BUS<sub>3</sub> BUSo Am29164 GND<sub>1</sub> 18 GND<sub>2</sub> R<sub>2</sub> BUS<sub>1</sub> 16 A<sub>2</sub> A<sub>1</sub> RLE 81 15 Bo BUS<sub>2</sub> BUS<sub>3</sub> 13 S LS000790 DIE SIZE .074" x .130" ORDERING INFORMATION AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired). Valid Combinations

#### **Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

05402A

Refer to Page 13-1 for Essential Information on Military Devices

5-139

#### PIN DESCRIPTION

| Pin No.          | Name                                                                             | 1/0 | Description                                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 8, 16, 20     | A <sub>0</sub> , A <sub>1</sub> ,<br>A <sub>2</sub> , A <sub>3</sub>             | 1   | The "A" word data input into the two input multiplexer of the driver register.                                                                                                                                     |

| 3, 9, 15, 21     | B <sub>0</sub> , B <sub>1</sub> ,<br>B <sub>2</sub> , B <sub>3</sub>             | ı   | The "B" word data input into the two input multiplexers of the driver register.                                                                                                                                    |

| 13               | s                                                                                | '   | Select. When the select input is LOW, the A data word is applied to the driver register. When the select input is HIGH, the B word is applied to the driver register.                                              |

| 23               | DRCP                                                                             | ı   | Oriver Clock Pulse. Clock pulse for the driver register.                                                                                                                                                           |

| 11               | BE                                                                               | 1   | Bus Enable. When the Bus Enable is HIGH, the four drivers are in the high-impedance state.                                                                                                                         |

| 5, 7, 17, 19     | BUS <sub>0</sub> ,<br>BUS <sub>1</sub><br>BUS <sub>2</sub> ,<br>BUS <sub>3</sub> | 1/0 | The four driver outputs and receiver inputs (data is inverted).                                                                                                                                                    |

| 2, 10, 14,<br>22 | R <sub>0</sub> , R <sub>1</sub> ,<br>R <sub>2</sub> , R <sub>3</sub>             | 0   | The four receiver outputs. Data from the bus is inverted while data from the A or B inputs is non-inverted.                                                                                                        |

| 1                | RLE                                                                              | 0   | Receiver Latch Enable. When RLE is LOW, data on the BUs inputs is passed through the receiver latches. When RLE is HIGH, the receiver latches are closed and will retain the data independent of all other inputs. |

| 12               | ODD                                                                              | 0   | Odd parity output. Generates parity with the driver enabled, checks parity with the driver in the high-impedance state.                                                                                            |

## FUNCTION TABLE

| INPUTS      |                                 |             |             |             | INTERNAL<br>TO DEVICE |          | BUS         | OUTPUTS     |             |             |                                                                           |  |  |

|-------------|---------------------------------|-------------|-------------|-------------|-----------------------|----------|-------------|-------------|-------------|-------------|---------------------------------------------------------------------------|--|--|

| s           | S A <sub>i</sub> B <sub>i</sub> |             | DRCP        | BE          | RLE                   | Di       | Qi          | BUS         | Ri          | ODD         | FUNCTION                                                                  |  |  |

| Х           | х                               | х           | ×           | Н           | х                     | Х        | Х           | Z.          | ×           | PQ          | Driver output disable                                                     |  |  |

| х           | ×                               | х           | ×           |             | х                     | Х        | Х           | Х           | х           | PD          | Driver output enable Driver output disable and receive data via Bus input |  |  |

| X<br>X      | X                               | X           | ×           | Н           | L                     | X<br>X   | L<br>H      | L<br>H      | H<br>L      | H           |                                                                           |  |  |

| х           | х                               | x           | ×           | х           | Н                     | Х        | NC          | Х           | NC          | Х           | Latch received data                                                       |  |  |

| L<br>L<br>H | L<br>X<br>X                     | X<br>L<br>H | 1<br>1<br>1 | X<br>X<br>X | X<br>X<br>X           | LILI     | X<br>X<br>X | X<br>X<br>X | ×<br>×<br>× | X<br>X<br>X | Load driver register                                                      |  |  |

| X<br>X      | X                               | X           | L<br>H      | X           | X                     | NC<br>NC | X           | X<br>X      | X<br>X      | X           | No driver clock restrictions                                              |  |  |

| X<br>X      | X                               | X           | ×           | L<br>L      | X                     | L<br>H   | X<br>X      | H           | X<br>X      | Н           | Drive Bus                                                                 |  |  |

Z = HIGH impedance H = HIGH L = LOW NC = No change

X = Don't care t = LOW to HIGH transition i = 0, 1, 2, 3

PQ=Parity of Q latches

PD=Parity of D flip-flops

### PARITY OUTPUT FUNCTION TABLE

| BE | ODD PARITY OUTPUT                                                       |

|----|-------------------------------------------------------------------------|

| L  | ODD = 10 + 11 + 12 + 13                                                 |

| н  | ODD = Q <sub>0</sub> + Q <sub>1</sub> + Q <sub>2</sub> + Q <sub>3</sub> |

Ii = Selected input Ai or Bi

05402A

Refer to Page 13-1 for Essential Information on Military Devices

### **ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices                                                                         |

|------------------------------------------------------------------------------------------------|

| Temperature0°C to +70°C                                                                        |

| Supply Voltage+4.75V to +5.25V                                                                 |

| Military (M) Devices                                                                           |

| Temperature55°C to +125°C                                                                      |

| Supply Voltage +4.5V to +5.5V                                                                  |

| Operating ranges define those limits over which the functionality of the device is guaranteed. |

| •                                                                                              |

#### DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters      | Description                         | Test Conditions (Note 2)                                                                                                          |                               |                                 | Min | Typ<br>(Note 1) | Max   | Units  |  |

|-----------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------|-----|-----------------|-------|--------|--|

|                 |                                     | Vcc = MIN                                                                                                                         | MIL: I <sub>OH</sub> = -1.0mA |                                 | 2.4 | 3.4             |       | Volts  |  |

| V <sub>OH</sub> | Receiver                            | VIN = VIL or VIH                                                                                                                  | COM'                          | COM'L: I <sub>OH</sub> = -2.6mA |     | 3.4             |       |        |  |

|                 | Output HiGH Voltage                 | $V_{CC} = 5.0V$ , $I_{OH} = -100 \mu A$                                                                                           |                               |                                 | 3.5 |                 |       |        |  |

|                 | Parity                              | V <sub>CC</sub> = MIN, I <sub>OH</sub> = -660μA<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>                           |                               | MIL                             | 2.5 | 3.4             |       |        |  |

| Vон             | Output HIGH Voltage                 |                                                                                                                                   |                               | COM'L                           | 2.7 | 3.4             |       | Volts  |  |

|                 |                                     | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub>   I <sub>OL</sub> = 8.0mA<br>I <sub>OL</sub> = 12mA |                               | I <sub>OL</sub> = 4.0mA         |     | 0.27            | 0.4   |        |  |

| Vol             | Output LOW Voltage                  |                                                                                                                                   |                               | I <sub>OL</sub> = 8.0mA         |     | 0.32            | 0.45  | Volts  |  |

| · OL            | (Except Bus)                        |                                                                                                                                   |                               | I <sub>OL</sub> = 12mA          |     | 0.37            | 0.5   |        |  |

| VIH             | Input HIGH Level<br>(Except Bus)    | Guaranteed input logical HIGH for all inputs                                                                                      |                               |                                 | 2.0 |                 |       | Volts  |  |

|                 | input LOW Level                     | Guaranteed input logical LOTT                                                                                                     |                               | MIL                             |     |                 | 0.7   | 1/-14- |  |

| V <sub>IL</sub> | (Except Bus)                        |                                                                                                                                   |                               | COM'L                           |     |                 | 0.8   | Volts  |  |

| v <sub>i</sub>  | Input Clamp Voltage<br>(Except Bus) | V <sub>CC</sub> = MIN, 1 <sub>IN</sub> = -18mA                                                                                    |                               |                                 |     |                 | -1.2  | Volts  |  |

| l <sub>IL</sub> | Input LOW Current                   | VCC = MAX, VIN = 0                                                                                                                | 4V                            | BE, RLE                         |     |                 | -0.72 | mA     |  |

| "L              | (Except Bus)                        | TOO INVIOLENTIAL O                                                                                                                |                               | All other inputs                |     |                 | -0.36 | ,,,,,  |  |

| lн              | Input HIGH Current<br>(Except Bus)  | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 2.7V                                                                                     |                               |                                 |     |                 | 20    | μΑ     |  |

| lį              | Input HIGH Current<br>(Except Bus)  | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 7.0V                                                                                     |                               |                                 |     |                 | 100   | μΑ     |  |

| 1               | Output Short Circuit Current        | N- MAY RE                                                                                                                         |                               | IVER                            | -30 |                 | -130  | mA     |  |

| Isc             | (Except Bus)                        | V <sub>CC</sub> = MAX                                                                                                             | PARITY                        |                                 | -20 |                 | -100  | ] "    |  |

| loc             | Power Supply Current                | V <sub>CC</sub> = MAX, All inpu                                                                                                   | II inputs = GND               |                                 |     | 75              | 110   | mA     |  |

Notes:

Typical limits are at V<sub>CC</sub> = 5.0 V, 25°C ambient and maximum loading.

For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

05402A

## BUS INPUT/OUTPUT CHARACTERISTICS over operating temperature range

| Parameters | Description                             | Test Cond                                     | Min                          | Тур  | Max. | Units |          |

|------------|-----------------------------------------|-----------------------------------------------|------------------------------|------|------|-------|----------|

|            |                                         |                                               | I <sub>OL</sub> = 24mA       |      |      | 0.4   | Volts    |

| VOL        | Bus Output LOW Voltage                  | V <sub>CC</sub> = MIN                         | I <sub>OL</sub> = 48mA       |      |      | 0.5   | Volts    |

| Voн        |                                         | V <sub>CC</sub> = MIN                         | COM'L, IOH = -20mA           | •    |      |       | Volts    |

|            | Bus Output HIGH Voltage                 |                                               | MIL, I <sub>OH</sub> = -15mA | 2.4  |      |       | Volts    |

|            |                                         |                                               | V <sub>O</sub> = 0.4V        |      |      | -200  | 1        |

|            | Bus Leakage Current<br>(High Impedance) | V <sub>CC</sub> = MAX                         | V <sub>O</sub> = 2.4V        |      |      | 50    | μA       |

| Ю          |                                         | Bus enable = 2.4V                             | V <sub>O</sub> = 4.5V        |      |      | 100   | <b> </b> |

| loff       | Bus Leakage Current<br>(Power OFF)      | V <sub>O</sub> = 4.5V<br>V <sub>CC</sub> = 0V |                              |      |      | 100   | μΑ       |

| VIH        | Receiver Input HIGH<br>Threshold        | Bus enable = 2.4V                             |                              | 2.0  |      |       | Volts    |

|            |                                         |                                               | COM'L                        |      |      | 0.8   | Volts    |

| VIL        | Receiver Input LOW Threshold            | Bus enable = 2.4V                             | MIL                          |      | ļ    | 0.7   | Voits    |

| Isc        | Bus Output Short Circuit Current        | V <sub>CC</sub> = MAX<br>V <sub>O</sub> = 0V  | -50                          | -120 | -225 | mA    |          |

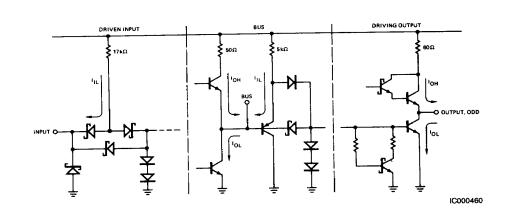

## INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Actual current flow direction shown.

05402A

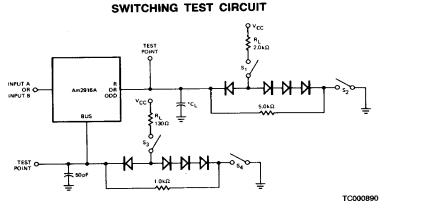

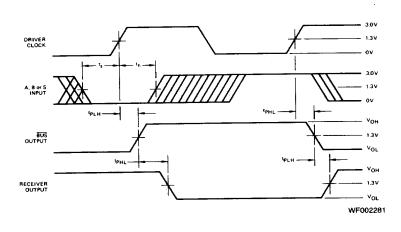

## SWITCHING CHARACTERISTICS over operating range unless otherwise specified

|                                   |                                   | ,                            | C       | OMMERCI         | AL  |         |                 |     |          |

|-----------------------------------|-----------------------------------|------------------------------|---------|-----------------|-----|---------|-----------------|-----|----------|

|                                   |                                   |                              | Am2916A |                 |     | Am2916A |                 |     |          |

| Parameters                        | Description                       | Test Conditions              | Min     | Typ<br>(Note 1) | Max | Min     | Typ<br>(Note 1) | Max | Units    |

| t <sub>PHL</sub>                  | Driver Clock (DRCP) to Bus        |                              |         | 21              | 32  |         | 21              | 36  | ns       |

| t <sub>PLH</sub>                  | Driver Clock (DHCF) to bus        | C <sub>L</sub> (BUS) = 50 pF |         | 21              | 32  |         | 21              | 36  | ] '''    |

| t <sub>ZH</sub> , t <sub>ZL</sub> | Bus Enable (BE) to Bus            | R <sub>L</sub> (BUS) = 130 Ω |         | 13              | 23  |         | 13              | 26  | ns       |

| tHZ, tLZ                          | Dus Chaple (DC) to Dus            |                              |         | 13              | 18  |         | 13              | 21  |          |

| ts                                | Data Inputs (A or B)              |                              | 12      |                 |     | 15      |                 |     | ns<br>ns |

| th                                | Data Inputs (A OI B)              |                              | 6.0     |                 |     | 8.0     |                 |     |          |

| ts                                | Select Inputs (S)                 |                              | 25      |                 |     | 28      |                 |     |          |

| th                                | Select riputs (3)                 |                              | 6.0     |                 |     | 8.0     |                 |     |          |

| tpw                               | Clock Pulse Width (HIGH)          |                              | 17      |                 |     | 20      |                 |     | ns       |

| t <sub>PLH</sub>                  | Bus to Receiver Output            |                              |         | 18              | 30  |         | 18              | 33  | ns ns ns |

| tpHL                              | (Latch Enabled)                   |                              |         | 18              | 27  |         | 18              | 30  |          |

| tplH                              | Latch Enable to Receiver Output   |                              |         | 21              | 30  |         | 21              | 33  |          |

| tPHL                              | Later Enable to Neceiver Output   |                              |         | 21              | 27  |         | 21              | 30  |          |

| ts                                | Bus to Latch Enable (RLE)         |                              | 13      |                 |     | 15      |                 |     |          |

| th                                | Bus to Later Eliable (ALE)        |                              | 4.0     |                 |     | 6.0     |                 |     |          |

| t <sub>PLH</sub>                  | A or B Data to Odd Parity Output  |                              |         | 32              | 42  |         | 32              | 46  |          |

| tpHL                              | (Driver Enabled)                  |                              |         | 26              | 36  |         | 26              | 40  |          |

| tPLH                              | Bus to Odd Parity Output          |                              |         | 21              | 32  |         | 21              | 36  | ns       |

| tpHL                              | (Driver Inhibited, Latch Enabled) |                              |         | 21              | 32  |         | 21              | 36  | ns       |

| t <sub>PLH</sub>                  | Latch Enable (RLE) to             |                              |         | 21              | 32  |         | 21              | 36  |          |

| tpHL                              | Odd Parity Output                 |                              |         | 21              | 32  |         | 21              | 36  |          |

Notes:

1. Typical limits are at V<sub>CC</sub> = 5.0 V, 25°C ambient and maximum loading.

2. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

$^{*}C_{L}$  = 15pF for tpLH, tpHL, tzL, tzH  $C_{L}$  = 5pF for tHz, tLZ

## SWITCHING WAVEFORMS

Note: Bus to Receiver output delay is measured by clocking data into the driver register and measuring the BUS to R combinatorial delay.

05402A

Refer to Page 13-1 for Essential Information on Military Devices