T.SZ-31

Micro

**Devices**

**Advanced**

# Am29833A/Am29853A

# **Parity Bus Transceivers**

# DISTINCTIVE CHARACTERISTICS

- High-speed bidirectional bus transceivers for processor organized devices

- T-R delay = 6 ns typical

- Ri-Parity delay = 9 ns typical

- Error flag with open-collector output

- Generates odd parity for all-zero protection

- 200 mV minimum input hysteresis (Commercial) on input data ports

- High drive capability:

- 48 mA Commercial lou

- Higher speed, lower power versions of the Am29833 & Am29853

#### **GENERAL DESCRIPTION**

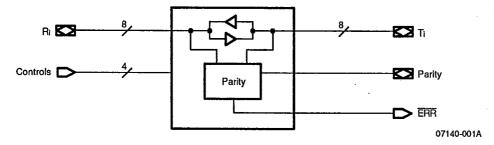

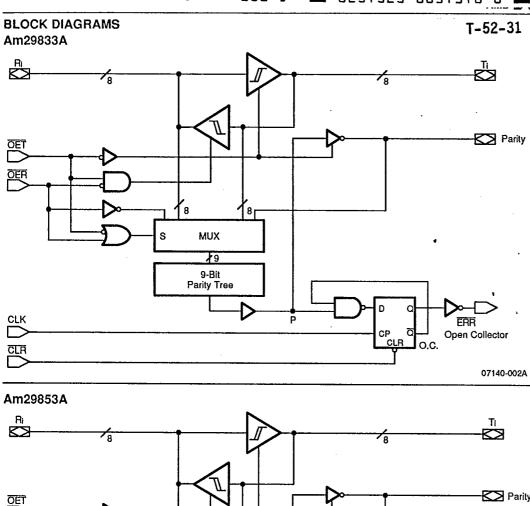

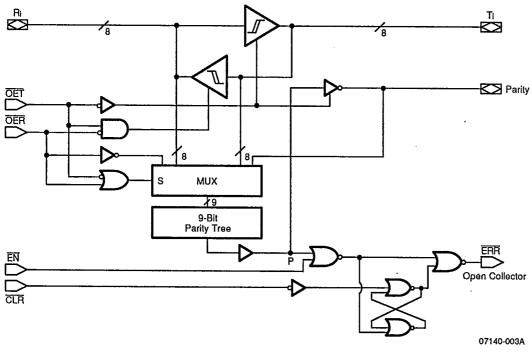

The Am29833A and Am29853A are high-performance parity bus transceivers designed for two-way communications. Each device can be used as an 8-bit transceiver, as well as a 9-bit parity checker/generator. In the transmit mode, data is read at the R port and output at the T port with a parity bit. In the receive mode, data and parity are read at the T port, and the data is output at the R port along with an ERR flag showing the result of the

In the Am29833A, the error flag is clocked and stored in a register which is read at the open-collector ERR output. The CLR input is used to clear the error flag register. In the Am29853A, a latch replaces this register, and the EN and CLR controls are used to pass, store, sample or clear the error flag output. When both output enables

are disabled in the Am29853A and Am29833A, the parity logic defaults to the transmit mode, so that the ERR pin reflects the parity of the R port.

The output enables, OER and OET, are used to force the port outputs to the high-impedance state so that other devices can drive bus lines directly. In addition, the user can force a parity error by enabling both OER and OET simultaneously. This transmission of inverted parity gives the designer more system diagnostic capability.

Each of these devices is produced with AMD's proprietary IMOX™ bipolar process, and features typical propagation delays of 6 ns, as well as high-capacitive drive capability.

## SIMPLIFIED BLOCK DIAGRAM

Publications 07140 Issue Date: December 1990 IMOX is a trademark of Advanced Micro Devices, Inc.

5-39

5-40

Am29833A/Am29853A

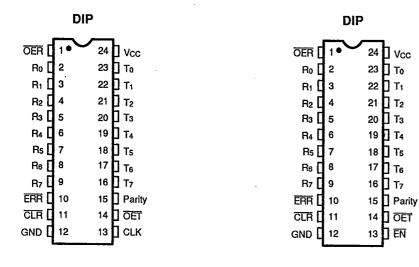

CONNECTION DIAGRAMS (Top View)

T-52-31

Am29833A

Am29853A

07140-004A

07140-005A

# **FUNCTION TABLE**

Am29833A (Register Option)

T-52-31

|                       | Inputs  |                       |             |                      |                                           |                           |                               |                          | Out              | puts                  |                           |                                                                                                                                        |

|-----------------------|---------|-----------------------|-------------|----------------------|-------------------------------------------|---------------------------|-------------------------------|--------------------------|------------------|-----------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| OET                   | ŌĒR     | CLR                   | CLK         | Ri                   | Sum of<br>H's<br>of Ri                    | <b>T</b> i                | Sum of<br>H's<br>(Ti+ Parity) | Ri                       | Ti               | Parity                | ERR                       | Function                                                                                                                               |

| L<br>L<br>L           | I I I I | X<br>X<br>X           | X<br>X<br>X | # #                  | ODD<br>EVEN<br>ODD<br>EVEN                | NA<br>NA<br>NA<br>NA      | NA<br>NA<br>NA<br>NA          | NA<br>NA<br>NA<br>NA     | H<br>H<br>L<br>L | HLH                   | NA<br>NA<br>NA            | Transmit mode:<br>transmits data from<br>R port to T port,<br>generating parity.<br>Receive path is<br>disabled.                       |

| H<br>H<br>H           | L L L L | H<br>H<br>H<br>H      | ↑<br>↑<br>↑ | NA<br>NA<br>NA<br>NA | NA<br>NA<br>NA<br>NA                      | HLLL                      | ODD<br>EVEN<br>ODD<br>EVEN    | H<br>L<br>L              | NA<br>NA<br>NA   | NA<br>NA<br>NA<br>NA  | HLHL                      | Receive mode:<br>transmits data from<br>T port to R port with<br>parity test resulting in<br>error flag. Transmit<br>path is disabled. |

| Х                     | х       | L                     | Х           | Х                    | Х                                         | Х                         | ×                             | Х                        | ×                | Х                     | Н                         | Clear error flag register.                                                                                                             |

| H                     | H       | H                     | X           | X<br>X               | X<br>X                                    | X<br>X                    | X                             | Z<br>Z                   | Z<br>Z           | Z<br>Z                | Н                         | Both transmitting and receiving paths are disabled.                                                                                    |

| H<br>H<br>L<br>L<br>L | H       | H<br>X<br>X<br>X<br>X | ↑           | LHHLL                | ODD<br>EVEN<br>ODD<br>EVEN<br>ODD<br>EVEN | X<br>NA<br>NA<br>NA<br>NA | X<br>X<br>NA<br>NA<br>NA      | Z<br>Z<br>NA<br>NA<br>NA | ZZHHLL           | Z<br>Z<br>H<br>L<br>H | H<br>NA<br>NA<br>NA<br>NA | Parity logic<br>defaults to transmit<br>mode. Forced-error<br>checking.                                                                |

H = HIGH

L = LOW

1 = LOW-to-HIGH Transition

X = Don't Care

Z = High Impedance

NA= Not Applicable

\* = Store the State of the Last Receive Cycle ODD = Odd Number

EVEN= Even Number

i = 0, 1, 2, 3, 4, 5, 6, 7

# T-52-31

## **FUNCTION TABLE** Am29853A (Latch Option)

|         |                                       |             |             | Input                | S                          |                |                            |                      | Out                  | puts                 |                      |                                                                                                                                              |

|---------|---------------------------------------|-------------|-------------|----------------------|----------------------------|----------------|----------------------------|----------------------|----------------------|----------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                       |             |             |                      | Sum of<br>H's              |                | Sum of<br>H's              |                      |                      |                      |                      |                                                                                                                                              |

| OET     | OER                                   | CLR         | EN          | Ri                   | of Ri                      | Ti             | (Ti + Parity)              | Ri                   | Ti                   | Parity               | ERR                  | Function                                                                                                                                     |

| L       | # # # # # # # # # # # # # # # # # # # | X<br>X<br>X | X<br>X<br>X | HLLL                 | ODD<br>EVEN<br>ODD<br>EVEN | NA<br>NA<br>NA | NA<br>NA<br>NA<br>NA       | NA<br>NA<br>NA<br>NA | HHLL                 | L<br>H<br>L<br>H     | NA<br>NA<br>NA       | Transmit mode:<br>transmits data from<br>R port to T port,<br>generating parity.<br>Receive path is<br>disabled.                             |

| HHHH    |                                       |             | 1111        | NA<br>NA<br>NA<br>NA | NA<br>NA<br>NA<br>NA       | エエーー           | ODD<br>EVEN<br>ODD<br>EVEN | H<br>H<br>L<br>L     | NA<br>NA<br>NA<br>NA | NA<br>NA<br>NA<br>NA | エーエン                 | Receive mode:<br>transmits data from<br>T port to R port with<br>parity test resulting in<br>error flag. Transmit<br>path is disabled.       |

| HHHH    |                                       | H H H       | 1 1 1       | NA<br>NA<br>NA<br>NA | NA<br>NA<br>NA<br>NA       | # #            | ODD<br>EVEN<br>ODD<br>EVEN | H<br>H<br>L          | NA<br>NA<br>NA<br>NA | NA<br>NA<br>NA<br>NA | T - T -              | Receive mode:<br>transmits data from<br>T port to R port,<br>passes parity test<br>resulting in error flag.<br>Transmit path is<br>disabled. |

| Н       | L                                     | Н           | Н           | NA                   | NA                         | Х              | ×                          | Х                    | NA                   | NA                   | •                    | Store the state of error flag latch.                                                                                                         |

| X       | Х                                     | L           | Н           | Х                    | X                          | Х              | X                          | X                    | NA                   | NA                   | Н                    | Clear error flag latch.                                                                                                                      |

| H H H H | <b>###</b>                            | X<br>X      | HHLL        | X<br>L<br>H          | X<br>X<br>ODD<br>EVEN      | X<br>X<br>X    | X<br>X<br>X                | Z<br>Z<br>Z<br>Z     | Z<br>Z<br>Z<br>Z     | Z<br>Z<br>Z<br>Z     | * ##-                | Both transmitting and<br>receiving paths are<br>disabled. Parity logic<br>defaults to transmit<br>mode.                                      |

|         | L<br>L<br>L                           | X<br>X<br>X | X<br>X<br>X | H<br>H<br>L          | ODD<br>EVEN<br>ODD<br>EVEN | NA<br>NA<br>NA | NA<br>NA<br>NA<br>NA       | NA<br>NA<br>NA<br>NA | HHLL                 | H<br>L<br>H<br>L     | NA<br>NA<br>NA<br>NA | Forced-error checking.                                                                                                                       |

H = HIGH

L = LOW

↑ = LOW-to-HIGH Transition X = Don't Care

Z= High Impedance

NA= Not Applicable

\*= Store the State of the Last Receive Cycle

ODD = Odd Number

EVEN= Even Number

i = 0, 1, 2, 3, 4, 5, 6, 7

T-52-31

## **TRUTH TABLES Error Flag Output**

Am29833A

| Inp | Inputs   |           | Outputs<br>Pre-state | Output |                      |

|-----|----------|-----------|----------------------|--------|----------------------|

| CLR | CLK      | Point "P" | ERR <sub>n-1</sub>   | ERR    | Function             |

| Н   | 1        | H         | Н                    | Н      |                      |

| н   | <b>↑</b> | ×         | L                    | L      | Sample (1's Capture) |

| Н   | <b>↑</b> | L         | x                    | L      |                      |

| L   | X        | X         | X                    | Н      | Clear                |

Note:

OET is HIGH and OER is LOW.

#### Am29853A

| Inputs |        | Internal Outputs to Device Pre-state |                    | Output |                      |

|--------|--------|--------------------------------------|--------------------|--------|----------------------|

| EN     | EN CLR |                                      | ERR <sub>n-1</sub> | ERR    | Function '           |

| L      | L      | L                                    | Х                  | L      | Dane .               |

| L      | L      | H                                    | X                  | Н      | Pass                 |

| L      | Н      | L                                    | X                  | L      |                      |

| L      | ј н    | x                                    | L                  | L      | Sample (1's Capture) |

| L      | н      | Н                                    | н                  | н      |                      |

| _ Н    | L      | X                                    | X                  | Н      | Clear                |

| Н      | Н      | Х                                    | L                  | L      | Store                |

| Н      | Н      | x                                    | Н                  | н      | Sivie                |

Note:

OET is HIGH and OER is LOW.

# T-52-31

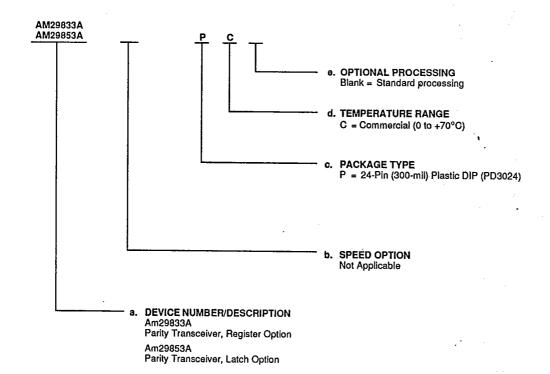

#### **ORDERING INFORMATION Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

a. Device Number

- a. Device Number

b. Speed Option (If applicable)

c. Package Type

d. Temperature Range

e. Optional Processing

| Valid Combinations |    |  |  |  |  |  |  |

|--------------------|----|--|--|--|--|--|--|

| AM29833A           |    |  |  |  |  |  |  |

| AM29853A           | PC |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### PIN DESCRIPTION Am29833A/Am29853A

#### OEF

## Output Enable Receive (Input, Active LOW)

When LOW in conjunction with OET HIGH, the devices are in the Receive mode (Ri are outputs, Ti and Parity are inputs).

#### **OET**

## Output Enable Transmit (Input, Active LOW)

When LOW in conjunction with OER HIGH, the devices are in the Transmit mode (Ri are inputs, Ti and Parity are outputs).

#### $R_i$

#### Receive Port (Input/Output, Three-State)

$\mbox{\bf R}_{i}$  are the 8-bit data inputs in the Transmit mode, and the outputs in the Receive mode.

#### Ti

#### Transmit Port (Input/Output, Three-State)

T<sub>i</sub> are the 8-bit data outputs in the Transmit mode, and the inputs in the Receive mode.

#### **Parity**

#### Parity Flag (input/Output, Three-State)

In the Transmit mode, the Parity signal is an active output used to generate odd parity. In the Receive mode, the Ti and Parity inputs are combined and checked for odd parity. When both output enables are HIGH, the Parity Flag is in the high impedance state. When both output enables are LOW, the Parity bit forces a parity error.

#### T-52-31

#### Am29833A Only

#### ERR

28E D

#### **Error Flag (Output, Open Collector)**

In the Receive mode, the parity of the Ti bits is calculated and compared to the Parity Input. ERR goes LOW when the comparison indicates a parity error. ERR stays LOW until the register is cleared.

#### **CLR**

#### Clear (Input, Active LOW)

When CLR goes LOW, the Error Flag Register is cleared (ERR goes HIGH).

#### **CLK**

#### Clock (Input, Positive Edge-Triggered)

This pin is the clock input for the Error Flag register.

#### Am29853A Only

#### **ERR**

#### Error Flag (Output, Open Collector)

In the Receive mode, the parity of the Tıbits is calculated and compared to the Parity input. ERR goes LOW when the comparison indicates a parity error. ERR stays LOW until the latch is cleared.

#### CLR

#### Clear (Input, Active LOW)

When CLR goes LOW, and EN is HIGH, the Error Flag latch is cleared (ERR goes HIGH).

#### ĒΝ

#### Latch Enable (Input, Active LOW)

This pin is the latch enable for the Error Flag latch.

**ABSOLUTE MAXIMUM RATINGS**

**OPERATING RANGES**

Commercial (C) Devices

T-52-31

Storage Temperature

-65°C to +150°C

Ambient Temperature with

Power Applied

-55 to +125°C

Ambient Temperature (TA) Supply Voltage (Vcc)

0 to +70°C +4.5 to +5.5 V

Supply Voltage to Ground

Potential Continuous

-0.5 V to +7.0 V

DC Voltage Applied to Outputs For High Output State

-0.5 V to +5.5 V

DC Input Voltage

-1.5 V to +6.0 V

DC Output Current, Into Outputs

100 mA

DC Input Current

-30 mA to +5.0 mA

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

Operating ranges define those limits between which the functionality of the device is guaranteed.

DC CHARACTERISTICS over operating range unless otherwise specified

| Parameter<br>Symbol | Parameter Description        | Test Condition                     | Test Conditions      |                  |     |      | Unit     |

|---------------------|------------------------------|------------------------------------|----------------------|------------------|-----|------|----------|

| Vон                 | Output HIGH Voltage          | Vcc = 4.5 V,                       | 2.4                  |                  |     |      |          |

|                     | Except (ERR)                 | Vin=VinorVil                       |                      | Iон = -24 mA     | 2.0 |      | ٧        |

| VoL                 | Output LOW Voltage           | Vcc = 4.5 V,                       | ERR                  | IoL = 48 mA      |     | 0.5  | V        |

|                     |                              | VIN = VIH Or VIL                   | All Other<br>Outputs | loL = 48 mA      |     | 0.5  | ٧        |

| ViH                 | Input HIGH Voltage           | Guaranteed Inp<br>all inputs (Note | ut Logical I<br>1)   | HIGH Voltage for | 2.0 |      | ٧        |

| VIL                 | Input LOW Voltage            | Guaranteed Inp<br>all inputs (Note | ut Logical L<br>1)   | OW Voltage for   |     | 8.0  | ٧        |

| Vı                  | Input Clamp Voltage          | Vcc = 4.5 V, I <sub>IN</sub>       |                      | -1.2             | . V |      |          |

| VHYST               | Hysteresis for Inputs Ri, Ti |                                    |                      |                  | 200 |      | mV       |

| IzL                 | I/O Port LOW Current         | Vcc = 5.5 V, VIN                   | = 0.4 V              |                  |     | -550 | μΑ       |

| l <sub>IL</sub>     | Input LOW Current            | Vcc = 5.5 V, Vin                   | = 0.4 V              |                  | 7   | -0.5 | mA       |

| Ін                  | Input HIGH Current           | Vcc = 5.5 V, Vin                   | = 2.7 V              |                  |     | 50   | μА       |

| lı .                | Input HIGH Current           | Vcc = 5.5 V, VIN                   | = 5.5 V              |                  |     | 100  | μА       |

| lzн                 | I/O Port HIGH Current        | Vcc = 5.5 V, VIN                   | = 2.7 V              |                  |     | 100  | μА       |

| lzı                 | I/O Port HIGH Current        | Vcc = 5.5 V, ViN                   | = 5.5 V              |                  |     | 150  | · μA     |

| Isc                 | Output Short-Circuit Current | Vcc = 5.5 V, Vo                    | = 0 V (Note          | e 2)             | -75 | -250 | mA       |

| loff                | Bus Leakage Current          | Vcc = 0 V, Vo =                    | 2.9 V                |                  |     | 100  | μА       |

| lcc                 | Power Supply Current         | Vcc = 5.5 V                        |                      | Outputs LOW      | ~ · | 180  | <u> </u> |

|                     |                              | Outputs Loaded                     |                      | Outputs HIGH     |     | 155  | mA       |

|                     |                              |                                    |                      | Outputs Hi-Z     |     | 170  |          |

<sup>1.</sup> Input thresholds are tested during DC parameter testing, and may be tested in combination with other DC parameters.

<sup>2.</sup> Not more than one output shorted at a time. Duration of the short-circuit test should not exceed one second.

SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                     |              | Test Conditions*       | Min. | Max.                 | Unit |  |

|---------------------|-------------------------------------------|--------------|------------------------|------|----------------------|------|--|

| tplH                | Propagation Delay to Ri to Ti             |              |                        |      | 10                   | ns   |  |

| tphl.               | Ti to Ri                                  |              |                        |      | 10                   | ns   |  |

| <b>t</b> PLH        |                                           |              |                        |      | 15                   | ns   |  |

| <b>t</b> PHL        | Propagation Delay Ri to Pari              | ty .         |                        |      | 15                   | ns   |  |

| tzн                 | Output Enable Time OER, O                 | ET to Ri, Ti |                        | 12   |                      | ns   |  |

| tzı                 | and Parity                                |              |                        |      | 12                   | ns   |  |

| tHZ                 | Output Disable Time OER, O                | ET to Ri, Ti |                        | 12   |                      | ns   |  |

| tız                 | and Parity                                |              |                        | 12   | 12                   | ns   |  |

| ts                  | T <sub>i</sub> , Parity to CLK Setup Time | (Note 1)     | C <sub>L</sub> = 50 pF | 12   |                      | ns   |  |

| tн                  | Ti, Parity to CLK Hold Time (             | Note 1)      | R <sub>1</sub> = 500 Ω | 10   | 15                   |      |  |

| TREC                | Clear (CLR ) to CLK Set (Note 2)          | up Time      | $R_2 = 500 \Omega$     | 15   |                      |      |  |

| tрwн                | Ole als Distant Ministry (Nation 4)       | HIGH         |                        | 7    |                      | ns   |  |

| tpwL                | Clock Pulse Width (Note 1)                | LOW          |                        | 7    |                      | ns   |  |

| tpwL                | Clear Pulse Width                         | LOW          |                        | 7    | 10<br>10<br>15<br>15 | ns   |  |

| <b>t</b> PHL        | Propagation Delay CLK to El               | RR (Note 1)  |                        |      | 12                   | ns   |  |

| <b>t</b> PLH        | Propagation Delay CLR to El               | RR           |                        |      | 16                   | ns   |  |

| tplH                | Propagation Delay T <sub>i</sub> , Parity | to ERR       |                        |      | 22                   | ns   |  |

| tphl.               | (PASS Mode Only) Am29853                  | 3A           |                        |      | 18                   | ns   |  |

| <b>t</b> PLH        | Propagation Delay OER to P                | larit.       |                        |      | 15                   | ns   |  |

| <b>t</b> PHL        | Fropagation Delay OER to P                | ainy         |                        |      | 15                   | ns   |  |

<sup>\*</sup>See test circuit and waveforms (Chapter 2).

#### Notes:

- 1. For Am29853A, replace CLK with EN.

- 2. Not applicable to Am29853A.

**Bus Interface Products**

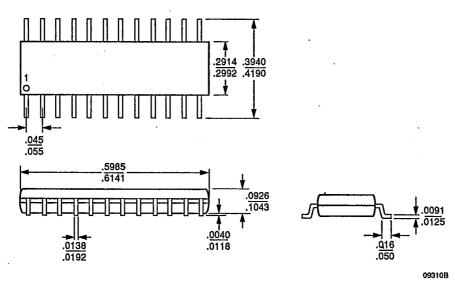

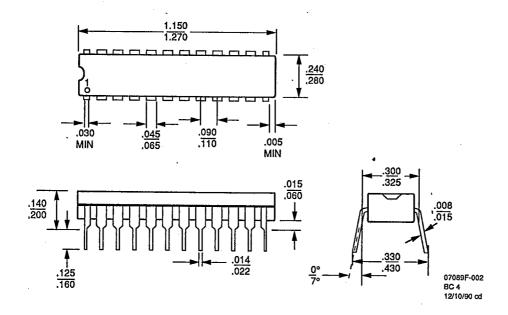

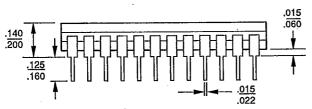

# PD3024 24-Pin 300-mil Plastic SKINNYDIP

Note: For reference only. All dimensions measured in inches. BSC is an ANSI standard for Basic Space Centering.

T-90-20

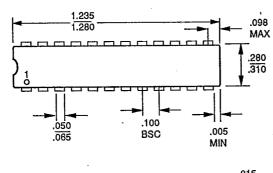

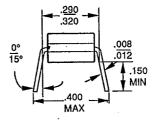

#### **CD**3024 24-Pin 300-mil Ceramic SKINNYDIP

06850C

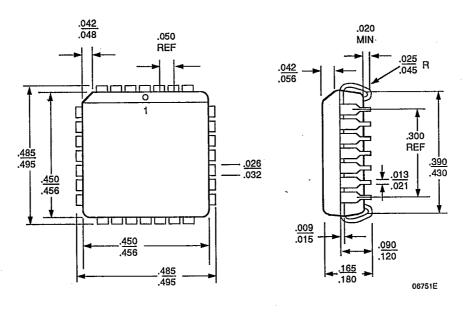

PL 028 28-Pin Plastic Leaded Chip Carrier

**Bus Interface Products**

\$0 024 24-Pin Plastic Small Outline Package

T-90-20