22-A, 3.3-V Input Non-Isolated Wide-Output Adjust Power Module

NOMINAL SIZE = 1.5 in x 0.87 in (38,1 mm x 22,1 mm)

**Features**

- Up to 22-A Output Current

- 3.3-V Input Voltage

- Wide-Output Voltage Adjust (0.8 V to 2.5 V)

- Efficiencies up to 93 % ٠

- 120 W/in<sup>3</sup> Power Density •

- On/Off Inhibit

- Output Voltage Sense

- Pre-Bias Startup

- Margin Up/Down Controls

- Auto-Track<sup>™</sup> Sequencing

- Under-Voltage Lockout

- Output Over-Current Protection (Non-Latching, Auto-Reset)

- Over-Temperature Protection

- Surface Mountable

- Operating Temp: -40 to +85 °C

- DSP Compatible Output Voltages

- IPC Lead Free 2

## Description

The PTH03020 series of non-isolated power modules offers OEM designers a combination of high performance, small footprint, and industry leading features. As part of a new class of power modules these products provide designers with the flexibility to power the most complex multi-processor digital systems using off-the-shelf catalog parts.

The series employs double-sided surface mount construction and provides highperformance step-down power conversion for up to 22 A of output current from a 3.3-V input bus voltage. The output voltage of the PTH03020W can be set to any value over the range, 0.8 V to 2.5 V, using a single resistor.

This series includes Auto-Track<sup>™</sup>. Auto-Track simplifies the task of supply voltage sequencing in a power system by enabling modules to track each other, or any external voltage, during power up and power down.

Other operating features include an on/off inhibit, output voltage adjust (trim), and margin up/down controls. To ensure tight load regulation, an output voltage sense is also provided. A non-latching over-current trip and over-tempterature shutdown provide load fault protection.

Target applications include complex multi-voltage, multi-processor systems that incorporate the industry's high-speed DSPs, micro-processors and bus drivers.

### **Pin Configuration**

| '   |                       |

|-----|-----------------------|

| Pin | Function              |

| 1   | GND                   |

| 2   | Vin                   |

| 3   | Inhibit *             |

| 4   | V <sub>o</sub> Adjust |

| 5   | V <sub>o</sub> Sense  |

| 6   | Vout                  |

| 7   | GND                   |

| 8   | Track                 |

| 9   | Margin Down *         |

| 10  | Margin Up *           |

|     |                       |

Denotes negative logic: Open = Normal operation Ground = Function active

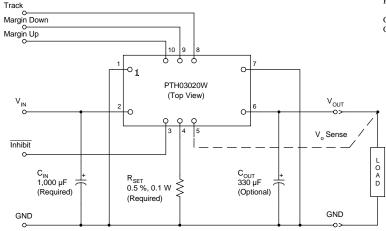

### **Standard Application**

= Resistor to set the desired ooutput

voltage (see spec. table for values). C<sub>in</sub> = Required electrolytic 1,000 µF

Cout = Recommended 330 µF electrolytic

### **Ordering Information**

| Output Voltage (PTH03020 ]xx) |                        | Package Options (PTH03020x ) <sup>(1)</sup> |                   |              |

|-------------------------------|------------------------|---------------------------------------------|-------------------|--------------|

| Code                          | Voltage                | Code                                        | Description       | Pkg Ref. (2) |

| W                             | 0.8 V – 2.5 V (Adjust) | AH                                          | Horiz. T/H        | (EUK)        |

|                               |                        | AS                                          | SMD, Standard (3) | (EUL)        |

Notes: (1) Add "T" to end of part number for tape and reel on SMD packages only.

(2) Reference the applicable package reference drawing for the dimensions and PC board layout

(3) "Standard" option specifies 63/37, Sn/Pb pin solder material.

### **Pin Descriptions**

**GND:** This is the common ground connection for the *Vin* and *Vout* power connections. It is also the 0 VDC reference for the control inputs.

**Vin:** The positive input voltage power node to the module, which is referenced to common *GND*.

**Inhibit:** The Inhibit pin is an open-collector/drain negative logic input that is referenced to *GND*. Applying a low-level ground signal to this input disables the module's output and turns off the output voltage. When the *Inhibit* control is active, the input current drawn by the regulator is significantly reduced. If the *Inhibit* pin is left open-circuit, the module will produce an output whenever a valid input source is applied.

**Vo Adjust:** A 0.5 %, 0.1 W resistor must be connected between this pin and the GND pin to set the output voltage to the desired value. The set point range for the output voltage is from 0.8 V to 2.5 V. The resistor required for a given output voltage may be calculated from the following formula. If left open circuit, the module output will default to its lowest output voltage value. For further information on the adjustment and/or trimming of the output voltage, consult the related application note.

$$R_{set} = 10 \text{ k} \cdot \frac{0.8 \text{ V}}{V_{out} - 0.8 \text{ V}} - 2.49 \text{ k}$$

The specification table gives the preferred resistor values for a number of standard output voltages.

**Vo Sense:** The sense input allows the regulation circuit to compensate for voltage drop between the module and the load. For optimal voltage accuracy *Vo Sense* should be connected to *Vout*. It can also be left disconnected.

**Vout:** The regulated positive power output with respect to the *GND* node.

**Track:** This is an analog control input that allows the output voltage to follow another voltage during powerup and power-down sequences. The pin is active from 0 V up to the nominal set-point voltage. Within this range the module's output will follow the voltage at the *Track* pin on a volt-for-volt basis. When the control voltage is raised above this range, the module regulates at its nominal output voltage. If unused, this input maybe left unconnected. For further information consult the related application note.

**Margin Down:** When this input is asserted to *GND*, the output voltage is decreased by 5% from the nominal. The input requires an open-collector (open-drain) interface. It is not TTL compatible. A lower percent change can be accomodated with a series resistor. For further information, consult the related application note.

**Margin Up:** When this input is asserted to *GND*, the output voltage is increased by 5%. The input requires an open-collector (open-drain) interface. It is not TTL compatible. The percent change can be reduced with a series resistor. For further information, consult the related application note.

22-A, 3.3-V Input Non-Isolated Wide-Output Adjust Power Module

# Environmental & Absolute Maximum Ratings (Voltages are with respect to GND)

| Characteristics             | Symbols             | Conditions                                                 | Min  | Тур | Max       | Units |

|-----------------------------|---------------------|------------------------------------------------------------|------|-----|-----------|-------|

| Track Input Voltage         | Vtrack              |                                                            | -0.3 | _   | Vin + 0.3 | V     |

| Operating Temperature Range | Ta                  | Over Vin Range                                             | -40  | _   | 85        | °C    |

| Solder Reflow Temperature   | T <sub>reflow</sub> | Surface temperature of module body or pins                 |      |     | 215 (i)   | °C    |

| Storage Temperature         | Ts                  | —                                                          | -40  | _   | 125       | °C    |

| Mechanical Shock            |                     | Per Mil-STD-883D, Method 2002.3<br>1 msec, ½ Sine, mounted | _    | TBD | _         | G's   |

| Mechanical Vibration        |                     | Mil-STD-883D, Method 2007.2<br>20-2000 Hz                  | _    | TBD | _         | G's   |

| Weight                      | _                   |                                                            |      | 5   | _         | grams |

| Flammability                | _                   | Meets UL 94V-O                                             |      |     |           |       |

Notes: (i) During reflow of SMD package version do not elevate peak temperature of the module, pins or internal components above the stated maximum. For further guidance refer to the application note, "Reflow Soldering Requirements for Plug-in Power Surface Mount Products."

## Specifications (Unless otherwise stated, T<sub>a</sub> =25 °C, V<sub>in</sub> =3.3 V, V<sub>out</sub> =2.5 V, C<sub>in</sub> =1,000 µF, C<sub>out</sub> =0 µF, and I<sub>o</sub> =I<sub>o</sub>max)

| Characteristics                                                   | Symbols                            | Conditions                                                                                                                                                                                                                                                                                         | Min                          | Тур                              | Max              | Units      |

|-------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------|------------------|------------|

| Output Current                                                    | Io                                 | 60 °C, 200 LFM airflow<br>25 °C, natural convection                                                                                                                                                                                                                                                | 0<br>0                       | _                                | 22 (1)<br>22 (1) | А          |

| Input Voltage Range                                               | Vin                                | Over I <sub>o</sub> range                                                                                                                                                                                                                                                                          | 2.95                         | _                                | 3.65             | V          |

| Set-Point Voltage Tolerance                                       | V <sub>o</sub> tol                 |                                                                                                                                                                                                                                                                                                    | _                            | _                                | ±2               | %Vo        |

| Temperature Variation                                             | $\Delta \text{Reg}_{\text{temp}}$  | $-40 ^{\circ}\text{C} < T_a < +85 ^{\circ}\text{C}$                                                                                                                                                                                                                                                | _                            | ±0.5                             | _                | %Vo        |

| Line Regulation                                                   | ΔRegline                           | Over V <sub>in</sub> range                                                                                                                                                                                                                                                                         | _                            | ±5                               | _                | mV         |

| Load Regulation                                                   | $\Delta \text{Reg}_{\text{load}}$  | Over I <sub>o</sub> range                                                                                                                                                                                                                                                                          | _                            | ±5                               | _                | mV         |

| Total Output Variation                                            | $\Delta Reg_{tot}$                 | Includes set-point, line, load,<br>-40 °C $\leq T_a \leq +85$ °C                                                                                                                                                                                                                                   | _                            | _                                | ±3               | %Vo        |

| Efficiency                                                        | η                                  | $ \begin{array}{c} I_{o} \!=\! 10A & R_{SET} \!=\! 2.21k\Omega \ V_{o} \!=\! 2.5V \\ R_{SET} \!=\! 4.12k\Omega \ V_{o} \!=\! 2.0V \\ R_{SET} \!=\! 5.49k\Omega \ V_{o} \!=\! 1.8V \\ R_{SET} \!=\! 8.87k\Omega \ V_{o} \!=\! 1.5V \\ R_{SET} \!=\! 36.5k\Omega \ V_{o} \!=\! 1.2V \\ \end{array} $ | <br>                         | 95<br>95<br>93<br>91<br>90<br>88 |                  | %          |

| V <sub>o</sub> Ripple (pk-pk)                                     | Vr                                 | 20 MHz bandwidth                                                                                                                                                                                                                                                                                   | _                            | 20                               | _                | mVpp       |

| Over-Current Threshold                                            | I <sub>o</sub> trip                | Reset, followed by auto-recovery                                                                                                                                                                                                                                                                   | _                            | 41                               | _                | A          |

| Transient Response                                                | ${}^{t_{tr}}_{\Delta V_{tr}}$      | 1 A/µs load step, 50 to 100 % I <sub>o</sub> max,<br>C <sub>out</sub> =330 μF<br>Recovery Time<br>V <sub>0</sub> over/undershoot                                                                                                                                                                   | _                            | TBD<br>TBD                       | _                | μSec<br>mV |

| Margin Up/Down Adjust                                             | V <sub>o</sub> adj                 |                                                                                                                                                                                                                                                                                                    | _                            | ± 5                              | _                | %          |

| Margin Input Current (pins 9 /10)                                 | IIL margin                         | Pin to GND                                                                                                                                                                                                                                                                                         | _                            | -8 (2)                           | _                | μA         |

| Track Input Current (pin 8)                                       | III. track                         | Pin to GND                                                                                                                                                                                                                                                                                         | _                            | _                                | -130 (3)         | μA         |

| Track Slew Rate Capability                                        | dV <sub>track</sub> /dt            | $ V_{track} - V_0  \le 50 \text{ mV} \text{ and } V_{track} < V_0(\text{nom})$                                                                                                                                                                                                                     | 5                            | _                                | _                | V/ms       |

| Under-Voltage Lockout                                             | UVLO                               | V <sub>in</sub> increasing<br>V <sub>in</sub> decreasing                                                                                                                                                                                                                                           | 2.2                          | 2.8<br>2.7                       | 2.95             | V          |

| Inhibit Control (pin3)<br>Input High Voltage<br>Input Low Voltage | V <sub>IH</sub><br>V <sub>IL</sub> | Referenced to GND                                                                                                                                                                                                                                                                                  | V <sub>in</sub> -0.5<br>-0.2 | _                                | Open (3)<br>0.8  | V          |

| Input Low Current                                                 | $\mathrm{I}_{\mathrm{IL}}$ inhibit | Pin to GND                                                                                                                                                                                                                                                                                         | _                            | -130                             | —                | μA         |

| Input Standby Current                                             | I <sub>in</sub> inh                | Inhibit (pin 3) to GND, Track (pin 8) open                                                                                                                                                                                                                                                         | _                            | 10                               | _                | mA         |

| Switching Frequency                                               | $f_{s}$                            | Over Vin and Io ranges                                                                                                                                                                                                                                                                             | 250                          | 300                              | 340              | kHz        |

| External Input Capacitance                                        | Cin                                |                                                                                                                                                                                                                                                                                                    | 1,000 (4)                    | _                                | _                | μF         |

| External Output Capacitance                                       | Cout                               |                                                                                                                                                                                                                                                                                                    | 0                            | 330 (5)                          | TBD              | μF         |

| Reliability                                                       | MTBF                               | Per Bellcore TR-332<br>50 % stress, T <sub>a</sub> =40 °C, ground benign                                                                                                                                                                                                                           | TBD                          | _                                | —                | 106 H      |

Notes: (1) See SOA curves or consult factory for appropriate derating.

(2) A small low-leakage (<100 nA) MOSFET is recommended to control this pin. The open-circuit voltage is less than 1 Vdc.</li>

(3) This control pin has an internal pull-up to the input voltage Vin. If it is left open-circuit the module will operate when input power is applied. A small low-leakage (<100 nA) MOSFET is recommended for control. For further information, consult the related application note.</li>

(4) A 1,000 µF electrolytic input capacitor is required for proper operation. The capacitor must be rated for a minimum of 700 mArms of ripple current.

(5) An external output capacitor is not required for basic operation. Adding 330 µF of distributed capacitance at the load will improve the transient response.

## 22-A, 3.3-V Input Non-Isolated Wide-Output Adjust Power Module

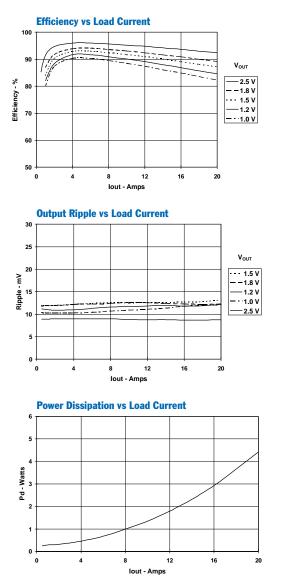

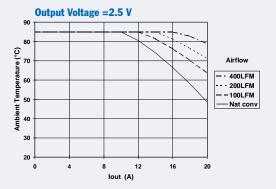

# Characteristic Data; V<sub>in</sub> =3.3V (See Note A)

Safe Operating Area; V<sub>in</sub> =3.3 V (See Note B)

The products listed hereunder are prototype or pre-production devices which have not been fully qualified to Texas Instrument's specifications. Product specifications are subject to change without notice. Texas Instruments makes no warranty, either expressed, implied, or statutory, including implied warranty of merchantability or fitness for a specific purpose, of these products.

Note A: Characteristic data bas been developed from actual products tested at 25°C. This data is considered typical data for the converter.

Note B: SOA curves represent the conditions at which internal components are at or below the manufacturer's maximum operating temperatures. Derating limits apply to modules soldered directly to a 4 in. × 4 in. double-sided PCB with 1 oz. copper.

**W** Texas Instruments

# Capacitor Recommendations for the PTH03020 & PTH05020 Series of Power Modules

### Input Capacitor

The recommended input capacitance is determined by 700 mArms minimum ripple current rating and  $1,000 \,\mu\text{F}$  minimum capacitance.

Ripple current and <100 m $\Omega$  equivalent series resistance (ESR) values are the major considerations, along with temperature, when designing with different types of capacitors. Tantalum capacitors have a recommended minimum voltage rating of twice, 2 × (the maximum DC voltage + AC ripple). This is necessary to insure reliability for input voltage bus applications.

### **Output Capacitors (Optional)**

The ESR of the capacitors is equal to or less than 150 m $\Omega$ . Electrolytic capacitors have marginal ripple performance at frequencies greater than 400 kHz but excellent low frequency transient response. Above the ripple frequency, ceramic capacitors are necessary to improve the transient response and reduce any high frequency noise components apparent during higher current excursions. Preferred low ESR type capacitor part numbers are identified in Table 2-1.

Tantalum Capacitors

Tantalum type capacitors can be used for the output, but

only the AVX TPS, Sprague 593D/594/595or Kemet T495/T510 series. These capacitors are recommended over many other tantalum types due to their higher rated surge, power dissipation, and ripple current capability. As a caution the TAJ series by AVX is not recommended. This series has considerably higher ESR, reduced power dissipation, and lower ripple current capability. The TAJ series is less reliable than the AVX TPS series when determining power dissipation capability. Tantalum or Oscon® types are recommended for applications where ambient temperatures fall below 0 °C.

### **Ceramic Capacitors**

Electrolyitic capacitors may be substituted with ceramic types with the minimum capacitance, for improved ripple reduction on the input and output bus.

### **Capacitor Table**

Table 2-1 identifies the characteristics of capacitors from a number of vendors with acceptable ESR and ripple current (rms) ratings. The number of capacitors required at both the input and output buses is identified for each capacitor type.

This is not an extensive capacitor list. Capacitors from other vendors are available with comparable specifications. Those listed are for guidance. The RMS ripple current rating and ESR (at 100kHz) are critical parameters necessary to insure both optimum regulator performance and long capacitor life.

| Capacitor Vendor/<br>Series                                    | Capacitor Characteristics      |                             |                                          |                                          |                                          |                  | antity           |                                                                           |

|----------------------------------------------------------------|--------------------------------|-----------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------|------------------|---------------------------------------------------------------------------|

|                                                                | Working<br>Voltage             | Value(µF)                   | (ESR) Equivalent<br>Series Resistance    | 105°C Maximum<br>Ripple<br>Current(Irms) | Physical<br>Size(mm)                     | Input<br>Bus     | Output<br>Bus    | Vendor Part Number                                                        |

| Panasonic<br>FC (Radial)<br>FK (Surface Mt.)                   | 10 V<br>10 V<br>25 V<br>10 V   | 560<br>1000<br>1000<br>1000 | 0.090 Ω<br>0.068 Ω<br>0060 Ω<br>0.080 Ω  | 755 mA<br>1050 mA<br>1100 mA<br>850 mA   | 10×12.5<br>10×16<br>12.5×13.5<br>10×10.2 | 2<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | EEUFC1A561<br>EEUFC1A102<br>EEVFK1E102Q<br>EEVFK1A102P                    |

| United Chemi-con<br>LXZ Series<br>FX<br>PXA (Surface Mt.)      | 6.3 V<br>6.3 V<br>10 V<br>10 V | 470<br>1000<br>680<br>1000  | 0.020 Ω<br>0.013 Ω<br>0.090 Ω<br>0.068 Ω | 4130 mA<br>4935 mA<br>760 mA<br>1050 mA  | 10×7.7<br>10×10.5<br>10×12.5<br>10×16    | 2<br>1<br>2<br>1 | 1<br>1<br>1<br>1 | PXA6.3VC471MJ80TP<br>6FX1000M<br>LXZ10VB681M10X12LL<br>LXZ10VB102M10X16LL |

| Nichicon<br>PM Series<br>NA<br>NX (Surface Mt.)                | 6.3 V<br>10 V<br>10 V<br>16 V  | 470<br>470<br>1000<br>1000  | 0.020 Ω<br>0.018 Ω<br>0.065 Ω<br>0.055 Ω | 4130 mA<br>4400 mA<br>1060mA<br>4400 mA  | 10×8<br>10×8<br>16×15<br>10×10           | 2<br>2<br>1<br>1 | 1<br>1<br>1<br>1 | PNX0J471MCAR1GS<br>PNA1A471M1<br>UPM1A102MPH6<br>UPM1C 102MHH6            |

| Sanyo-Os-con:<br>SP<br>SVP (Surface Mt.)                       | 10 V<br>10 V                   | 470<br>560                  | 0.015 Ω<br>0.013 Ω                       | >4500 mA<br>>5200 mA                     | 10×10.5<br>10×12.7                       | 2<br>2           | 1                | 10SP470M<br>10SVP560M                                                     |

| AVX Tantalum<br>TPS (Surface Mt.)                              | 10 V<br>10 V                   | 470<br>470                  | 0.045 Ω<br>0.060 Ω                       | 1723 mA<br>1826 mA                       | 7.3L<br>×5.7W<br>×4.1H                   | 2<br>2           | 1                | TPSE477M010R0045<br>TPSV477M010R0060                                      |

| Kemet Polymer<br>Tantalum<br>T520/T530 Series<br>(Surface Mt.) | 10 V<br>10 V                   | 330<br>330                  | 0.040 Ω<br>0.015 Ω                       | 1800 mA<br>>3800 mA                      | 4.3W<br>×7.3L<br>×4.0H                   | 3<br>3           | 1<br>1           | T520X337M010AS<br>T530X337M010AS                                          |

| Sprague Tantalum<br>595D Series<br>(Surface Mt.)               | 10 V                           | 470                         | 0.100Ω                                   | 1440 mA                                  | 7.2L<br>×6W<br>×4.1H                     | 2                | 1                | 595D477X0010R2T                                                           |

#### Table 2-1: Input/Output Capacitors

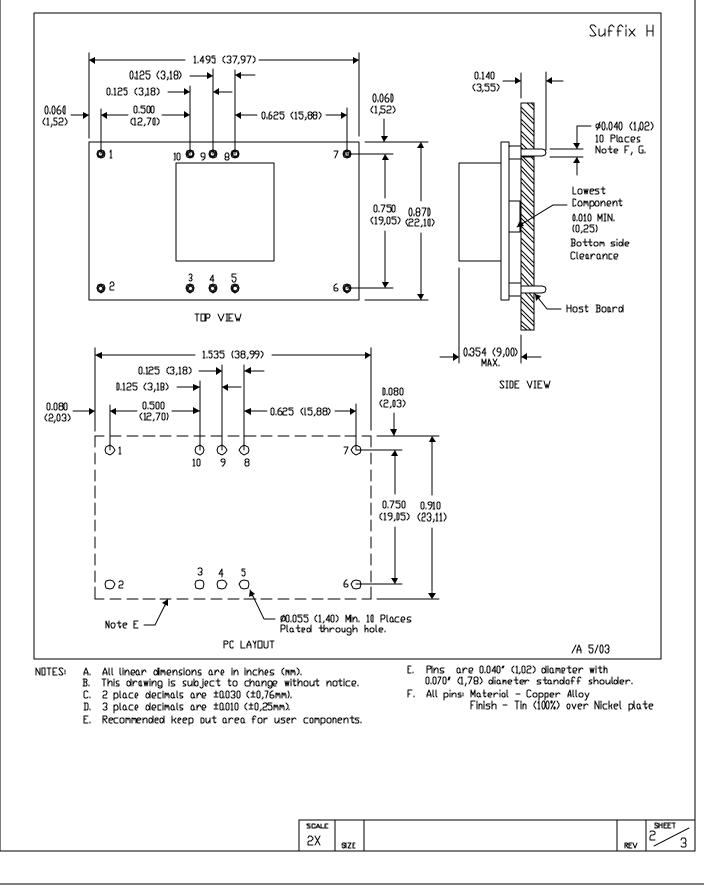

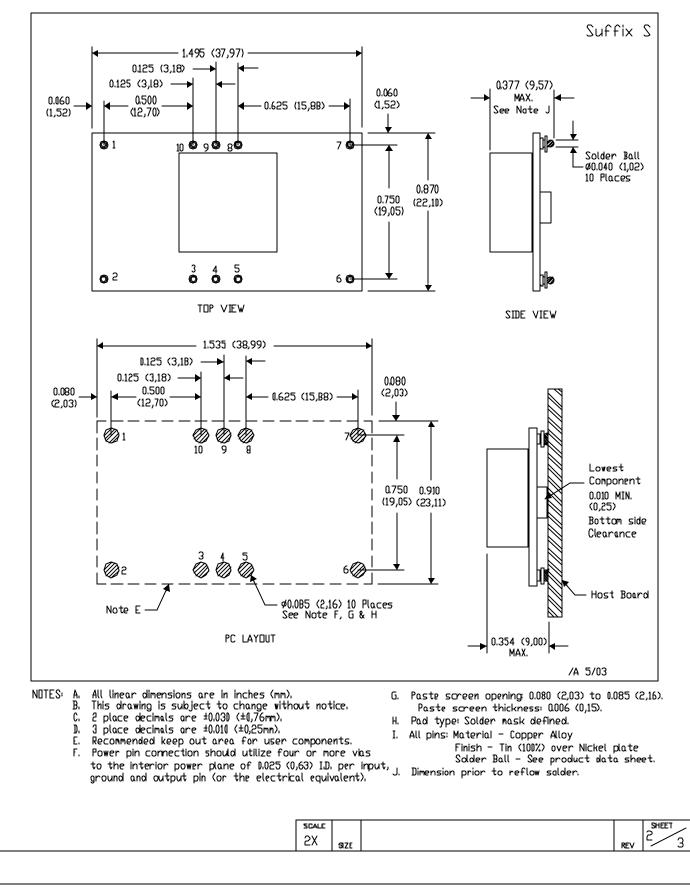

EUK (R-PDSS-T10)

DOUBLE SIDED MODULE

# EUL (R-PDSS-B10)

# DOUBLE SIDED MODULE

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated