## 口

## Am6080

Microprocessor System Compatible 8-Bit High-Speed Multiplying D/A Converter

Advanced Micro Devices

## **DISTINCTIVE CHARACTERISTICS**

- 8-bit D/A with 8-bit input data latch

- Compatible with most popular microprocessors including the Am8086 and the Am2900 Families

- Write, Chip Select and Data Enable logic on chip

- DAC appears as memory location to microprocessor

- MSB inversion under logic control

- Differential current output

- Choice of six coding formats

- Fast settling current output—160 ns

- Nonlinearity to ±0.1% max over temperature range

- Full scale current pre-matched to ±1 LSB

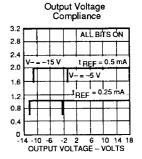

- High output impedance and voltage compliance

- Low full scale current drift—±5 ppm/°C

- Wide range multiplying capability—2.0 MHz bandwidth

- Direct interface to TTL, CMOS, NMOS

- High-speed data latch—80 ns min write time

## **GENERAL DESCRIPTION**

The Am6080 is a monolithic 8-bit multiplying Digital-to-Analog converter with an 8-bit data latch, chip select and other control signal lines used for direct interfacing with microprocessor buses.

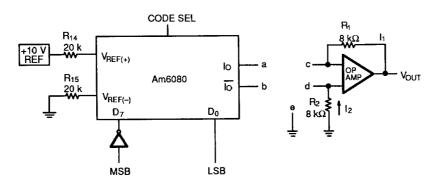

The converter allows a choice of six different coding formats. The most significant bit (D<sub>7</sub>) can be inverted or non-inverted under the control of the code-select input. The code control also provides a zero differential current output for two's complement coding. A high-voltage compliance, complementary current output pair is provided. The data latch is very high speed which makes the Am6080 capable of interfacing with high-speed microprocessors.

Monotonic multiplying performance is maintained over a more than 40-to-1 reference-current range. Matching

within  $\pm 1$  LSB between reference and full-scale current eliminates the need for full-scale trimming in most applications.

The Am6080 guarantees full 8-bit monotonicity. Nonlinearities as tight as 0.1% over the entire operating temperature range are available. Device performance is essentially unchanged over the full power-supply voltage and temperature range.

Applications for the Am6080 include microprocessorcompatible data-acquisition systems and data-distribution systems, 8-bit A/D converters, servo-motor and pen drivers, waveform generators, programmable attenuators, analog-meter drivers, programmable power supplies, CRT-display drivers and high-speed modems.

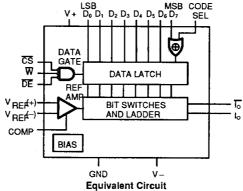

## **BLOCK DIAGRAM**

03941-001C

Publication # 03941 Rev. C Amendment /0 Issue Date: March 1989

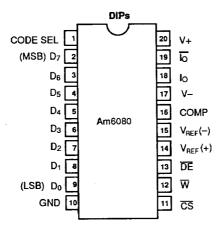

## CONNECTION DIAGRAM Top View

03941-002C

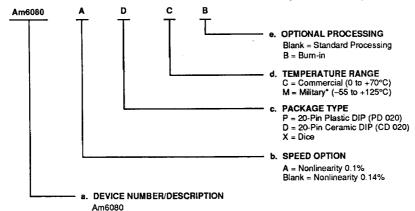

## ORDERING INFORMATION

## **Standard Products**

AMD standard products are available in several packages and operating ranges. The ordering number (Valid Combination) is

formed by a combination of:

a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

Valid Combinations

Am6080 DC, DCB, PC, DMB

Am6080A XM, XC

## Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### **Group A Tests**

Group A tests consist of subgroups 1, 2, 3, 4, 5, 6.

Microprocessor System Compatible 8-Bit High-Speed Multiplying D/A Converter

<sup>\*</sup>Military temperature range products are "NPL" (Non-Compliant Products List) or Non-Mil-STD-883C Compliant products only.

## PIN DECRIPTION

#### Do-D7

$D_0$ - $D_7$  are the input bits 1–8 to the input data latch. Data is transferred to the data latch when  $\overline{CS}$ ,  $\overline{DE}$ , and  $\overline{W}$  are active and is latched when any of the enable signals go inactive.

## $\overline{CS}$

## **Chip Select**

This active low input signal enables the Am6080. Writing into the data latch occurs only when the device is selected.

## CODE SEL Code Select

When CODE SEL = 0, the MSB (D<sub>7</sub>) is inverted and 1 LSB balance current is added to the  $T_0$  output.

## COMP

## Compensation

Frequency compensating terminal for the reference amplifier.

## DE

## **Data Latch Enable**

This active low input is used to enable the data latch. The  $\overline{CS}$ ,  $\overline{DE}$ , and  $\overline{W}$  must be active in order to write into the data latch.

## lo, To

These are high-impedance complementary current outputs. The sum of these currents is always equal to IFS.

#### VREF(+), VREF(-)

Positive and negative reference voltage to the reference bias amplifier. These differential inputs allow the use of positive, negative and bipolar references.

## W

## Write

This active low control signal enables the data latch when the  $\overline{CS}$  and  $\overline{DE}$  inputs are active.

#### **FUNCTIONAL TABLES**

## **DATA LATCH CONTROL**

| ĊS | W | DE | Data Latch  |

|----|---|----|-------------|

| 0  | 0 | 0  | Transparent |

| X  | Х | 1  | Latched     |

| X  | 1 | Х  | Latched     |

| 1  | Х | Х  | Latched     |

X = Don't Care

## **CODE SELECT**

| CODE | Function              |

|------|-----------------------|

| 0    | MSB Inverted (Note 1) |

| 1    | MSB Non-Inverted      |

Note 1. LSB balance current is added to the lo output.

## **APPLICATIONS**

#### APPLICATION HINTS:

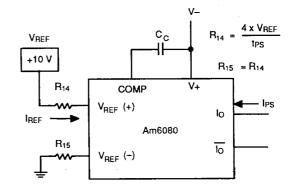

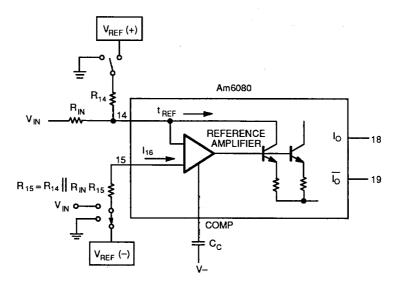

#### 1. Reference current and reference resistor.

There is a 1-to-4 scale up between the reference current ( $I_{REF}$ ) and the full-scale output current ( $I_{FS}$ ). If  $V_{REF}$  = +10 V and  $I_{FS}$  = 2 mA, the value of the  $R_{14}$  is:

$$R_{t4} = \frac{4 \times 10 \text{ Volts}}{2 \text{ mA}} = 20 \text{ k}\Omega$$

03941-004C

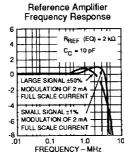

## 2. Reference amplifier compensation.

For AC Reference applications, a minimum value compensation capacitor ( $C_c$ ) is normally used. The value of this capacitor depends on  $R_{15}$ . The minimum values to maximize bandwidth without oscillation are as follows:

TABLE 2.

COMPENSATION CAPACITOR

(I<sub>FS</sub> = 2 mA, I<sub>REF</sub> = 0.5 mA)

| $R_{REF}(k\Omega)$ | C <sub>c</sub> (pF) |

|--------------------|---------------------|

| 10                 | 50                  |

| 5                  | 25                  |

| 2                  | 10                  |

| 1                  | 5                   |

| .5                 | 0                   |

03941-005C

03941-006C

A  $0.01-\mu F$  capacitor is recommended for the fixed reference operation.

Reference Amplifier Biasing

03941-007C

| Reference Configuration             | R <sub>14</sub> | R <sub>15</sub>  | R <sub>IN</sub> | C <sub>c</sub> | REF                                                              |

|-------------------------------------|-----------------|------------------|-----------------|----------------|------------------------------------------------------------------|

| Positive Reference                  | V <sub>R+</sub> | 0V               | N/C             | .01 μF         | V <sub>R4</sub> /R <sub>14</sub>                                 |

| Negative Reference                  | oV              | V <sub>R</sub> _ | N/C             | .01 μF         | -V <sub>R-</sub> /R <sub>14</sub>                                |

| Low Impedance Bipolar<br>Reference  | V <sub>R+</sub> | ov               | V <sub>IM</sub> | (Note 1)       | $(V_{R*}/R_{14}) + (V_{IN}/R_{IN})$<br>(Note 2)                  |

| High Impedance Bipolar<br>Reference | V <sub>P+</sub> | V <sub>IN</sub>  | N/C             | (Note 1)       | (V <sub>R+</sub> − V <sub>IN</sub> )/R <sub>14</sub><br>(Note 3) |

| Pulsed Reference (Note 4)           | V <sub>R+</sub> | ov               | V <sub>IN</sub> | No Сар         | $(V_R + /R_{14}) + (V_{IN}/R_{IN})$                              |

## Notes:

- 1. The compensation capacitor is a function of the impedance seen at the + $V_{REF}$  input and must be at least C = 5 pFX  $R_{14}(eq)$  in k $\Omega$ . For  $R_{14}$  < 800  $\Omega$  no capacitor is necessary.

- 2. For negative values of  $V_{IN}$ ,  $V_R + IR_{14}$  must be greater than  $-V_{IN}$  Max/ $R_{IN}$  so that the amplifier is not turned off.

- 3. For positive values of V<sub>IN</sub>, V<sub>B+</sub> must be greater than V<sub>IN</sub> Max so that the amplifier is not turned off.

- 4. For pulsed operation,  $V_n$ , provides a DC offset and may be set to zero in some cases. The impedance at pin 14 should be 800  $\Omega$  or less and an additional resistor may be connected from pin 14 to ground to lower the impedance.

Am6080 3-19

03941-008C

| cc                             | DE FORMAT                                                                                                                                         | CODE<br>SEL   | CONNECTIONS | OUTPUT SCALE                                                                                                              | OUT<br>SEL            | MSB<br>D7                  | D6                         | D5                         | D4                         | D3                         | D2                         | D1                    | LSB<br>Do                  | I <sub>1</sub><br>(mA)                            | I <sub>2</sub><br>(mA)                                   | Vour                                                  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-----------------------|----------------------------|---------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------|

|                                | Straight binary; one polarity with true input code, true zero output.                                                                             | 1             | a-c<br>b-e  | Positive full scale<br>Positive full scale – LSB<br>Zero scale                                                            | 1 0                   | 1<br>1<br>0                | 1<br>1<br>0                | 1 1 0                      | 1 0                        | 1<br>1<br>0                | 1 1 0                      | 1<br>0<br>0           | 1<br>0<br>0                | 1.9929<br>1.964<br>.000                           | 0                                                        | 9.9606<br>9.9201<br>.000                              |

| UNIPOLAR                       | Complementary binary;<br>one polarity with<br>complementary input<br>code, true zero output.                                                      | 1             | a-e<br>b-c  | Positive full scale<br>Positive full scale – LSB<br>Zero scale                                                            | 0 0 1                 | 0                          | 0 0 1                      | 0<br>0<br>1                | 0<br>0<br>1                | 0<br>0<br>1                | 0 0 1                      | 0 1 1                 | 0<br>1<br>1                | 1.992<br>1.964<br>.000                            | 0 0                                                      | 9.9606<br>9.9201<br>.000                              |

| SYMMETRICAL                    | Straight offset binary;<br>offset half scale,<br>symmetrical about zero,<br>no true zero output.                                                  | 1             | a-c<br>b-d  | Positive full scale Positive full scale – LSB (+) Zero scale (-) Zero scale Negative full scale – LSB Negative full scale | 1<br>1<br>0<br>0      | 1<br>0<br>1<br>0           | 1<br>0<br>1<br>0<br>0      | 1<br>0<br>1<br>0<br>0      | 1<br>1<br>0<br>1<br>0      | 1<br>0<br>1<br>0<br>0      | 1<br>0<br>1<br>0           | 1 0 0 1 1 0           | 1<br>0<br>0<br>1<br>1<br>0 | 1,992<br>1,984<br>1,000<br>,992<br>,008<br>,000   | .000<br>.008<br>.992<br>1.000<br>1.984<br>1.992          | 9.9606<br>9.8807<br>.040<br>0404<br>-9.8807<br>-9.960 |

| OFFSET                         | 1's complement;<br>offset half scale<br>symmetrical about zero,<br>no true zero output<br>MSB complemented<br>(need inverter at B <sub>i</sub> ). | 1<br>(Note 1) | a-c<br>b-d  | Positive full scale Positive full scale – LS8 (+) Zero scale (-) Zero scale Negative full scale – LSB Negative full scale | 0<br>0<br>0<br>1<br>1 | 1<br>1<br>0<br>1<br>0      | 1<br>1<br>0<br>1<br>0      | 1 0 1 0                    | 1<br>1<br>0<br>1<br>0      | 1 0 1 0 0                  | 1<br>0<br>1<br>0           | 1<br>0<br>0<br>1<br>1 | 1<br>0<br>0<br>1<br>1<br>0 | 1.992<br>1.964<br>1.000<br>.992<br>.008<br>.000   | .000<br>.008<br>.992<br>1.000<br>1.984<br>1.992          | -9.880                                                |

| OFFSET<br>WITH<br>TRUE<br>ZERO | Offset binary; offset half scale, true zero output MSB complemented remainder add to IO (need inverter at D <sub>2</sub> )                        | 0<br>(Note 1) | a-c<br>b-d  | Positive full scale Positive full scale – LSB + LSB Zero scale - LSB Negative full scale + LSB Negative full scale        | 1<br>1<br>1<br>0<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1 1 0 0 1 0 0 0            | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1 0 1 0 1 1 0         | 1<br>0<br>1<br>0<br>1<br>1 | 1.992<br>1.984<br>1.008<br>1.000<br>1.992<br>.008 | .008<br>.016<br>.992<br>1.000<br>1.008<br>1.992<br>2.000 | 080                                                   |

|                                | 2's complement;<br>offset half scale,<br>true zero output<br>MSB complemented.                                                                    | 0             | a-c<br>b-d  | Positive full scale Positive full scale – LSB +1 LSB Zero scale -1 LSB Negative full scale + LSB Negative full scale      | 0 0 0 1 1 1 1         | 1<br>0<br>0<br>1<br>0      | 1<br>1<br>0<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>1<br>0 | 1 1 0 0 1 0 0              | 1 1 0 0 1 0 0              | 1<br>1<br>0<br>0<br>1<br>0 | 1 0 1 0 1 1 0         | 1<br>0<br>1<br>0<br>1<br>1 | 1.992<br>1.984<br>1.008<br>1.000<br>.992<br>.008  | .008<br>.016<br>.992<br>1.000<br>1.008<br>1.992<br>2.000 | 080                                                   |

#### Note:

## ADDITIONAL CODE MODIFICATIONS

1. Any of the offset binary codes may be complemented by reversing the output terminal pair.

<sup>1.</sup> An external inverter is necessary since the code select inverts the MSB and adds a 1 LSB balance current to  $\overline{l_0}$ . Only one of these features is desired for this code

## WRITING DATA INTO THE Am6080 (2's Complement)

PORT 1 MOV A, M **:EQU OOH OUTPUT PORT ADDRESS**

:GET DATA FROM MEMORY OUT 0 PORT 1: :SEND DATA

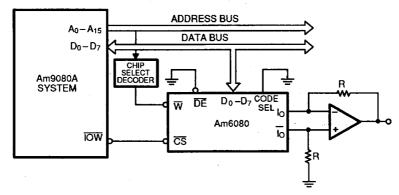

Am9080A Data System

03941-009C

Am6080

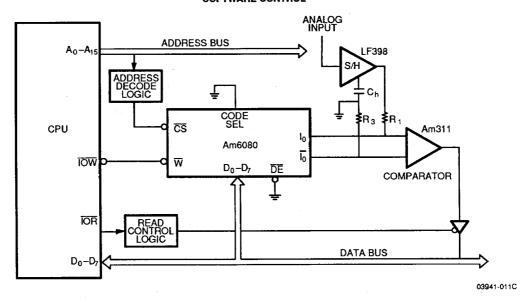

#### ANALOG/DIGITAL COMVERTER UNDER SOFTWARE CONTROL

## Am6080A SOFTWARE FOR A/D CONVERSION USING Am6080

| SEQ       | SOURCE          | STATEMENT                    | SEQ       | SOURCE    | STATEMENT                  |

|-----------|-----------------|------------------------------|-----------|-----------|----------------------------|

| 0 PORT1   | EQU 00H         | :6080 A/O PORT ADDRESS       | 13        | IN PORT3  | INPUT FROM COMP            |

| 1 PORT3   | EQU 02H         | COMPARATOR ADDRESS           | 14        | CRA A     | ;SET SIGN FLAG             |

| 2         | ORG 3E50H       |                              | 15        | JM NEXT   | ;IF SMALLER GO TO NEXT BIT |

| 3 START:  | LXISP, STAKS-16 | :INITIAL STAKS POINTER       | 16        | MOV D,E   | :SAVE RESULT               |

| 4 SAMPLE: | CALL ADCON      | :CALL A/D CONVERSATION       | 17 NEXT:  | MOV A,B   | GET NEXT TRIAL BIT         |

| 5         | JMP SAMPLE      | NEXT SAMPLE                  | 18        | RAR       | SHIFT RIGHT ONCE           |

| 6 ADCON:  | XRA A           | CLEAR ACC                    | 19        | RC        | RETURN ON CARRY            |

| 7         | MOV D.A         | CLEAR D REG                  | 20        | MOV B.A   | STORE TEST BIT             |

| 8         | STC             | SET CARRY                    | 21        | ADD D     | :ACCUMULATE RESULT         |

| 9         | RAR             | :SET BIT 7 TO 1              | 22        | JMP LOOP  | TRY NEXT BIT               |

| 10        | MOV B.A         | STORE TEST BIT AT B REGISTER | 23 STAKS: | DS 16     |                            |

| 11 LOOP:  | MOV E.A         | STORE TEST WORD              | 24        | END START |                            |

| 12        | OUT PORT1       | OUTPUT TO A/D                |           |           |                            |

## Instrumentation and Control

Data Acquisition

Data Distribution

Function Generation

Servo Controls

Programmable Power Supplies

Digital Zero Scale Calibration

Digital Full Scale Calibration

Digitally Controlled Offset Null

#### Audio

Music Distribution

Digitally Controlled Gain

Potentiometer Replacement

Digital Recording

Speech Digitizing

## Signal Processing

CRT Displays

IF Gain Control

8 x 8 Digital Multiplication

Line Driver

## A/D Converters

Ratiometric ADC

Differential Input ADC

Microprocessor Controlled ADC

## D/A Converters

Signal Quadrant Multiplying DAC Two Quadrant Multiplying DAC Four Quadrant Multiplying DAC

3-22 Am6080

## **MAXIMUM RATINGS**

| Storage Temperature               | -65 to +150°C |

|-----------------------------------|---------------|

| Lead Temperature                  |               |

| (Soldering, 60 sec)               | 300°C         |

| Logic Inputs                      | −5 to +18 V   |

| Analog Current Outputs            | -12 to +18 V  |

| Reference Inputs (V14, V15)       | V – to V +    |

| Reference Input                   |               |

| Differential Voltage (V14 to V15) | ±18 V         |

| Reference Input Current (I14)     | 1.25 mA       |

Stresses above those listed under MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

| Military             | -55 to +125°C     |

|----------------------|-------------------|

| Commercial           | 0 to +70°C        |

| Power Supply Voltage | ±18 V             |

| Die Size             | 0.083 x 0.121 in. |

Operating ranges define those limits between which the functionality of the device is guaranteed.

Am6080 3–23

## **DC CHARACTERISTICS**

These specifications apply for  $V_+ = +5 V$ ,  $V_- = -15 V$ ,  $I_{REF} = 0.5 mA$ , over the operating temperature range unless othewise specified. Output characteristics refer to all outputs.

Included in Group A Subgroup. 1, 2, 3, 4, 5, 6 unless otherwise noted.

|                      |                         |            |                                                                |                             |       | Am6080A     |              |                |             |              |                |

|----------------------|-------------------------|------------|----------------------------------------------------------------|-----------------------------|-------|-------------|--------------|----------------|-------------|--------------|----------------|

| Parameter            | Descripti               | on         | Test Conditions                                                |                             | Min   | Тур         | Max          | Min            | Min Typ     |              | Unit           |

|                      | Resolutio               | n          |                                                                |                             | 8     | 8           | 8            | 8              | 8           | 8            | bits           |

|                      | Monotonio               | city       |                                                                |                             | 8     | 8           | 8            | 8              | 8           | 8            | bits           |

| DNL                  | Differentia<br>Nonlinea |            |                                                                |                             | _     | _           | ±.0.19       | -              | _           | ±.0.39       | %FS            |

| NL                   | Nonlinear               | ity        |                                                                |                             |       |             | ±.0.1        | _              | _           | ±0.19        | %FS            |

| I <sub>FS</sub>      | Full Scale              | Current    | $V_{REF} = 10.000$ $R_{14} = R_{15} = 20.$ $T_A = 25^{\circ}C$ | V<br>000 kΩ                 | 1.984 | 1.992       | 2.000        | 1.976          | 1.992       | 2.008        | mA             |

| TCI <sub>FS</sub>    | Full Scale              | Tempco     |                                                                |                             | _     | ±5          | ±20          | _              | ±10         | ±40          | ppm/°C         |

|                      |                         |            |                                                                |                             |       | .0005       | ±.002        | _              | .001        | ±.004        | %FS/°C         |

| V <sub>∞</sub>       | Output Vo               |            |                                                                |                             | -10   | _           | +18          | -10            | _           | +18          | ٧              |

| l <sub>FSS</sub>     | Full Scale<br>Symmet    |            | I <sub>FS1</sub> — I <sub>FS1</sub>                            |                             | _     | ±0.1        | ±1.0         | _              | ±0.2        | ±2.0         | μА             |

| Izs                  | Zero Scal               | e Current  |                                                                |                             |       | 0.01        | 1.0          |                | 0.01        | 2.0          | μА             |

| I <sub>BB</sub>      | Reference Current       |            | V-=-5 V                                                        |                             | 0     | 0.5         | 0.55         | 0              | 0.5         | 0.55         | mA             |

|                      | Range                   |            | V-=-15 V                                                       |                             | 0     | 0.5         | 1.1          | 0              | 0.5         | 1.1          |                |

| V <sub>IL</sub>      | Logic                   | Logic "0"  |                                                                |                             | _     | _           | 0.8          |                | -           | 0.8          | ١ ,,           |

| V <sub>IH</sub>      | Input<br>Levels         | Logic "1"  |                                                                |                             | 2.0   |             | _            | 2.0            | _           | _            | \ \            |

| I <sub>IN</sub>      | Logic Inp               | ut Current | $V_{in} = -5 \text{ V to } +$                                  | -18 V                       |       | _           | 40           | _              | _           | 40           | μА             |

| V <sub>is</sub>      | Logic Inp               | ut Swing   | V- = -15 V                                                     |                             | -5    |             | +18          | -5             |             | +18          | ٧              |

| I <sub>15</sub>      | Reference<br>Current    | e Bias     |                                                                |                             | 0     | -0.5        | -2.0         | 0              | -0.5        | -2.0         | μА             |

| dl/dt                | Referenc<br>Slew Ra     |            | $R_{14(eq)} = 800 \Omega$<br>$C_c = 0 pF$                      | (Note 2)                    | 4.0   | 8.0         | -            | 4.0            | 8.0         | _            | m <b>A</b> /μs |

| PSSI <sub>FS+</sub>  | Power<br>Supply         |            | V + = +4.5 V to<br>V - = -15 V                                 | ,                           | _     | ±0.0003     | ±0.01        | _              | ±0.0005     | ±0.01        | %FS/%          |

| PSSI <sub>FS</sub> _ | Sensitiv                | ity        | V- = -13.5 V<br>V+ = +5 V                                      | V- = -13.5  V to  -16.5  V, |       | ±0.0005     | ±0.01        | _              | ±0.0005     | ±0.01        |                |

| V+                   | Power Su                | pply       | I <sub>REF</sub> = 0.5 mA                                      |                             | 4.5   | _           | 18           | 4,5            |             | 18           | V              |

| V-                   |                         |            | 001                                                            | V+ = +5 V                   | -18   |             | -12          | -18            |             | -12          |                |

| 1+                   | Power Supply            |            | V+ = +5 V, V-                                                  | = -15 V                     |       | 9.8         | 14.7         |                | 9.8         | 14.7         | mA             |

| 1-                   | Current                 |            | <u> </u>                                                       |                             |       | -7.4        | -9.9         |                | -7.4        | -9.9         | 4              |

| l+                   |                         |            | V+ = +15 V, V                                                  | = -15 V                     |       | 9.8<br>-7.4 | 14.7<br>-9.9 | -              | 9.8<br>-7.4 | 14.7<br>-9.9 | 4              |

| I-                   | D=                      | +          | V. 5V.                                                         | 4F \/                       |       |             | <del> </del> | <del>  -</del> | <del></del> | <del></del>  |                |

| P <sub>D</sub>       | Power Di<br>(Note 1)    |            | V+ = +5 V, V-<br>V+ = +15 V, V                                 |                             | =     | 160<br>258  | 222<br>369   | $+ \equiv$     | 160<br>258  | 222<br>369   | mW             |

## Notes:

- 1. Derate Hermetic DIP 10 mW/°C above 100°C. Plastic package 6.8 mW/°C. Leadless 10 mW/°C above 100°C.

- 2. Not tested. Guaranteed by characterization.

## **AC CHARACTERISTICS**

V+ = +5 V, V- = -15 V, I\_{REF} = 0.5 mA,  $R_L < 500~\Omega$ ,  $C_L < 15~pF$  over the operating temperature range unless otherwise specified.

|                  |                            |                   |                       | Commercial |      |      |      |      |      |      |

|------------------|----------------------------|-------------------|-----------------------|------------|------|------|------|------|------|------|

| Parameter        | Descrip                    | Description       |                       | Min.       | Тур. | Max. | Min. | Тур. | Мах. | Unit |

| t <sub>s</sub>   | Setting Time,              |                   | T <sub>A</sub> = 25°C |            | 160  |      |      | 160  |      | ns   |

|                  | All Bits Switched (Note 4) |                   | Settling to ±1/2 LSB  |            |      |      |      |      |      |      |

| t <sub>eus</sub> | Propagation                | Each bit          | T <sub>A</sub> = 25°C |            | 80   | 160  |      | 80   | 160  | ns   |

| t <sub>PHL</sub> | Delay (Note 4)             | All bits switched | 50% to 50%            |            | 80   | 160  |      | 80   | 160  |      |

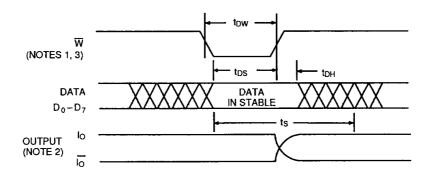

| t <sub>on</sub>  | Data Hold Time (Note 4)    |                   | See timing diagram    | 10         | -30  |      | 10   | -30  |      | ns   |

| tos              | Data Set Up Time (Note 4)  |                   | See timing diagram    | 80         | 35   |      | 100  | 35   |      | ns   |

| t <sub>ow</sub>  | Data Write Time (Note 4)   |                   | See timing diagram    | 80         | 35   |      | 100  | 35   |      | ns   |

#### Notes:

- t<sub>DW</sub> is the overlap of W LOW, CS LOW, and DE LOW. All three signals must be LOW to enable the latch. Any signal going inactive latches the data.

- t<sub>s</sub> is measured with the latches open from the time the data becomes stable on the inputs to the time when the outputs are settled to within ±1/2 LSB. All bits switched on or off.

- The internal time delays from CS, W, and DE inputs to the enabling of the latches are all equal.

- 4. Not tested. Guaranteed by characterization.

## **Timing Diagram**

03941-003C

Am6080 3–25

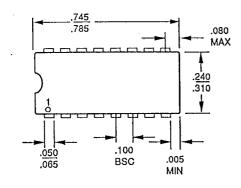

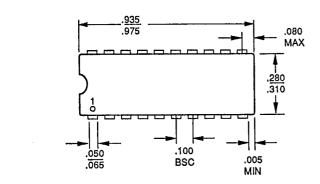

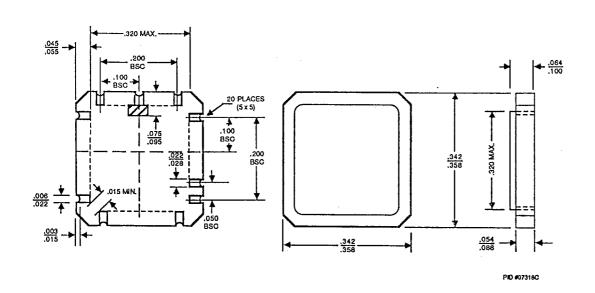

# PHYSICAL DIMENSIONS CD 016

07319B

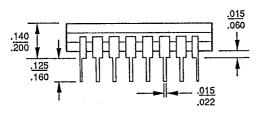

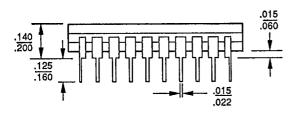

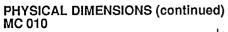

## CD 020

03941-004C

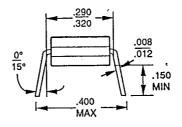

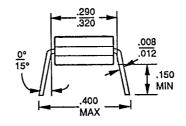

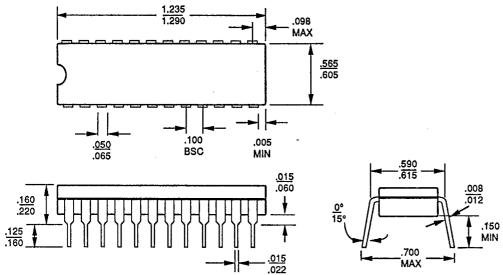

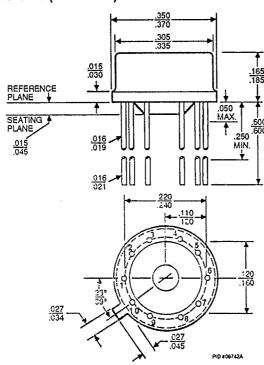

## PHYSICAL DIMENSIONS (continued) CD 024

03067-008A

**CL 020**

## PD 020

03941-005C