# Am79C02/03/031(A)

# Dual Subscriber Line Audio ProcessingCircuit (DSLAC™) Devices

# **TABLE OF CONTENTS**

| Distinctive Characteristics                                    | . 7 |

|----------------------------------------------------------------|-----|

| General Description                                            | . 7 |

| Block Diagram                                                  | . 8 |

| Ordering Information                                           | . 9 |

| Standard Products                                              | . 9 |

| Connection Diagrams                                            | 10  |

| Pin Descriptions                                               | 11  |

| -<br>Functional Description                                    |     |

| Absolute Maximum Ratings                                       |     |

| Operating Ranges                                               |     |

| Commercial (C) Devices                                         |     |

| Electrical Characteristics                                     |     |

| Transmission Characteristics                                   |     |

| Attenuation Distortion                                         |     |

| Group Delay Distortion                                         |     |

| Variation of Gain with Input Level                             |     |

| Total Distortion, Including Quantizing Distortion              |     |

| Discrimination against Out-of-Band Input Signals               |     |

| Discrimination against 12 khz And 16 khz Metering Signals      |     |

| Spurious Out-of-Band Signals at the Analog Output              |     |

| Overload Compression                                           |     |

| Switching Characteristics                                      | 21  |

| Microprocessor Interface                                       | 21  |

| PCM Interface                                                  | 21  |

| Master Clock                                                   | 22  |

| Switching Waveforms                                            | 22  |

| Input and Output Waveforms for AC Tests                        | 22  |

| Master Clock Timing                                            |     |

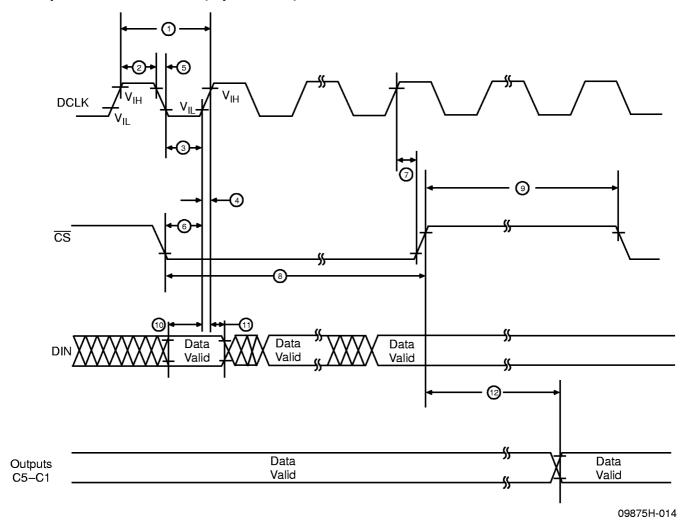

| Microprocessor Interface (Input Mode)                          | 23  |

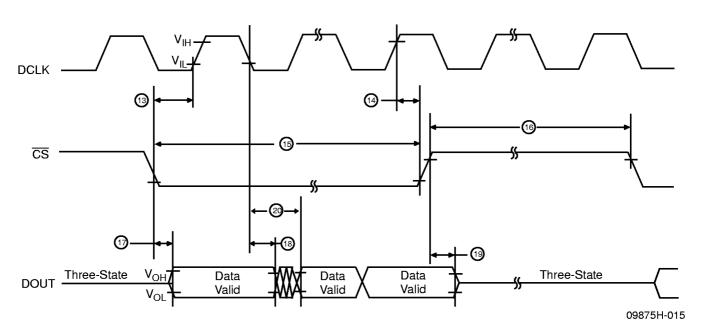

| Microprocessor Interface (Output Mode)                         |     |

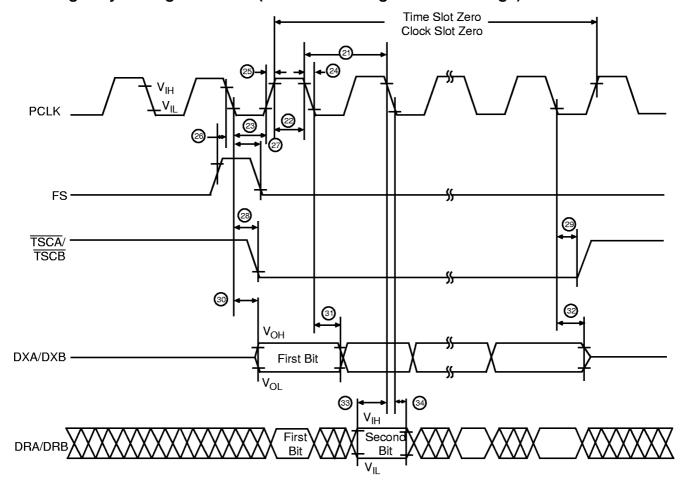

| PCM Highway Timing for Xe = 0 (Transmit on Negative PCLK Edge) | 24  |

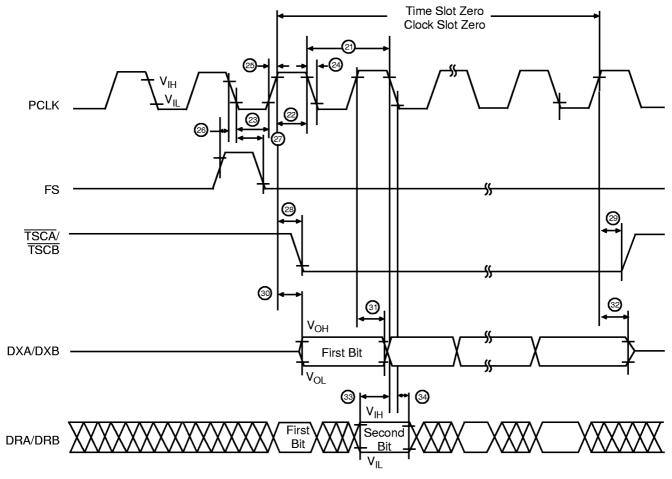

| PCM Highway Timing for Xe = 1 (Transmit on Positive PCLK Edge) |     |

| Operating the DSLAC Device                                     | 26  |

| Signal Processing                                              |     |

| Command Description and Formats                                |     |

| Summary of MPI Commands**                                      |     |

| Command Structure                                              | 31  |

| Programmable Filters                                           |     |

| Detailed Description of DSLAC Device Coefficients              |     |

| Adaptive B Filter Overview                                     |     |

| Adaptive Filter Programming                                    |     |

| User Test Modes                                                |     |

| A-law And μ-law Companding                                     |     |

| Applications                                                   |     |

| Controlling the SLIC                                           |     |

| Calculating Coefficients with Winslac Software                 | 50  |

# FINAL

| LIST OF FIGURES |                                               |    |

|-----------------|-----------------------------------------------|----|

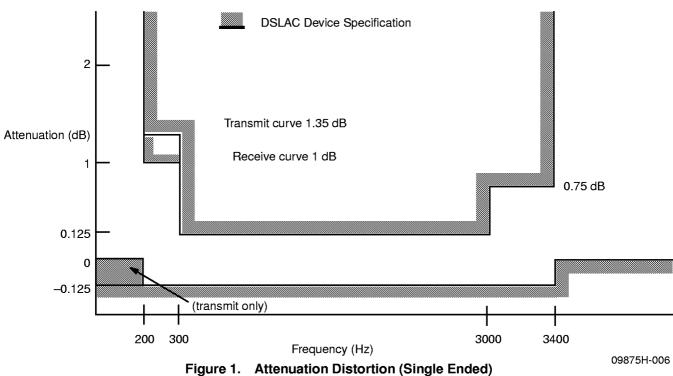

| Figure 1        | Attenuation Distortion (Single Ended)         | 16 |

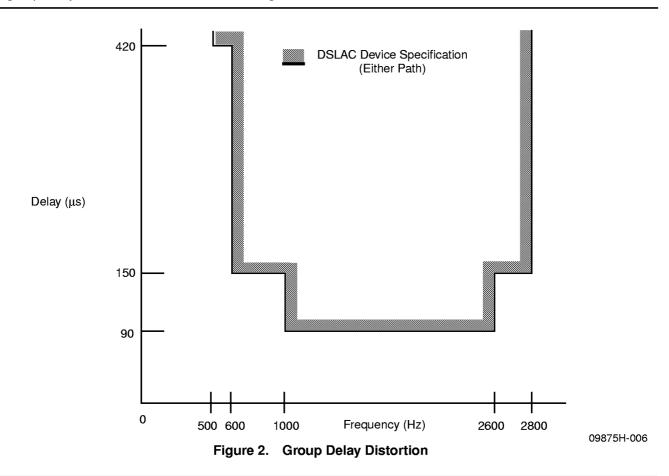

| Figure 2        | Group Delay Distortion                        | 16 |

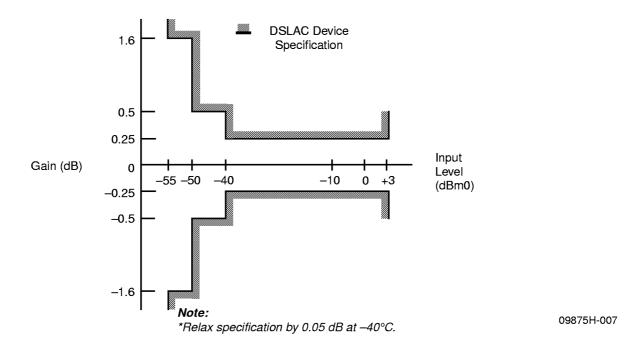

| Figure 3        | Gain Tracking with Tone Input*                | 17 |

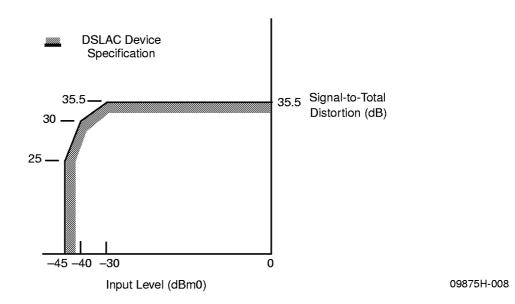

| Figure 4        | Total Distortion with Tone Input (Both Paths) | 17 |

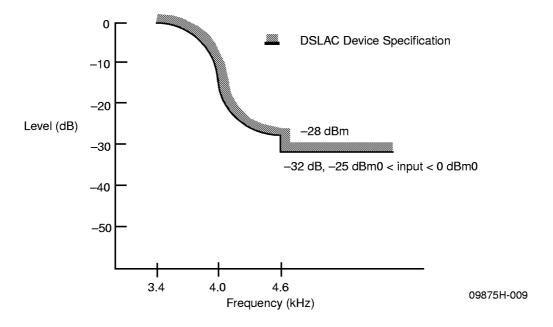

| Figure 5        | Discrimination against Out-of-Band Signals    | 18 |

| Figure 6        | Spurious Out-of-Band Signals                  | 19 |

| Figure 7        | A/A Overload Compression                      | 20 |

| Figure 8        | DSLAC Block Diagram                           | 27 |

| LIST OF TABLES  |                                               |    |

| Table 1         | A-Law: Positive Input Values                  | 49 |

| Table 2         | μ-Law: Positive Input Values                  |    |

#### **DISTINCTIVE CHARACTERISTICS**

#### ■ Software programmable:

- SLIC impedance

- Transhybrid balance

- Transmit and receive gains

- Equalization

- Digital I/O pins

- Time Slot Assigner

- PCM transmit clock edge options

- Adaptive transhybrid balance filter (A suffix only)

- A-law or µ-law coding

- Dual PCM ports

- Up to 8.192 MHz each (128 channels per port)

- 2.048 MHz or 4.096 MHz master clock

- Direct transformer drive

- Built-in test modes

- Low power CMOS

- Mixed mode (analog and digital) impedance scaling

- Performance characteristics guaranteed over 12 dB gain range

#### **GENERAL DESCRIPTION**

The Am79C02/03/031(A) Dual Subscriber Line Audio Processing Circuit (DSLAC device) integrates the key functions of an analog linecard into a single high-performance, programmable dual codec/filter device. The DSLAC device is based on the proven design of the reliable Am7901A Subscriber Line Audio Processing Circuit (SLAC device). The advanced architecture of the DSLAC device implements two independent channels and employs digital filters to allow software control of transmission, thus providing a cost effective solution for the analog to PCM function of a linecard.

The Am79C02/03/031(A) DSLAC device's advanced CMOS technology makes this an economical device that has both the functionality and the low power consumption needed in linecard designs to maximize linecard density at minimum cost. When used with two AMD SLICs, the DSLAC device provides software configurable solutions to the BORSCHT function.

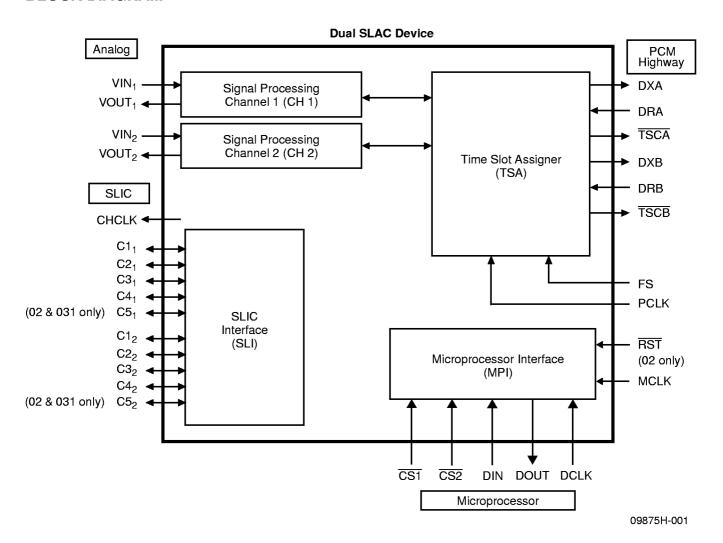

# **BLOCK DIAGRAM**

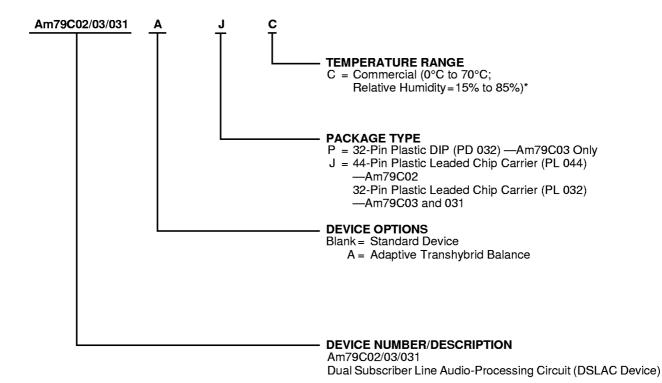

# **ORDERING INFORMATION**

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |                  |  |  |  |

|--------------------|------------------|--|--|--|

| Am79C02            | AJC, JC          |  |  |  |

| Am79C03            | AJC, APC, PC, JC |  |  |  |

| Am79C031           | AJC, JC          |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### Note:

<sup>\*</sup> Functionality of the device from  $0^{\circ}C$  to  $+70^{\circ}C$  is guaranteed by production testing. Performance from  $-40^{\circ}C$  to  $+85^{\circ}C$  is guaranteed by characterization and periodic sampling of production units.

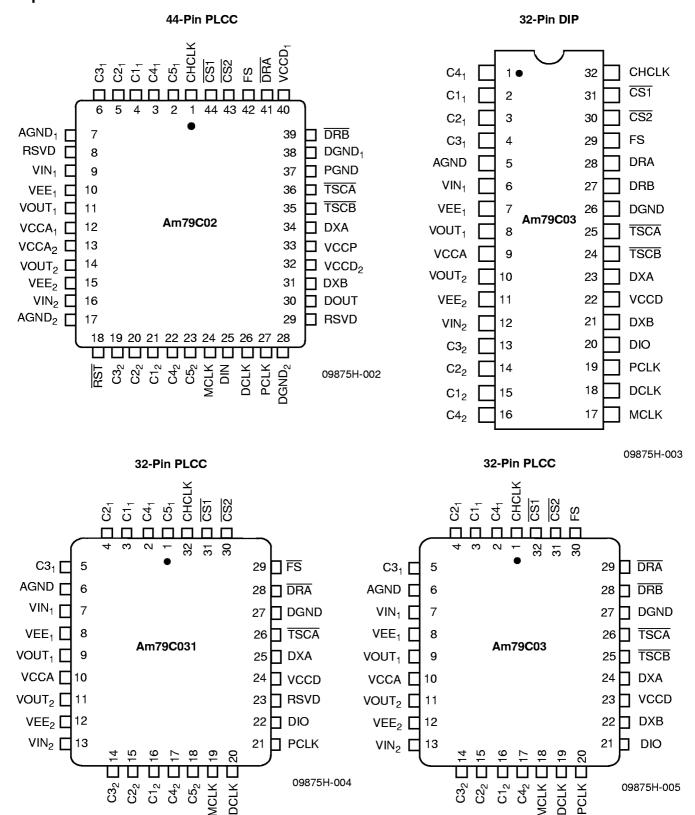

### **CONNECTION DIAGRAMS**

# **Top View**

#### Notes:

- 1. Pin 1 is marked for orientation.

- 2. RSVD = Reserved pin; should not be connected externally to any signal or supply.

# **PIN DESCRIPTIONS**

# C1<sub>1</sub>-C5<sub>1</sub>, C1<sub>2</sub>-C5<sub>2</sub>

#### **Control Inputs/Outputs**

The five SLIC control lines per channel are TTL compatible and bidirectional. They can be used to monitor or control the operation of a SLIC or any other device associated with the subscriber line. Lines C11–C51 are associated with Channel 1, and lines C12–C52 are associated with Channel 2. The C51 and C52 lines are available on the Am79C02(A) and Am79C031(A). C51 and C52 are output only on the Am79C031(A) and must be programmed as outputs.

### **CHCLK**

#### **SLIC Clock Output**

This output provides a 256 kHz or 293 kHz, 50% duty cycle, TTL compatible clock for use by two SLICs. The CHCLK frequency is derived from MCLK and the phase relationship to MCLK is random. CHCLK is capable of driving two TTL inputs.

# CS2-CS1

# **Chip Select Inputs**

The Chip Select inputs (active Low) enable the device to read or write control data.  $\overline{CS1}$  is for the Channel 1 microprocessor interface and  $\overline{CS2}$  is for the Channel 2 microprocessor interface.

# **DCLK**

### **Data Clock Input**

The Data Clock input shifts data into and out of the microprocessor interface of the DSLAC device. The maximum clock rate is 4.096 MHz.

#### DIN

### **Data Input**

Control data is serially written into the Am79C02(A) DSLAC device via the DIN pin with the most significant bit first. The Data Clock determines the data rate. DIN and DOUT may be strapped together to reduce the number of connections to the microprocessor.

#### DIO

### Data Input/Output

Control data is serially written into and read out of the Am79C03(A) and Am79C031(A) DSLAC device via the DIO pin with the most significant bit first. The Data Clock determines the data rate. DIO is high impedance except when data is being transmitted from these DSLAC devices under control of CS1 or CS2. DIO replaces DIN and DOUT as found on the Am79C02(A).

#### **DOUT**

#### **Data Output**

Control data is serially read out of the Am79C02(A) DSLAC device via the DOUT pin with the most significant bit first. The Data Clock determines the data rate. DOUT is high impedance except when data is being transmitted from the DSLAC device under control of  $\overline{CS1}$  or  $\overline{CS2}$ . DIN and DOUT may be strapped together to reduce the number of connections to the microprocessor.

# DRA, DRB

### **PCM Inputs**

The PCM data for Channels 1 and 2 is serially received on either the DRA or the DRB port during user programmed time slots. Eight bits are received with the most significant bit first. Data for each channel is received in 8-bit bursts every 125 µs at the PCLK rate.

# DXA, DXB

#### **PCM Outputs**

The Transmit PCM data from Channels 1 and 2 is sent serially through either the DXA or DXB port during user programmed time slots. Eight bits are transmitted with the most significant bit first. The output is available every 125  $\mu$ s and the data is shifted out in 8-bit bursts at the PCLK rate. DXA and DXB are high impedance between bursts and while the device is in the Inactive mode. DXB is not available on the 79C031(A).

#### **FS**

#### Frame Sync Input

The Frame Sync pulse is an 8 kHz signal that identifies the beginning of a system's PCM frame. The DSLAC device references individual time slots with respect to this input, which must be synchronized to PCLK.

#### **MCLK**

#### **Master Clock Input**

The Master Clock must be a 2.048 MHz or 4.096 MHz clock input for use by the digital signal processor. MCLK may be asynchronous to PCLK.

# **PCLK**

### **PCM Clock Input**

The PCM clock determines the rate at which PCM data is serially shifted into or out of the PCM ports. PCLK is an integer multiple of the frame sync frequency. The maximum clock frequency is 8.192 MHz and the minimum clock frequency is 128 kHz. The PCLK clock may be asynchronous to MCLK.

#### **RST**

#### Reset Input

A logic Low signal to this pin resets the DSLAC device to its default state. (Am79C02(A) only.)

# TSCA, TSCB

# **Time Slot Control Outputs**

The Time Slot Control outputs are open drain (requiring pull-up resistors) and are normally inactive (high impedance). TSCA is active (Low) when PCM data is output on the DXA pin and TSCB is active (Low) when PCM data is output on the DXB pin. (TSCB is available on the Am79C02 and Am79C03 only.)

# VIN<sub>1</sub>, VIN<sub>2</sub>

#### **Analog Inputs**

The analog input is applied to the transmit path of the DSLAC device. The signal is sampled, digitally processed, and encoded for the PCM output.  $VIN_1$  is the input for Channel 1 and  $VIN_2$  is the input for Channel 2.

# VOUT<sub>1</sub>, VOUT<sub>2</sub>

# **Analog Outputs**

The received PCM data is digitally processed and converted to an analog signal at the VOUT pin.  $VOUT_1$  is the output from Channel 1 and  $VOUT_2$  is the output for Channel 2. These outputs can directly drive a transformer SLIC.

## Power supply for the Am79C02:

| AGND <sub>1</sub> | Analog Ground (Channel 1)            |

|-------------------|--------------------------------------|

| AGND <sub>2</sub> | Analog Ground (Channel 2)            |

| DGND <sub>1</sub> | Digital Ground (Channel 1)           |

| DGND <sub>2</sub> | Digital Ground (Channel 2)           |

| PGND              | PCM I/O Ground                       |

| VCCA <sub>1</sub> | +5 V Analog Power Supply (Channel 1) |

| VCCA <sub>2</sub> | +5 V Analog Power Supply (Channel 2) |

| VCCD <sub>1</sub> | +5 V Digital Power Supply            |

|                   | Internally connected to substrate    |

VCCD<sub>2</sub> +5 V Digital Power Supply

Internally connected to substrate

VCCP +5 V PCM I/O Power Supply

Internally connected to substrate

VEE<sub>1</sub> -5 V Power Supply (Channel 1) VEE<sub>2</sub> -5 V Power Supply (Channel 2)

# Power supply for the Am79C03 and Am79C031:

AGND Analog Ground

DGND Digital Ground

VCCA +5 V Analog Power Supply

VCCD +5 V Digital Power Supply

Internally connected to substrate

VEE<sub>1</sub> –5 V Power Supply (Channel 1)

VEE<sub>2</sub> –5 V Power Supply (Channel 2)

The many separate power supply inputs are intended to provide for good power supply decoupling techniques. Note that all of the +5 V inputs should be connected to the same source, all of the ground inputs should be connected to the same source, and both of the -5 V inputs should be connected to the same source.

#### **FUNCTIONAL DESCRIPTION**

The DSLAC device performs the codec/filter functions associated with the four-wire section of the subscriber line circuitry in a digital switch. These functions involve converting an analog voice signal into digital PCM samples and converting digital PCM samples back into an analog signal. During conversion, digital filters are used to bandlimit the voice signals.

Independent channels allow the DSLAC device to function as two SLAC™ devices. All of the digital filtering is performed in digital signal processors operating from either a 2.048 MHz or 4.096 MHz external clock. The A/D, D/A, and signal processing is separate for each channel and each channel has its own Chip Select (CS1 and CS2) to allow separate programming.

The user-programmable filters set the receive and transmit gain, perform the transhybrid balancing function, permit adjustment of the two-wire termination impedance, and provide equalization of the receive and transmit paths. All programmable digital filter coefficients can be calculated using the AmSLAC2 software. The PCM codes can be either 8-bit companded A-law or  $\mu$ -law. The PCM data is read and written to the PCM highway in user-programmable time slots at rates of 128 kHz to 8.192 MHz. The output hold time and the transmit clock edge can be selected for compatibility with other devices that can be connected to the PCM highway.

Four configurations of the DSLAC device are offered with the PCM interface described above. The Am79C02(A), the original version of the DSLAC device, is available in the 44-pin PLCC package. The Am79C03(A) and Am79C031(A) are reduced pin count versions obtained by consolidating a number of ground and power supply buses on chip, and eliminating the hardware reset function. The Am79C03(A) is available in both 32-pin plastic DIP and 32-pin PLCC packages. The Am79C031(A) is available in a 32-pin PLCC package. The "A" version of both devices (e.g., Am79C02A) offers the adaptive transhybrid balance feature described in the Adaptive B Filter overview.

# **ABSOLUTE MAXIMUM RATINGS**

| Storage temperature $-60 ^{\circ}\text{C} \le T_{A} \le +125 ^{\circ}\text{C}$ |

|--------------------------------------------------------------------------------|

| Ambient operating temperature–40 $^{\circ}C \! \leq T_{A} \leq +85  ^{\circ}C$ |

| Ambient relative humidity 5% to 100%                                           |

| (noncondensing)                                                                |

| $V_{CCA}$ with respect to AGND0.4 V to +7.0 V                                  |

| $V_{CCD}$ with respect to DGND0.4 V to +7.0 V                                  |

| $V_{CCP}$ with respect to PGND0.4 V to +7.0 V                                  |

| $V_{\mbox{\footnotesize EE}}$ with respect to AGND +0.4 V to -7.0 V            |

| $V_{\mbox{\scriptsize IN}}$ with respect to VCCA +0.4 V to -10.0 V             |

| $(V_{EE} = -5 V)$                                                              |

| $V_{\text{IN}}$ with respect to $V_{\text{EE}}$ –0.4 V to +10.0 V              |

| $(V_{CCA} = +5 V)$                                                             |

| Other pins with respect to $DGND_1 \ldots -0.4 \; V$ to $V_{CC}$               |

| Total combined C1–C5 current per channel:                                      |

| Source from VCC 32 mA                                                          |

| Sink into DGND 24 mA                                                           |

| Latch-up immunity (any pin) ±30 mA                                             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

# **OPERATING RANGES Commercial (C) Devices**

| Analog supply +5.0 V ±5%                                                                 |

|------------------------------------------------------------------------------------------|

| VCCA <sub>1</sub> , VCCA <sub>2</sub> , or VCCA                                          |

| Digital supply +5.0 V ±5%                                                                |

| V <sub>CCP</sub> VCCD <sub>1</sub> , VCCD <sub>2</sub> , or VCCD                         |

| Analog supply VEE <sub>1</sub> , VEE <sub>2</sub> –5.0 V $\pm 5\%$                       |

| PGND, $DGND_1$ , $DGND_2$ , or $DGND$ 0 V                                                |

| $AGND_1,AGND_2,orAGND\dots\dots\dots\dots\pm 50mV$                                       |

| Ambient temperature $\dots\dots\dots0^{\circ}$ $C\!\leq T_{A} \leq +70^{\circ}C^{\star}$ |

| Ambient relative humidity 15% to 85%                                                     |

Operating Ranges define those limits between which the functionality of the device is guaranteed.

<sup>\*</sup> Functionality of the device from  $0^{\circ}C$  to  $+70^{\circ}C$  is guaranteed by production testing. Performance from  $-40^{\circ}C$  to  $+85^{\circ}C$  is guaranteed by characterization and periodic sampling of production units.

# **ELECTRICAL CHARACTERISTICS over operating range unless otherwise noted**

Typical values are for  $T_A = 25$  °C and nominal supply voltages. Minimum and maximum specifications are over the temperature and supply voltage ranges shown in Operating Ranges.

| Symbol                             | Parameter Descriptions                                                                                                                                                    | Min                                                   | Тур                 | Max                      | Unit | Note        |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|--------------------------|------|-------------|

| V <sub>IL</sub>                    | Input Low voltage                                                                                                                                                         | -0.5                                                  |                     | 0.8                      | ,,   |             |

| V <sub>IH</sub>                    | Input High voltage                                                                                                                                                        | 2.0                                                   |                     | V <sub>CC</sub>          | \    |             |

| I <sub>IL</sub>                    | Input leakage current                                                                                                                                                     |                                                       |                     | ±10                      | μА   |             |

| V <sub>OL</sub>                    | Output Low voltage  C1-C5 (I <sub>OL</sub> = 6 mA)  C1-C5 (I <sub>OL</sub> = 15 mA)  TSCA, TSCB (I <sub>OL</sub> = 14 mA)  Other digital outputs (I <sub>OL</sub> = 2 mA) |                                                       |                     | 0.4<br>1.0<br>0.4<br>0.4 | V    | 2<br>2<br>— |

| V <sub>OH</sub>                    | Output High voltage<br>C1–C5 ( $I_{OH}$ = 4 mA)<br>C1–C5 ( $I_{OH}$ = 10 mA)<br>Other digital outputs ( $I_{OH}$ = 400 $\mu$ A)                                           | V <sub>CC</sub> - 0.4<br>V <sub>CC</sub> - 1.0<br>2.4 |                     |                          |      | 2<br>2<br>— |

| l <sub>OL</sub>                    | Output leakage current (HI-Z State)                                                                                                                                       |                                                       |                     | ±10                      | μΑ   |             |

| $V_{IR}$                           | Analog input voltage range (AX = 0 dB) (AX = 6.02 dB)                                                                                                                     |                                                       |                     | ±3.12<br>±1.56           | V    |             |

| V <sub>IOS</sub>                   | Offset voltage allowed on V <sub>IN</sub>                                                                                                                                 |                                                       |                     | ±160                     | mV   |             |

| I <sub>IL</sub> (V <sub>IL</sub> ) | Input leakage current on V <sub>IN</sub>                                                                                                                                  |                                                       |                     | ±10                      | μΑ   |             |

| $Z_{IN}$                           | Analog input impedance 300 Hz to 3400 Hz                                                                                                                                  | 5                                                     |                     |                          | МΩ   |             |

| Z <sub>OUT</sub>                   | V <sub>OUT</sub> output impedance                                                                                                                                         |                                                       | 1                   | 10                       | Ω    |             |

| l <sub>OUT</sub>                   | V <sub>OUT</sub> output current (f < 3400 Hz)                                                                                                                             |                                                       |                     | ±6.3                     | mA   | 1           |

| V <sub>OR</sub>                    | $V_{OUT}$ voltage range (AR = 0 dB) (AR = 6.02 dB)                                                                                                                        |                                                       |                     | ±3.12<br>±1.56           | V    |             |

| V <sub>oos</sub>                   | V <sub>OUT</sub> offset voltage (AISN off)                                                                                                                                |                                                       |                     | ±40                      | mV   |             |

| V <sub>OOSA</sub>                  | V <sub>OUT</sub> offset voltage (AISN on)                                                                                                                                 |                                                       |                     | ±80                      | 1114 | 3           |

| LIN <sub>AISN</sub>                | Linearity of AISN circuity (input = 0 dBm0)                                                                                                                               |                                                       |                     | ±1/4                     | LSB  |             |

| PD                                 | Power dissipation Both channels active (MCLK, PCLK = 2.048 MHz) 1 channel active Both channels inactive                                                                   |                                                       | 180<br>120<br>10    | 240<br>160<br>19         | m\A/ | _<br>_<br>4 |

| PD                                 | Power dissipation Both channels active (MCLK, PCLK > 2.048 MHz) 1 channel active Both channels inactive                                                                   |                                                       | 190<br>130<br>10    | 270<br>175<br>19         | - mW |             |

| lcc                                | Total +5 V current  Both channels active 1 channel active Both channels inactive                                                                                          |                                                       | 24.0<br>18.0<br>2.5 |                          | mΛ   | <br><br>4   |

| I <sub>EE</sub>                    | Total –5 V current  Both channels active 1 channel active Both channels inactive                                                                                          |                                                       | 10.0<br>5.0<br>0.05 |                          | - mA |             |

| CI                                 | Input capacitance (Digital)                                                                                                                                               |                                                       | 15                  |                          | pF   |             |

| C <sub>O</sub>                     | Output capacitance (Digital)                                                                                                                                              |                                                       | 15                  |                          | Pi   |             |

| PSRR                               | Power supply rejection ratio (1.02 kHz, 100 mVrms, either supply or path, GX = GR = 0 dB)                                                                                 | 40                                                    |                     |                          | dB   |             |

#### Notes:

- 1. When the DSLAC device is in the Inactive mode, the analog output presents a 0 V output level through a  $\sim$ 3 k $\Omega$  resistor.

- 2. The C1-C5 outputs are resistive for less than a 1 V drop. Total current must not exceed absolute maximum ratings.

- 3. If there is an external DC path from  $V_{OUT}$  to  $V_{IN}$  with a gain of GDC and the AISN has a gain of  $h_{AISN}$ , then the output offset is multiplied by  $1/[1 (h_{AISN} \cdot GDC)]$ .

- 4. Power Dissipation in the Inactive mode is measured with all digital inputs at  $V_{IH} = V_{CC}$  and  $V_{IL} = V_{SS}$  and with no load connected to  $VOUT_1$  or  $VOUT_2$ .

#### **Transmission Characteristics**

The gain of the receive path is defined to be 0 dB when a 0 dBm0, 1014 Hz PCM sine wave input results in a nominal 1.55 Vrms for  $\mu$ -law or 1.56 Vrms for A-law analog output. The gain of the transmit path is 0 dB when a 1.55 Vrms for  $\mu$ -law or 1.56 Vrms for A-law, 1014 Hz sine wave analog input results in a level of 0 dBm0 at the digital output.

When relative levels (dBm0) are used in any of the following transmission specifications, the specification holds for any setting of the AX + GX gain from 0 to 12 dB and the AR + GR loss from 0 to 12 dB. Performance specification for settings of the AX + GX gain from 12 to 18 dB and the AR + GR loss from 12 to 18 dB is determined as the device is characterized.

| Description                                                | Test Condit                                                                                                                                      | ions                                                       | Min                              | Тур | Max                                  | Unit                                                 | Note                      |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------|-----|--------------------------------------|------------------------------------------------------|---------------------------|

| Gain accuracy<br>D to A or A to D                          | 0 dBm0, 1014 Hz<br>0 dB <  path gain  < 6 dB                                                                                                     | 25°C to 85°C<br>0°C<br>–40°C                               | -0.20<br>-0.25<br>-0.35          |     | +0.20<br>+0.25<br>+0.35              |                                                      |                           |

| Gain accuracy<br>D to A or A to D                          | 0 dBm0, 1014 Hz<br>6 dB <  path gain  < 12 dB                                                                                                    | 70°C to 85°C<br>25°C<br>0°C<br>–40°C                       | -0.20<br>-0.25<br>-0.30<br>-0.35 |     | +0.20<br>+0.25<br>+0.30<br>+0.35     |                                                      | 1<br>1<br>1               |

| Gain accuracy<br>analog to analog<br>or digital to digital |                                                                                                                                                  | 25°C to 85°C<br>0°C<br>–40°C                               | -0.20<br>-0.25<br>-0.35          |     | +0.20<br>+0.25<br>+0.35              | dB                                                   |                           |

| Attenuation distortion                                     |                                                                                                                                                  | 300 Hz to 3400 Hz                                          | -0.125                           |     | +0.125                               |                                                      | 2                         |

| Single frequency distortion, A to D                        |                                                                                                                                                  |                                                            |                                  |     | -46                                  |                                                      | 3                         |

| Single frequency distortion, D to A                        | -6 dB < (GR + AR) < 0 dB<br>-12 dB < (GR + AR) < -6 dB | 25°C<br>0°C                                                |                                  |     | -46<br>-46<br>-45<br>-43<br>-40      |                                                      | 3<br>3, 4<br>3, 4<br>3, 4 |

| Intermodulation distortion                                 |                                                                                                                                                  |                                                            |                                  |     | -42<br>-56                           | dBr                                                  | 5                         |

| Analog out Idle channel noise Digital out                  | digital looped back digital input = 0 analog V <sub>IN</sub> = 0                                                                                 | weighted<br>unweighted<br>A-law<br>µ-law<br>A-law<br>µ-law |                                  |     | -68<br>-55<br>-78<br>12<br>-68<br>19 | dBm0p<br>dBm0p<br>dBm0p<br>dBrnc0<br>dBm0p<br>dBrnc0 | 6                         |

| Crosstalk TX to RX same channel RX to TX                   | 0 dBm0                                                                                                                                           | 300 Hz to 3400 Hz                                          |                                  |     | –75<br>–75                           |                                                      |                           |

| Crosstalk TX to TX between channels RX to TX RX to RX      | 0 dBm0                                                                                                                                           | 300 Hz to 3400 Hz                                          |                                  |     | -76<br>-78<br>-76<br>-78             |                                                      |                           |

| Group delay PCLK ≥ 1.53 MHz<br>PCLK ≤ 1.03 MHz             | B, X, R, and Z filters disabled                                                                                                                  |                                                            |                                  |     | 630<br>695                           | μs                                                   | 7                         |

#### Notes.

- 1. AMD guarantees less than 0.1% of units fall into the last 0.05 dB of these specification numbers.

- 2. See Figure 1.

- 3. With f swept between 0 to 300 Hz and 3400 to 12 kHz, any generated output signals other than f are less than –28 dBm0. This specification is valid for either transmission path.

- 4. AMD guarantees < 0.2% of units are above -46 dB. This relaxed specification applies to only the third harmonic.

- 5. Intermodulation distortion specification for two signals of same level in the range of –4 dBm0 to –21 dBm0 does not produce 2 (f1 f2) component above specified level. 50 Hz IMD specified with 50 Hz signal at –23 dBm0 and signal between 300 Hz to 3400 Hz at –9 dBm0.

- 6. No single frequency component in the range above 3800 Hz may exceed a level of -55 dBm0.

- 7. The Group Delay specification is defined as the sum of the minimum values of the group delays for the transmit and the receive paths when the transmit and receive time slots are identical and the B, X, R, and Z filters are disabled. For PCLK frequencies between 1.03 MHz and 1.53 MHz, the group delay may vary from one cycle to the next. See Figure 2.

# **Group Delay Distortion**

For either transmission path, the group delay distortion is within the limits shown in Figure 2. The minimum value of the group delay is taken as the reference. The signal level should be 0 dBm0.

# Variation of Gain with Input Level

The gain deviation relative to the gain at -10 dBm0 is within the limits shown if Figure 3 for either transmission path when the input is a sine wave signal of frequency 1014 Hz.

Figure 3. Gain Tracking with Tone Input\*

# **Total Distortion, Including Quantizing Distortion**

The signal-to-total distortion exceeds the limits shown in Figure 4 for either transmission path when the input is a sine wave signal of frequency 1014 Hz.

Figure 4. Total Distortion with Tone Input (Both Paths)

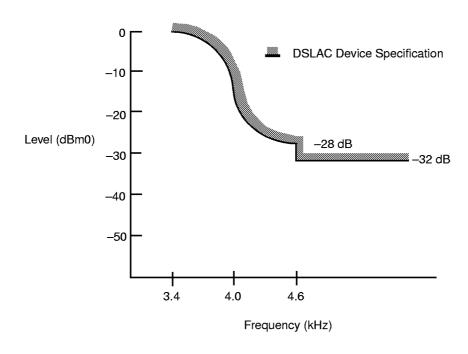

# **Discrimination against Out-of-Band Input Signals**

When an out-of-band sine wave signal with frequency f and level A is applied to the analog input, there may be frequency components below 4 kHz at the digital output, caused by the out-of-band signal. These components are at least the specified dB level below the level of a signal at the same output originating from a 1014 Hz sine wave signal with a level of A dBm0 also applied to the analog input. The minimum specifications are shown in Figure 5.

| Frequency of Out-of-Band Signal | Amplitude of Out-of-Band Signal | Level below A |

|---------------------------------|---------------------------------|---------------|

| 16.6 Hz < f < 45 Hz             | –25 dBm0 < A ≤ 0 dBm0           | 18 dB         |

| 45 Hz < f < 65 Hz               | –25 dBm0 < A ≤ 0 dBm0           | 25 dB         |

| 65 Hz < f < 100 Hz              | –25 dBm0 < A ≤ 0 dBm0           | 10 dB         |

| 3400 Hz < f < 4600 Hz           | -25 dBm0 < A ≤ 0 dBm0           | see Figure 5  |

| 4600 Hz < f < 100 kHz           | -25 dBm0 < A ≤ 0 dBm0           | 32 dB         |

#### Note:

The attenuation of the waveform below amplitude A between 3400 Hz and 4600 Hz is given by the formula:

Attenuation (dB) =

$$14 - 14 \sin \frac{\pi (4000 - f)}{1200}$$

Figure 5. Discrimination against Out-of-Band Signals

# Discrimination against 12 kHz and 16 kHz Metering Signals

If the DSLAC device is used in a metering application where 12 kHz or 16 kHz tone bursts are injected onto the telephone line toward the subscriber, a portion of those tones also may appear at the  $V_{\rm IN}$  terminal. These out-of-band signals may cause frequency components to appear below 4 kHz at the digital output. For a 12 kHz tone, the frequency components below 4 kHz are reduced from the input by at least 48 dB, and for 16 kHz tones, the components are reduced by more than 70 dB.

To avoid degradation of in-band transmission performance, the input levels of these out-of-band tones must be limited. The maximum allowable level is 100 mVrms at 12 kHz, and is 500 mVrms at 16 kHz. An external notch filter at the VIN pin of the DSLAC device, incorporated with the metering injection design, is effective in reducing these tone levels.

# Spurious Out-of-Band Signals at the Analog Output

With PCM code words representing a sine wave signal in the range of 300 Hz to 3400 Hz at a level of 0 dBm0 applied to the digital input, the level of the spurious out-of-band signals at the analog output is less than the limits shown in the following table.

| Frequency         | Level    |

|-------------------|----------|

| 4.6 kHz to 40 kHz | –32 dBm0 |

| 40 kHz to 240 kHz | –46 dBm0 |

| 240 kHz to 1 MHz  | –36 dBm0 |

With code words representing any sine wave signal in the range 3.4 kHz to 4.0 kHz at a level of 0 dBm0 applied to the digital input, the level of the signals at the analog output are below the limits in Figure 6. The amplitude of the spurious out-of-band signals between 3400 Hz and 4600 Hz is given by the formula:

$$A = -14 - 14 \sin \frac{\pi(f - 4000)}{1200} dBm0$$

09875H-010

Figure 6. Spurious Out-of-Band Signals

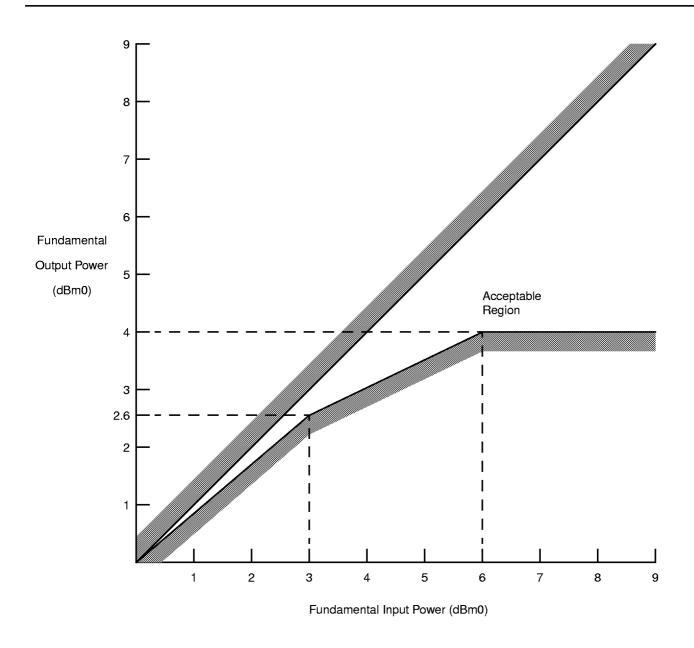

# **Overload Compression**

Figure 7 shows the acceptable region of operation for input signal levels above the reference input power (0 dBm0). The conditions for this figure are: (1) 1 dB < GX  $\leq$  12 dB; (2) -12 dB  $\leq$  GR < -1 dB; (3) PCM output connected to PCM input; and (4) measurement analog-to-analog.

09875H-011

Figure 7. A/A Overload Compression

# **SWITCHING CHARACTERISTICS** over operating range unless otherwise noted Microprocessor Interface

Min and max values are valid for all digital outputs with a 150 pF load, except C1–C5 with a 30 pF load. Pull-up resistors of 360  $\Omega$  are attached to  $\overline{\text{TSCA}}$  and  $\overline{\text{TSCB}}$ .

| No. | Symbol            | Parameter                                  | Min | Тур               | Max                   | Units |

|-----|-------------------|--------------------------------------------|-----|-------------------|-----------------------|-------|

| 1   | t <sub>DCY</sub>  | Data Clock Period                          | 244 |                   |                       |       |

| 2   | t <sub>DCH</sub>  | Data Clock High Pulse Width (Note 1)       | 97  |                   |                       |       |

| 3   | t <sub>DCL</sub>  | Data Clock Low Pulse Width (Note 1)        | 97  |                   |                       |       |

| 4   | t <sub>DCR</sub>  | Rise Time of Clock                         |     |                   | 25                    | ns    |

| 5   | t <sub>DCF</sub>  | Fall Time of Clock                         |     |                   | 25                    | 1115  |

| 6   | t <sub>ICSS</sub> | Chip Select Setup Time, Input Mode         | 70  |                   | t <sub>DCY</sub> - 10 |       |

| 7   | t <sub>ICSH</sub> | Chip Select Hold Time, Input Mode          | 0   |                   | t <sub>DCH</sub> - 20 |       |

| 8   | t <sub>ICSL</sub> | Chip Select Pulse Width, Input Mode        |     | 8t <sub>DCY</sub> |                       |       |

| 9   | t <sub>ICSO</sub> | Chip Select Off Time, Input Mode (Note 7)  |     | 5                 |                       | μs    |

| 10  | t <sub>IDS</sub>  | Input Data Setup Time                      | 30  |                   |                       |       |

| 11  | t <sub>IDH</sub>  | Input Data Hold Time                       | 30  |                   |                       |       |

| 12  | t <sub>OLH</sub>  | SLIC Output Latch Valid                    | 20  |                   | 1000                  | ns    |

| 13  | tocss             | Chip Select Setup Time, Output Mode        | 70  |                   | t <sub>DCY</sub> – 10 | ] 113 |

| 14  | t <sub>OCSH</sub> | Chip Select Hold Time, Output Mode         | 0   |                   | t <sub>DCH</sub> – 20 |       |

| 15  | t <sub>OCSL</sub> | Chip Select Pulse Width, Output Mode       |     | 8t <sub>DCY</sub> |                       |       |

| 16  | tocso             | Chip Select Off Time, Output Mode (Note 7) |     | 5                 |                       | μs    |

| 17  | t <sub>ODD</sub>  | Output Data Turn On Delay (Note 5)         |     |                   | 50                    |       |

| 18  | t <sub>ODH</sub>  | Output Data Hold Time                      | 0   |                   |                       | ns    |

| 19  | t <sub>ODOF</sub> | Output Data Turn Off Delay                 |     |                   | 50                    |       |

| 20  | t <sub>ODC</sub>  | Output Data Valid                          | 0   |                   | 50                    |       |

# **PCM** Interface

PCLK not to exceed 4.096 MHz when PCM delay is used.

| No. | Symbol           | Parameter                                                           | Min     | Тур | Max                   | Units |

|-----|------------------|---------------------------------------------------------------------|---------|-----|-----------------------|-------|

| 21  | t <sub>PCY</sub> | PCM Clock Period (Note 2)                                           | 0.122   |     | 7.8125                | μs    |

| 22  | t <sub>PCH</sub> | PCM Clock High Pulse Width                                          | 48      |     | 3890                  |       |

| 23  | t <sub>PCL</sub> | PCM Clock Low Pulse Width                                           | 48      |     | 3890                  |       |

| 24  | t <sub>PCF</sub> | Fall Time of Clock                                                  |         |     | 15                    |       |

| 25  | t <sub>PCR</sub> | Rise Time of Clock                                                  |         |     | 15                    |       |

| 26  | t <sub>FSS</sub> | FS Setup Time                                                       | 25      |     | t <sub>PCY</sub> - 50 |       |

| 27  | t <sub>FSH</sub> | FS Hold Time                                                        | 50      |     |                       |       |

| 28  | t <sub>TSD</sub> | Delay to TSC Valid (with Programmable Delay) (Note 3)               | 5<br>30 |     | 80<br>150             |       |

| 29  | t <sub>TSO</sub> | Delay to TSC Off (with Programmable Delay) (Note 6)                 | 5<br>30 |     | 80<br>150             | ns    |

| 30  | t <sub>DXD</sub> | PCM Data Output Delay<br>(with Programmable Delay) (Note 4)         | 3<br>30 |     | 80<br>150             |       |

| 31  | t <sub>DXH</sub> | PCM Data Output Hold Time<br>(with Programmable Delay) (Note 4)     | 5<br>30 |     | 80<br>150             |       |

| 32  | t <sub>DXZ</sub> | PCM Data Output Delay to HI-Z<br>(with Programmable Delay) (Note 4) | 5<br>30 |     | 80<br>150             |       |

| 33  | t <sub>DRS</sub> | PCM Data Input Setup Time                                           | 25      |     |                       |       |

| 34  | t <sub>DRH</sub> | PCM Data Input Hold Time                                            | 5       |     |                       |       |

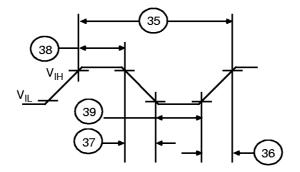

#### **Master Clock**

For 2.048 MHz ±100 ppm or 4.096 MHz ±100 ppm operation:

| No. | Symbol           | Parameter                         | Min    | Тур    | Max    | Units |

|-----|------------------|-----------------------------------|--------|--------|--------|-------|

| 35  | t <sub>MCY</sub> | Master Clock Period (2.048 MHz)   | 488.23 | 488.28 | 488.33 |       |

|     |                  | Master Clock Period (4.096 MHz)   | 244.11 | 244.14 | 244.17 |       |

| 36  | t <sub>MCR</sub> | Rise Time of Clock                |        | 15     |        |       |

| 37  | t <sub>MCF</sub> | Fall Time of Clock                |        |        | 15     | ns    |

| 38  | t <sub>MCH</sub> | MCLK High Pulse Width (2.048 MHz) | 200    |        |        | 115   |

|     |                  | MCLK High Pulse Width (4.096 MHz) | 80     |        |        |       |

| 39  | t <sub>MCL</sub> | MCLK Low Pulse Width (2.048 MHz)  | 200    |        |        |       |

|     |                  | MCLK Low Pulse Width (4.096 MHz)  | 80     |        |        |       |

#### Notes:

- 1. DCLK may be stopped in the High or Low state indefinitely without loss of information. If  $\overline{CS}$  makes a transition to the Low state, the last byte received is interpreted by the Microprocessor Interface logic.

- 2. The PCM clock (PCLK) frequency must be an integer multiple of the frame sync (FS) frequency with an accuracy of 800 ppm relative to the MCLK frequency. This allowance includes any jitter that may occur between the PCM signals (FS, PCLK) and MCLK. The actual PCLK rate is dependent on the number of channels allocated within a frame. The DSLAC supports 2–128 channels. A PCLK of 1.544 MHz can be used for standard US transmission systems. The minimum clock frequency is 128 kHz.

- 3. TSC is delayed from FS by a typical value of N t<sub>PCY</sub>, where N is the value stored in the time/clock-slot register.

- 4. There is a special conflict detection circuitry that prevents high-power dissipation from occurring when the DXA or DXB pins of two DSLAC devices are tied together and one DSLAC device starts to transmit before the other has gone into a high-impedance state.

- 5. The first data bit is enabled on the falling edge of  $\overline{CS}$  or on the falling edge of DCLK, whichever occurs last.

- 6.  $t_{TSO}$  is defined as the time at which the output achieves the open circuit condition.

- The DSLAC device requires 40 cycles of the 8 MHz internal clock (5 μs) between SIO operations. If the MPI is being accessed

while the MCLK input is not active, a Chip Select Off time of 20 μs is required.

#### **SWITCHING WAVEFORMS**

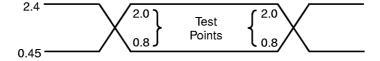

# Input and Output Waveforms for AC Tests

09875H-012

# **Master Clock Timing**

09875H-013

# **Microprocessor Interface (Input Mode)**

# **Microprocessor Interface (Output Mode)**

# **PCM** Highway Timing for XE = 0 (Transmit on Negative PCLK Edge)

09875H-016

# **PCM** Highway Timing for XE = 1 (Transmit on Positive PCLK Edge)

09875H-017

#### Note:

In this mode, the PCM transmit timing is compatible with other CODEC IC's.

# Operating the DSLAC Device

The following describes the operation of either channel of the DSLAC device. The description is valid for either Channel 1 or 2. VIN in this data sheet refers to either  $VIN_1$  or  $VIN_2$ , VOUT refers to either  $VOUT_1$  or  $VOUT_2$ , and  $\overline{CS}$  refers to either  $\overline{CS1}$  or  $\overline{CS2}$ .

#### Power-Up Sequence from $V_{CC} = 0 \text{ V}$

The recommended power-up sequence is to apply:

- 1. Power supply grounds

- 2.  $V_{CC}/V_{FF}$

- 3. Signal connections

- 4. Hardware Reset (02 only)

The software initialization should then include:

- 1. Select MCLK (Command 6)

- 2. Software Reset (Command 2)

- 3. Program filter coefficients and other parameters

- 4. Activate (Command 5)

Software initialization of the DSLAC device should always follow any power-up or hardware reset.

Upon initial application of power, a minimum of 1 ms is needed before  $\overline{CS1}$  or  $\overline{CS2}$  may go Low and an MPI command initiated. If the power supply (VCCD<sub>1</sub> or VCCD<sub>2</sub>) falls below approximately 2.0 V, the device is reset and requires complete reprogramming with the above sequence. Bit 7 of the SLIC Direction Register reads back as a logical 1 to indicate that a power interruption has been detected. This bit is cleared when a software reset command is sent to the DSLAC device. The RST pin may be tied to +5 V if it is not needed in the system (Am79C02 only).

#### **Active Mode**

Each channel of the DSLAC device can operate in either the Active (operational) or Inactive (standby) mode. In the Active mode, the DSLAC device is able to transmit and receive PCM and analog information. This is the normal operating mode when a telephone call is in progress. The Activate command, Microprocessor Interface (MPI) Command 5, puts the device into this state. Bringing the DSLAC device into the Active mode is possible only through the MPI.

#### **Inactive Mode**

The DSLAC device is forced into the Inactive (standby) mode after a powerup, hardware or software reset, or is programmed into this mode by the Deactivate command (Command 1). Power is switched off from all non-essential circuitry, though the MPI remains active to receive new commands. The analog output is tied to ground through an approximate 3 k $\Omega$  resistor. All circuits, which contain programmed information, retain their data in the Inactive mode.

#### **Reset State**

An active Low, hardware Reset pin (RST) is available on the Am79C02, which resets the device to the following default state. (For the Am79C02, Am79C03, and Am79C031, when power is first applied, an internal power-up reset puts the device into the following default state.)

- 1. A-law is selected

- 2. B, X, R, and Z filters disabled; AISN gain is zero.

- Digital (GX and GR) gain blocks are disabled, resulting in unity gain, and analog (AX and AR) gains are set to unity.

- 4. SLIC input/output direction is set to the Input mode.

- 5. Normal conditions are selected (see Command 4).

- 6. The B-filter Adaptive mode is turned off.

- 7. Both channels placed in Inactive (standby) mode.

- 8. Transmit time, receive time, and clock slots are set to zero.

- 9. DXA/DRA ports are selected for Channel 1.

- 10. DXB/DRB ports are selected for Channel 2.

**Note:** Must be reassigned to DXA/DRA for Am79C031.

- 11. MCLK is selected to be 4.096 MHz.

- 12. Transmit on the negative edge of PCLK. (XE = 0)

- 13. PCM Delay is inserted.

Reset states 1 to 7 are identical to those of the software reset (Command 2). The software reset command affects only those channels that have their CS asserted.

# Signal Processing

### **Overview of Digital Filters**

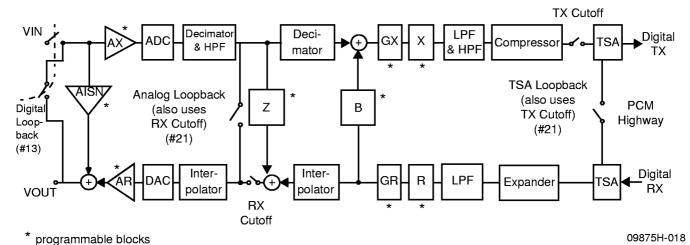

Several of the blocks in the signal processing section are user programmable. These allow the user to optimize the performance of the DSLAC device for the system. Figure 8 shows the DSLAC device signal processing and indicates the programmable blocks.

The advantages of digital filters are:

- High reliability

- No drift with time or temperature

- Unit-to-unit repeatability

- Superior transmission performance

#### **Two-Wire Impedance Matching**

Two feedback paths on the DSLAC device modify the effective two-wire input impedance of the SLIC by providing programmable feedback from  $V_{\text{IN}}$  to  $V_{\text{OUT}}$ . The Analog Impedance Scaling Network (AISN) is a programmable analog gain of -0.9375 to +0.935 from  $V_{\text{IN}}$  to  $V_{\text{OUT}}$ . The Z filter is a programmable digital filter, also connecting  $V_{\text{IN}}$  to  $V_{\text{OUT}}$ .

Figure 8. DSLAC Block Diagram

#### **Distortion Correction and Equalization**

The DSLAC device contains programmable filters in the receive (R) and transmit (X) directions that may be programmed for line equalization and to correct any attenuation distortion caused by the Z filter.

#### Transhybrid Balancing

The DSLAC device's programmable B filter is used to adjust transhybrid balance. The filter has a single pole IIR section (BIIR) and an eight tap FIR section (BFIR), both operating at 16 kHz. The DSLAC device has an optional Adaptive mode for the B filter, which may be used to achieve optimum performance. The Echo Path Gain (EPG) and Error Level Threshold (ELT) registers contain values that determine the Adaptive mode performance.

#### **Gain Adjustment**

The DSLAC device's transmit path has two programmable gain blocks. Gain block AX is an analog gain of 0 dB or 6.02 dB, located immediately before the A/D converter. Gain block GX is a digital gain that is programmable to any gain from 0 dB to 12 dB with a worst-case step size of 0.3 dB for gain settings above 10 dB. The filters provide a net gain in the range of 0 dB to 18 dB.

The DSLAC device receive path has two programmable loss blocks. Loss block GR is a digital loss that is programmable from 0 dB to 12 dB with a worst-case step size of 0.1 dB. Loss block AR is an analog loss of 0 dB or 6.02 dB, located immediately after the D/A converter. This provides a net loss in the range of 0 dB to 18 dB.

#### **Transmit Signal Processing**

In the transmit path, the analog input signal is A/D converted, filtered, companded (A-law or  $\mu$ -law), and made available for output to the PCM highway. The signal processor contains an ALU, RAM, ROM, and control logic to implement the filter sections. The B, X, and GX blocks

are user-programmable digital filter sections with coefficients stored in the coefficient RAM while AX is an analog amplifier that can be programmed for 0 dB or 6.02 dB gain. The filters may be made transparent when not required in a system.

The decimator reduces the high input sampling rate to 16 kHz for input to the B, GX, and X filters. The X filter is a six tap FIR section, which is part of the frequency response correction network. The B filter operates on samples from the receive signal path in order to provide transhybrid balancing in the loop. The high-pass filter rejects low frequencies such as 50 or 60 Hz and may be disabled.

#### **Transmit PCM Interface**

The transmit PCM interface receives an 8-bit compressed code from the digital A-law/ $\mu$ -law compressor. Transmit logic controls the transmission of data onto the PCM highway through output port selection and time/clock slot control circuitry.

The frame sync (FS) pulse identifies the beginning of a transmit frame and all channels (time slots) are referenced to it. The logic contains user programmable Transmit Time Slot and Transmit Clock Slot registers.

The Time Slot register is 7 bits wide and allows up to 128 8-bit channels (using a PCLK of 8.192 MHz) in each frame. This feature allows any clock frequency between 128 kHz and 8.192 MHz (2 to 128 channels) in a system. The Clock Slot register is 3 bits wide and may be programmed to offset the time slot assignment by 0 to 7 PCLK periods to eliminate any clock skew in the system. The data is transmitted in bytes with the most significant bit first.

An exception occurs when division of the PCLK frequency by 64 kHz produces a nonzero remainder, R (R =  $f_{PCLK}$  modulo 64 kHz, R > 0), and when the transmit clock slot is greater than R. In that case, the R-bit

fractional time slot after the last full time slot in the frame contains random information and has the TSC output turned on. For example, if the PCLK frequency is 1.544 MHz (R = 1) and the transmit clock slot is greater than 1, the 1-bit fractional time slot after the last full time slot in the frame contains random information, and the TSC output remains active during the fractional time slot. The data is transmitted in bytes, with the most significant bit first.

The PCM data may be user programmed for output onto either the DXA or DXB port. Correspondingly, either TSCA or TSCB is Low during transmission.

The DXA/DXB and TSCA/TSCB outputs can be programmed to change either on the negative or positive edge of PCLK. In the first case, an extra delay (PCM delay) in the timing of the DXA and DXB signals may be programmed to allow timing compatibility with other devices on the PCM highway.

# **Receive Signal Processing**

In the receive path, the digital signal is expanded, filtered, converted to analog, and passed to the VOUT pin. The signal processor contains an ALU, RAM, ROM, and control logic to implement the filter sections. The Z, R, and GR blocks are user-programmable filter sections with their coefficients stored in the coefficient RAM, while AR is an analog amplifier that can be programmed for a 0 dB or 6.02 dB loss. The filters may be made transparent when not required in a system.

The low-pass filter band limits the signal. The R filter is a six tap FIR section operating at a 16 kHz sampling rate and is part of the frequency response correction network. The Analog Impedance Scaling Network (AISN) is a user-programmable gain block providing feedback from  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  to emulate different ZSLIC impedances from a single external ZSLIC impedance. The Z filter provides feedback from the transmit signal path to the receive path and is used to modify the effective input impedance to the system. The interpolator increases the sampling rate prior to D/A conversion.

#### **Receive PCM Interface**

The receive PCM interface logic controls the reception of data bytes from the PCM highway, transfers the data to the A-law/ $\mu$ -law expansion logic, and then passes the data to the receive path of the signal processor. The frame sync (FS) pulse identifies the beginning of a receive frame, and all channels (time slots) are referenced to it.

The logic contains user-programmable Receive Time Slot and Receive Clock Slot registers. The Time Slot register is 7 bits wide and allows up to 128 8-bit channels (using a PCLK of 8.192 MHz) in each frame. This feature allows any clock frequency between 128 kHz and 8.192 MHz (2 to 128 channels) in a system. The Clock Slot register is 3 bits wide and may be pro-

grammed to offset the time slot assignment by 0 to 7 PCLK periods to eliminate any clock skews in the system. An exception occurs when division of the PCLK frequency by 64 kHz produces a nonzero remainder, R (R =  $f_{PCLK}$  modulo 64 kHz, R > 0) and when the receive clock slot is greater than R. In that case, the last receive time slot in the frame is not usable. For example, if the PCLK frequency is 1.544 MHz (R = 1), the receive clock slot can be only 0 or 1 if the last time slot is to be used. The PCM data may be user programmed for input from either the DRA or DRB port.

# **Analog Impedance Scaling Network (AISN)**

The AISN is incorporated in the DSLAC device to scale the value of the external ZSLIC impedance. Scaling this external impedance with the AISN (along with the Z filter) allows matching of many different line conditions using a single impedance value. Linecards may be designed for many different specifications without any hardware changes.

The AISN is a programmable gain that is connected across the DSLAC device input from  $V_{\text{IN}}$  to  $V_{\text{OUT}}$ . The gain can be varied from -0.9375 to +0.9375 in 31 steps of 0.0625. The AISN gain is given by the following equation:

$$h_{AISN} = 0.0625[(A2^4 + B2^3 + C2^2 + D2^1 + E2^0) - 16]$$

where A, B, C, D, and E = 1 or 0.

The AISN gain is used to alter the input impedance of the DSLAC device from the SLIC as given by:

$$Z_{IN} = Z_{SL} \frac{(1 - G_{44}h_{AISN})}{(1 - G_{440}h_{AISN})}$$

where  $G_{440}$  (defined as  $G_{24}$   $G_{42}$  +  $G_{44}$ ) is the echo gain into an open circuit and  $G_{44}$  is the echo gain into a short circuit.

There are two special cases to the formula for  $h_{AISN}$ : 1) value of ABCDE = 00000 specifies a gain of 0 (or cutoff), and 2) a value of ABCDE = 10000 is a special case where the AISN circuitry is disabled and the  $V_{OUT}$  pad is connected internally to  $V_{IN}$  with a gain of 0 dB. This allows a digital-to-digital Loopback mode wherein a digital PCM input signal is completely processed through the receive section all the way to the VOUT pin. The signal then is connected internally to  $V_{IN}$  where it is processed through the transmit section and output as digital PCM data.

### **Speech Coding**

The A/D and D/A conversion follows either the A-law or the  $\mu$ -law as they are defined in CCITT Rec. G.711. A-law or  $\mu$ -law operation is programmed using MPI Command 19. Alternate bit inversion is performed as part of the A-law coding.

# **Command Description and Formats**

#### **Microprocessor Interface Description**

A microprocessor may be used to program the DSLAC device and control its operation using the Microprocessor Interface (MPI). Data programmed previously may be read out for verification. For each channel, commands are provided to assign values to the following parameters.

- Transmit time slot

- Receive time slot

- Transmit clock slot

- Receive clock slot

- Transmit gain

- Receive loss

- B-filter coefficients

- X-filter coefficients

- R-filter coefficients

- Z-filter coefficients

- Adaptive B filter parameters

- AISN coefficient

- Read/Write SLIC Input/Output

- Select A-law or μ-law code

- Select Transmit PCM Port A or B

- Select Transmit PCM clock edge

- Select Transmit PCM delay

- Select Receive PCM Port A or B

- Enable/disable B filter

- Enable/disable Z filter

- Enable/disable X filter

- Enable/disable R filter

- Enable/disable GX filter

- Enable/disable GR filter

- Enable/disable AX amplifier

- Enable/disable AR amplifier

- Enable/disable adaptive B filter

- Select test modes

- Select Active or Inactive (standby) mode

The following description of the MPI is valid for either Channel 1 or 2. Whenever  $\overline{CS}$  is specified, it refers to either  $\overline{CS1}$  or  $\overline{CS2}$ . If desired, both channels may be programmed simultaneously with identical information by activating  $\overline{CS1}$  and  $\overline{CS2}$  at the same time. Commands that affect both channels simultaneously are noted as such.

The MPI consists of serial data input (DIN or DIO), output (DOUT or DIO), data clock (DCLK), and a separate chip select ( $\overline{CS1}$  and  $\overline{CS2}$ ) input for each channel. The serial input consists of 8-bit command words that may be followed with additional bytes of input data or may be followed by the DSLAC device sending out bytes of data. All data input and output is MSB (D7) first and LSB (D0) last. All data bytes are read or written one at a time, with  $\overline{CS}$  going High for at least the minimum off period before the next byte is read or written.

All commands that require additional input data to the device must have the input data as the next N words written into the device (for example, framed by the next N transitions of  $\overline{CS}$ ). All commands that are followed by output data causes the device to output data for the next N transitions of  $\overline{CS}$  going Low. The DSLAC device does not accept any input commands until all the data is shifted out. Unused bits in the data bytes are read out as zeros.

A command sequence to one channel must be finished before a command can be sent to the channel. The NOP Command 2 is recommended to follow any set of commands to the DSLAC device. The NOP is executed in the event of any anamolous  $\overline{\text{CS}}$  assertion.

An MPI cycle is defined by transitions of  $\overline{CS}$  and DCLK. If the CS lines are held in the High state between accesses, the DCLK may run continuously with no change to the internal control data. Using this method, the same DCLK may be run to a number of DSLAC devices and the individual  $\overline{\text{CS}}$  lines selects the appropriate device to access. Between command sequences, DCLK can stay in the High state indefinitely with no loss of internal control information regardless of any transitions on the CS lines. Between bytes of a multibyte read or write command sequence, DCLK also can stay in the High state indefinitely; however, each low-going transition of the CS line still advances the byte counter. DCLK can stay in the Low state indefinitely with no loss of internal control information, provided the  $\overline{\text{CS}}$  lines remain at a high level.

# Summary of MPI Commands\*\*

| C#  | Hex | Description                                                             |

|-----|-----|-------------------------------------------------------------------------|

| 1.  | 00  | Deactivate (Standby mode)                                               |

| 2.  | 02  | Reset                                                                   |

| 3.  | 06  | No Operation                                                            |

| 4.  | 08  | Reset to Normal Conditions                                              |

| 5.  | 0E  | Activate                                                                |

| 6.  | 1*  | MCLK Selection                                                          |

| 7.  | 40  | Write TX Time Slot & PCM Highway                                        |

| 8.  | 41  | Read TX Time Slot & PCM Highway                                         |

| 9.  | 42  | Write RX Time Slot & PCM Highway                                        |

| 10. | 43  | Read RX Time Slot & PCM Highway                                         |

| 11. | 44  | Write RX & TX Clock Slot and TX Edge                                    |

| 12. | 45  | Read RX & TX Clock Slot and TX Edge                                     |

| 13. | 50  | Write AISN, PCM delay, Analog Gains                                     |

| 14. | 51  | Read AISN, PCM delay, Analog Gains                                      |

| 15. | 52  | Write SLIC Input/Output Register                                        |

| 16. | 53  | Read SLIC Input/Output Register                                         |

| 17. | 54  | Write SLIC Input/Output Direction                                       |

| 18. | 55  | Read SLIC I/O Direction, Power<br>Interrupt Bit, and Channel Status Bit |

| 19. | 60  | Write Operating Functions                                               |

| 20. | 61  | Read Operating Functions                                                |

| 21. | 70  | Write Operating Conditions                                              |

| 22. | 71  | Read Operating Conditions                                               |

| 23. | 73  | Read Revision Code Number                                               |

| C#  | Hex | Description                     |

|-----|-----|---------------------------------|

| 24. | 80  | Write GX Filter Coefficients    |

| 25. | 81  | Read GX Filter Coefficients     |

| 26. | 82  | Write GR Filter Coefficients    |

| 27. | 83  | Read GR Filter Coefficients     |

| 28. | 84  | Write Z Filter Coefficients     |

| 29. | 85  | Read Z Filter Coefficients      |

| 30. | 86  | Write B Filter Coefficients     |

| 31. | 87  | Read B Filter Coefficients      |

| 32. | 88  | Write X Filter Coefficients     |

| 33. | 89  | Read X Filter Coefficients      |

| 34. | 8A  | Write R Filter Coefficients     |

| 35. | 8B  | Read R Filter Coefficients      |

| 36. | 8C  | Write Echo Path Gain            |

| 37. | 8D  | Read Echo Path Gain             |

| 38. | 8E  | Write Error Level Threshold     |

| 39. | 8F  | Read Error Level Threshold      |

| 40. | 92  | Write GZ Filter Coefficient     |

| 41. | 93  | Read GZ Filter Coefficient      |

| 42. | 90  | Write Adaptive B Filter Control |

| 43. | 91  | Read Adaptive B Filter Control  |

| 44. | 64  | Write Operating Functions II    |

| 45. | 65  | Read Operating Functions II     |

# Notes:

- 1. \*Code changes with function.

- 2. \*\*All codes not listed are reserved by AMD and should not be used.

#### **COMMAND STRUCTURE**

This section describes in detail each of the MPI commands. Each of the commands is shown along with the format of any additional data bytes that follow. For details of the filter coefficients of the for  $C_{xy}m_{xy}$ , please refer to the Description of Coefficients section.

#### 1. Deactivate (Standby State)

(00h)

|         | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|---------|----------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|

| Command | 0              | 0              | 0              | 0              | 0     | 0              | 0              | 0              |

During the Inactive state (of one or more channels):

- a) All of the programmed information is retained.

- b) The Microprocessor Interface (MPI) remains active.

- c) The PCM outputs are in high impedance and the PCM inputs are disabled.

- d) The analog output is tied to 2.1 V through an internal resistor ( $\sim$ 3 k $\Omega$ ).

#### 2. Software Reset

(02h)

|         | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|---------|----------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|

| Command | 0              | 0              | 0              | 0              | 0     | 0              | 1              | 0              |

The software reset state of the device is:

- a) The channel is placed in the Inactive (standby) mode.

- b) GX, GR, X, R, B, and Z filters are disabled with coefficients retained.

- c) AX and AR are set to unity and AISN gain is set to 0.

- d) The Adaptive B feature is disabled.

- e) A-law is selected.

- f) All SLIC I/O lines are configured as inputs.

- g) Normal conditions are selected (see Command 4).

### 3. No Operation

(06h)

|         | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|---------|----------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|

| Command | 0              | 0              | 0              | 0              | 0     | 1              | 1              | 0              |

#### 4. Reset to Normal Conditions

(08h)

|         | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|---------|----------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|

| Command | 0              | 0              | 0              | 0              | 1     | 0              | 0              | 0              |

Reset to Normal Conditions performs the following operations:

- a) Does not insert 6 dB loss in receive path.

- b) Receive and transmit paths are not cutoff.

- c) High-pass filter is enabled.

- d) Test modes are turned off.

#### 5. Activate (Operational State)

(0Eh)

|         | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|---------|----------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|

| Command | 0              | 0              | 0              | 0              | 1     | 1              | 1              | 0              |

This command places the device in the Active mode. No valid PCM data is transmitted until after the second FS pulse is received following the execution of the Activate command.

### 6. MCLK Selection

(10h/12h)

|         | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|---------|----------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|

| Command | 0              | 0              | 0              | 1              | 0     | 0              | Α              | 0              |

MCLK may be selected to operate from a 2.048 MHz or 4.096 MHz external clock. MCLK selection on either channel affects both channels.

A = 0: 2.048 MHz A = 1: 4.096 MHz

# 7. Write Transmit Time Slot and PCM Highway Selection

(40h)

|             | D <sub>7</sub> | $D_6$ | D <sub>5</sub> | $D_4$ | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|-------------|----------------|-------|----------------|-------|-------|----------------|----------------|----------------|

| Command     | 0              | 1     | 0              | 0     | 0     | 0              | 0              | 0              |

| Output Data | PCM            | TS    | TS             | TS    | TS    | TS             | TS             | TS             |

PCM = 0: Highway A PCM = 1: Highway B

TS: Time slot number 0 to 127

The PCM Highway B is not available on the Am79C031(A). The Transmit section of both channels must not be set to the same time slot on the same output port simultaneously.

# 8. Read Transmit Time Slot and PCM Highway Selection

(41h)

|             | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|-------------|----------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|

| Command     | 0              | 1              | 0              | 0              | 0     | 0              | 0              | 1              |

| Output Data | PCM            | TS             | TS             | TS             | TS    | TS             | TS             | TS             |

# 9. Write Receive Time Slot and PCM Highway Selection

(42h)

|             | D <sub>7</sub> | $D_6$ | D <sub>5</sub> | $D_4$ | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|-------------|----------------|-------|----------------|-------|-------|----------------|----------------|----------------|

| Command     | 0              | 1     | 0              | 0     | 0     | 0              | 1              | 0              |

| Output Data | PCM            | TS    | TS             | TS    | TS    | TS             | TS             | TS             |

PCM = 0: Highway A PCM = 1: Highway B

TS: Time slot number 0 to 127

The PCM Highway B is not available on the Am79C031(A).

# 10. Read Receive Time Slot and PCM Highway Selection

(43h)

|             | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|-------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Command     | 0              | 1              | 0              | 0              | 0              | 0              | 1              | 1              |

| Output Data | PCM            | TS             |