# D

## Am79C04(A)

### Advanced Micro Devices

## Dual Subscriber Line Audio-Processing Circuit (DSLAC™ Device)

#### DISTINCTIVE CHARACTERISTICS

- IOM 2 Interface

- -Control and PCM on one bus

- Data rate up to 4.096-MHz independent of master clock

- Two independent channels

- Software programmable

- SLIC impedance

- Trans-hybrid balance

- Transmit and receive gains

- Equalization

- Digital I/O pins with input debouncing

- m A-law or μ-law coding

- Adaptive trans-hybrid balance function (Am79C04/A only)

- 2.048- or 4.096-MHz master clock

- Simple interface to Am795XX series SLICs

- Direct transformer drive

- Built-in test modes

- Low-power CMOS

- Mixed mode (analog and digital) impedance scaling

- Performance characteristics guaranteed over 12-dB gain range

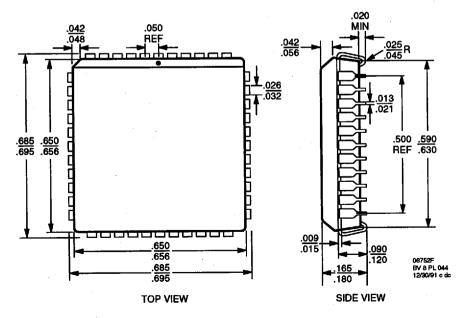

#### **BLOCK DIAGRAM**

This document contains information on a product under development at Advanced Micro Devices, Inc. The information is intended to help you evaluate this product. AMD reserves the right to change or discontinue work on this proposed product without notice.

Publication #: 12764 Rev. C Amendment /0 Issue Date: June 1992

#### **GENERAL DESCRIPTION**

The DSLAC IC is designed to be used in telecommunication linecards for both PBX and central office telephone exchanges. It converts the analog signal from the subscriber to digital PCM-encoded signals for transmission on the IOM 2 highway and converts a PCM-encoded signal received from an IOM 2 highway to an analog signal to be sent to the subscribers. The advanced architecture of the DSLAC device implements two independent channels and employs digital filters to allow software control of transmission parameters.

Advanced CMOS technology gives the economical DSLAC device both the functions and the low-power consumption needed by linecard designers to maximize linecard density at minimum cost. When used with two SLICs, the DSLAC device provides a complete dual-channel, software-configurable solution to the BORSCHT (Battery feed, Overvoltage protection, Ringing, Supervision, coding, Hybrid and Test) function.

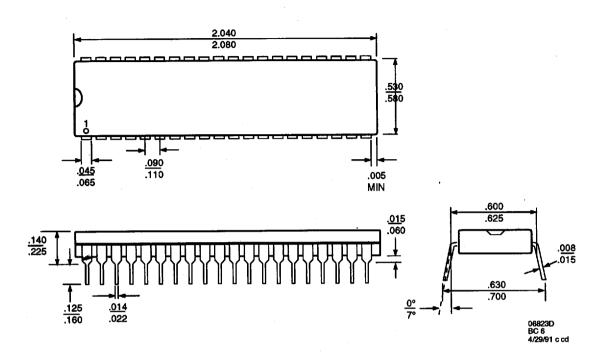

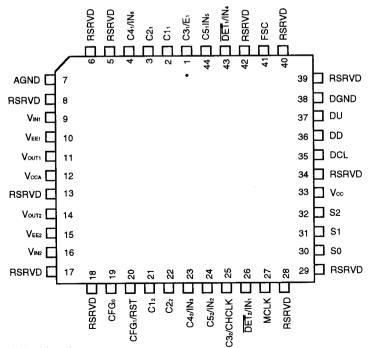

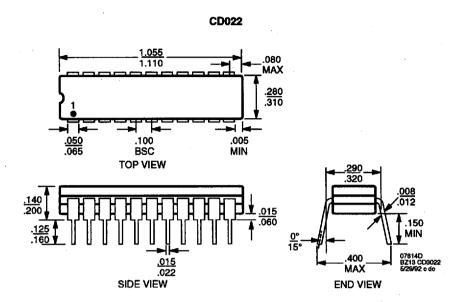

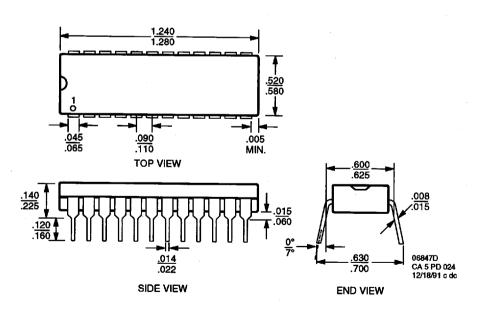

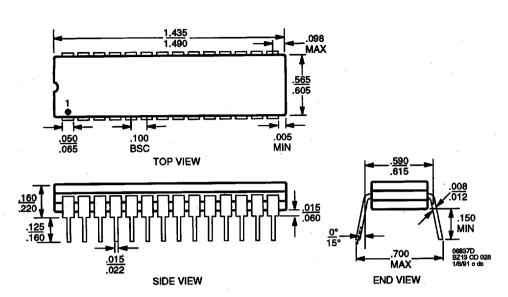

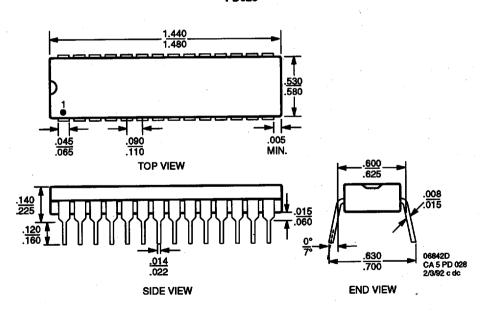

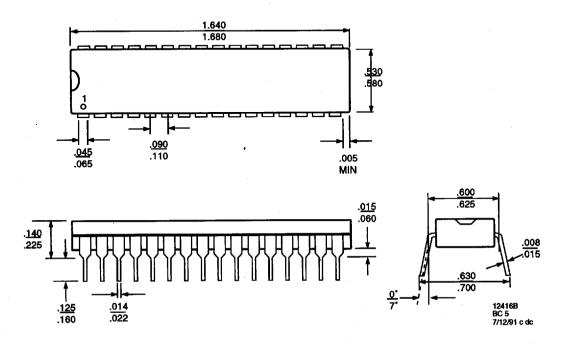

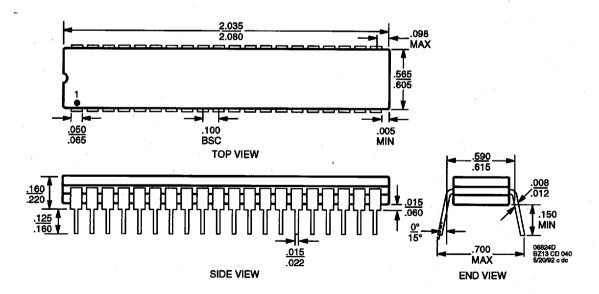

#### 32-Pin DIP

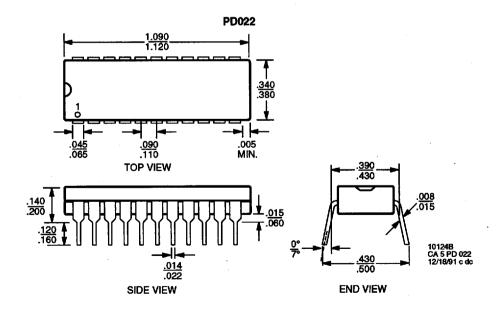

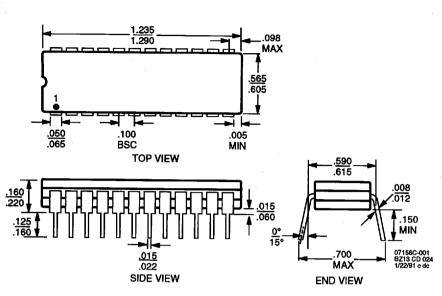

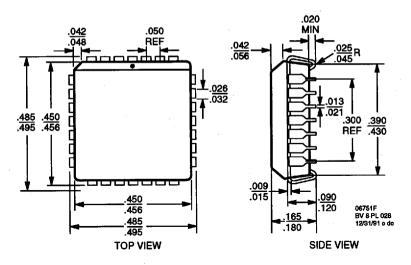

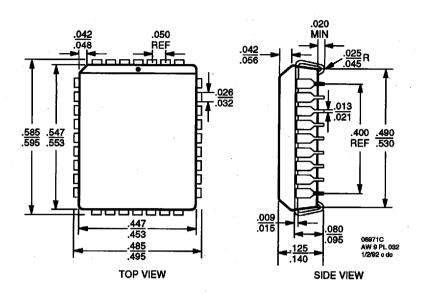

#### 44-Pin PLCC

Note: 1. Pin 1 is marked for orientation purposes.

2. RSRVD = Reserved pin, should not be connected externally to any signal or supply.

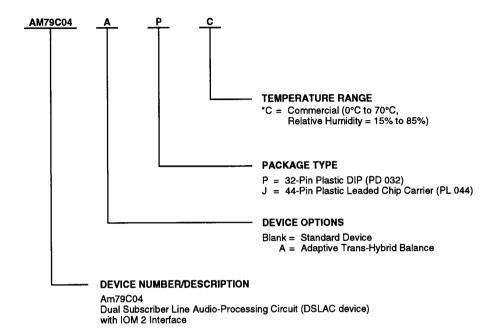

#### ORDERING INFORMATION

#### Standard Products

AMD® standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |                  |  |  |  |  |  |  |

|--------------------|------------------|--|--|--|--|--|--|

| AM79C04            | AJC, APC, JC, PC |  |  |  |  |  |  |

#### Valid Combinations

Valid Combinations lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on the AMD standard military grade products.

<sup>\*</sup> The performance specifications contained in this data sheet are valid for the commercial temperature range only. See the DSLAC Extended Temperature Supplement for information on industrial temperature range (-40°C to +85°C) specifications.

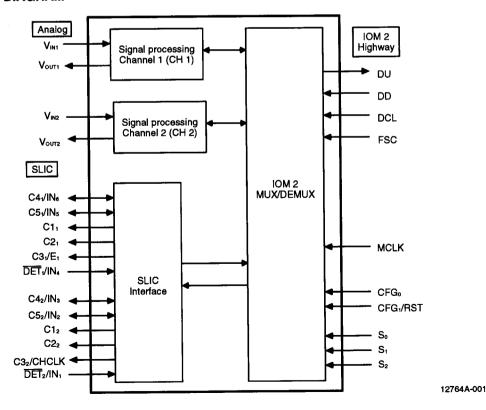

#### PIN DESCRIPTION **AGND**

#### Analog Ground

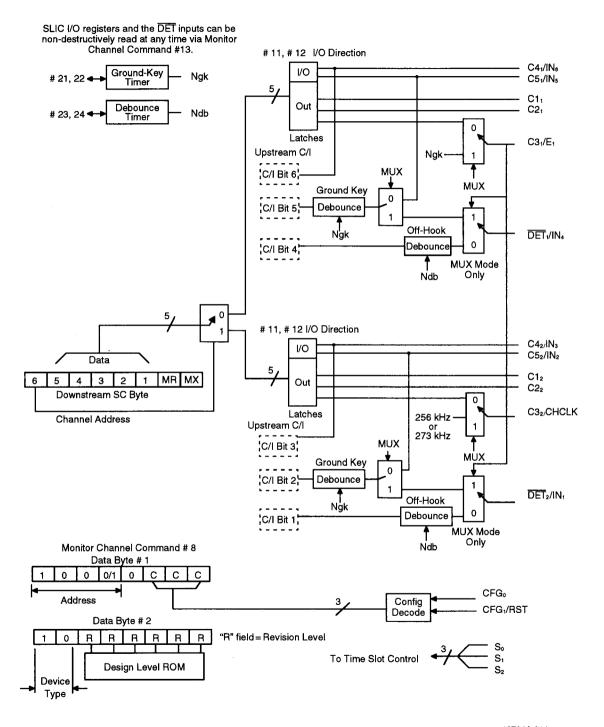

C1, C2, C3,/E1, C12, C22, C32/CHCLK **SLIC Outputs**

These latched outputs are TTL compatible and may be used to control the operation of a SLIC or any other device associated with the subscriber line, C1, C2, and C3,/E1 are associated with Channel 1 and C12, C22, and C3<sub>2</sub>/CHCLK are associated with Channel 2. The outputs are set to a Low level when the device is powered up. The C/I (Command/Indicate) channel is then used to write data to these pins.

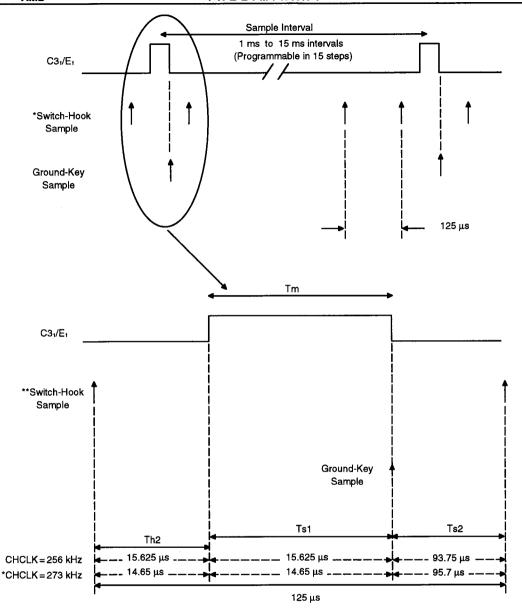

In the Multiplexed mode, the C32/CHCLK output provides a 256-kHz or 273-kHz, 50% duty-cycle clock for use by two SLICs. The CHCLK frequency is synchronous to MCLK, but the phase relationship to MCLK is random. It is capable of driving two TTL inputs. As CHCLK, this output is only active when one or both channels are in the active state; otherwise it is held High. In the Multiplexed mode, the C3<sub>1</sub>/E<sub>1</sub> output is used to control the DET output from an Am795XX series SLIC. A High level allows the SLIC to output its ground-key detect status while a Low level allows the SLIC to output the status of its off-hook detector. C3/E1 can be programmed to go to a High level for approximately 16 µs every 1 to 15 ms to demultiplex the DET inputs.

#### C51/IN5, C52/IN2, C41/IN6, C42/IN3 SLIC Inputs/Outputs

Each pin may be programmed to be an input or output. C4<sub>1</sub>/IN<sub>5</sub> and C5<sub>1</sub>/IN<sub>5</sub> are associated with Channel 1 and C42/IN3 and C52/IN2 are associated with Channel 2. All pins are set to the Input mode when the device is powered up. If these pins are programmed to be outputs, they are written via the C/I channel. These lines are TTL compatible with latched outputs and may be used to control the operation of a SLIC or any other device associated with the subscriber line. If the pins are programmed to be inputs, C41/IN6 will appear as C/I upstream bit 6, C5<sub>1</sub>/IN<sub>5</sub> will appear as C/I upstream bit 5, C42/IN3 will appear as C/I upstream bit 3, and C52/IN2 will appear as C/I upstream bit 2. The Monitor Channel may be used to read the data on these pins.

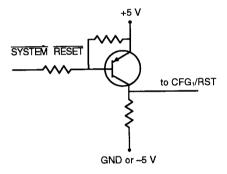

#### CFG<sub>1</sub>/RST, CFG<sub>0</sub>

#### **Configuration Number Assignment**

These inputs allow a configuration number assignment from 0 to 5 by connecting them to either -5 V. ground. or +5 V. A voltage of greater than +2 V applied to the CFG<sub>1</sub>/RST input causes the device to perform a hardware reset. For proper operation, CFGo should be hardwired to one of the DSLAC device's power supplies.

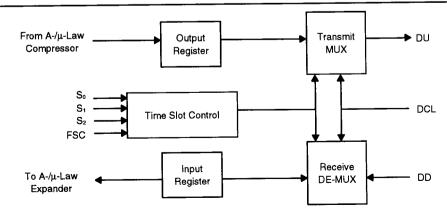

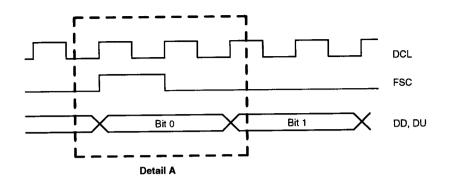

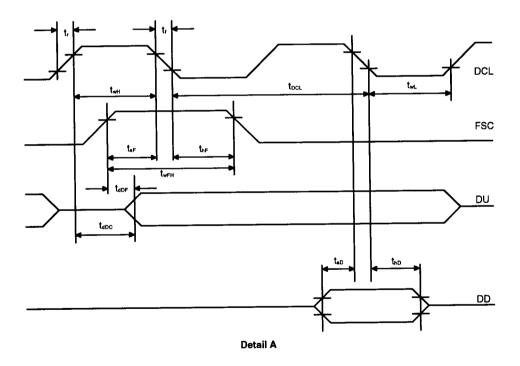

#### DCL

#### IOM 2 Clock

The IOM 2 clock determines the rate at which IOM 2 data is serially shifted into or out of the IOM 2 ports. This rate is twice the desired bit rate. The maximum clock frequency is 8.192 MHz and the minimum clock frequency is 512 kHz. The IOM 2 clock may be asynchronous to MCLK.

#### DD

#### **IOM 2 Downstream Input**

Downstream data is received serially on the DD port every 125 us at half the DCL rate.

#### DET<sub>1</sub>/IN<sub>4</sub>, DET<sub>2</sub>/IN<sub>1</sub>

#### **Loop Status Detector Inputs**

In the Multiplexed mode, the DET<sub>1</sub>/IN<sub>4</sub> and DET<sub>2</sub>/IN<sub>1</sub> inputs are intended to monitor outputs from a Subscriber Line Interface Circuit (SLIC), providing off-hook and ground-key sensing on the same signal. When the E<sub>1</sub> output is Low, the IOM 2 DSLAC device interprets DET./IN. or DET./IN. as off-hook detector inputs. When E1 is High, the DSLAC device interprets these pins as ground-key detector inputs. These pins may also be used in a non-Multiplexed mode, whereby the DET/IN4 input is routed to the C/I upstream bit 4 and the DET<sub>2</sub>/IN<sub>1</sub> input is routed to the C/I upstream bit 1. These inputs are TTL compatible.

#### DGND

#### **Digital Ground**

#### DU

#### IOM 2 Upstream Output

Upstream data is output serially on the DU pin every 125 us at half the DCL rate. DU is high impedance between bursts. This pin is an open-drain output.

#### **FSC**

#### Frame Sync

The Frame Sync pulse is an 8-kHz signal which identifies the beginning of a frame. The IOM 2 DSLAC device references individual time slots with respect to the Frame Sync pulse. FSC is synchronized to DCL.

#### **MCLK**

#### **Master Clock**

The Master Clock is a 2.048- or 4.096-MHz clock input for use by the digital signal processor. DCL may be asynchronous to MCLK.

#### S2-S0

#### **Time Slot Number Assignment**

These inputs are used for a time slot number assignment from 0 to 7. They direct the DSLAC device to input and output PCM and programming information on one of eight time slots.

#### $V_{cc}$

#### **Digital Power Supply**

+5-V digital power supply.

#### Vcca

#### **Analog Power Supply**

+5-V analog power supply must be connected to the +5-V digital power supply.

#### VEET

-5-V power supply-Channel 1.

#### Ver

-5-V power supply- Channel 2.

#### VIN1, VIN2

#### **Analog Inputs**

The analog input is applied to the transmit path of the IOM 2 DSLAC device. The signal is sampled, digitally processed, and encoded for the IOM 2 PCM output.  $V_{\text{IN1}}$  is for Channel 1 and  $V_{\text{IN2}}$  is for Channel 2.

#### VOUT1. VOUT2

#### **Analog Outputs**

The received PCM data is digitally processed and converted to an analog signal at the  $V_{\text{out}}$  pin.  $V_{\text{out1}}$  is for Channel 1 and  $V_{\text{out2}}$  is for Channel 2. These outputs may be used to drive a transformer SLIC directly.

#### **FUNCTIONAL DESCRIPTION**

The DSLAC device performs the Codec/filter functions associated with the four-wire section of the subscriber line circuitry in a digital switch. These functions involve converting an analog voice signal into digital PCM samples and converting digital PCM samples back into an analog signal. The PCM codes are 8-bit and are programmed to be either A-law or u-law companded. During conversion, digital filters are used to band-limit the voice signals.

The user-programmable filters set the receive and transmit gain, perform the trans-hybrid balancing function, permit adjustment of the two-wire termination impedance, and provide frequency attenuation adjustment (equalization) of the receive and transmit paths. Adaptive trans-hybrid balancing is a feature of the Am79C04A. All programmable digital filter coefficients can be calculated using AmSLAC2™ software.

The independent channels allow the DSLAC device to function as two SLAC™ devices. All of the digital filtering is performed in digital signal processors operating from either a 2.048-MHz or 4.096-MHz external clock. The A/D, D/A, and signal processing are separate for each channel. The IOM 2 DSLAC device is available in a 32-pin DIP or a 44-pin PLCC.

This section describes the operation of the IOM 2 interface portion of the Am79C04 DSLAC device. The operational and signal processing features of the Am79C04 DSLAC device are identical to the Am79C02. A full description of these features can be found in the Am79C02 data sheet.

#### **Operational Modes**

See the Am79C02/3(A) Data Sheet.

#### Signal Processing

See the Am79C02/3(A) Data Sheet.

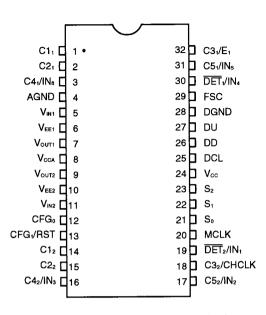

#### IOM 2 Interface

The IOM 2 Interface allows communication of both control and voice data between the IOM 2 highway and subscriber line circuits over a single pair of pins on the DSLAC device.

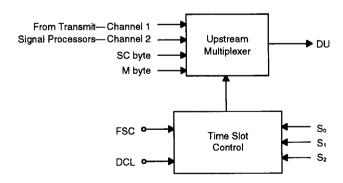

#### **Upstream IOM 2 Interface**

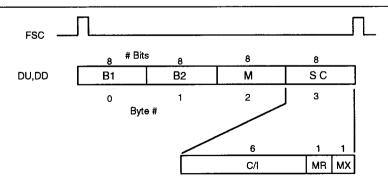

The upstream IOM 2 Interface logic (Figure 1) receives an 8-bit compressed voice code from each subscriber channel signal processor. Also input to the multiplexer are a Status and Control (SC) byte containing subscriber line status information and a Monitor (M) byte containing processor status information. These four inputs are formed into a 4-byte time slot by the upstream multiplexer and sent upstream via the DU pin on the DSLAC device. The frame sync (FSC) pulse identifies the beginning of a frame and all time slots are referenced to it.

The time slot is determined by the code appearing on the Time Slot Assignment pins, S2-S₀. This allows up to eight 4-byte time slots (using a DCL of 4.096 MHz) in each frame. This feature allows any clock frequency between 512 kHz and 4.096 MHz (1 to 8 time slots) in a system. Frequencies between 4.096 MHz and 8.192 MHz are allowed, but only the first eight time slots are used.

Figure 1. Transmit (Upstream) IOM 2 Interface

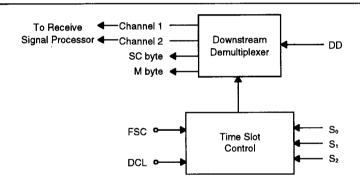

#### Downstream IOM 2 Interface

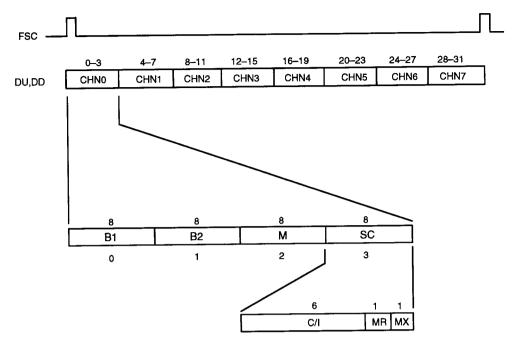

The downstream IOM 2 Interface logic (Figure 2) demultiplexes a time slot (determined by the code on pins  $S_z$ – $S_o$ ) from the downstream data on input DD of the DSLAC device. The time slot contains voice data destined for each of the subscriber line signal processors. Also obtained from the time slot are an SC byte used for SLIC I/O programming and an M byte used for signal processor programming.

As in the upstream interface, one to eight 4-byte time slots are allowed in each frame (using a DCL frequency of 512 kHz to 4.096 MHz).

## IOM 2 FORMAT AND COMMAND STRUCTURE

#### **IOM 2 Format**

A complete IOM 2 frame is sent upstream on the DU pin and received downstream on the DD pin every 125 µs. Each frame consists of up to eight 4-byte time slots. The overall structure of the IOM 2 frame is shown in Figures 3 and 4. Figure 3 shows the pattern when only a single IOM 2 time slot is used with a 256 kb/s bit rate. In this

case the same 32-bit time slot is sent for every frame. Figure 4 shows the pattern when the maximum capacity of eight IOM 2 time slots is used. In this case, a bit rate of 2048 kb/s is needed. Any number of time slots between 1 and 8 can be used, provided the bit rate is adjusted such that a complete frame of time slots can occur every 125 µs. Note that the DCL clock input must be set at a frequency of twice the desired bit rate.

An individual 4-byte IOM 2 time slot contains the following:

- Two bytes, B1 and B2, containing voice data for two separate channels. One IOM 2 time slot can serve two analog subscriber lines.

- One Monitor (M) byte for reading and writing control data and DSP coefficients.

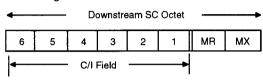

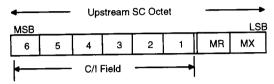

- One Signaling and Control (SC) byte containing a 6-bit Command/Indicate (C/I) field for control information and a 2-bit field with Monitor Receive and Monitor Transmit (MR and MX) bits for handshaking functions. All principal signaling information is carried on the C/I channel.

12764A-003

Figure 2. Receive (Downstream) IOM 2 Interface

Figure 3. IOM 2 Time Slot Structure (256 kb/s)

12764A-005

Figure 4. Multiplexed IOM 2 Time Slot Structure (2048 kb/s)

Programming the DSLAC device is accomplished by using the Signaling and Control (SC) and Monitor (M) bytes of the downstream IOM 2 channel. Additionally, data programmed previously may be read out for verification via the upstream IOM 2 channel M and SC bytes. For each subscriber channel, commands are provided to assign values to the following parameters:

Transmit gain

Receive loss

B-filter coefficients

X-filter coefficients

R-filter coefficients

Z-filter coefficients

Adaptive B-filter parameters

AISN coefficient

Switch-hook/ground-key sampling interval

Debounce time for SLIC input port

Read/Write SLIC input/output

Enable/disable GX filter

Enable/disable GR filter

Enable/disable B filter

Enable/disable X filter

Enable/disable R filter

Enable/disable Z filter

Enable/disable adaptive B filter

Enable/disable AX amplifier

Enable/disable AR amplifier

Selection of A-law or u-law code

Selection of test modes

Selection of active or standby mode

#### The SC Channel Command Structure

#### Downstream C/I Channel

C/I bit 6, the first bit received of the SC octet, is the address bit and selects whether the data in C/I bits 5 through 1 is intended for Channel 1 or Channel 2. C/I bits 5 through 1 are directed to C₅ through C₁, provided these SLIC I/O bits are programmed to be outputs. Any data directed to a SLIC line programmed to be an input would be ignored.

Downstream Bit Definitions of C/I field:

Bit 6—Address bit. A0 selects Channel 1. A1 selects Channel 2

Bit 5-Data to C5 (if configured to be an output)

Bit 4—Data to C4 (if configured to be an output)

Bit 3—Data to C3 (in non-Multiplexed mode)

Bit 2-Data to C2

Bit 1-Data to C1

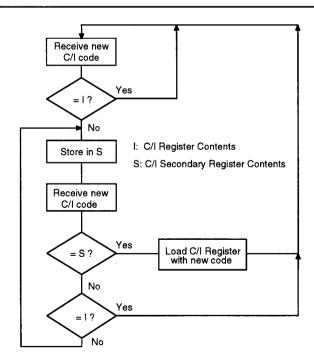

Figure 5 shows a flow chart describing the maximum security protocol. Whenever the received pattern of C/I bits 6 through 1 is different from the pattern currently in the C/I input register, the new pattern is loaded into a secondary C/I register. When the next pattern is received (in the following cycle), the following rules apply:

- If the channel is addressed in the following frame and the received pattern corresponds to the pattern in the secondary register, then the new pattern is loaded into the C/I register.

- If the channel is not addressed in the following frame, the newly received pattern is loaded into the secondary C/I and the content of the C/I register is unchanged.

- If the channel is addressed in the following frame but the received pattern is different from the pattern in the secondary register and different from the pattern currently in the C/I register, the newly received pattern is loaded into the secondary C/I register.

- 4. If the channel is addressed in the following frame but the received pattern is the same as the pattern currently in the C/I register, the C/I register is unchanged. The result is the C/I field (6–1) must be the same for two consecutive frames before it is latched internally.

Figure 5. Security Procedure for C/I Downstream Byte

#### Upstream C/I Channel

There are three upstream C/I bits for each of the two analog lines. C/l bits 4, 5, and 6 are used for Channel 1, while C/I bits 1, 2, and 3 are used for Channel 2. Since the upstream receiving device will also be applying a last look security protocol to the complete 6-bit C/I field, and since changes to the C/I pattern will not be synchronized between two independent source devices, each new 3-bit pattern must be present in at least three consecutive 125-us frames to ensure transfer.

Upstream Bit Definitions of C/I field:

Bit 6—C41/IN6, if C41/IN6 is programmed to be an input, High otherwise

- \*Bit 5—Ground-key detect, Channel 1 (Multiplexed mode), or C5/INs (non-Multiplexed mode if pin is programmed to be an input), or logic 1 (if pin is programmed to be an output)

- \*Bit 4—Switch-hook detect, Channel 1 (Multiplexed mode), or DET/IN4 (non-Multiplexed mode)

- Bit 3—C42/IN3, if C42/IN3 is programmed to be an input, High otherwise

- \*Bit 2—Ground-key detect, Channel 2 (Multiplexed mode), or C52/IN2 (non-Multiplexed mode if pin is programmed to be an input), or logic 1 (if pin is programmed to be an output)

- \*Bit 1—Switch-hook detect, Channel 2 (Multiplexed mode), or DET<sub>2</sub>/IN<sub>1</sub> (non-Multiplexed mode)

- \*The data sent from the DSLAC device on bits 5, 4, 2, and 1 reflect the output from the corresponding debounce circuit, if enabled.

#### The Monitor Channel

#### Monitor Channel Protocol

The Monitor Channel is used to load internal device registers, to read the status of the device and the contents of the internal registers, and to provide supplementary signaling. Information is transferred on the Monitor Channel using the MR and MX bits of the fourth (SC) octet to provide a reliable method of handshaking."

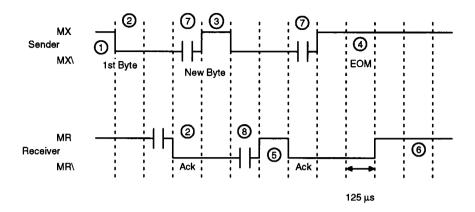

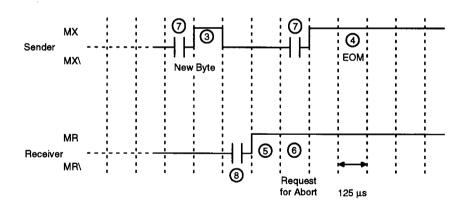

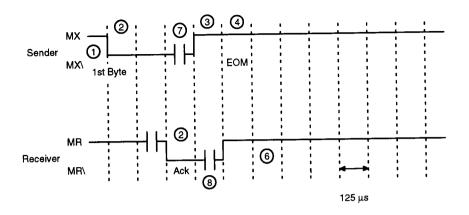

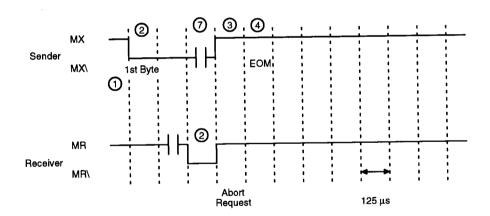

Monitor byte information is transferred via the IOM 2 Interface between read/write registers in the DSLAC device and upstream devices using the following procedure (refer to Figures 6 through 9). Note that the active state of the MX and MR bits is Low.

- 1. The MX bit remains in the inactive state for two or more consecutive frames to indicate an idle state or an end of transmission on the Monitor channel.

- 2. A start-of-message is initiated by the sender by a transition of the MX bit from the inactive state to the active state together with the first byte transmitted in the monitor data octet of the same frame. The transmission may start only if the MR bit received by the transmitter has previously been in the inactive state for at least two frames. The receiver acknowledges start-of-messages by a transition of its MR bit to the active state and confirms receipt of the first byte by holding the MR bit in the active state for a second frame.

- 3. The transition of the MX bit from the active to the inactive state indicates the transmission of a new byte. The transition of the MX bit from the inactive state to the active state in the following frame indicates a repeat of the new data byte.

- 4. The transition of the MX bit from the active to the inactive state, followed by a repeat of the inactive state for at least one or more frames, indicates end-of-message and that the content of the monitor data field is invalid.

- 5. The transition of the MR bit from the active to the inactive state acknowledges receipt of the first transmission of a new byte. The transition of the MR bit from the inactive to the active state in the following frame confirms the new byte has been correctly received.

- 6. The transition of the MR bit from the active to the inactive state, followed by a repeat of the inactive state for at least one more frame, acknowledges the receipt of end-of-message or, if received before end-of-message has been transmitted, requests to abort the message and repeat.

- 7. The active state of the MX bit, accompanied by further transmissions of the current data byte, may continue indefinitely (subject to a time out) for the purpose of flow control.

- 8. The active state of the MR bit may continue indefinitely (subject to a time out) for the purpose of flow control.

Each data byte is repeated until the transmission of a new byte, an end-of-message, or an abort.

<sup>\*</sup>The IOM 2 DSLAC device will acknowledge receipt of a Monitor byte only if it is identical to the Monitor byte of the previous Frame. [This is the same security protocol used for the C/l bits (6-1).]

The circled numbers in Figures 6 through 9 refer to the sequence numbers listed previously:

12764A-007

Figure 6. General Case of Multiple Byte Message Transfer

Figure 7. Abort Request on Multiple Byte Message Transfer

12764A-009

Figure 8. Single Byte Message Transfer

Figure 9. Abort Request on Single Byte Message Transfer

#### **Monitor Channel Command Structure**

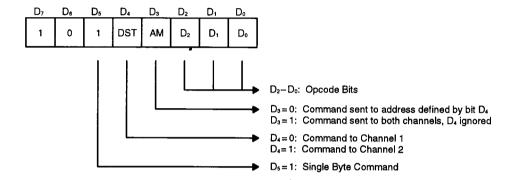

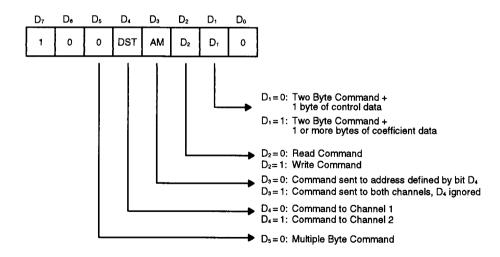

The Monitor byte is the third byte in the 4-byte frame sent and received every 125 µs over the DU or DD pins. A Monitor command consists of one or more command bytes which may be followed with additional bytes of input data or may be followed by the DSLAC device sending out bytes of data over the DU pin. The first byte sent in a monitor channel message contains address, com-

mand, and read/write information conforming to the format in the diagrams below. Commands #25 through #40 are used to program the internal filters of the DSLAC device. Please refer to the Am79C02/3(A) DSLAC Preliminary Data Sheet for a complete description of the filter transfer functions and the coefficient structure.

12764A-011

## **Summary of Monitor Channel Commands**

| Summ    | =                       |                    | 1145                                              |

|---------|-------------------------|--------------------|---------------------------------------------------|

| #       | Byte 1                  | Byte 2             |                                                   |

| 1       | 101AB000                |                    | Inactivate (Standby mode)                         |

| 2       | 101AB001                |                    | Reset                                             |

| 3       | 101AB010                |                    | No Operation                                      |

| 4       | 101AB011                |                    | Reset to Normal Conditions                        |

| 5       | 101AB100                |                    | Activate                                          |

| 6       | 101AB110                |                    | MCLK = 2.048 MHz                                  |

| 7       | 101AB111                |                    | MCLK = 4.096 MHz                                  |

| 8       | 100A0000                | 00000000           | Read Channel ID Information                       |

| 9       | 100AB100                | 0000001            | Write AISN & Analog Gains                         |

| 10      | 100A0000                | 0000001            | Read AISN & Analog Gains                          |

| 11      | 100AB100                | 00000011           | Write SLIC Input/Output Direction                 |

| 12      | 100A0000                | 00000011           | Read SLIC Input/Output Direction and Power Status |

| 13      | 100A0000                | 00000100           | Read SLIC Input/Output Registers                  |

| 14      | 100AB100                | 00000101           | Write Operating Functions                         |

| 15      | 100A0000                | 00000101           | Read Operating Functions                          |

| 16      | 100AB100                | 00000110           | AMD Internal Use Only                             |

| 17      | 100A0000                | 00000110           | AMD Internal Use Only                             |

| 18      | 100AB100                | 00000111           | Write Operating Conditions                        |

| 19      | 100A0000                | 00000111           | Read Operating Conditions                         |

| 20      | 100A0000                | 00001000           | Read Revision Code Number                         |

| 21      | 100AB100                | 00001001           | Write Ground-Key Sampling Interval                |

| 22      | 100A0000                | 00001001           | Read Ground-Key Sampling Interval                 |

| 23      | 100AB100                | 00001010           | Write SLIC Upstream Input Debounce Time           |

| 24      | 100A0000                | 00001010           | Read SLIC Upstream Input Debounce Time            |

| 25      | 100AB110                | 00000000           | Write GX-Filter Coefficients                      |

| 26      | 100A0010                | 0000000            | Read GX-Filter Coefficients                       |

| 27      | 100AB110                | 0000001            | Write GR-Filter Coefficients                      |

| 28      | 100A0010                | 0000001            | Read GR-Filter Coefficients                       |

| 29      | 100AB110                | 0000010            | Write Z-Filter Coefficients                       |

| 30      | 100A0010                | 0000010            | Read Z-Filter Coefficients                        |

| 31      | 100AB110                | 00000011           | Write B-Filter Coefficients                       |

| 32      | 100A0010                | 00000011           | Read B-Filter Coefficients                        |

| 33      | 100AB110                | 00000100           | Write X-Filter Coefficients                       |

| 34      | 100A0010                | 00000100           | Read X-Filter Coefficients                        |

| 35      | 100AB110                | 00000101           | Write R-Filter Coefficients                       |

| 36      | 100A0010                | 00000101           | Read R-Filter Coefficients                        |

| 37      | 100AB110                | 00000110           | Write Echo Path Gain                              |

| 38      | 100A0010                | 00000110           | Read Echo Path Gain                               |

| 39      | 100AB110                | 00000111           | Write Error Level Threshold                       |

| 40      | 100A0010                | 00000111           | Read Error Level Threshold                        |

| A is re | ferred to as DST in the | following section. | B is referred to as AM in the following section.  |

A: 0 = Destination is Channel 1 1 = Destination is Channel 2 B: 0 = Command to channel defined by A bit

1 = Command to both channels, A bit ignored

#### **DETAILED MONITOR COMMAND DEFINITIONS**

### Inactivate (Standby mode)

Format:

| ИSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 1 | DST | AM | 0 | 0 | 0   |

Bit Name Description

During Inactive mode (of one or both channels), none of the programmed information is changed and the analog output is set to 0 V.

#### Reset

Format:

| /ISB |   |   |     |    |   |   | LSB |  |

|------|---|---|-----|----|---|---|-----|--|

| 1    | 0 | 1 | DST | AM | 0 | 0 | 1   |  |

#### Bit Name Description

The Reset state of the device is:

- a. A-law is selected.

- b. B, X, R, and Z filters are disabled and AISN gain is zero.

- c. Transmit (GX and AX) and Receive (GR and AR) gains are set to unity.

- d. SLIC Input/Output is set to the Read mode.

- e. Normal conditions are selected (see Command 4).

- f. The Adaptive mode and Error Level Threshold are reset.

- g. The SLIC interface is set to the non-Multiplexed mode.

- h. Both channels are placed in the Inactive (Standby) mode.

### **Reset to Normal Conditions**

Format:

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 1 | DST | AM | 0 | 1 | 1   |

#### Bit Name Description

Normal conditions are:

- a. 6 dB loss in receive path not inserted.

- b. Receive path not cut off.

- c. High-pass filter enabled.

- d. Test modes are turned off.

### **Activate (Operational Mode)**

Format:

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 1 | DST | AM | 1 | 0 | 0   |

| Bit Name | Description                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|

|          | Valid IOM 2 data is not transmitted until after the second FSC pulse is received following the execution of the Activate command. |

#### Set MCLK to 2.048 MHz

Format:

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 1 | DST | AM | 1 | 1 | 0   |

#### Set MCLK to 4.096 MHz

Format:

Format:

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 1 | DST | AM | 1 | 1 | 1   |

### **Read Channel Identification Information**

| Co | m | m | 9 | n | d |

|----|---|---|---|---|---|

| MSB |   |   |     |   |   |   | L2B |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 0 | 0   |

|     |   |   |     |   |   |   |     |

| 0   | 0 | 0 | 0   | 0 | 0 | 0 | 0   |

| 1 | 0 | 0 | SRC | 0 | С | С | С |

|---|---|---|-----|---|---|---|---|

| Т | Т | L | L   | L | L | L | L |

| Bit Name | Description                                                                                                                                                |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRC      | Source                                                                                                                                                     |

|          | 0 = Source is Channel 1.<br>1 = Source is Channel 2.                                                                                                       |

| С        | Configuration                                                                                                                                              |

|          | This field reflects the state of the configuration inputs.                                                                                                 |

| T        | Device Type                                                                                                                                                |

|          | These 2 bits always have a value of 10.                                                                                                                    |

| L        | Design Level                                                                                                                                               |

|          | This 6-bit field is used to differentiate between different implementations of the same device type. The IOM 2 DSLAC device is assigned the number 000100. |

## Write AISN and Analog Gains

### Command (2 Bytes)

Format:

| MSB |   | _ |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 0 | DST | AM | 1 | 0 | 0   |

| 0   | 0 | 0 | 0   | 0  | 0 | 0 | 1   |

### **Input Data**

| _ | AX | AR | Α | В | С | D | E |

|---|----|----|---|---|---|---|---|

| Bit Name      | Description                                                                                                                                                                                           |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| AX            | Transmit Analog Gain                                                                                                                                                                                  |  |  |  |  |  |  |

|               | AX = 0 0 dB gain<br>AX = 1 6 dB gain                                                                                                                                                                  |  |  |  |  |  |  |

| AR            | Receive Analog Loss                                                                                                                                                                                   |  |  |  |  |  |  |

|               | AR = 0 0 dB loss<br>AR = 1 6 dB loss                                                                                                                                                                  |  |  |  |  |  |  |

| A, B, C, D, E | AISN coefficients                                                                                                                                                                                     |  |  |  |  |  |  |

|               | The Analog Impedance Scaling Network (AISN) gain can be varied from -0.9375 to 0.9375 in increments of 0.0625. The gain coefficient is encoded and decoded using the following equation:              |  |  |  |  |  |  |

|               | $h_{AISN} = 0.0625 ((A2^4 + B2^3 + C2^2 + D2^1 + E2^0) - 16)$                                                                                                                                         |  |  |  |  |  |  |

|               | where $h_{AISN}$ is the gain of the AISN and A, B, C, D, and E=0 or 1. A value of ABCDE=10000 implements a special digital loop-back mode and a value of ABCDE=00000 indicates a gain of 0 (cut off). |  |  |  |  |  |  |

### **Read AISN and Analog Gains**

### Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 0 | 0   |

| 0   | 0 | 0 | 0   | 0 | 0 | 0 | 1   |

|     |   |   |     |   |   |   |     |

| _ | AX | AR | Α | В | С | D | Е |

|---|----|----|---|---|---|---|---|

### Write SLIC Input/Output Direction

### Command (2 Bytes)

Input Data

Format:

| MSB |   |          |     |    |   |   | LSB |

|-----|---|----------|-----|----|---|---|-----|

| 1   | 0 | 0        | DST | AM | 1 | 0 | 0   |

| 0   | 0 | 0        | 0   | 0  | 0 | 1 | 1   |

|     |   | <u> </u> |     |    |   |   |     |

В

| Bit Name | Description                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|          | Pins C5 <sub>1</sub> /IN <sub>5</sub> , C5 <sub>2</sub> /IN <sub>2</sub> , C4 <sub>1</sub> /IN <sub>6</sub> , and C4 <sub>2</sub> /IN <sub>3</sub> are set to Input or Output modes individually. The Input mode is set when the appropriate data bit is set to 0, and the Output mode is set when the data bit is set to 1. |  |  |  |  |  |  |

|          | Data bit A sets pins C5₁/IN₅ or C5₂/IN₂                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|          | Data bit B set pins C4 <sub>1</sub> /IN <sub>6</sub> , or C4 <sub>2</sub> /IN <sub>3</sub>                                                                                                                                                                                                                                   |  |  |  |  |  |  |

Α

## Read SLIC Input/Output Direction and Power Status

### Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 0 | 0   |

| 0   | 0 | 0 | 0   | 0 | 0 | 1 | 1   |

|    |    |   |   |   | <br> |  |

|----|----|---|---|---|------|--|

| PI | cs | _ | Α | В | <br> |  |

| Bit Name | Description                                                                                                                                                                                                                                     |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pl       | Power Interrupt Bit                                                                                                                                                                                                                             |

|          | PI = 0 There has not been a power interruption since the last software reset command.                                                                                                                                                           |

|          | PI = 1 A power interruption has been previously detected requiring the DSLAC device to be<br>completely reprogrammed. This bit is cleared by issuing a software reset command.<br>THE DSLAC DEVICE CANNOT BE ACTIVATED UNTIL THIS BIT IS CLEAR. |

| cs       | Channel Status Bit                                                                                                                                                                                                                              |

|          | CS=0 The status of the channel is inactive (Standby mode).                                                                                                                                                                                      |

|          | CS = 1 The status of the channel is active (Operational mode).                                                                                                                                                                                  |

### Read SLIC Input/Output Registers

### Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 0 | 0   |

| 0   | 0 | 0 | 0   | 0 | 1 | 0 | 0   |

### **Output Data**

|  | _ | DET | C5 | C4 | СЗ | C2 | C1 |

|--|---|-----|----|----|----|----|----|

| Bit Name | Description                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------|

| C5       | Refers to C5₁ or C5₂ if they are used as outputs.<br>Refers to IN₃ or IN₂ if they are used as inputs. |

| C4       | Refers to C4₁ or C4₂ if they are used as outputs.<br>Refers to IN₀ or IN₃ if they are used as inputs. |

### **Write Operating Functions**

### Command (2 Bytes)

Format:

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 0 | DST | AM | 1 | 0 | 0   |

| 0   | 0 | 0 | 0   | 0  | 1 | 0 | 1   |

|     |     |     |     | -  |    |    |    |  |

|-----|-----|-----|-----|----|----|----|----|--|

| ABF | A/U | EGR | EGX | EX | ER | EZ | EB |  |

| Bit Name | Description        |                                         |  |  |  |  |  |

|----------|--------------------|-----------------------------------------|--|--|--|--|--|

| ABF      | Adaptive B Filter  |                                         |  |  |  |  |  |

|          | ABF=0<br>ABF=1     | non-Adaptive mode<br>Adaptive mode      |  |  |  |  |  |

| A/U      | A-law/μ-la         | w                                       |  |  |  |  |  |

|          | A/U = 0<br>A/U = 1 | A-law coding<br>μ-law coding            |  |  |  |  |  |

| EGR      | GR Filter          |                                         |  |  |  |  |  |

|          | EGR=0<br>EGR=1     | GR filter disabled<br>GR filter enabled |  |  |  |  |  |

| EGX      | GX Filter          |                                         |  |  |  |  |  |

|          | EGX=0<br>EGX=1     | GX filter disabled<br>GX filter enabled |  |  |  |  |  |

| EX       | X Filter           |                                         |  |  |  |  |  |

|          | EX = 0<br>EX = 1   | X filter disabled<br>X filter enabled   |  |  |  |  |  |

## Write Operating Functions—(continued)

| Bit Name | Description      |                                       |  |  |  |  |

|----------|------------------|---------------------------------------|--|--|--|--|

| ER       | R Filter         |                                       |  |  |  |  |

|          | ER = 0<br>ER = 1 | R filter disabled<br>R filter enabled |  |  |  |  |

| EZ       | Z Filter         |                                       |  |  |  |  |

|          | EZ=0<br>EZ=1     | Z filter disabled<br>Z filter enabled |  |  |  |  |

| EB       | B Filter         |                                       |  |  |  |  |

|          | EB = 0<br>EB = 1 | B filter disabled<br>B filter enabled |  |  |  |  |

### **Read Operating Functions**

### Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 0 | 0   |

| 0   | 0 | 0 | 0   | 0 | 1 | 0 | 1   |

| 0   | 0 | 0 | 0   | 0 | 1 | 0 | _   |

### **Output Data**

|  | ABF | Α/μ | EGR | EGX | EX | ER | EZ | EB |

|--|-----|-----|-----|-----|----|----|----|----|

|--|-----|-----|-----|-----|----|----|----|----|

### **Write Operating Conditions**

### Command (2 Bytes)

Format:

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 0 | DST | АМ | 1 | 0 | 0   |

| 0   | 0 | 0 | 0   | 0  | 1 | 1 | 1   |

| _ | CRP | HPF | RG | ALB | DLB | _ | _ |

|---|-----|-----|----|-----|-----|---|---|

| Bit Name | Description        | on                                                    |

|----------|--------------------|-------------------------------------------------------|

| CRP      | Cutoff Red         | ceive Path                                            |

|          | CRP=0<br>CRP=1     | Receive path connected<br>Receive path cutoff         |

| HPF      | High-Pass          | s Filter                                              |

|          | HPF = 0<br>HPF = 1 | High-pass filter enabled<br>High-pass filter disabled |

| RG       | Receive F          | ath Gain                                              |

|          | RG = 0<br>RG = 1   | 6 dB loss not inserted<br>6 dB loss inserted          |

## Write Operating Conditions—(continued)

| Bit Name | Descripti          | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ALB      | Analog Loop-Back   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|          | ALB = 0<br>ALB = 1 | Analog loop-back disabled<br>Analog loop-back enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| DLB      | Digital Loop-Back  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|          | DLB = 0<br>DLB = 1 | Digital loop-back disabled<br>Digital loop-back enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|          |                    | hadronia de la companya de la desarron de la desarron de la desarron de la dela companya dela dela dela dela dela dela dela del |  |  |  |  |

Note: Analog and Digital loop-backs must not be programmed at the same time.

### **Read Operating Conditions**

### Command (2 Bytes)

|             | MSB |     |     |     |     |     |   | LSB |

|-------------|-----|-----|-----|-----|-----|-----|---|-----|

| Format:     | 1   | 0   | 0   | DST | 0   | 0   | 0 | 0   |

|             | 0   | 0   | 0   | 0   | 0   | 1   | 1 | 1   |

| Output Data |     |     |     |     |     |     |   |     |

|             | _   | CRP | HPF | RG  | ALB | DLB | _ | _   |

### **Read Revision Code Number**

### Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 0 | 0   |

| 0   | 0 | 0 | 0   | 1 | 0 | 0 | 0   |

|     |   |   |     |   |   |   |     |

| # # # # # # # # |   |   |   |   |   |   |   |   |

|-----------------|---|---|---|---|---|---|---|---|

|                 | # | # | # | # | # | # | # | # |

| Bit Name | Description |

|----------|-------------|

| DST      | Don't care  |

### Write Ground-Key Sampling Interval

### Command (2 Bytes)

Format:

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 0 | DST | AM | 1 | 0 | 0   |

| 0   | 0 | 0 | 0   | 1  | 0 | 0 | 1   |

#### **Input Data**

| _ | CHF* | MUX | Gk3 | Gk2 | Gk1 | Gk0 |

|---|------|-----|-----|-----|-----|-----|

| Bit Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MUX      | Multiplexed mode                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|          | MUX = 0 non-Multiplexed mode                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|          | MUX = 1 Multiplexed mode                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|          | The device may be configured to operate in the Multiplexed mode (MUX) where the off-hook status and the ground-key status are multiplexed onto the same line. Note that there is only one Ground-Key Sampling Interval register and one MUX bit per IOM 2 DSLAC device (not per channel). Thus, the DST and the AM fields are not decoded and a command to either channel will write into the Ground-Key register and the MUX bit. |  |  |  |  |  |

| Gk3-Gk0  | Sampling Interval                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|          | 1 to 15 ms in 1 ms steps.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|          | If the Gk3–Gk0 field is set to 0000 there is no debounce performed. If, additionally, the MUX bit is set to a 0 or if the Gk3–Gk0 field is set to 0000, the C3./E1 output is controlled by writing a 0 or a 1 into the output latch via the C/I downstream byte.                                                                                                                                                                   |  |  |  |  |  |

### **Read Ground-Key Sampling Interval**

#### Command (2 Bytes)

Format:

| M | SB |   |   |     |   |   |   | LSB |

|---|----|---|---|-----|---|---|---|-----|

|   | 1  | 0 | 0 | DST | 0 | 0 | 0 | 0   |

| Ī | 0  | 0 | 0 | 0   | 1 | 0 | 0 | 1   |

#### **Output Data**

| _ | _ | CHF* | MUX | Gk3 | Gk2 | Gk1 | Gk0 |

|---|---|------|-----|-----|-----|-----|-----|

\*CHF— Chopper Clock Frequency (this bit sets the chopper clock frequency when the IOM 2 DSLAC device is operating in multiplexed mode).

CHF=0 256 kHz (default)

CHF=1 273 kHz

### **Write SLIC Detect Inputs Debounce Time**

### Command (2 Bytes)

Format:

|   |   |     |               |                    |                           | LSB                           |

|---|---|-----|---------------|--------------------|---------------------------|-------------------------------|

| 0 | 0 | DST | AM            | 1                  | 0                         | 0                             |

| 0 | 0 | 0   | 1             | 0                  | 1                         | 0                             |

|   | 0 | 0 0 | 0 0 DST 0 0 0 | 0 0 DST AM 0 0 0 1 | 0 0 DST AM 1<br>0 0 0 1 0 | 0 0 DST AM 1 0<br>0 0 0 1 0 1 |

#### **Input Data**

| _ | _ | _ | _ | Db3 | Db2 | Db1 | Db0 |

|---|---|---|---|-----|-----|-----|-----|

| Bit Name | Description                                                                                                                                                                                                                                                                                                                     |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Db3-Db0  | Debounce Interval                                                                                                                                                                                                                                                                                                               |

|          | Sets the debounce time from 0 to 15 ms in steps of 1 ms.                                                                                                                                                                                                                                                                        |

|          | This command sets the debounce interval for the input signals at DET <sub>1</sub> and DET <sub>2</sub> . Note that there is only one Detect Input Debounce register per IOM 2 DSLAC device (not per channel). Thus, the DST and the AM fields are unused and a command to either channel will write into the Debounce register. |

|          | If the Db3-Db0 field is set to 0000, there is no debounce performed.                                                                                                                                                                                                                                                            |

### **Read SLIC Upstream Inputs Debounce Time**

### Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 0 | 0   |

| 0   | 0 | 0 | 0   | 1 | 0 | 1 | 0   |

### **Output Data**

|  | <br>_ | _ | Db3 | Db2 | Db1 | Db0 |

|--|-------|---|-----|-----|-----|-----|

### **Write GX-Filter Coefficients**

#### Command (2 Bytes)

Format:

| MSB |   |   |     |    |   |   | LSE | 3 |

|-----|---|---|-----|----|---|---|-----|---|

| 1   | 0 | 0 | DST | AM | 1 | 1 | 0   |   |

| 0   | 0 | 0 | 0   | 0  | 0 | 0 | 0   | _ |

| C <sub>40</sub> | m <sub>40</sub> | C <sub>30</sub> | M <sub>30</sub> | Byte 1 |

|-----------------|-----------------|-----------------|-----------------|--------|

| C <sub>20</sub> | m <sub>20</sub> | C <sub>10</sub> | m <sub>10</sub> | Byte 2 |

### **Read GX-Filter Coefficients**

Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 1 | 0   |

| 0   | 0 | 0 | 0   | 0 | 0 | 0 | 0   |

**Output Data**

| C <sub>40</sub> | m <sub>40</sub> | C <sub>30</sub> | M <sub>30</sub> | Byte 1 |

|-----------------|-----------------|-----------------|-----------------|--------|

| C <sub>20</sub> | M <sub>20</sub> | C <sub>10</sub> | M <sub>10</sub> | Byte 2 |

### **Write GR-Filter Coefficients**

Command (2 Bytes)

Format:

| MSB |   |   |     |    |   |   | LSE |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 0 | DST | AM | 1 | 1 | 0   |

| 0   | 0 | 0 | 0   | 0  | 0 | 0 | 1   |

Input Data

| C <sub>40</sub> | M <sub>40</sub> | C <sub>30</sub> | m <sub>30</sub> |

|-----------------|-----------------|-----------------|-----------------|

| C <sub>20</sub> | m <sub>20</sub> | C <sub>10</sub> | m <sub>10</sub> |

### **Read GR-Filter Coefficients**

Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 1 | 0   |

| 0   | 0 | 0 | 0   | 0 | 0 | 0 | 1   |

**Output Data**

|   | C <sub>40</sub> | M <sub>40</sub> | C <sub>30</sub> | m <sub>so</sub> | Byte 1 |

|---|-----------------|-----------------|-----------------|-----------------|--------|

| İ | C <sub>20</sub> | M <sub>20</sub> | C <sub>10</sub> | m <sub>10</sub> | Byte 2 |

Byte 1 Byte 2

### **Write Z-Filter Coefficients**

### Command (2 Bytes)

Format:

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 0 | DST | AM | 1 | 1 | 0   |

| 0   | 0 | 0 | 0   | 0  | 0 | 1 | 0   |

### Input Data

| C <sub>45</sub> | m <sub>45</sub> | C <sub>35</sub> | M <sub>35</sub> | Byte 1  |

|-----------------|-----------------|-----------------|-----------------|---------|

| C <sub>25</sub> | m <sub>25</sub> | C <sub>15</sub> | M <sub>15</sub> | Byte 2  |

| C <sub>40</sub> | M <sub>40</sub> | C <sub>30</sub> | m <sub>30</sub> | Byte 3  |

| C <sub>20</sub> | m <sub>20</sub> | C <sub>10</sub> | m <sub>10</sub> | Byte 4  |

| C <sub>41</sub> | M <sub>41</sub> | C <sub>31</sub> | m <sub>31</sub> | Byte 5  |

| C <sub>21</sub> | M <sub>21</sub> | C <sub>11</sub> | M <sub>11</sub> | Byte 6  |

| C <sub>42</sub> | m <sub>42</sub> | C <sub>32</sub> | m <sub>32</sub> | Byte 7  |

| C <sub>22</sub> | m <sub>22</sub> | C <sub>12</sub> | M <sub>12</sub> | Byte 8  |

| C <sub>43</sub> | m <sub>43</sub> | C <sub>33</sub> | m <sub>33</sub> | Byte 9  |

| C <sub>23</sub> | m <sub>23</sub> | C <sub>13</sub> | M <sub>13</sub> | Byte 10 |

| C44             | m₄₄             | C <sub>34</sub> | m <sub>34</sub> | Byte 11 |

| C <sub>24</sub> | m <sub>24</sub> | C <sub>14</sub> | M <sub>14</sub> | Byte 12 |

| C <sub>48</sub> | M <sub>46</sub> | C <sub>36</sub> | m <sub>36</sub> | Byte 13 |

| C <sub>26</sub> | m <sub>26</sub> | C <sub>16</sub> | M <sub>16</sub> | Byte 14 |

### **Read Z-Filter Coefficients**

Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 1 | 0   |

| 0   | 0 | 0 | 0   | 0 | 0 | 1 | 0   |

|                 |                 |                 |                 | _       |

|-----------------|-----------------|-----------------|-----------------|---------|

| C <sub>45</sub> | M <sub>45</sub> | C <sub>35</sub> | m <sub>35</sub> | Byte 1  |

| C <sub>25</sub> | M <sub>25</sub> | C <sub>15</sub> | m <sub>15</sub> | Byte 2  |

| C <sub>40</sub> | M <sub>40</sub> | C <sub>30</sub> | m <sub>30</sub> | Byte 3  |

| C <sub>20</sub> | M <sub>20</sub> | C <sub>10</sub> | m <sub>10</sub> | Byte 4  |

| C <sub>41</sub> | M <sub>41</sub> | C <sub>31</sub> | m <sub>31</sub> | Byte 5  |

| C <sub>21</sub> | m <sub>21</sub> | C <sub>11</sub> | m <sub>11</sub> | Byte 6  |

| C <sub>42</sub> | m <sub>42</sub> | C <sub>32</sub> | m <sub>32</sub> | Byte 7  |

| C <sub>22</sub> | m <sub>22</sub> | C <sub>12</sub> | m <sub>12</sub> | Byte 8  |

| C <sub>43</sub> | M <sub>43</sub> | C <sub>33</sub> | m <sub>33</sub> | Byte 9  |

| C <sub>23</sub> | m <sub>23</sub> | C <sub>13</sub> | M <sub>13</sub> | Byte 10 |

| C44             | M <sub>44</sub> | C <sub>34</sub> | m <sub>34</sub> | Byte 11 |

| C <sub>24</sub> | M <sub>24</sub> | C <sub>14</sub> | m₁₄             | Byte 12 |

| C <sub>46</sub> | M <sub>46</sub> | C <sub>36</sub> | m <sub>36</sub> | Byte 13 |

| C <sub>28</sub> | M <sub>26</sub> | C <sub>16</sub> | M <sub>16</sub> | Byte 14 |

### **Write B-Filter Coefficients**

### Command (2 Bytes)

Format:

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 0 | DST | AM | 1 | 1 | 0   |

| 0   | 0 | 0 | 0   | 0  | 0 | 1 | 1   |

#### **Input Data**

| Byte 1  | m <sub>20</sub> | C <sub>20</sub> | m <sub>30</sub> | C <sub>30</sub> |

|---------|-----------------|-----------------|-----------------|-----------------|

| Byte 2  | m <sub>31</sub> | C <sub>31</sub> | m <sub>10</sub> | C <sub>10</sub> |

| Byte 3  | m <sub>11</sub> | C <sub>11</sub> | m <sub>21</sub> | C <sub>21</sub> |

| Byte 4  | m <sub>22</sub> | C <sub>22</sub> | m <sub>32</sub> | C <sub>32</sub> |

| Byte 5  | m <sub>33</sub> | C <sub>33</sub> | m <sub>12</sub> | C <sub>12</sub> |

| Byte 6  | m <sub>13</sub> | C <sub>13</sub> | m <sub>23</sub> | C <sub>23</sub> |

| Byte 7  | m <sub>24</sub> | C <sub>24</sub> | m <sub>34</sub> | C <sub>34</sub> |

| Byte 8  | m <sub>35</sub> | C <sub>35</sub> | m <sub>14</sub> | C <sub>14</sub> |

| Byte 9  | m <sub>15</sub> | C <sub>15</sub> | m <sub>25</sub> | C <sub>25</sub> |

| Byte 10 | m <sub>26</sub> | C <sub>26</sub> | m <sub>36</sub> | C <sub>36</sub> |

| Byte 11 | m <sub>37</sub> | C <sub>37</sub> | m <sub>16</sub> | C <sub>16</sub> |

| Byte 12 | M <sub>17</sub> | C <sub>17</sub> | m <sub>27</sub> | C <sub>27</sub> |

| Byte 13 | m <sub>38</sub> | Сзе             | M <sub>48</sub> | C <sub>48</sub> |

| Byte 14 | m <sub>18</sub> | C <sub>18</sub> | m <sub>28</sub> | C <sub>28</sub> |

### **Read B-Filter Coefficients**

### Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 1 | 0   |

| 0   | 0 | 0 | 0   | 0 | 0 | 1 | 1   |

### **Output Data**

| Byt | m <sub>20</sub> | C <sub>20</sub> | m <sub>30</sub> | C <sub>30</sub> |

|-----|-----------------|-----------------|-----------------|-----------------|

| Byt | M₃ı             | C <sub>31</sub> | m <sub>10</sub> | C <sub>10</sub> |

| Byt | m <sub>11</sub> | C <sub>11</sub> | m <sub>21</sub> | C <sub>21</sub> |

| Byt | m <sub>22</sub> | C <sub>22</sub> | m <sub>32</sub> | C <sub>32</sub> |

| Byt | M <sub>33</sub> | C <sub>33</sub> | m <sub>12</sub> | C <sub>12</sub> |

| Byt | m <sub>13</sub> | C <sub>13</sub> | m <sub>23</sub> | C <sub>23</sub> |

| Byt | m <sub>24</sub> | C <sub>24</sub> | M <sub>34</sub> | C <sub>34</sub> |

| Byt | m <sub>35</sub> | C <sub>35</sub> | M <sub>14</sub> | C <sub>14</sub> |

| Byt | m <sub>15</sub> | C <sub>15</sub> | M <sub>25</sub> | C <sub>25</sub> |

| By  | m <sub>26</sub> | C <sub>26</sub> | m <sub>36</sub> | C <sub>36</sub> |

| Ву  | m <sub>37</sub> | C <sub>37</sub> | M <sub>16</sub> | C <sub>16</sub> |

| Ву  | m <sub>17</sub> | C <sub>17</sub> | m <sub>27</sub> | C <sub>27</sub> |

| By  | m <sub>38</sub> | C <sub>38</sub> | M <sub>48</sub> | C <sub>48</sub> |

| Ву  | mte             | C <sub>18</sub> | m <sub>28</sub> | C <sub>28</sub> |

### Write X-Filter Coefficients

Format:

### Command (2 Bytes)

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 0 | DST | AM | 1 | 1 | 0   |

| 0   | О | 0 | 0   | 0  | 1 | 0 | 0   |

### Input Data

| C <sub>40</sub> | m <sub>40</sub> | C <sub>30</sub> | m <sub>30</sub> | Byte 1            |

|-----------------|-----------------|-----------------|-----------------|-------------------|

| C <sub>20</sub> | m <sub>20</sub> | C <sub>10</sub> | m <sub>10</sub> | Byte 2            |

| C <sub>41</sub> | m <sub>41</sub> | C <sub>31</sub> | m <sub>31</sub> | Byte 3            |

| C <sub>21</sub> | m <sub>21</sub> | C <sub>11</sub> | m <sub>11</sub> | Byte 4            |

| C <sub>42</sub> | m <sub>42</sub> | C <sub>32</sub> | m <sub>32</sub> | Byte 5            |

| C <sub>22</sub> | m <sub>22</sub> | C <sub>12</sub> | m <sub>12</sub> | Byte 6            |

| C <sub>43</sub> | m <sub>43</sub> | C <sub>33</sub> | m <sub>33</sub> | Byte 7            |

| C <sub>23</sub> | m <sub>23</sub> | C <sub>13</sub> | m <sub>13</sub> | Byte 8            |

| C44             | M44             | C <sub>34</sub> | m <sub>34</sub> | Byte 9            |

| C <sub>24</sub> | m <sub>24</sub> | C <sub>14</sub> | m <sub>14</sub> | Byte 1            |

| C <sub>45</sub> | m <sub>45</sub> | C <sub>35</sub> | m <sub>as</sub> | Byte <sup>-</sup> |

| C <sub>25</sub> | m <sub>25</sub> | C <sub>15</sub> | m <sub>15</sub> | Byte 1            |

### **Read X-Filter Coefficients**

Command (2 Bytes)

Format:

| MSB |   |   |     |   |   |   | LSB |

|-----|---|---|-----|---|---|---|-----|

| 1   | 0 | 0 | DST | 0 | 0 | 1 | 0   |

| 0   | 0 | 0 | 0   | 0 | 1 | 0 | 0   |

| C <sub>40</sub> | m <sub>40</sub> | C <sub>30</sub> | m <sub>30</sub> | Byte 1  |

|-----------------|-----------------|-----------------|-----------------|---------|

| C <sub>20</sub> | m <sub>20</sub> | C <sub>10</sub> | m <sub>10</sub> | Byte 2  |

| C <sub>41</sub> | m <sub>41</sub> | C <sub>31</sub> | m <sub>31</sub> | Byte 3  |

| C <sub>21</sub> | m <sub>21</sub> | C11             | M <sub>11</sub> | Byte 4  |

| C <sub>42</sub> | m <sub>42</sub> | C <sub>32</sub> | M <sub>32</sub> | Byte 5  |

| C <sub>22</sub> | m <sub>22</sub> | C <sub>12</sub> | m <sub>12</sub> | Byte 6  |

| C <sub>43</sub> | m <sub>43</sub> | C <sub>33</sub> | m <sub>33</sub> | Byte 7  |

| C <sub>23</sub> | m <sub>23</sub> | C <sub>13</sub> | m <sub>13</sub> | Byte 8  |

| C44             | m44             | C <sub>34</sub> | m <sub>34</sub> | Byte 9  |

| C <sub>24</sub> | m <sub>24</sub> | C <sub>14</sub> | m <sub>14</sub> | Byte 10 |

| C <sub>45</sub> | m <sub>45</sub> | C <sub>35</sub> | m <sub>as</sub> | Byte 11 |

| C <sub>25</sub> | m <sub>25</sub> | C <sub>15</sub> | M <sub>15</sub> | Byte 12 |

### **Write R-Filter Coefficients**

### Command (2 Bytes)

Format:

| MSB |          |   |     |    |   |   | LSB |

|-----|----------|---|-----|----|---|---|-----|

| 1   | 0        | 0 | DST | AM | 1 | 1 | 0   |

| 0   | 0        | 0 | 0   | 0  | 1 | 0 | 1   |

|     | <u> </u> |   |     |    |   |   |     |

### **Input Data**

|                 | m               | C <sub>30</sub> | m <sub>30</sub> | Byte 1  |

|-----------------|-----------------|-----------------|-----------------|---------|

| C <sub>40</sub> | M <sub>40</sub> |                 |                 | Byte 2  |

| C <sub>20</sub> | M <sub>20</sub> | C <sub>10</sub> | M <sub>10</sub> |         |

| C41             | m <sub>41</sub> | C <sub>31</sub> | m₃₁             | Byte 3  |

| C <sub>21</sub> | m <sub>21</sub> | C <sub>11</sub> | m <sub>11</sub> | Byte 4  |

| C <sub>42</sub> | m <sub>42</sub> | C <sub>32</sub> | m <sub>32</sub> | Byte 5  |

| C <sub>22</sub> | m <sub>22</sub> | C <sub>12</sub> | m <sub>12</sub> | Byte 6  |

| C <sub>43</sub> | m <sub>43</sub> | C <sub>33</sub> | m <sub>33</sub> | Byte 7  |

| C <sub>23</sub> | M <sub>23</sub> | C <sub>13</sub> | m <sub>13</sub> | Byte 8  |

| C44             | M44             | C <sub>34</sub> | M <sub>34</sub> | Byte 9  |

| C <sub>24</sub> | m <sub>24</sub> | C <sub>14</sub> | M <sub>14</sub> | Byte 10 |

| C <sub>45</sub> | M <sub>45</sub> | C <sub>35</sub> | m <sub>35</sub> | Byte 11 |

| C <sub>25</sub> | m <sub>25</sub> | C <sub>15</sub> | m <sub>15</sub> | Byte 12 |

### **Read R-Filter Coefficients**

### Command (2 Bytes)

Format:

| ı   | MSB |   |   |     |   |   |   | LSB |

|-----|-----|---|---|-----|---|---|---|-----|

|     | 1   | 0 | 0 | DST | 0 | 0 | 1 | 0   |

| Ì   | 0   | 0 | 0 | 0   | 0 | 1 | 0 | 1   |

| - 1 | _   |   |   |     |   |   |   |     |

| C <sub>40</sub> | m <sub>40</sub> | C <sub>30</sub> | m <sub>30</sub> | Byte 1  |

|-----------------|-----------------|-----------------|-----------------|---------|

| C <sub>20</sub> | m <sub>20</sub> | C <sub>10</sub> | m <sub>10</sub> | Byte 2  |

| C <sub>41</sub> | m <sub>41</sub> | C <sub>31</sub> | m <sub>31</sub> | Byte 3  |

| C <sub>21</sub> | m <sub>21</sub> | C <sub>11</sub> | m <sub>11</sub> | Byte 4  |

| C <sub>42</sub> | m <sub>42</sub> | C <sub>32</sub> | m <sub>32</sub> | Byte 5  |

| C <sub>22</sub> | m <sub>22</sub> | C <sub>12</sub> | m <sub>12</sub> | Byte 6  |

| C <sub>43</sub> | M <sub>43</sub> | C <sub>33</sub> | m <sub>33</sub> | Byte 7  |

| C <sub>23</sub> | m <sub>23</sub> | C <sub>13</sub> | m <sub>13</sub> | Byte 8  |

| C44             | M <sub>44</sub> | C <sub>34</sub> | M <sub>34</sub> | Byte 9  |

| C <sub>24</sub> | m <sub>24</sub> | C <sub>14</sub> | M <sub>14</sub> | Byte 10 |

| C <sub>45</sub> | m <sub>45</sub> | C <sub>35</sub> | M <sub>35</sub> | Byte 11 |

| C <sub>25</sub> | M <sub>25</sub> | C <sub>15</sub> | M <sub>15</sub> | Byte 12 |

### Write Echo Path Gain

Command (2 Bytes)

Format:

| MSB |   |   |     |    |   |   | LSB |

|-----|---|---|-----|----|---|---|-----|

| 1   | 0 | 0 | DST | АМ | 1 | 1 | 0   |

| 0   | 0 | 0 | 0   | 0  | 1 | 1 | 0   |

**Input Data**