# Am79C940

## Media Access Controller for Ethernet (MACE™)

### DISTINCTIVE CHARACTERISTICS

- Integrated Controller with Manchester encoder/decoder and 10BASE-T transceiver and AUI port

- Supports IEEE 802.3/ANSI 8802-3 and Ethernet standards

- 84-pin PLCC and 100-pin PQFP Packages

- 80-pin Thin Quad Flat Pack (TQFP) package available for space critical applications such as PCMCIA

- Modular architecture allows easy tuning to specific applications

- High speed, 16-bit synchronous host system interface with 2 or 3 cycles/transfer

- Individual transmit (136 byte) and receive (128 byte) FIFOs provide increase of system latency and support the following features:

- Automatic retransmission with no FIFO reload

- Automatic receive stripping and transmit padding (individually programmable)

- Automatic runt packet rejection

- Automatic deletion of collision frames

- Automatic retransmission with no FIFO reload

- Direct slave access to all on board configuration/status registers and transmit/ receive FIFOs

- Direct FIFO read/write access for simple interface to DMA controllers or I/O processors

### **GENERAL DESCRIPTION**

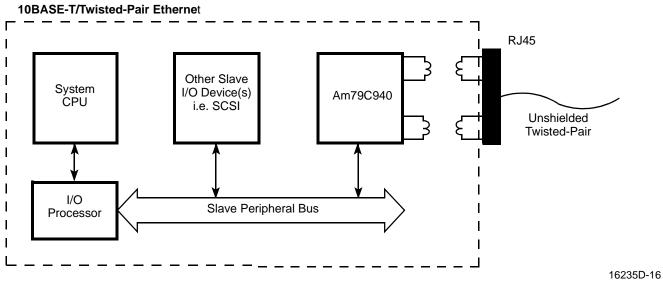

The Media Access Controller for Ethernet (MACE) chip is a CMOS VLSI device designed to provide flexibility in customized LAN design. The MACE device is specifically designed to address applications where multiple I/O peripherals are present, and a centralized or system specific DMA is required. The high speed, 16-bit synchronous system interface is optimized for an external DMA or I/O processor system, and is similar to many existing peripheral devices, such as SCSI and serial link controllers.

- Arbitrary byte alignment and little/big endian memory interface supported

- Internal/external loopback capabilities

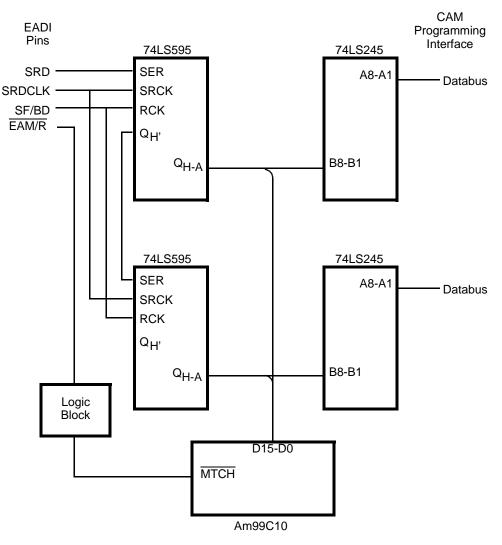

- External Address Detection Interface (EADI<sup>™</sup>) for external hardware address filtering in bridge/router applications

- JTAG Boundary Scan (IEEE 1149.1) test access port interface for board level production test

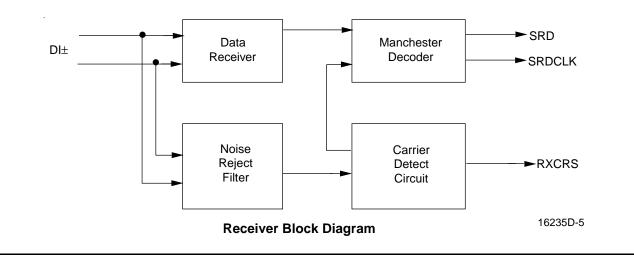

- Integrated Manchester Encoder/Decoder

- Digital Attachment Interface (DAI<sup>™</sup>) allows by-passing of differential Attachment Unit Interface (AUI)

- Supports the following types of network interface:

- AUI to external 10BASE2, 10BASE5 or 10BASE-F MAU

- DAI port to external 10BASE2, 10BASE5, 10BASE-T, 10BASE-F MAU

- General Purpose Serial Interface (GPSI) to external encoding/decoding scheme

- Internal 10BASE-T transceiver with automatic selection of 10BASE-T or AUI port

- Sleep mode allows reduced power consumption for critical battery powered applications

- 5 MHz-25 MHz system clock speed

- Support for operation in industrial temperature range (-40°C to +85°C) available in all three packages

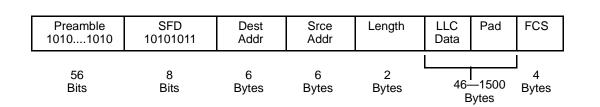

The MACE device is a slave register based peripheral. All transfers to and from the system are performed using simple memory or I/O read and write commands. In conjunction with a user defined DMA engine, the MACE chip provides an IEEE 802.3 interface tailored to a specific application. Its superior modular architecture and versatile system interface allow the MACE device to be configured as a stand-alone device or as a connectivity cell incorporated into a larger, integrated system. The MACE device provides a complete Ethernet node solution with an integrated 10BASE-T transceiver, and supports up to 25-MHz system clocks. The MACE device embodies the Media Access Control (MAC) and Physical Signaling (PLS) sub-layers of the IEEE 802.3 standard, and provides an IEEE defined Attachment Unit Interface (AUI) for coupling to an external Medium Attachment Unit (MAU). The MACE device is compliant with 10BASE2, 10BASE5, 10BASE-T, and 10BASE-F transceivers.

Additional features also enhance over-all system design. The individual transmit and receive FIFOs optimize system overhead, providing substantial latency during packet transmission and reception, and minimizing intervention during normal network error recovery. The integrated Manchester encoder/decoder eliminates the need for an external Serial Interface Adapter (SIA) in the node system. If support for an external encoding/decoding scheme is desired, the General Purpose Serial Interface (GPSI) allows direct access to/from the MAC. In addition, the Digital Attachment Interface (DAI), which is a simplified electrical attachment specification, allows implementation of MAUs that do not require DC isolation between the MAU and DTE. The DAI port can also be used to indicate transmit, receive, or collision status by connecting LEDs to the port. The MACE device also provides an External Address Detection Interface (EADI) to allow external hardware address filtering in internet working applications.

The Am79C940 MACE chip is offered in a Plastic Leadless Chip Carrier (84-pin PLCC), a Plastic Quad Flat Package (100-pin PQFP), and a Thin Quad Flat Package (TQFP 80-pin). There are several small functional and physical differences between the 80-pin TQFP and the 84-pin PLCC and 100-pin PQFP configurations. Because of the smaller number of pins in the TQFP configuration versus the PLCC configuration, four pins are not bonded out. Though the die is identical in all three package configurations, the removal of these four pins does cause some functionality differences between the TQFP and the PLCC and PQFP configurations. Depending on the application, the removal of these pins will or will not have an effect. (See section: "Pins Removed for TQFP Package and Their Effects.)

With the rise of embedded networking applications operating in harsh environments where temperatures may exceed the normal commercial temperature (0°C to +70°C) window, an industrial temperature (-40°C to +85°C) version is available in all three packages; 84-pin PLCC, 100-pin PQFP and 80-pin TQFP. The industrial temperature version of the MACE Ethernet controller is characterized across the industrial temperature range (-40°C to +85°C) within the published power supply specification (4.75 V to 5.25 V; i.e.,  $\pm$ 5% V<sub>CC</sub>). Thus, conformance of MACE performance over this temperature range is guaranteed by the design and characterization monitor.

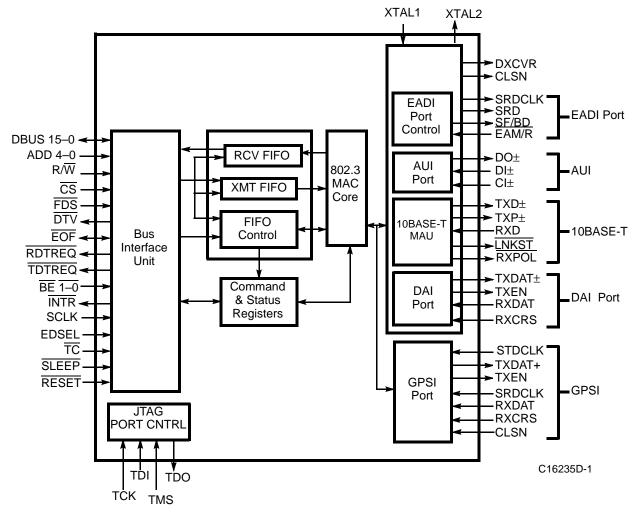

## **BLOCK DIAGRAM**

#### Notes:

- 1. Only one of the network ports AUI, 10BASE-T, DAI port or GPSI can be active at any time. Some shared signals are active regardless of which network port is active, and some are reconfigured.

- 2. The EADI port is active at all times.

## TABLE OF CONTENTS

| AM79C9401                                    |

|----------------------------------------------|

| DISTINCTIVE CHARACTERISTICS1                 |

| GENERAL DESCRIPTION                          |

| BLOCK DIAGRAM                                |

| TABLE OF CONTENTS                            |

| CONNECTION DIAGRAMS PL 084 PLCC PACKAGE7     |

| CONNECTION DIAGRAMS PQR100 PQFP PACKAGE8     |

| CONNECTION DIAGRAMS PQT080 TQFP PACKAGE9     |

| ORDERING INFORMATION                         |

| Standard Products                            |

| PIN/PACKAGE SUMMARY (PLCC)11                 |

| PIN DESCRIPTION                              |

| Network Interfaces                           |

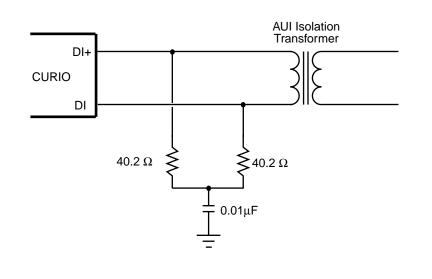

| Attachment Unit Interface (AUI)              |

| CI+/CI                                       |

| DI+/DI                                       |

| DO+/DO                                       |

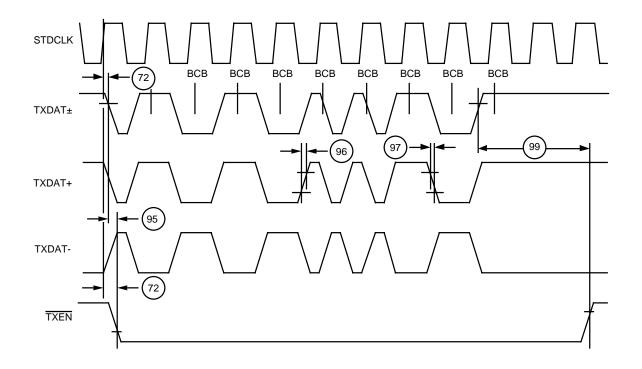

| Digital Attachment Interface (DAI)           |

| TXDAT+/TXDAT                                 |

| TXEN <b>/TXEN</b>                            |

| Transmit Enable (Output)                     |

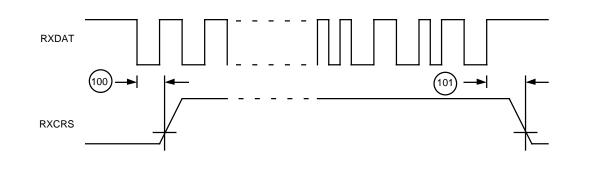

| RXDAT                                        |

| RXCRS                                        |

| DXCVR                                        |

| 10BASE-T INTERFACE                           |

| TXD+, TXD–                                   |

| TXP+, TXP–                                   |

| RXD+, RXD–                                   |

| LNKST                                        |

| RXPOL                                        |

| General Purpose Serial Interface (GPSI)      |

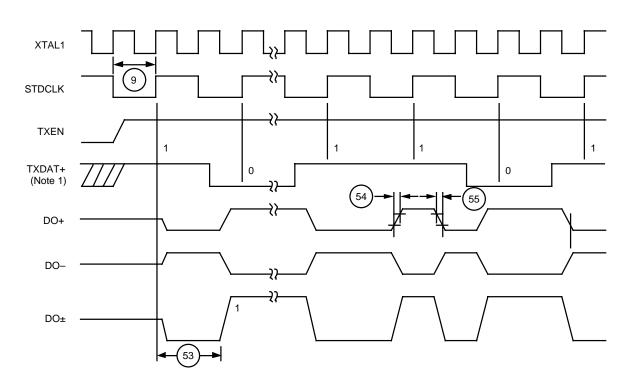

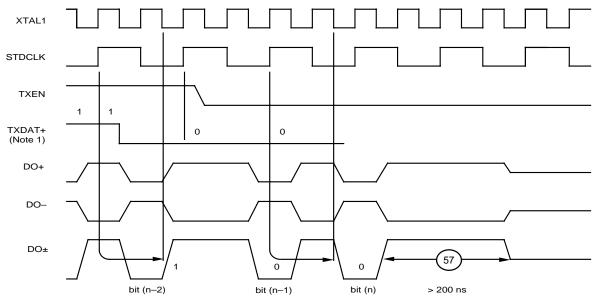

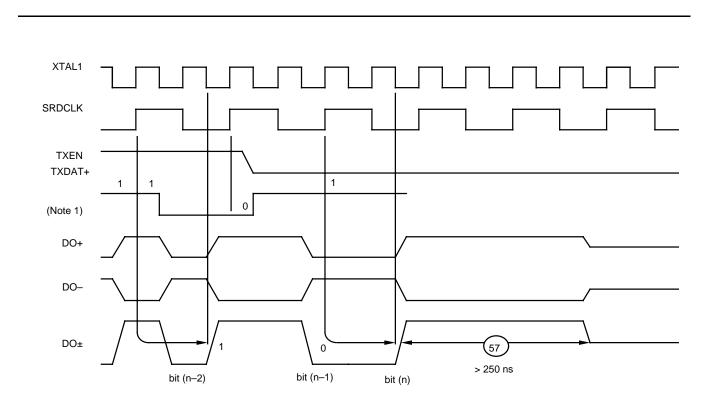

| STDCLK                                       |

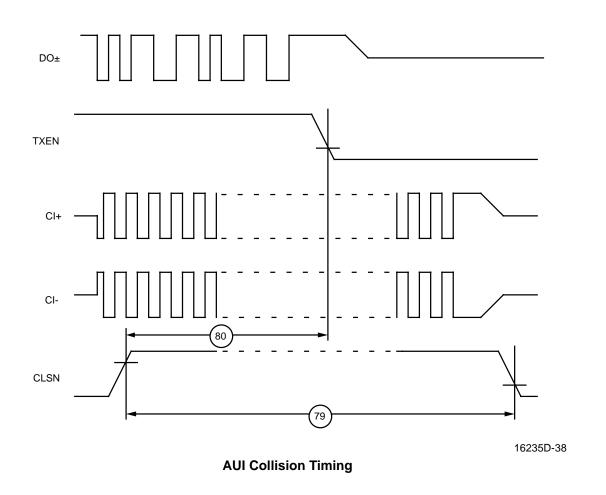

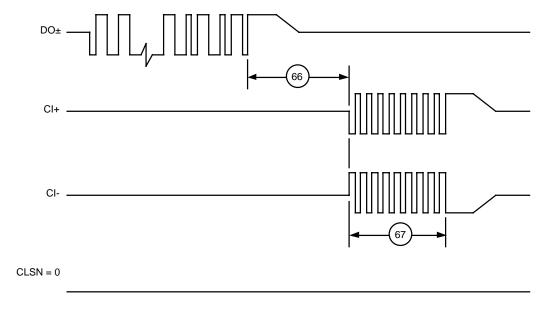

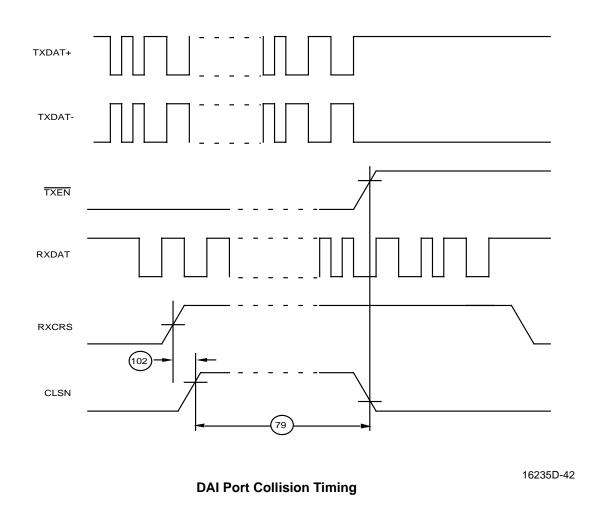

| CLSN                                         |

| External Address Detection Interface (EADI)  |

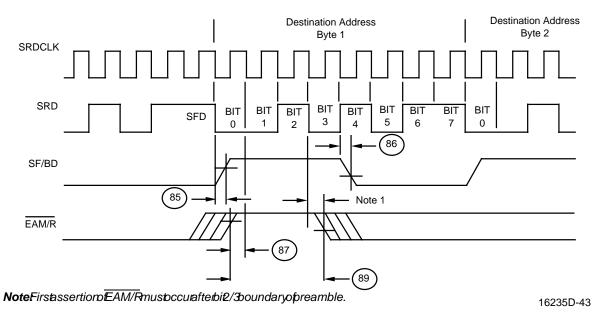

| SF/BD                                        |

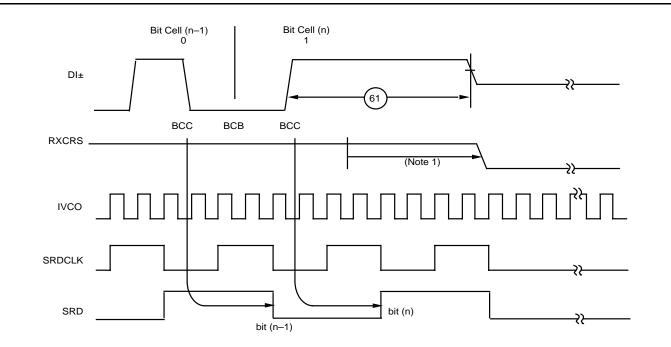

| SRD                                          |

| EAM/R                                        |

| SRDCLK                                       |

| HOST SYSTEM INTERFACE                        |

| DBUS15-0                                     |

| ADD4-0                                       |

| R/W                                          |

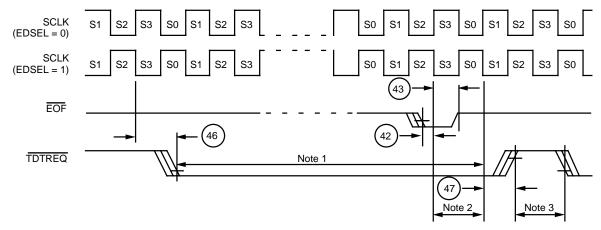

| RDTREQ                                       |

| TDTREQ                                       |

| FDS                                          |

| DTV                                          |

| EOF                                          |

| BE1–0                                        |

| CS                                           |

| INTR                                         |

| RESET                                        |

| SCLK                                         |

| EDSEL                                        |

| TC                                           |

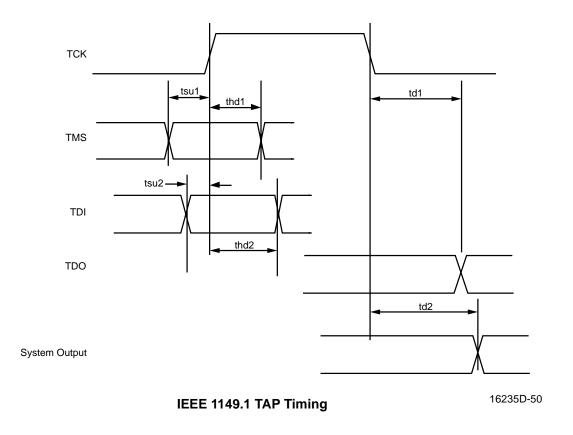

| IEEE 1149.1 TEST ACCESS PORT (TAP) INTERFACE |

| TCK                                          |

|                                              |

| TMS                                                      | 27 |

|----------------------------------------------------------|----|

| TDI                                                      | 27 |

| TDO                                                      |    |

| GENERAL INTERFACE                                        | 27 |

| XTAL1                                                    | 27 |

| XTAL2                                                    | 27 |

| SLEEP                                                    | 27 |

| Power Supply.                                            |    |

| DVDD.                                                    |    |

| DVSS                                                     |    |

| AVDD                                                     |    |

| AVSS                                                     |    |

| PIN FUNCTIONS NOT AVAILABLE WITH THE 80-PIN TQFP PACKAGE |    |

| PINS REMOVED FOR TQFP PACKAGE AND THEIR EFFECTS          | 28 |

| FUNCTIONAL DESCRIPTION                                   |    |

| Network Interfaces.                                      |    |

| System Interface                                         |    |

| DETAILED FUNCTIONS                                       |    |

| Block Level Description                                  |    |

| Bus Interface Unit (BIU).                                |    |

| BIU to FIFO Data Path.                                   |    |

| Byte Alignment For FIFO Read Operations.                 |    |

|                                                          |    |

| BIU to Control and Status Register Data Path.            |    |

| FIFO Subsystem                                           |    |

| Media Access Control (MAC)                               |    |

| Manchester Encoder/Decoder (MENDEC)                      |    |

| Attachment Unit Interface (AUI)                          |    |

| Digital Attachment Interface (DAI)                       |    |

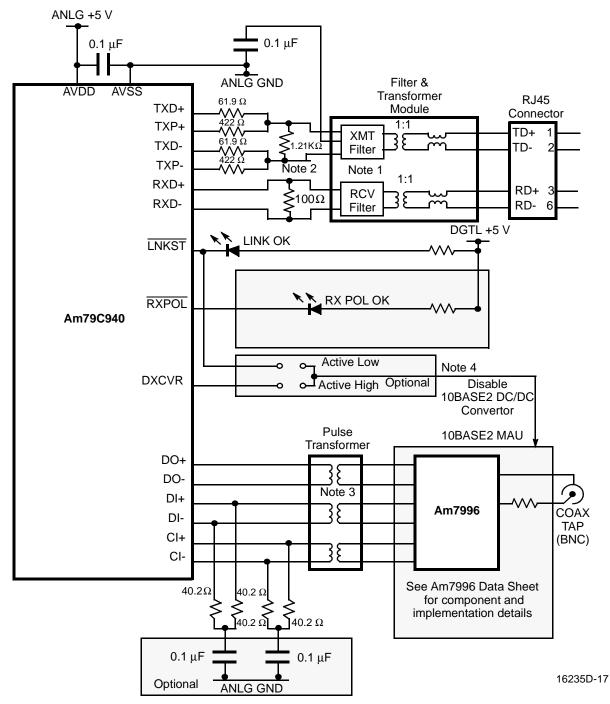

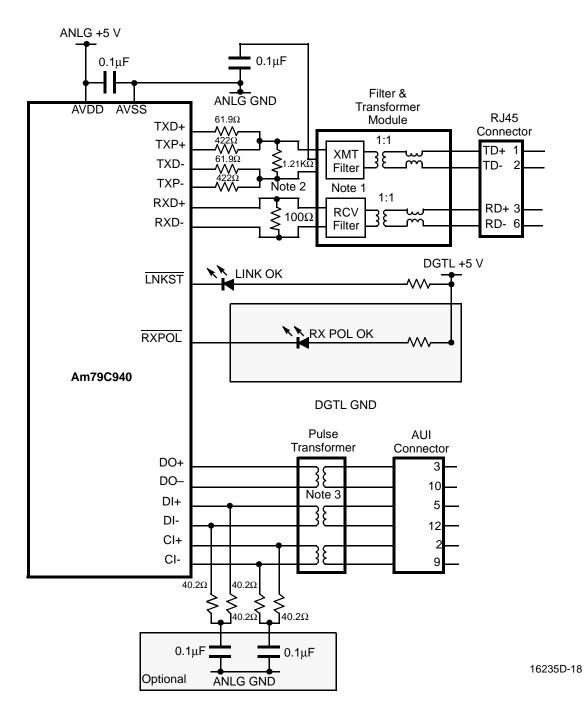

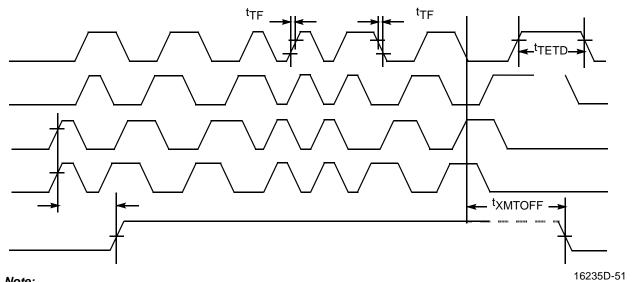

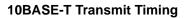

| 10BASE-T Interface                                       |    |

| Twisted Pair Transmit Function                           |    |

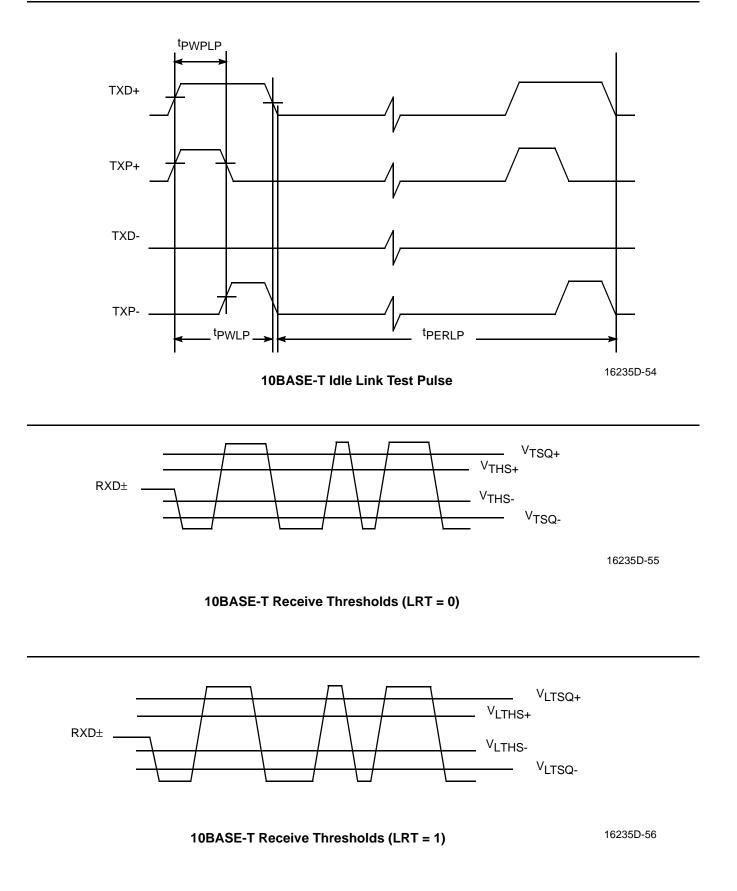

| Twisted Pair Receive Function                            |    |

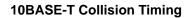

| Link Test Function                                       |    |

| Polarity Detection and Reversal                          |    |

| Twisted Pair Interface Status                            |    |

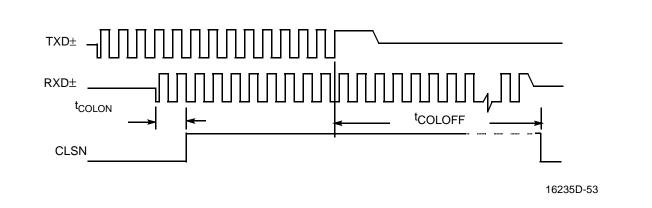

| Collision Detect Function                                |    |

| Signal Quality Error (SQE) Test (Heartbeat) Function     |    |

|                                                          |    |

| External Address Detection Interface (EADI)              |    |

| Internal/External Address Recognition Capabilities       |    |

| General Purpose Serial Interface (GPSI)                  |    |

| IEEE 1149.1 Test Access Port Interface                   |    |

| SLAVE ACCESS OPERATION                                   |    |

| Read Access                                              |    |

| Write Access                                             |    |

|                                                          |    |

| Reinitialization                                         |    |

|                                                          |    |

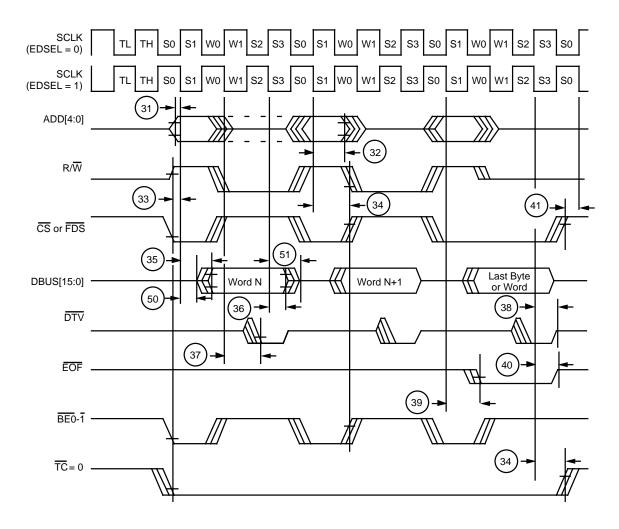

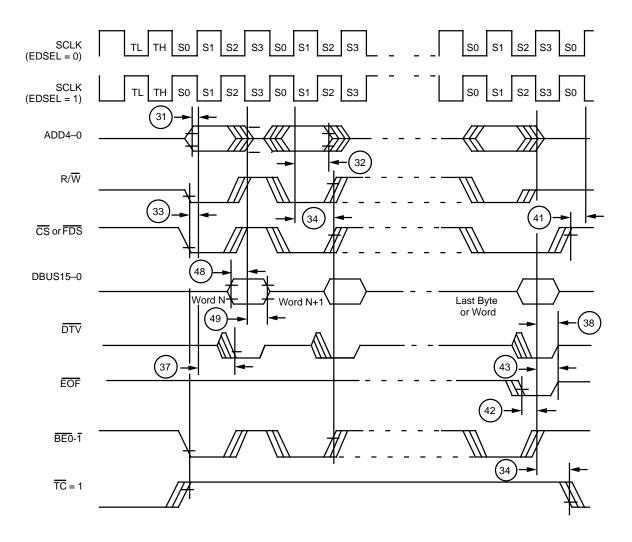

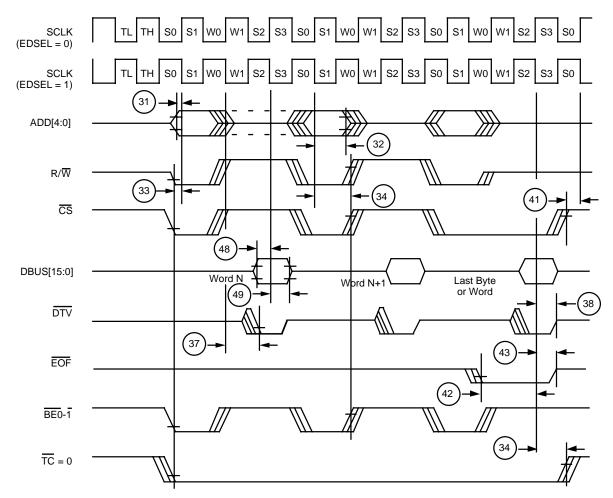

| Transmit FIFO Write                                      |    |

| Transmit Function Programming                            |    |

| Automatic Pad Generation.                                |    |

| Transmit FCS Generation                                  |    |

| Transmit Status Information                              |    |

| Transmit Exception Conditions                            |    |

| RECEIVE OPERATION                                        |    |

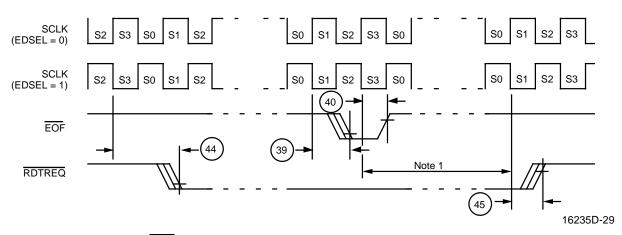

| Receive FIFO Read                                        |    |

| Receive Function Programming                             | 54 |

| Automatic Pad Stripping                                  |    |

| Receive FCS Checking                                     | 55 |

| Receive Status Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Exception Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LOOPBACK OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| USER ACCESSIBLE REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8-Bit Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Programmer's Register Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Missing Table Title?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

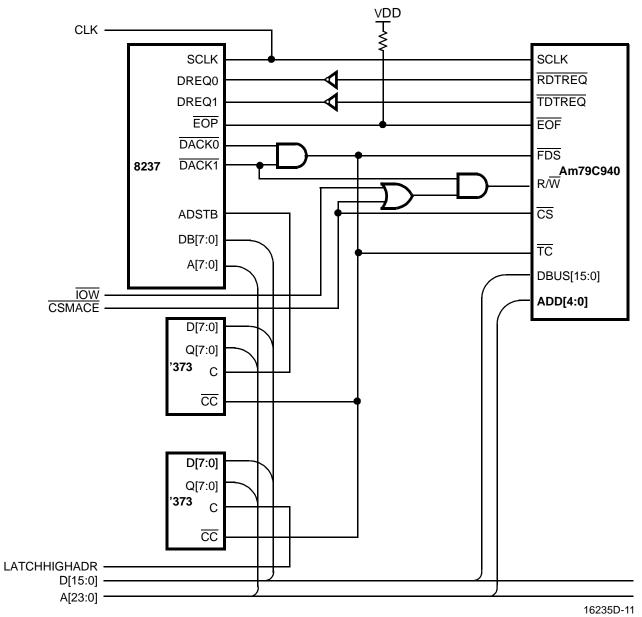

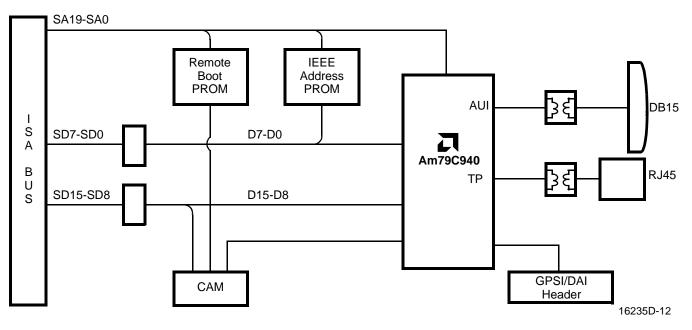

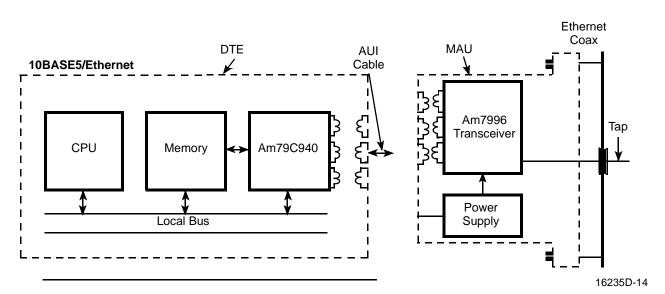

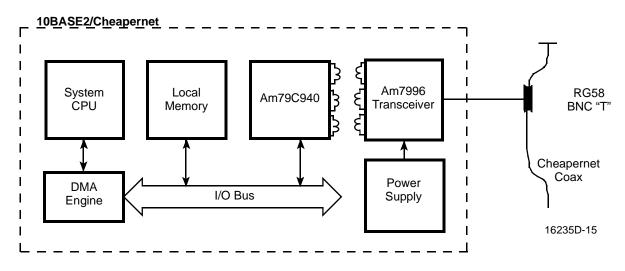

| SYSTEM APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Host System Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NETWORK INTERFACES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

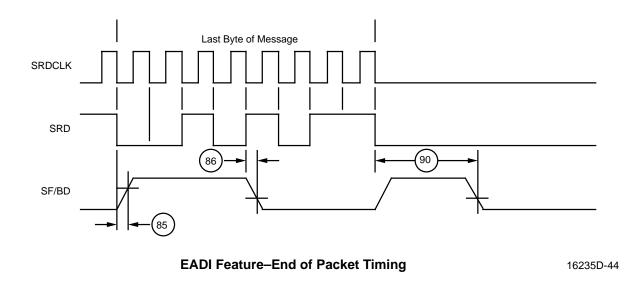

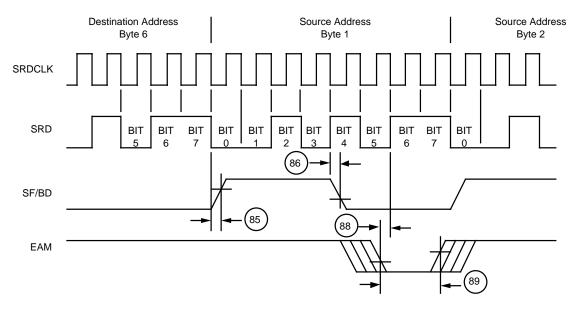

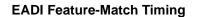

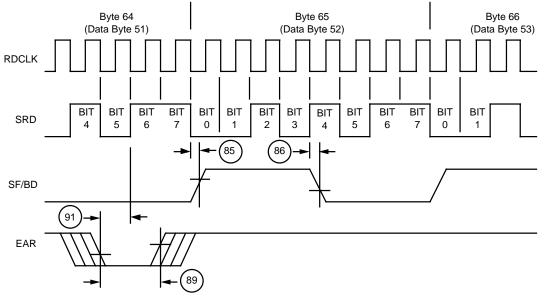

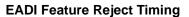

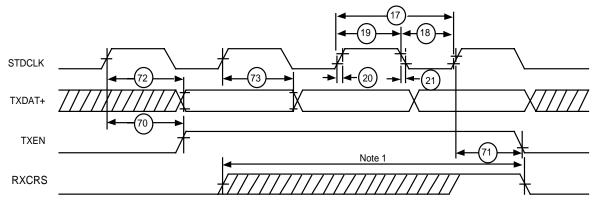

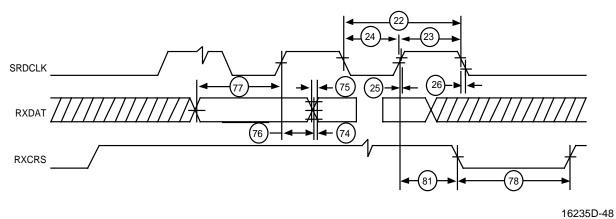

| External Address Detection Interface (EADI)83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MACE Compatible AUI Isolation Transformers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MANUFACTURER CONTACT INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OPERATING RANGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Commercial (C) Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Industrial (I) Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>CC</sub> Supply Voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME<br>BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME<br>BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME<br>BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME<br>BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME<br>BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME<br>BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME<br>BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

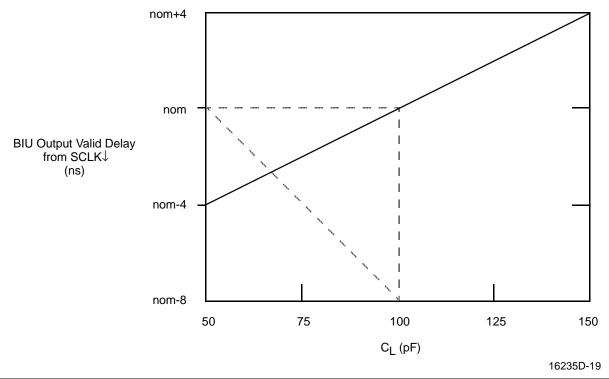

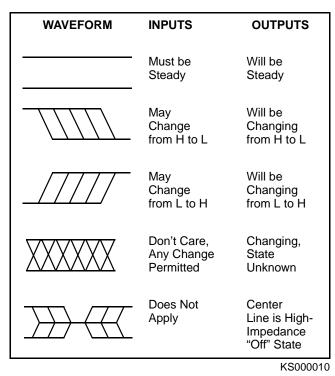

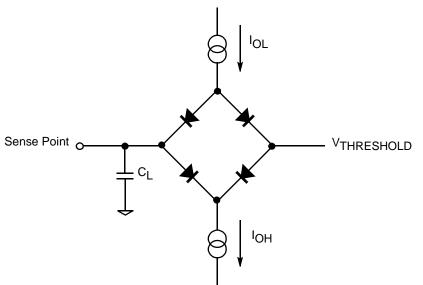

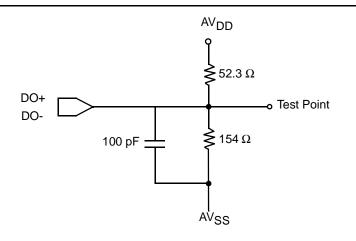

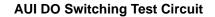

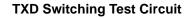

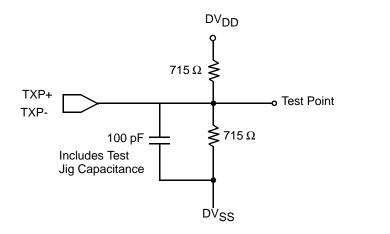

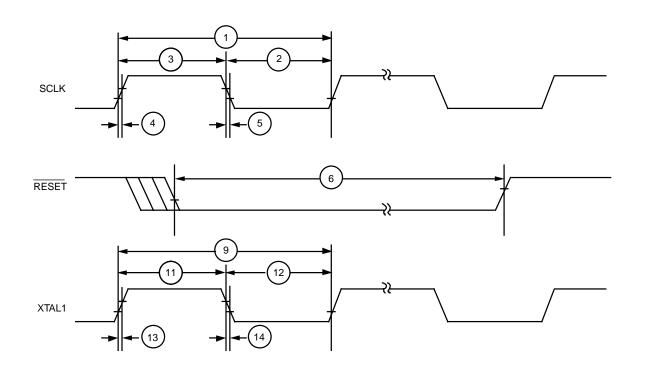

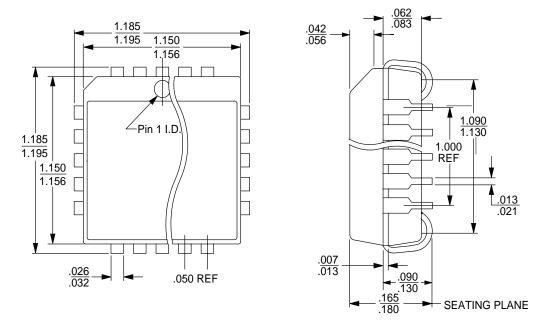

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .90         AC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .93         KEY TO SWITCHING WAVEFORMS       .97         SWITCHING TEST CIRCUITS.       .98         PHYSICAL DIMENSIONS*       .117         PL 084       .117         84-Pin Plastic Leaded Chip Carrier (measured in inches)       .117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .90         AC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .93         KEY TO SWITCHING WAVEFORMS       .97         SWITCHING TEST CIRCUITS.       .98         PHYSICAL DIMENSIONS*       .117         84-Pin Plastic Leaded Chip Carrier (measured in inches).       .118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

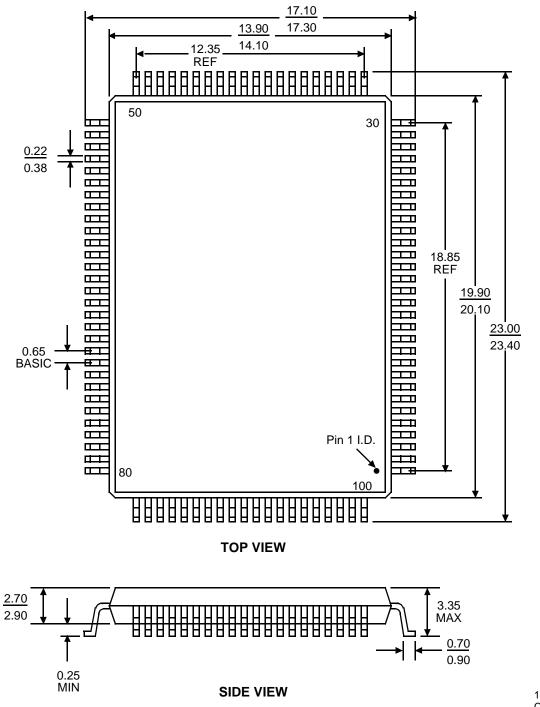

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .90         AC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .93         KEY TO SWITCHING WAVEFORMS       .97         SWITCHING TEST CIRCUITS.       .98         PHYSICAL DIMENSIONS*       .117         84-Pin Plastic Leaded Chip Carrier (measured in inches)       .118         PQR100       .118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .90         AC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .93         KEY TO SWITCHING WAVEFORMS       .97         SWITCHING TEST CIRCUITS.       .98         PHYSICAL DIMENSIONS*       .117         PL 084       .117         PHYSICAL DIMENSIONS*       .117         PHYSICAL DIMENSIONS*       .118         100-Pin Plastic Quad Flat Pack; Trimmed and Formed (measured in millimeters)       .118                                                                                                                                                                                                                                                                                                                                                                                                      |

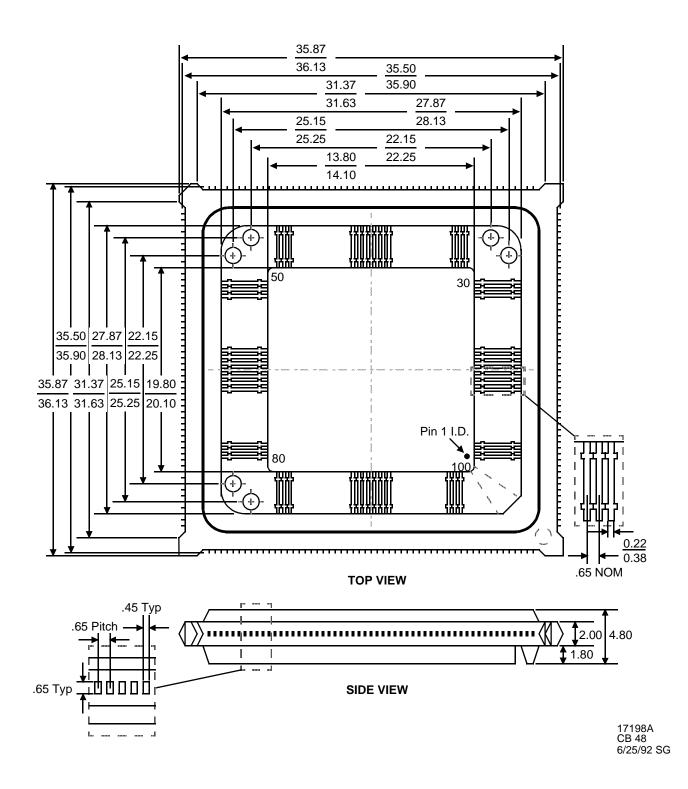

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME<br>BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.).90AC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME<br>BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.).93KEY TO SWITCHING WAVEFORMS.97SWITCHING TEST CIRCUITS98PHYSICAL DIMENSIONS*.117PL 084.117PHYSICAL DIMENSIONS*.118PQR100.118100-Pin Plastic Quad Flat Pack; Trimmed and Formed (measured in millimeters).119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .90         AC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .93         KEY TO SWITCHING WAVEFORMS       .97         SWITCHING TEST CIRCUITS.       .98         PHYSICAL DIMENSIONS*       .117         PL 084       .117         PHYSICAL DIMENSIONS*       .117         PHYSICAL DIMENSIONS*       .118         PQR100       .118         POR100       .118         PHYSICAL DIMENSIONS       .119         PQR100 100-Pin Plastic Quad Flat Pack; Trimmed and Formed (measured in millimeters)       .119                                                                                                                                                                                                                                                                                                    |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .90         AC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .93         KEY TO SWITCHING WAVEFORMS       .97         SWITCHING TEST CIRCUITS.       .98         PHYSICAL DIMENSIONS*       .117         PL 084       .117         84-Pin Plastic Leaded Chip Carrier (measured in inches)       .117         PHYSICAL DIMENSIONS*       .118         PQR100       .118         PHYSICAL DIMENSIONS*       .118         PQR100       .118         PHYSICAL DIMENSIONS       .119         PHYSICAL DIMENSIONS       .119         PHYSICAL DIMENSIONS*       .119 |

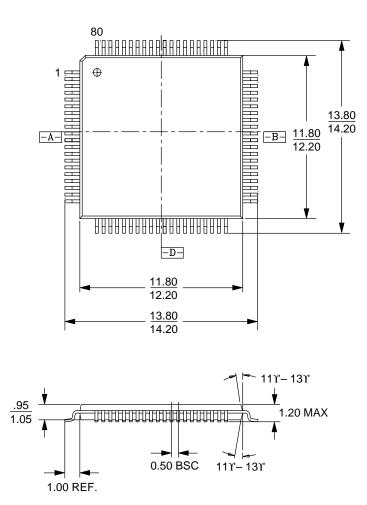

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .90         AC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .93         KEY TO SWITCHING WAVEFORMS       .97         SWITCHING TEST CIRCUITS.       .98         PHYSICAL DIMENSIONS*       .117         PL 084       .117         84-Pin Plastic Leaded Chip Carrier (measured in inches)       .118         PQR100       .118         100-Pin Plastic Quad Flat Pack; Trimmed and Formed (measured in millimeters)       .119         PQR100 100-Pin Plastic Quad Flat Pack with Molded Carrier Ring (measured in millimeters)       .119         PHYSICAL DIMENSIONS*       .119         PHYSICAL DIMENSIONS* PQT080 80-Pin Thin Quad Flat Package (measured in millimeters)       .121                                                                                                                      |

| DC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .90         AC CHARACTERISTICS (UNLESS OTHERWISE NOTED, PARAMETRIC VALUES ARE THE SAME         BETWEEN COMMERCIAL DEVICES AND INDUSTRIAL DEVICES.)       .93         KEY TO SWITCHING WAVEFORMS       .97         SWITCHING TEST CIRCUITS.       .98         PHYSICAL DIMENSIONS*       .117         PL 084       .117         84-Pin Plastic Leaded Chip Carrier (measured in inches)       .117         PHYSICAL DIMENSIONS*       .118         PQR100       .118         PHYSICAL DIMENSIONS*       .118         PQR100       .118         PHYSICAL DIMENSIONS       .119         PHYSICAL DIMENSIONS       .119         PHYSICAL DIMENSIONS*       .119 |

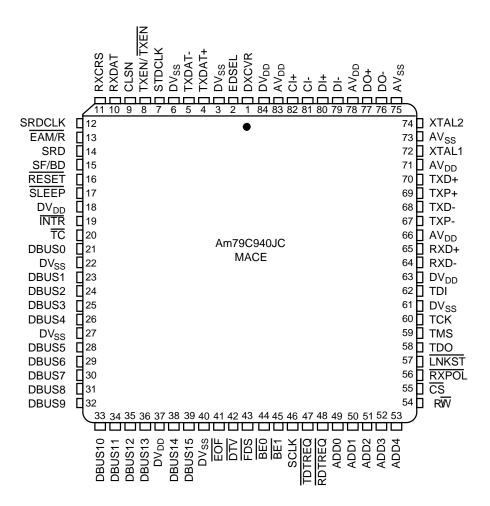

#### CONNECTION DIAGRAMS PL 084 PLCC PACKAGE

16235D-2

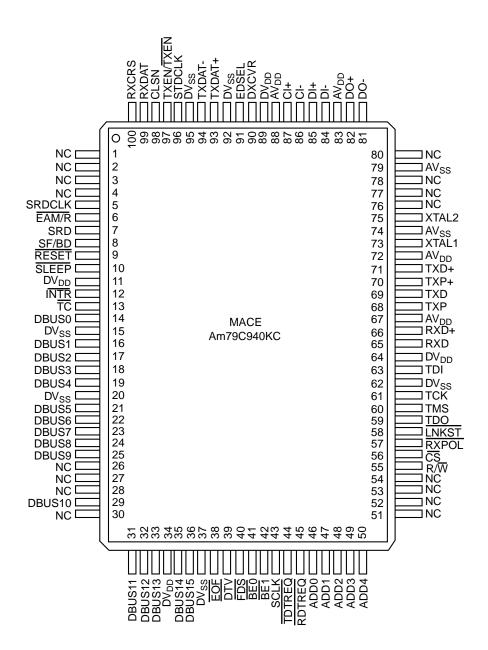

CONNECTION DIAGRAMS PQR100 PQFP PACKAGE

16235D-3

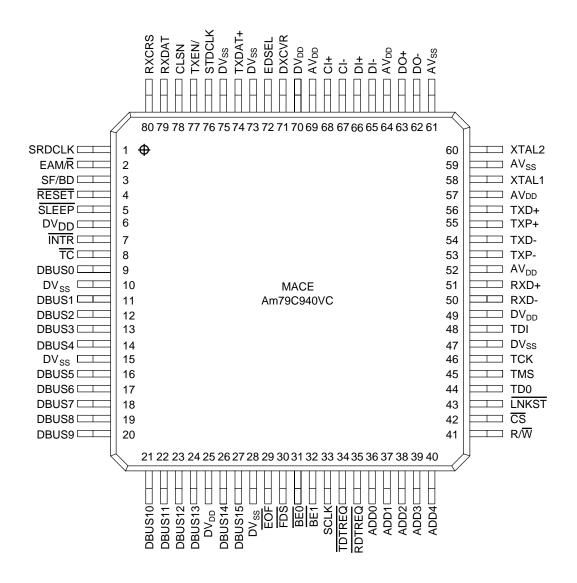

#### CONNECTION DIAGRAMS PQT080 TQFP PACKAGE

16235D-4

**Notes:** Four pin functions available on the PLCC and PQFP packages are not available with the TQFP package. (See full data sheet for description of pins not included with the 80-pin TQFP package. In particular, see section "Pin Functions not available with the 80-pin TQFP package.")

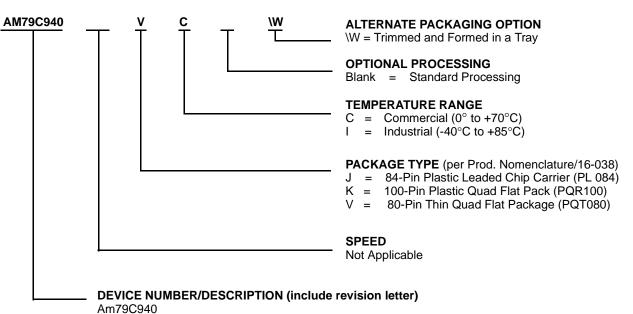

## **ORDERING INFORMATION**

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

Media Access Controller for Ethernet

| Valid Combinations |                              |  |  |  |

|--------------------|------------------------------|--|--|--|

| AM79C940           | JC, KC,<br>KC\W, VC,<br>VC\W |  |  |  |

| AM79C940           | JI, KI,<br>KI\W, VI,<br>VI\W |  |  |  |

#### Valid Combinations

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### Note:

Currently the silicon revision level of the MACE Ethernet controller is revision C0. This is designated by the marking on the package as Am79C940Bxx, where "xx" indicate package type and temperature range.

## PIN/PACKAGE SUMMARY (PLCC)

| PLCC Pin # | Pin Name         | Pin Function                  |  |  |

|------------|------------------|-------------------------------|--|--|

| 1          | DXCVR            | Disable Transceiver           |  |  |

| 2          | EDSEL            | Edge Select                   |  |  |

| 3          | DV <sub>SS</sub> | Digital Ground                |  |  |

| 4          | TXDAT+           | Transmit Data +               |  |  |

| 5          | TXDAT–           | Transmit Data –               |  |  |

| 6          | DV <sub>SS</sub> | Digital Ground                |  |  |

| 7          | STDCLK           | Serial Transmit Data Clock    |  |  |

| 8          | TXEN/TXEN        | Transmit Enable               |  |  |

| 9          | CLSN             | Collision                     |  |  |

| 10         | RXDAT            | Receive Data                  |  |  |

| 11         | RXCRS            | Receive Carrier Sense         |  |  |

| 12         | SRDCLK           | Serial Receive Data Clock     |  |  |

| 13         | EAM/R            | External Address Match/Reject |  |  |

| 14         | SRD              | Serial Receive Data           |  |  |

| 15         | SF/BD            | Start Frame/Byte Delimiter    |  |  |

| 16         | RESET            | Reset                         |  |  |

| 17         | SLEEP            | Sleep Mode                    |  |  |

| 18         | DV <sub>DD</sub> | Digital Power                 |  |  |

| 19         | INTR             | Interrupt                     |  |  |

| 20         | TC               | Timing Control                |  |  |

| 21         | DBUS0            | Data Bus0                     |  |  |

| 22         | DV <sub>SS</sub> | Digital Ground                |  |  |

| 23         | DBUS1            | Data Bus1                     |  |  |

| 24         | DBUS2            | Data Bus2                     |  |  |

| 25         | DBUS3            | Data Bus3                     |  |  |

| 26         | DBUS4            | Data Bus4                     |  |  |

| 27         | DV <sub>SS</sub> | Digital Ground                |  |  |

| 28         | DBUS5            | Data Bus5                     |  |  |

| 29         | DBUS6            | Data Bus6                     |  |  |

| 30         | DBUS7            | Data Bus7                     |  |  |

| 31         | DBUS8            | Data Bus8                     |  |  |

| 32         | DBUS9            | Data Bus9                     |  |  |

| 33         | DBUS10           | Data Bus10                    |  |  |

| 34         | DBUS11           | Data Bus11                    |  |  |

| 35         | DBUS12           | Data Bus12                    |  |  |

| 36         | DBUS13           | Data Bus13                    |  |  |

| 37         | DV <sub>DD</sub> | Digital Power                 |  |  |

| 38         | DBUS14           | Data Bus14                    |  |  |

| 39         | DBUS15           | Data Bus15                    |  |  |

| 40         | DV <sub>SS</sub> | Digital Ground                |  |  |

| 41         | EOF              | End Of Frame                  |  |  |

| 42         | DTV              | Data Transfer Valid           |  |  |

| 43         | FDS              | FIFO Data Strobe              |  |  |

| 44         | BE0              | Byte Enable0                  |  |  |

## PIN/PACKAGE SUMMARY (continued)

| PLCC Pin # | Pin Name         | Pin Function                   |  |  |

|------------|------------------|--------------------------------|--|--|

| 45         | BE1              | Byte Enable 1                  |  |  |

| 46         | SCLK             | System Clock                   |  |  |

| 47         | TDTREQ           | Transmit Data Transfer Request |  |  |

| 48         | RDTREQ           | Receive Data Transfer Request  |  |  |

| 49         | ADD0             | Address0                       |  |  |

| 50         | ADD1             | Address1                       |  |  |

| 51         | ADD2             | Address2                       |  |  |

| 52         | ADD3             | Address3                       |  |  |

| 53         | ADD4             | Address4                       |  |  |

| 54         | R/W              | Read/Write                     |  |  |

| 55         | CS               | Chip Select                    |  |  |

| 56         | RXPOL            | Receive Polarity               |  |  |

| 57         | LNKST            | Link Status                    |  |  |

| 58         | TDO              | Test Data Out                  |  |  |

| 59         | TMS              | Test Mode Select               |  |  |

| 60         | TCK              | Test Clock                     |  |  |

| 61         | DV <sub>SS</sub> | Digital Ground                 |  |  |

| 62         | TDI              | Test Data Input                |  |  |

| 63         | DV <sub>DD</sub> | Digital Power                  |  |  |

| 64         | RXD-             | Receive Data-                  |  |  |

| 65         | RXD+             | Receive Data+                  |  |  |

| 66         | AV <sub>DD</sub> | Analog Power                   |  |  |

| 67         | TXP-             | Transmit Pre-distortion        |  |  |

| 68         | TXD-             | Transmit Data-                 |  |  |

| 69         | TXP+             | Transmit Pre-distortion+       |  |  |

| 70         | TXD+             | Transmit Data+                 |  |  |

| 71         | AV <sub>DD</sub> | Analog Power                   |  |  |

| 72         | XTAL1            | Crystal Output                 |  |  |

| 73         | AV <sub>SS</sub> | Analog Ground                  |  |  |

| 74         | XTAL2            | Crystal Output                 |  |  |

| 75         | AV <sub>SS</sub> | Analog Ground                  |  |  |

| 76         | DO-              | Data Out-                      |  |  |

| 77         | DO+              | Data Out+                      |  |  |

| 78         | AV <sub>DD</sub> | Analog Power                   |  |  |

| 79         | DI–              | Data In–                       |  |  |

| 80         | DI+              | Data In+                       |  |  |

| 81         | CI–              | Control In-                    |  |  |

| 82         | CI+              | Control In+                    |  |  |

| 83         | AV <sub>DD</sub> | Analog Power                   |  |  |

| 84         | DV <sub>DD</sub> | Digital Power                  |  |  |

## PIN/PACKAGE SUMMARY (PQFP) (continued)

| PQFP Pin # | Pin Name         | Pin Function                  |  |

|------------|------------------|-------------------------------|--|

| 1          | NC               | No Connect                    |  |

| 2          | NC               | No Connect                    |  |

| 3          | NC               | No Connect                    |  |

| 4          | NC               | No Connect                    |  |

| 5          | SHDCLK           | Serial Receive Data Clock     |  |

| 6          | EAM/R            | External Address Match/Reject |  |

| 7          | SRD              | Serial Receive Data           |  |

| 8          | SF/BD            | Start Frame/Byte Delimiter    |  |

| 9          | RESET            | Reset                         |  |

| 10         | SLEEP            | Sleep Mode                    |  |

| 11         | DVDD             | Digital Power                 |  |

| 12         | INTR             | Interrupt                     |  |

| 13         | TC               | Timing Control                |  |

| 14         | DBUS0            | Data Bus0                     |  |

| 15         | DV <sub>SS</sub> | Digital Ground                |  |

| 16         | DBUS1            | Data Bus1                     |  |

| 17         | DBUS2            | Data Bus2                     |  |

| 18         | DBUS3            | Data Bus3                     |  |

| 19         | DBUS4            | Data Bus4                     |  |

| 20         | DVSS             | Digital Ground                |  |

| 21         | DBUS5            | Data Bus5                     |  |

| 22         | DBUS6            | Data Bus6                     |  |

| 23         | DBUS7            | Data Bus7                     |  |

| 24         | DBUS8            | Data Bus8                     |  |

| 25         | DBUS9            | Data Bus9                     |  |

| 26         | NC               | No Connect                    |  |

| 27         | NC               | No Connect                    |  |

| 28         | NC               | No Connect                    |  |

| 29         | DBUS10           | Data Bus10                    |  |

| 30         | NC               | No Connect                    |  |

| 31         | DBUS11           | Data Bus11                    |  |

| 32         | DBUS12           | Data Bus12                    |  |

| 33         | DBUS13           | Data Bus13                    |  |

| 34         | DV <sub>DD</sub> | Digital Power                 |  |

| 35         | DBUS14           | Data Bus14                    |  |

| 36         | DBUS15           | Data Bus15                    |  |

| 37         | DVSS             | Digital Ground                |  |

| 38         | EOF              | End of Frame                  |  |

| 39         | DTV              | Data Transfer Valid           |  |

| 40         | FDS              | FIFO Data Strobe              |  |

| 41         | BEO              | Byte Enable0                  |  |

| 42         | BE1              | Byte Enable1                  |  |

## PIN/PACKAGE SUMMARY (continued)

| PQFP Pin # | Pin Name         | Pin Function                   |

|------------|------------------|--------------------------------|

| 43         | SCLK             | System Clock                   |

| 44         | TDTREQ           | Transmit Data Transfer Request |

| 45         | RDTREQ           | Receive Data Transfer Request  |

| 46         | ADD0             | Address0                       |

| 47         | ADD1             | Address1                       |

| 48         | ADD2             | Address2                       |

| 49         | ADD3             | Address3                       |

| 50         | ADD4             | Address4                       |

| 51         | NC               | No Connect                     |

| 52         | NC               | No Connect                     |

| 53         | NC               | No Connect                     |

| 54         | NC               | No Connect                     |

| 55         | R/W              | Read/Write                     |

| 56         | CS               | Chip Select                    |

| 57         | RXPOL            | Receive Polarity               |

| 58         | LNKST            | Link Status                    |

| 59         | TDO              | Test Data Out                  |

| 60         | TMS              | Test Mode Select               |

| 61         | ТСК              | Test Clock                     |

| 62         | DV <sub>SS</sub> | Digital Ground                 |

| 63         | TDI              | Test Data Input                |

| 64         | DV <sub>DD</sub> | Digital Power                  |

| 65         | RXD-             | Receive Data-                  |

| 66         | RXD+             | Receive Data+                  |

| 67         | AV <sub>DD</sub> | Analog Power                   |

| 68         | TXP-             | Transmit Pre-distortion-       |

| 69         | TXD-             | Transmit Data-                 |

| 70         | TXP+             | Transmit Pre-distortion+       |

| 71         | TXD+             | Transmit Data+                 |

| 72         | AV <sub>DD</sub> | Analog Power                   |

| 73         | XTAL1            | Crystal Input                  |

| 74         | AV <sub>SS</sub> | Analog Ground                  |

| 75         | XTAL2            | Crystal Output                 |

| 76         | NC               | No Connect                     |

| 77         | NC               | No Connect                     |

| 78         | NC               | No Connect                     |

| 79         | AV <sub>SS</sub> | Analog Ground                  |

| 80         | NC               | No Connect                     |

| 81         | DO-              | Data Out-                      |

| 82         | DO+              | Data Out+                      |

| 83         | AV <sub>DD</sub> | Analog Power                   |

| 84         | DI–              | Data In-                       |

| 85         | DI+              | Data In+                       |

## PIN/PACKAGE SUMMARY (continued)

| PQFP Pin # | Pin Name         | Pin Function               |

|------------|------------------|----------------------------|

| 86         | CI–              | Control In-                |

| 87         | CI+              | Control In+                |

| 88         | AV <sub>DD</sub> | Analog Power               |

| 89         | DV <sub>DD</sub> | Digital Power              |

| 90         | DXCVR            | Disable Transceiver        |

| 91         | EDSEL            | Edge Select                |

| 92         | DV <sub>SS</sub> | Digital Ground             |

| 93         | TXDAT+           | Transmit Data +            |

| 94         | TXDAT–           | Transmit Data-             |

| 95         | DV <sub>SS</sub> | Digital Ground             |

| 96         | STDCLK           | Serial Transmit Data Clock |

| 97         | TXEN/TXEN        | Transmit Enable            |

| 98         | CLSN             | Collision                  |

| 99         | RXDAT            | Receive Data               |

| 100        | RXCRS            | Receive Carrier Sense      |

## PIN/PACKAGE SUMMARY (TQFP) (continued)

| TQFP # | Pin Name | Pin Function                   | TQFP<br>Pin Number | Pin Name  | Pin Function               |

|--------|----------|--------------------------------|--------------------|-----------|----------------------------|

| 1      | SRDCLK   | Serial Receive Data Clock      | 41                 | R/W       | Read/Write                 |

| 2      | EAM/R    | External Address Match/Reject  | 42                 | CS        | Chip/Select                |

| 3      | SF/BD    | Start Frame/Byte Delimiter     | 43                 | LNKST     | Link Status                |

| 4      | RESET    | Reset                          | 44                 | TDO       | Test Data Out              |

| 5      | SLEEP    | Sleep Mode                     | 45                 | TMS       | Test Mode Select           |

| 6      | DVDD     | Digital Power                  | 46                 | ТСК       | Text Clock                 |

| 7      | INTR     | Interrupt                      | 47                 | DVSS      | Digital Ground             |

| 8      | TC       | Timing Control                 | 48                 | TDI       | Test Data Input            |

| 9      | DBUS0    | Data Bus0                      | 49                 | DVDD      | Digital Power              |

| 10     | DVSS     | Digital Ground                 | 50                 | RXD-      | Receive Data-              |

| 11     | DBUS1    | Data Bus1                      | 51                 | RXD+      | Receive Data+              |

| 12     | DBUS2    | Data Bus2                      | 52                 | AVDD      | Analog Power               |

| 13     | DBUS3    | Data Bus3                      | 53                 | TXP-      | Transmit Pre-distortion-   |

| 14     | DBUS4    | Data Bus4                      | 54                 | TXD-      | Transmit Data-             |

| 15     | DVSS     | Digital Ground                 | 55                 | TXP+      | Transmit Pre-distortion+   |

| 16     | DBUS5    | Data Bus5                      | 56                 | TXD+      | Transmit Data+             |

| 17     | DBUS6    | Data Bus6                      | 57                 | AVDD      | Analog Power               |

| 18     | DBUS7    | Data Bus7                      | 58                 | XTAL1     | Crystal Output             |

| 19     | DBUS8    | Data Bus8                      | 59                 | AVSS      | Analog Ground              |

| 20     | DBUS9    | Data Bus9                      | 60                 | XTAL2     | Crystal Output             |

| 21     | DBUS10   | Data Bus10                     | 61                 | AVSS      | Analog Ground              |

| 22     | DBUS11   | Data Bus11                     | 62                 | DO-       | Data Out–                  |

| 23     | DBUS12   | Data Bus12                     | 63                 | DO+       | Data Out+                  |

| 24     | DBUS13   | Data Bus13                     | 64                 | AVDD      | Analog Power               |

| 25     | DVDD     | Digital Power                  | 65                 | DI–       | Data In-                   |

| 26     | DBUS14   | Data Bus14                     | 66                 | DI+       | Data Out+                  |

| 27     | DBUS15   | Data Bus15                     | 67                 | CI–       | Control In-                |

| 28     | DVSS     | Digital Ground                 | 68                 | Cl+       | Control In+                |

| 29     | EOF      | End of Frame                   | 69                 | AVDD      | Analog Power               |

| 30     | FDS      | FIFO Data Strobe               | 70                 | DVDD      | Digital Power              |

| 31     | BE0      | Byte Enable0                   | 71                 | DXCVR     | Disable Transceiver        |

| 32     | BE1      | Byte Enable1                   | 72                 | EDSEL     | Edge Select                |

| 33     | SCLK     | System Clock                   | 73                 | DVSS      | Digital Ground             |

| 34     | TDTREQ   | Transmit Data Transfer Request | 74                 | TXDAT+    | Transmit Data+             |

| 35     | RDTREQ   | Receive Data Transfer Request  | 75                 | DVSS      | Digital Ground             |

| 36     | ADD0     | Address0                       | 76                 | STDCLK    | Serial Transmit Data Clock |

| 37     | ADD1     | Address1                       | 77                 | TXEN/TXEN | Transmit Enable            |

| 38     | ADD2     | Address2                       | 78                 | CLSN      | Collision                  |

| 39     | ADD3     | Address3                       | 79                 | RXDAT     | Receive Data               |

| 40     | ADD4     | Address4                       | 80                 | RXCRS     | Receive Carrier Sense      |

## **PIN SUMMARY**

| Pin Name        | Pin Function               | Туре | Active | Comment                             |

|-----------------|----------------------------|------|--------|-------------------------------------|

| Attachment Uni  | t Interface (AUI)          |      | 1      |                                     |

| DO+/DO-         | Data Out                   | 0    |        | Pseudo-ECL                          |

| DI+/DI–         | Data In                    | I    |        | Pseudo-ECL                          |

| CI+/CI-         | Control In                 | I    |        | Pseudo-ECL                          |

| RXCRS           | Receive Carrier Sense      | I/O  | High   | TTL output. Input in DAI, GPSI port |

| TXEN            | Transmit Enable            | 0    | High   | TTL. TXEN in DAI port               |

| CLSN            | Collision                  | I/O  | High   | TTL output. Input in GPSI           |

| DXCVR           | Disable Transceiver        | 0    | Low    | TTL low                             |

| STDCLK          | Serial Transmit Data Clock | I/O  |        | Output. Input in GPSI               |

| SRDCLK          | Serial Receive Data Clock  | I/O  |        | Output. Input in GPSI               |

| Digital Attachm | ent Interface (DAI)        |      | 1      |                                     |

| TXDAT+          | Transmit Data +            | 0    | High   | TTL. See also GPSI                  |

| TXDAT–          | Transmit Data-             | 0    | Low    | TTL                                 |

| TXEN            | Transmit Enable            | 0    | Low    | TTL. See TXEN in GPSI               |

| RXDAT           | Receive Data               | I    |        | TTL. See also GPSI                  |

| RXCRS           | Receive Carrier Sense      | I/O  | High   | TTL input. Output in AUI            |

| CLSN            | Collision                  | I/O  | High   | TTL output. Input in GPSI           |

| DXCVR           | Disable Transceiver        | 0    | High   | TTL high                            |

| STDCLK          | Serial Transmit Data Clock | I/O  |        | Output. Input in GPSI               |

| SRDCLK          | Serial Receive Data Clock  | I/O  |        | Output. Input in GPSI               |

| 10BASE-T Inter  | face                       |      |        |                                     |

| TXD+/TXD-       | Transmit Data              | 0    |        |                                     |

| TXP+/TXP-       | Transmit Pre-distortion    | 0    |        |                                     |

| RXD+/RXD-       | Receive Data               | I    |        |                                     |

| LNKST           | Link Status                | 0    | Low    | Open Drain                          |

| RXPOL           | Receive Polarity           | 0    | Low    | Open Drain                          |

| TXEN            | Transmit Enable            | 0    | High   | TTL. TXEN in DAI port               |

| RXCRS           | Receive Carrier Sense      | I/O  | High   | TTL output. Input in DAI, GPSI port |

| CLSN            | Collision                  | I/O  | High   | TTL output. Input in GPSI           |

| DXCVR           | Disable Transceiver        | 0    | High   | TTL high                            |

| STDCLK          | Serial Transmit Data Clock | I/O  |        | Output. Input in GPSI               |

| SRDCLK          | Serial Receive Data Clock  | I/O  |        | Output. Input in GPSI               |

| General Purpos  | e Serial Interface (GPSI)  |      |        |                                     |

| STDCLK          | Serial Transmit Data Clock | I/O  |        | Input                               |

| TXDAT+          | Transmit Data +            | 0    | High   | TTL. See also DAI port              |

| TXEN            | Transmit Enable            | 0    | High   | TTL. TXEN in DAI port               |

| SRDCLK          | Serial Receive Data Clock  | I/O  |        | Input. See also EADI port           |

| RXDAT           | Receive Data               | I    |        | TTL. See also DAI port              |

| RXCRS           | Receive Carrier Sense      | I/O  | High   | TTL input. Output in AUI            |

| CLSN            | Collision                  | I/O  | High   | TTL input                           |

| DXCVR           | Disable Transceiver        | 0    | Low    | TTL low                             |

## PIN SUMMARY (continued)

| Pin Name         | Pin Function                                | Туре | Active   | Comment               |  |  |  |

|------------------|---------------------------------------------|------|----------|-----------------------|--|--|--|

| External Add     | External Address Detection Interface (EADI) |      |          |                       |  |  |  |

| SF/BD            | Start Frame/Byte Delimiter                  | 0    | High     |                       |  |  |  |

| SRD              | Serial Receive Data                         | 0    | High     |                       |  |  |  |

| EAM/R            | External Address Match/Reject               | I    | Low      |                       |  |  |  |

| SRDCLK           | Serial Receive Data Clock                   | I/O  |          | Output except in GPSI |  |  |  |

| Host System      | Interface                                   |      |          | -                     |  |  |  |

| DBUS 15-0        | Data Bus                                    | I/O  | High     |                       |  |  |  |

| ADD4–0           | Address                                     | I    | High     |                       |  |  |  |

| R/W              | Read/Write                                  | I    | High/Low |                       |  |  |  |

| RDTREQ           | Receive Data Transfer Request               | 0    | Low      |                       |  |  |  |

| TDTREQ           | Transmit Data Transfer Request              | 0    | Low      |                       |  |  |  |

| DTV              | Data Transfer Valid                         | 0    | Low      | Tristate              |  |  |  |

| EOF              | End Of Frame                                | I/O  | Low      |                       |  |  |  |

| BE0              | Byte Enable 0                               | I    | Low      |                       |  |  |  |