# LIBERTY AM99C58/AM99C59

SRAIL 16K(4K XV) 3-State

DISTINCTIVE CHARACTERISTICS

# **PRELIMINARY**

- 4096 x 4 organization

- High Speed

- 20 ns tAA Maximum

- 10 ns tACS Maximum (Am99C59)

- Separate data inputs and outputs

- Automatic power-down when deselected (Am99C58)

- Maximum power dissipation: 990 mW

- Maximum standby power dissipation: 220 mW (Am99C58)

- TTL-compatible inputs and outputs

- Single +5-V ±10% power supply

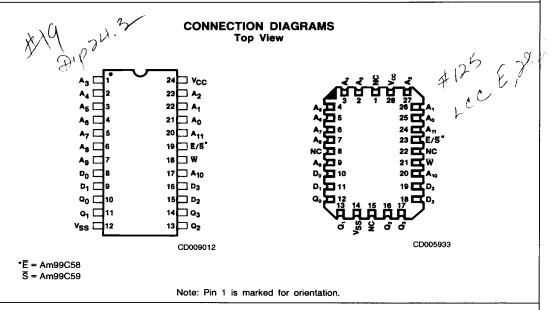

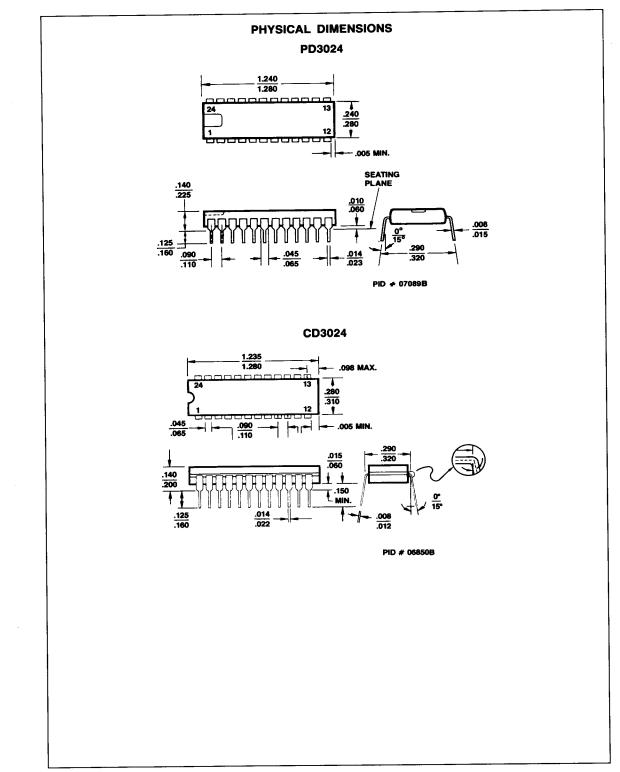

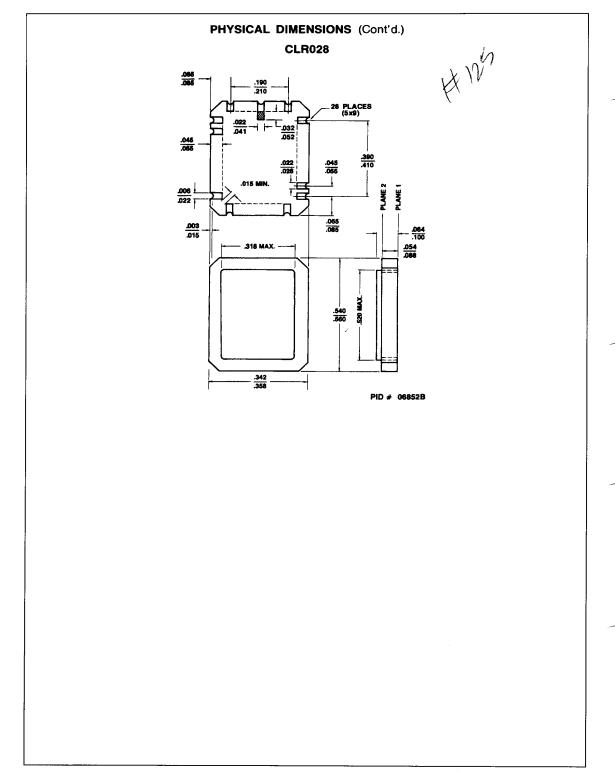

- Slim 24-pin, 300-mil DIP and 28-pin ceramic leadless

### **GENERAL DESCRIPTION**

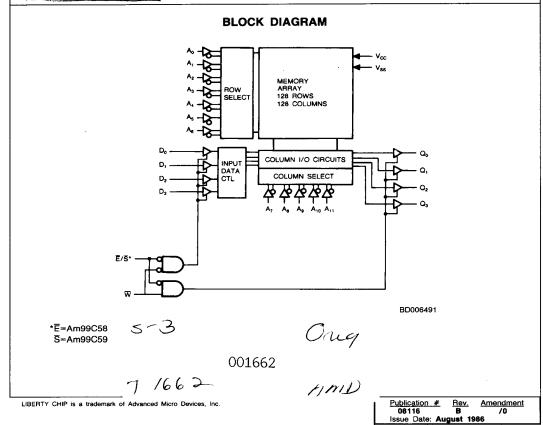

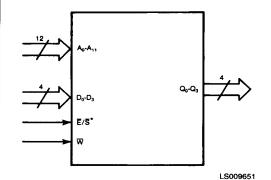

The Am99C58 and Am99C59 are high-performance CMOS Static RAMs organized as 4096 words by 4 bits. They are manufactured using an advanced high-performance CMOS process that combines high speed with low-power consumption and increased reliability.

Both devices feature access times as fast as 20 ns and separate data inputs and outputs. The Am99C58 and Am99C59 operate from a single 5-V supply and all inputs and outputs are fully TTL-compatible. The Am99C58 provides a Chip Enable (E) function that automatically powers down the device when deselected. The Am99C59 provides a Chip Select (S) function that offers a chip select access time of 10 ns.

Two inputs,  $\overline{E}/\overline{S}^*$  and  $\overline{W}$ , are used to control the device. Chip Enable/Select  $(\overline{E}/\overline{S})^*$  selects the device for operation and provides for easy memory expansion. Write Enable  $(\overline{W})$ controls write and read operations. The data outputs will be in a high-impedance state when E/S\* is HIGH, or W is LOW.

The Am99C58 and Am99C59 are packaged in a slim 24pin, 300-mil DIP or 28-pin ceramic leadless chip carrier.

## PRODUCT SELECTOR GUIDE

| Part Number   |                            | Am99C58 |       |       |     | Am99C59 |     |     |     |

|---------------|----------------------------|---------|-------|-------|-----|---------|-----|-----|-----|

| Part Number   | -20                        | -25     | -35   | -45   | -20 | -25     | -35 | -45 |     |

| Access Time M | 20                         | 20 25   | 25 35 | 15 45 | 20  | 25      | 35  | 45  |     |

| 0 to +70°C    | I <sub>CC</sub> Max. (mA)  | 180     | 180   | 160   | 160 | 180     | 180 | 160 | 160 |

|               | I <sub>SB</sub> Max. (mA)  | 40      | 40    | 40    | 40  | _       |     | _   | _   |

|               | I <sub>SBC</sub> Max. (mA) | 10      | 10    | 10    | 10  | _       | _   | _   | _   |

|               | I <sub>CC</sub> Max. (mA)  | _       | _     | 180   | 180 |         | _   | 180 | 180 |

| -55 to +125°C | I <sub>SB</sub> Max. (mA)  | _       | _     | 40    | 40  | _       | _   |     | _   |

|               | I <sub>SBC</sub> Max. (mA) | _       | _     | 10    | 10  | _       |     |     | _   |

## LOGIC SYMBOL

$\overline{E}$  = Am99C58  $\overline{S}$  = Am99C59

#### **ADDRESS DESIGNATORS**

| External        | internal        | Pin Number<br>DIP Package |

|-----------------|-----------------|---------------------------|

| A <sub>0</sub>  | AX <sub>0</sub> | 21                        |

| A <sub>1</sub>  | AX <sub>1</sub> | 22                        |

| A <sub>2</sub>  | AX <sub>2</sub> | 23                        |

| Аз              | AX <sub>3</sub> | 1                         |

| A <sub>4</sub>  | AX <sub>4</sub> | 2                         |

| A <sub>5</sub>  | AX <sub>5</sub> | 3                         |

| A <sub>6</sub>  | AX <sub>6</sub> | 4                         |

| A <sub>7</sub>  | AY <sub>0</sub> | 5                         |

| A <sub>8</sub>  | AY <sub>1</sub> | 6                         |

| A <sub>9</sub>  | AY <sub>2</sub> | 7                         |

| A <sub>10</sub> | AY3             | 17                        |

| A <sub>11</sub> | AY <sub>4</sub> | 20                        |

## PIN DESCRIPTION

## A<sub>0</sub> - A<sub>11</sub> Address (Inputs)

The 12 address inputs select one of the 4096 4-bit words in the RAM.

## E/S Chip Enable/Chip Select (Input)

An active-LOW input which selects the device for operation. When  $E/\overline{S}$  is HIGH, the device is deselected and the outputs will be in a high-impedance state. The  $\overline{E}$  pin will also power down the Am99C58 when HIGH.

#### Write Enable (Input)

$\overline{W}$  controls read and write operations. When  $\overline{W}$  is HIGH and  $\overline{E}/\overline{S}$  is LOW, data will be present at the data outputs. When

$\overline{\mathbf{W}}$  is LOW, data present on the data inputs will be written into the selected memory location. The data outputs will be in a high-impedance state.

## D<sub>0</sub> - D<sub>3</sub> Data Input

Data inputs to the RAM.

## Q<sub>0</sub> - Q<sub>3</sub> Data Output

Data outputs from the RAM. The data outputs will be in a high-impedance state when  $\overline{E}/\overline{S}$  is HIGH or  $\overline{W}$  is LOW.

V<sub>CC</sub> Power Supply +5 Volts

/ss Ground

TABLE 1. MODE SELECT

| Inp | uts | Outputo  | Mode         | Power  |

|-----|-----|----------|--------------|--------|

| Ē/S | W   | Outputs  | Mode         |        |

| н   | Х   | Hi-Z     | Not Selected | *      |

| L   | L   | Hi-Z     | Write '      | Active |

| L   | н   | Data Out | Read         | Active |

H = HIGH

L = LOW

X = Don't Care

\*The Am99C58 will be in Standby; The Am99C59 will be Active

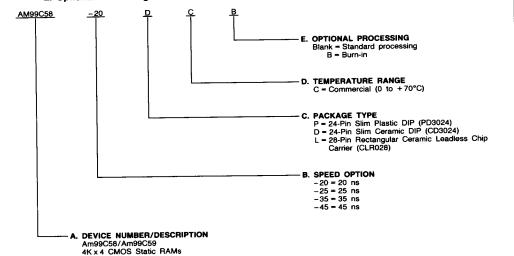

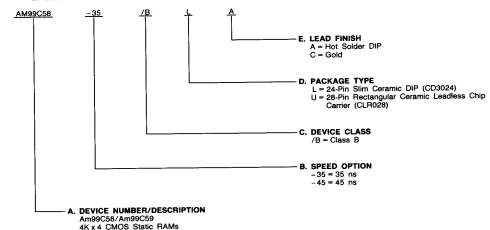

## ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: **A. Device Number**

- B. Speed Option (if applicable)

- C. Package Type

- D. Temperature Range

- E. Optional Processing

| Valid      | Valid Combinations |  |  |  |  |  |

|------------|--------------------|--|--|--|--|--|

| AM99C58-20 | 7/,                |  |  |  |  |  |

| AM99C58-25 | <del>-</del>       |  |  |  |  |  |

| AM99C58-35 | <b>-7</b> /        |  |  |  |  |  |

| AM99C58-45 | PC, PCB,           |  |  |  |  |  |

| AM99C59-20 | DC, DCB,           |  |  |  |  |  |

| AM99C59-25 |                    |  |  |  |  |  |

| AM99C59-35 |                    |  |  |  |  |  |

| AM99C59-45 |                    |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

preliminary

## **ORDERING INFORMATION**

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. CPL (Controlled Products List) products are processed in accordance with MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) for APL products is formed by a combination of: **A. Device Number**

- B. Speed Option (if applicable)

- C. Device Class

- D. Package Type

- E. Lead Finish

| Valid Combinations |            |  |  |  |  |

|--------------------|------------|--|--|--|--|

| AM99C58-35         |            |  |  |  |  |

| AM99C58-45         |            |  |  |  |  |

| AM99C59-35         | /BLA, /BUC |  |  |  |  |

| AM99C59-45         |            |  |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

883 CRUEN B

## ABSOLUTE MAXIMUM RATINGS (Note 1) Storage Temperature ......-65 to +150°C

Ambient Temperature with Power Applied ...... -55 to +125°C Supply Voltage with Respect to Ground......-0.5 V to +7.0 V Signal Voltages with Respect to Ground......-0.5 V to +7.0 V

The products described by this specification include internal circuitry designed to protect input devices from damaging accumulations of static charge. It is suggested nevertheless, that conventional precautions be observed during storage, handling and use in order to avoid exposure to excessive

Power Dissipation (Package Limitation) ......................1.2 W

## **OPERATING RANGES** (Note 2)

Commercial (C) Devices Temperature (T<sub>A</sub>)...... 0 to +70°C Supply Voltage (V<sub>CC</sub>) .....+ 5.0 V ± 10% Military (M) Devices\* Temperature (T<sub>C</sub>).....-55 to +125°C Supply Voltage (VCC) .....+5.0 V ±10%

Operating ranges define those limits between which the functionality of the device is guaranteed.

\*Military Product 100% tested at T<sub>C</sub> = +25°C, +125°C, and -55°C.

## DC CHARACTERISTICS over operating range unless otherwise specified\*

|                          |                                               |                                                        | Am99C58-20, -25<br>Am99C59-20, -25 |      | Am99C58-35, -45<br>Am99C59-35, -45 |             |      |           |

|--------------------------|-----------------------------------------------|--------------------------------------------------------|------------------------------------|------|------------------------------------|-------------|------|-----------|

| Parameter<br>Symbol      | Parameter<br>Description                      | Test Conditions                                        |                                    | Min. | Max.                               | Min.        | Max. | Units     |

| Voн                      | Output HIGH Voltage                           | V <sub>CC</sub> = Min., I <sub>OH</sub> = -4 mA        |                                    | 2.4  | l                                  | 2.4         |      |           |

| VOL                      | Output LOW Voltage                            | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8 mA         |                                    |      | 0.4                                |             | 0.4  | 327       |

| ViH                      | Input HIGH Voltage                            |                                                        |                                    | 2.2  | 6.0                                | 2.2         | 8.0  | ٧         |

| VIL                      | Input LOW Voltage                             | (Note 3)                                               |                                    | -0.5 | 0.8                                | -0.5        | 0.8  | V         |

| lıх                      | Input Load Current                            | GND ≤ V <sub>I</sub> ≤ V <sub>CC</sub>                 |                                    | -2.0 | 2.0                                | <b>-2.0</b> | 2.0  | μΑ        |

| loz                      | Output Leakage Current                        | GND ≤ V <sub>O</sub> ≤ V <sub>CC</sub> Output Disabled |                                    | -10  | 10                                 | -10         | 10   | μΑ        |

|                          |                                               | Max V <sub>CC</sub> , E/\$ ≤ V <sub>IL</sub> ,         | C Devices                          |      | (180)                              |             | 160  | mA        |

| lcc                      | V <sub>CC</sub> Operating Supply<br>Current   | Output Open<br>Cycle = Min.                            | M Devices                          |      | NA                                 |             | 180  | ) <u></u> |

| ····                     | Standby Power Supply                          | Max. V <sub>CC</sub> ,                                 | C Devices                          | 772  | 40                                 |             | 40   | mA        |

| ISB                      | Current, TTL input<br>Levels (Am99C58 only)   | Max. V <sub>CC</sub> ,<br>E = V <sub>IH</sub>          | M Devices                          |      | NA                                 |             | 40   |           |

| ISBC Current, CMOS Input | Standby Power Supply                          | thy Power Supply E>Vcc-0.2 V                           | C Devices                          |      |                                    |             | (10) | mA        |

|                          | Current, CMOS Input<br>Levels (Arm99C58 only) | <sup>tit</sup>   v <sub>vv</sub> ≥ Voo = 0.2 V [       |                                    |      | NA                                 |             | 10   | ""        |

Notes: 1. Absolute Maximum Ratings are intended for user guidelines and are not tested.

- Absolute Maximum Hatings are intended for user guidelines and are not tested.

For test and correlation purposes, operating temperature is defined as the "instant-ON" case temperature.

V<sub>IL</sub> = -1.5 V for pulse width less than 10 ns.

This parameter is not tested, but guaranteed by characterization.

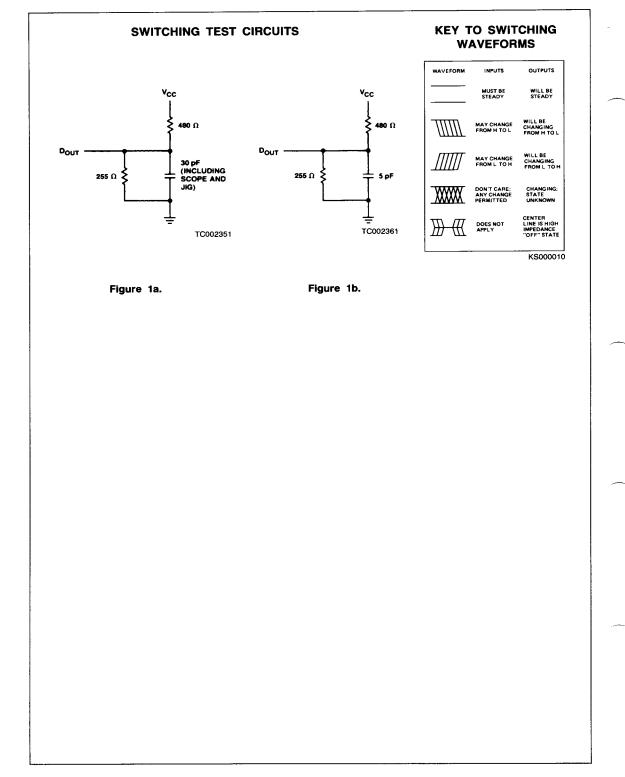

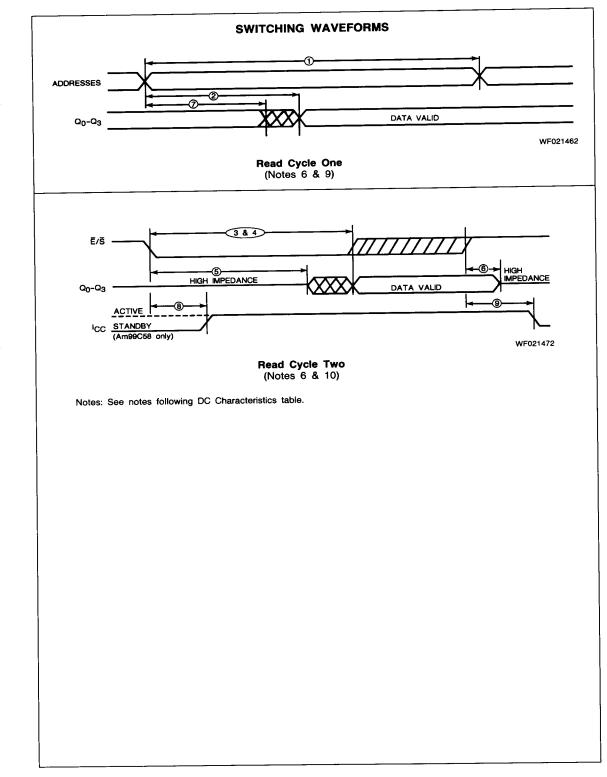

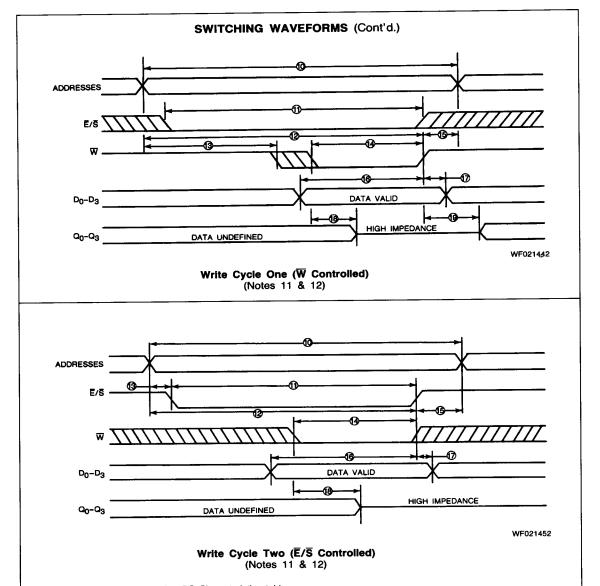

Test conditions assume signal transition times of 10 ns or less, timing reference levels of 1.5 V, input pulse levels of 0 to 3.0 V and cutting leading of the precified by (less and 30 pt lead capsailance. Cuteut timing reference is 1.5 V. output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> and 30 pF load capacitance. Output timing reference is 1.5 V. 8. W is HIGH for read cycle.

6. The Finder for lead byte.

7. Transition is measured ±500 mV from steady state voltage with specified loading in Figure 1b under Switching Test Circuits.

8. The internal write time of the memory is defined by the overlap of E/S LOW and W LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input setup and hold timing is referenced to the rising edge

of the signal that terminates the write.

9. E/S is LOW for read cycle.

9. E/3 is LOW for read cycle.

10. Address Valid prior to or coincident with E/S LOW.

11. E/S or W must be HIGH during address transitions.

12. If E goes HIGH simultaneously with ₩ HIGH, the output remains in a high-impedance state. What Investment 12000 1000 1

## CAPACITANCE

voltages.

| Parameter<br>Symbol | Parameter<br>Description | Test Conditions                                                     | Min. | Max. | Min. | Max. | Units |

|---------------------|--------------------------|---------------------------------------------------------------------|------|------|------|------|-------|

| Cı                  | Input Capacitance        | Test Frequency = 1.0 MHz<br>T <sub>A</sub> = 25°C, All Pins at 0 V, |      | 5    |      | 5    | ρF    |

| Co                  | Output Capacitance       | V <sub>CC</sub> = 5 V (Note 4)                                      |      | 7    |      | 7    |       |

<sup>\*</sup>See the last page of this spec for Group A Subgroup Testing information.

|        | Parameter<br>Symbol                    |                 |                                                     |                              | Am99C58-20 Am99C58-25<br>Am99C59-20 Am99C59-25 |                                                  | Am99C58-35<br>Am99C59-35 |          | Am99C58-45<br>Am99C59-45 |          |          |          |          |

|--------|----------------------------------------|-----------------|-----------------------------------------------------|------------------------------|------------------------------------------------|--------------------------------------------------|--------------------------|----------|--------------------------|----------|----------|----------|----------|

| No.    | Standard                               | Alternate       | Description                                         |                              | Min.                                           | Max.                                             | Min.                     | Max.     | Min.                     | Max.     | Min.     | Max.     | Units    |

| READ ( | CYCLE                                  |                 |                                                     |                              |                                                |                                                  |                          |          |                          |          |          |          |          |

| 1      | tavav                                  | <sup>t</sup> RC | Read Cycle Time<br>(Note 6)                         | ө                            | 20                                             |                                                  | 25                       |          | 35                       |          | 45       | 45       | ns<br>ns |

| 2      | tavov                                  | taa             | Address Access                                      |                              |                                                | 20                                               |                          | 25       |                          | 35       | P        |          | - 113    |

| 3      | tELQV                                  | tACE            | Chip Enable<br>Access Time                          | Am99C58<br>only              | İ                                              | 20                                               |                          | 25       | <u> </u>                 | 35       | <b>}</b> | 45       | ns       |

| 4      | tsLQV                                  | tacs            | Chip Select<br>Access Time                          | Am99C59<br>only              |                                                | 10                                               | ≥_                       | 15       |                          | 20       | <u> </u> | (25)     | ns       |

| 5      | t <sub>ELQX</sub><br>t <sub>SLQX</sub> | tCLZ            | Chip Enable/Sel<br>Output in Low-Z<br>(Notes 4 & 7) |                              | 0                                              |                                                  | 0                        |          | 0                        |          | 0        |          | ns       |

| 6      | t <sub>EHQZ</sub>                      | tcHZ            | Chip Enable/Sel<br>Output in Hi-Z (                 | lect HIGH to<br>Notes 4 & 7) | 0                                              | 15                                               | 0                        | 20       | 0                        | 25       | 0        | 30       | ns       |

|        |                                        |                 | Output Hold<br>after Address                        | C Devices                    | 3                                              | <u> </u>                                         | 3                        |          | 3                        | <u> </u> | 3        |          | ns ns    |

| 7      | tAXQX                                  | toha            | Change                                              | M Devices                    | 1                                              |                                                  | 1                        |          | 1                        | L        | 1        | <b>↓</b> |          |

| 8      | tELICCH                                | tpu             | Chip Enable to<br>(Am99C58) (Not                    |                              | 0                                              |                                                  | 0                        |          | 0                        | <u> </u> | 0        | ļ        | ns       |

| 9      | t <sub>EHICCL</sub>                    | tPD             | Chip Disable to Power Down<br>(Am99C58) (Note 4)    |                              | 0                                              | 20                                               | 0                        | 25       | 0                        | 35       | 0        | 40       | ns       |

| WRITE  | CYCLE                                  |                 |                                                     |                              |                                                |                                                  |                          |          |                          |          |          |          |          |

| 10     | tavav                                  | twc             | Write Cycle Tim                                     | ne (Note 8)                  | 20                                             |                                                  | 25                       |          | 35                       |          | 45       | <u> </u> | ns       |

| 11     | telwh<br>tslwh                         | \$cw            | Chip Enable/Se<br>Write Enable H                    | lect LOW to                  | 15                                             |                                                  | 20                       |          | 30                       | ļ        | 40       | ļ        | ns       |

| 12     | tavwh                                  | taw             | Address Valid t<br>Write                            | o End of                     | 15                                             |                                                  | 20                       | <u> </u> | 30                       | _        | 40       |          | ns       |

| 13     | 1AVWL                                  | tas             | Address Valid to of Write                           | o Beginning                  | 0                                              |                                                  | 0                        |          | 0                        |          | 0        | 1        | ns       |

| 14     | twLwH                                  | twp             | Write Pulse Wid                                     |                              | 15                                             |                                                  | 20                       |          | 30                       |          | 40       |          | ns       |

| 15     | twhax                                  | twn             | Address Hold after End of Write                     |                              | 5                                              |                                                  | 5                        |          | 5                        |          | 5        |          | ns       |

| 16     | t <sub>DVWH</sub>                      | t <sub>DW</sub> | Data in Valid to Write Enable<br>HIGH               |                              | 10                                             |                                                  | 10                       |          | 15                       |          | 20       | <u> </u> | ns       |

| 17     | twHDX                                  | t <sub>DH</sub> |                                                     | Data Hold after End of Write |                                                | <del>                                     </del> | 5                        | -        | 5                        | -        | 5        | +        | ns       |

| 18     | twLQZ                                  | twz             | Write Enable L<br>in Hi-Z (Notes                    |                              | 0                                              | 10                                               | 0                        | 10       | 0                        | 15       | 0        | 20       | ns       |

| 19     | twnqx                                  | tow             | Write Enable H                                      |                              | 0                                              |                                                  | 0                        |          | 0                        |          | 0        |          | ns       |

Notes: See notes following DC Characteristics table.

<sup>\*</sup>See the last page of this spec for Group A Subgroup Testing information.

Notes: See notes following DC Characteristics table.

## **GROUP A SUBGROUP TESTING**

#### DC CHARACTERISTICS

| Parameter<br>Symbol | Subgroups |  |

|---------------------|-----------|--|

| VoH                 | 1, 2, 3   |  |

| V <sub>OL</sub>     | 1, 2, 3   |  |

| VIH                 | 7, 8      |  |

| V <sub>IL</sub>     | 7, 8      |  |

| I <sub>IX</sub>     | 1, 2, 3   |  |

| loz                 | z 1, 2, 3 |  |

| lcc                 | 1, 2, 3   |  |

| I <sub>SB</sub>     | 1, 2, 3   |  |

| ISBC                | 1, 2, 3   |  |

#### SWITCHING CHARACTERISTICS

| No. | Parameter<br>Symbol                                        | Subgroups       | No. | Parameter<br>Symbol | Subgroups       |

|-----|------------------------------------------------------------|-----------------|-----|---------------------|-----------------|

| 1   | tavav (tRC)                                                | 7, 8, 9, 10, 11 | 16  | tDVWH (tDW)         | 7, 8, 9, 10, 11 |

| 2   | tavqv (taa)                                                | 7, 8, 9, 10, 11 | 17  | twhox (tph)         | 7, 8, 9, 10, 11 |

| 3   | t <sub>ELQV</sub> (t <sub>ACE</sub> )<br>(Am99C58<br>only) | 7, 8, 9, 10, 11 |     |                     | -               |

| 4   | tSLQV (tACS)<br>(Am99C59<br>only)                          | 7, 8, 9, 10, 11 |     |                     |                 |

| 7   | taxqx (toha)                                               | 7, 8, 9, 10, 11 |     |                     |                 |

| 10  | tavav (twc)                                                | 7, 8, 9, 10, 11 |     |                     |                 |

| 11  | tslwh (tcw)                                                | 7, 8, 9, 10, 11 |     |                     |                 |

| 12  | tavwh (taw)                                                | 7, 8, 9, 10, 11 |     |                     |                 |

| 13  | tavwl (tas)                                                | 7, 8, 9, 10, 11 |     |                     |                 |

| 14  | twlwh (twp)                                                | 7, 8, 9, 10, 11 |     |                     |                 |

| 15  | twhax (twn)                                                | 7, 8, 9, 10, 11 |     |                     |                 |

#### **MILITARY BURN-IN**

Military burn-in is in accordance with the current revision of MIL-STD-883, Test Method 1015, Conditions A through E. Test conditions are selected at AMD's option.