AMC

# Q700 SERIES ECL/TTL LOGIC ARRAYS

## **FEATURES**

#### **VARIOUS ARRAY SIZES**

250, 500, 1000 equivalent gate versions to support various circuit requirements.

#### **VERY HIGH SPEED**

0.5 to 0.9 ns average gate delay within the internal array.

#### **ECL & TTL COMPATIBILITY**

The Q700 series logic arrays are compatible with ECL, TTL or simultaneous ECL/TTL systems, in both single and multiple power supply configurations. This flexible I/O structure eliminates the need for ECL/TTL and TTL/ECL translator logic in high performance applications.

## **MODERATE POWER**

The Q700 series devices offer the advantage of low power ECL coupled with the very flexible I/O structure.

#### **FULL MILITARY AVAILABILITY**

These logic arrays are available for applications requiring MIL-STD-883C Class B screening including burn-in. The thermal transfer characteristics of the device packaging, and with the low overall power dissipation, allows operation over the military temperature range of  $-55^{\circ}$  to  $+125^{\circ}$ C.

## **RADIATION HARD TECHNOLOGY**

This series features a washed emitter ECL process which is one of the most radiation tolerant technologies in production.

| PERFORMANCE SUMMA                                                                                                                      | RY                                              |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| PARAMETER                                                                                                                              | VALUE                                           |

| Typical gate delay* Maximum I/O frequency TTL output drive ECL output drive Average cell utilization *Based on complex macro functions | 0.5 to 0.9 ns<br>100 MHZ<br>20 ma<br>50Ω<br>85% |

TABLE 1

### **DESCRIPTION**

The AMCC Q700 series consists of the Q720, Q710 and Q700 Logic arrays providing equivalent densities of up to 250, 500 and 1000 gates respectively. The series is optimized to provide a system approach to high performance semi-custom applications. High speed ECL logic and proven reliability are combined with an advanced, interactive CAD system to provide a quick and cost effective solution to discrete I.C. replacement.

Each device shares a common Internal Logic and I/O macro library. The Q700 series utilize advanced series gating techniques providing both density and speed improvements over gate oriented and other macro oriented designs.

The Q700 logic arrays offer a wide range of standard packaging and support up to 76 I/O signals and 8 power supply connections.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 046741          | 0 (1671(2) | B 12 37 Y |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|-----------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ESOURCE SUMMARY |            |           |

| DESCRIPTION OF A SECOND OF THE PROPERTY OF THE | 9709            | 9710       | 1072p J   |

| Approximate gate complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1000            | 500        | 250       |

| Internal logic cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 208             | 120        | 56        |

| Input cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38              | 28         | 8         |

| I/O cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38              | 28         | 26        |

| Typical power dissipation per cell in MW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-8             | 5-8        | 5-8       |

| Typical total circuit power dissipation in Watts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.8             | 1.2        | 0.75      |

TABLE 2

**APPLIED MICRO CIRCUITS CORPORATION**

5502 OBERLIN DRIVE, SAN DIEGO, CA 92121

(619) 450-9333

## **Q700 SERIES DIE LAYOUTS**

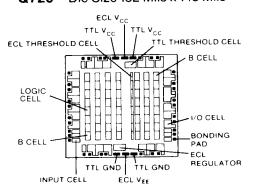

#### Q700 - Die Size 236 Mils x 243 Mils

#### **ARRAY STRUCTURE**

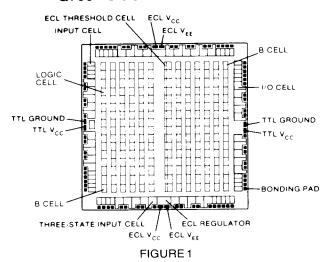

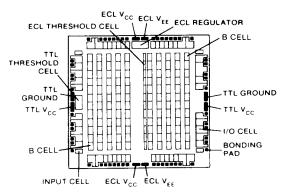

The Q700 series logic arrays each have an internal structure comprised of 3 basic configurable cell types plus overhead logic such as voltage references, bias generators, and voltage regulators. The 3 configurable cell types are INPUT, I/O and INTERNAL LOGIC cells.

#### **INTERNAL ARRAY**

There are 208 internal logic cell positions for the Q700, 120 cells for the Q710, and 56 cells for the Q720. B cells occupy only the top and bottom rows in the internal array. Internal logic macros can be placed in either a Logic (L) or Buffer (B) cell, while ECL output buffer macros can only be placed in a B cell. Macro placement is performed automatically using AMCC CAD software. If a circuit requires critical timing considerations, these macros may be preplaced using interactive graphics.

| IN      | TERNAL ARRA        | BLE 3<br>Y CELL RESOU | IRCE A |

|---------|--------------------|-----------------------|--------|

|         | <b>SUN</b><br>Q700 | MARY<br>Q710          | Q720   |

| L Cells | 182                | 100                   | 42     |

| B Cells | 26                 | 20                    | 14     |

| Total   | 208                | 120                   | 56     |

The input and I/O cells are located around the periphery of the array and can be configured into many different combinations of circuit I/O. An INPUT CELL may be interconnected to form a TTL input or ECL input. An I/O cell may be interconnected to produce TTL or ECL input, output or bi-directional I/O.

Table 4 lists the available I/O resources for the Q700 series logic arrays. Each logic array requires a different number of power supply connections depending on the mode of operation.

PAGE 2

#### Q710 - Die Size 195 mils x 197 Mils

FIGURE 2

## Q720 - Die Size 152 Mils x 148 Mils

FIGURE 3

| MODE                        | DESCRIPTION                                                                                                                                                                              | Q700                               | Q710                         | Q720                        |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------|-----------------------------|

|                             | Input Cells (Max) I/O Cells (Max) Dedicated 3-State Driver Cells V <sub>CC</sub> (+5 V <sub>DC</sub> nom.) Ground                                                                        | 37*<br>38<br>2<br>4<br>5           | 27<br>28<br>0<br>4<br>5      | 8<br>26<br>0<br>3<br>3      |

|                             | Input Cells (Max)<br>I/O Cells (Max)<br>V <sub>EE</sub> (-5.2 V <sub>DC</sub> nom.)<br>Ground                                                                                            | 38*<br>38<br>2<br>6                | 28<br>28<br>2<br>6           | 8<br>26<br>1<br>5           |

| MIXED<br>ECL/TTL<br>SYSTEMS | Input Cells (Max ECL or TTL) I/O Cells (Max ECL or TTL) 3-State Driver Cells V <sub>CC</sub> (+5V V <sub>DC</sub> nom.) V <sub>EE</sub> (-5.2V <sub>DC</sub> nom.) TTL Ground ECL Ground | 37*<br>37<br>2<br>3<br>2<br>3<br>2 | 27<br>27<br>0<br>3<br>2<br>3 | 8<br>25<br>0<br>3<br>1<br>2 |

<sup>\*</sup>Includes dedicated 3-state driver cells which are usable as simple inputs.

TABLE 4

I/O RESOURCES

## **INTERNAL LOGIC CELLS**

## INTERNAL LOGIC CELL CAPABILITIES

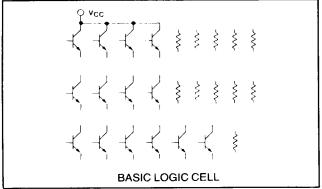

The Q700 series logic arrays each have identically configured internal logic cells containing the components shown in Figure 4. These uncommitted cells are custom interconnected during metallization to provide the desired logic function defined by the macro library elements chosen.

FIGURE 4

### **HIGH PERFORMANCE MACROS**

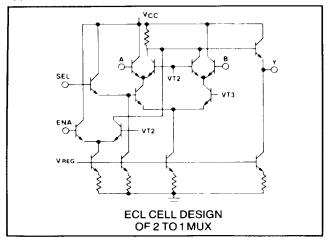

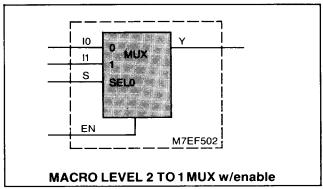

Figure 5 shows the individual logic cell components configured as a 2 to 1 multiplexer, Figure 6 shows the multiplexer as configured in the library. To obtain high circuit density and performance, the circuit uses 2 level series gating; a technique which allows a second level of gating to be added to a macro without a significant increase in component count, circuit delay, or circuit power.

Many of the macros for the Q700 series arrays use series gating. Along with the I/O macros, they provide a powerful high speed library of circuit building blocks for virtually any circuit application.

FIGURE 5

### HIGH PERFORMANCE CIRCUIT DESIGN

The Q700 series internal macros have performance comparable to circuits designed with ECL 10K SSI and MSI logic devices. With the translation from TTL to ECL available directly on the Q700 series arrays, very high speed circuits can be realized with 100% TTL compatible I/O. Additionally, the mixed TTL/ECL capabilities allow the use of both technologies in a single design without the use of 10124 and 10125 ECL/TTL translators.

#### EASY TO USE MACRO LIBRARY

The Q700 series macro libraries are organized much like standard TTL or ECL logic catalogs. Figure 6 shows the 2 to 1 multiplexor as it is illustrated in the macro library. All the macros contained in the library are documented in a similar fashion, consisting of the type of macro, a functional description, and the speed and power requirements.

FIGURE 6

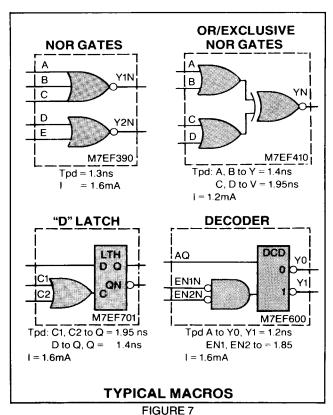

#### **TYPICAL MACROS**

The following macros are typical of those found in the INTER-NAL LOGIC MACRO library. Each macro occupies one logic cell location and has its typical performance and power consumption specified. AMCC provides over 40 different INTER-NAL LOGIC MACROS in the library, providing all the needed building blocks for complex logic design.

PAGE 3

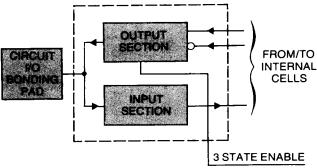

#### FLEXIBLE I/O CAPABILITY

The I/O structure of the Q700 series arrays has been designed to provide a very flexible I/O capability. The input cells are configurable to provide TTL input or ECL 10K input with either +5V or -5.2V DC power supply.

In addition to standard input cells, the Q700-1000 gate array has two special input cells which can also be used as high fanout 3-state enable drivers. These special drivers can directly drive up to 16 three-state enables, alleviating the need to use an I/O cell for 3-state enables in the Q700.

The I/O cells may be configured to operate in an input mode, output mode, or bi-directional I/O mode. In the input mode, the I/O cell operates identically to the I cell. When used in the output mode, the I/O cell can provide TTL totem pole output; TTL open collector output, or ECL 10K output capable of driving 200 ohms, 100 ohms, or 50 ohms.

The I/O cells can also be used to provide a driver for 3-state enables. When used in this manner, the I/O cell can be used with either internal or external signals and will drive up to 8 loads of 3-state enable.

## I CELL CAPABILITIES

The following modes of input are supported by the Q700

- TTL compatible input

- ECL compatible input (V<sub>CC</sub> = +5V  $V_{EE} = GND$

- ECL compatible input (V<sub>CC</sub> = GND V<sub>EE</sub> = -5.2V)

16 load 3-state driver (2 cells Q700 only)

#### I/O CELL CAPABILITIES

Each I/O cell has two distinct sections which can be used independently or in combination.

The following I/O modes are supported:

#### INPUT ONLY

- TTL compatible INPUT

- ECL 10K compatible INPUT (V<sub>CC</sub> = +5V V<sub>EE</sub> = GND)

- ECL 10K compatible INPUT ( $V_{CC} = GND V_{EE} = -5.2V$ )

- External 3-state enable INPUT

#### **OUTPUT ONLY**

- TTL S/LS,TTL totem pole

- TTL OPEN COLLECTOR (.5V @ 20 mA IOL)

- ECL 10K @ 200 ohms, 100 ohms, 50 ohms  $(V_{CC} = 5V \ V_{EE} = GND)$ ECL 10K @ 200 ohms, 100 ohms, 50 ohms

- $(V_{CC} = \widetilde{GND} \ V_{EE} = -5.2V)$

- Internal 3-state enable drive

### **BI-DIRECTIONAL I/O**

- TTL LS/S TRANSCEIVER

- ECL 10K TRANSCEIVER ( $V_{CC} = GND V_{EE} = -5.2V$ )

### **DESIGN INTERFACE**

The AMCC design interface has been structured to be highly flexible with respect to the customer's level of involvement. AMCC has developed an entire set of CAD tools providing an easy to understand, user-friendly interface.

## **AMCC CAD TOOLS**

- · Schematic capture

- · Logic simulation

- Timing verifier

- Test vector generation with optional fault grading

- Auto place and route

- Design rule and interconnect verifier

These CAD tools provide the logic designer with the required support to design and develop a logic array from schematic diagrams through complete layout.

In addition to providing the required CAD to allow customer design of arrays, AMČC provides a number of services to support customer design.

## **AMCC PROVIDED SERVICES**

- Logic conversion to AMCC macros

- Logic simulation with customer provided simulation vectors

- · Custom macro development

- Hi-level engineering support

#### **PACKAGING**

The Q700 series logic arrays can be provided in a full variety of dual in-line, leaded and leadless chip carriers, and pin grid packages.

| Pin Count | Package<br>Type | Q720 | Q710 | Q700 |

|-----------|-----------------|------|------|------|

| 24        | DIP             | •    | •    |      |

| 28        | DIP             | •    | •    |      |

| 40        | DIP<br>LCC      | •    | •    | •    |

| 44        | LCC             | •    | •    | •    |

| 48        | DIP             | •    | •    | •    |

| 64        | FP<br>LDCC      |      | •    | •    |

| 68        | LCC<br>PGA      |      | •    | •    |

| 84        | FP<br>PGA       |      |      | •    |

DIP -- Dual In-line Leadless Chip Carrier FP—Flat Pack

\_DCC —Leaded Chip Carrier PGA —pin grid array

## **Q700 SERIES ECL MODE OPERATING CONDITIONS**

## **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                    | MIN    | HOM   | MAX    | UNIT |

|------------------------------|--------|-------|--------|------|

| Supply Voltage (VFF) VCC = 0 |        |       |        |      |

| Military                     | - 4.7  | - 5.2 | - 5.7  | V    |

| Commercial                   | - 4.94 | - 5.2 | - 5.46 | ٧    |

| Input Signal Rise/Fall Time  |        | 2.0   |        | nS   |

| Junction Temperature         |        |       |        |      |

| Military                     |        |       | 150    | °C   |

| Commercial                   |        |       | 130    | °C   |

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>EE</sub> ) V <sub>CC</sub> = 0 | - 8.0 V DC                          |

|-------------------------------------------------------|-------------------------------------|

| Input Voltage V <sub>CC</sub> = 0                     | GND to V <sub>EE</sub>              |

| Output Source Current Continuous                      | - 50 mA DC                          |

| Operating Temperature                                 | -55°C (Ambient)<br>to +125°C (Case) |

| Operating Junction Temperature T <sub>J</sub>         | +150°C                              |

| Storage Temperature                                   | -65°C to +150°C                     |

## ECL 10K INPUT/OUTPUT DC CHARACTERISTICS $V_{EE} = -5.2V^{1}$

|                                    |                       | Tambient              | en e |                       | T <sub>case</sub>     |      |

|------------------------------------|-----------------------|-----------------------|------------------------------------------|-----------------------|-----------------------|------|

|                                    | -55°C                 | Jone .                | 25°C                                     | 75°C                  | 125°C                 | UNIT |

| V <sub>OH max</sub>                | V <sub>CC</sub> -850  | V <sub>CC</sub> -770  | V <sub>CC</sub> -730                     | V <sub>CC</sub> 650   | V <sub>CC</sub> -575  | mV   |

| V <sub>IH max</sub>                | V <sub>CC</sub> -800  | V <sub>CC</sub> -720  | V <sub>CC</sub> -680                     | V <sub>CC</sub> 600   | V <sub>CC</sub> -525  | mV   |

| V <sub>OH min</sub>                | V <sub>CC</sub> -1080 | V <sub>CC</sub> -1000 | V <sub>CC</sub> -980                     | V <sub>CC</sub> -920  | V <sub>CC</sub> -850  | mV   |

| V <sub>IH min</sub>                | V <sub>CC</sub> -1255 | V <sub>CC</sub> -1145 | V <sub>CC</sub> -1105                    | V <sub>CC</sub> -1045 | V <sub>CC</sub> -1000 | mV   |

| V <sub>IL max</sub>                | V <sub>CC</sub> -1510 | V <sub>CC</sub> -1490 | V <sub>CC</sub> -1475                    | V <sub>CC</sub> -1450 | V <sub>CC</sub> -1400 | mV   |

| V <sub>OL max</sub>                | V <sub>CC</sub> -1655 | V <sub>CC</sub> -1625 | V <sub>CC</sub> -1620                    | V <sub>CC</sub> -1585 | V <sub>CC</sub> -1545 | mV   |

| V <sub>OL min</sub>                | V <sub>CC</sub> -1980 | V <sub>CC</sub> -1980 | V <sub>CC</sub> -1980                    | V <sub>CC</sub> -1980 | V <sub>CC</sub> -1980 | mV   |

| V <sub>IL min</sub>                | V <sub>CC</sub> -2000 | V <sub>CC</sub> -2000 | V <sub>CC</sub> -2000                    | V <sub>CC</sub> -2000 | V <sub>CC</sub> -2000 | mV   |

| I <sub>in</sub> H max <sup>2</sup> | 30                    | 30                    | 30                                       | 30                    | 30                    | μΑ   |

| I <sub>in</sub> L min <sup>2</sup> | .5                    | .5                    | .5                                       | .5                    | .5                    | μΑ   |

#### NOTES:

1. Data measured at thermal equilibrium. For +5V ref. ECL  $V_{CC} = +5.0V$

2. Per fan-in

## **DEDICATED AC ELECTRICAL CHARACTERISTICS**

| SYMBOL            | PARAMETER                                   |                                                      | COMM | 0° C/+ | 75° C | MIL-58 | 5° C/+ | 125°C | UNIT      |

|-------------------|---------------------------------------------|------------------------------------------------------|------|--------|-------|--------|--------|-------|-----------|

| SIMBUL            | SIMPUL                                      |                                                      | MIN  | TYP    | MAX   | MIN    | TYP    | MAX   | · · · · · |

| <sup>t</sup> IPD  | Input Propagation Delay through buffer      |                                                      |      | 1.6    |       |        | 1.6    |       | nS        |

| tOPD              | Output Propagation Delay including buffer   | $C_{L} = 5 \text{ pf}$<br>$50\Omega \text{ to } -2V$ |      | 2.95   |       |        | 2.95   |       | nS        |

| t <sub>FPD</sub>  | Internal Equivalent Gate Delay <sup>1</sup> |                                                      |      | 0.9    |       |        | 0.9    |       | nS        |

| F <sub>MAXE</sub> | Max. Internal Flip-Flop<br>Toggle Frequency |                                                      |      | 250    |       |        | 250    |       | MHz       |

#### NOTES:

1. Logic cell delays are for each gating level of a more complex logic function (i.e. D flip/flop, 4 to 1 mux, etc.)

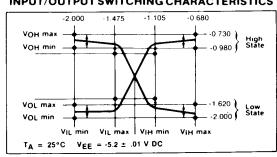

#### INPUT/OUTPUT SWITCHING CHARACTERISTICS

PAGE 5

## **Q700 SERIES TTL MODE OPERATING CONDITIONS**

## **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                                                     | MIN                                | NON.       | MAX                                | UNUT     |

|---------------------------------------------------------------|------------------------------------|------------|------------------------------------|----------|

| Supply Voltage (V <sub>CC</sub> )<br>Military<br>Commercial   | 4.5<br>4.75                        | 5.0<br>5.0 | 5.5<br>5.25                        | V<br>V   |

| Output Current Low (IOL) Military Commercial                  |                                    |            | 20<br>20                           | mA<br>mA |

| Operating Temperature<br>Military<br>Commercial               | -55<br>(ambient)<br>0<br>(ambient) |            | + 125<br>(case)<br>70<br>(ambient) | °C       |

| Junction Temperature T <sub>J</sub><br>Military<br>Commercial |                                    |            | 150<br>130                         | °C       |

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>CC</sub> ),V <sub>EE</sub> = 0 | 7.0V                                |

|-------------------------------------------------------|-------------------------------------|

| Input Voltage                                         | 5.5V                                |

| Operating Temperature                                 | -55°C (Ambient)<br>to +125°C (Case) |

| Junction Temperature (Operating)                      | 150°C                               |

| Storage Temperature                                   | -65°C<br>to +150°C                  |

#### INPUT/OUTPUT DC CHARACTERISTICS

| INPOT/COTFOT DC CHARACTERISTICS |                                   |         |                        |                                       |      |        |      |      |                       |      |      |

|---------------------------------|-----------------------------------|---------|------------------------|---------------------------------------|------|--------|------|------|-----------------------|------|------|

| - Colorina                      | ALEXA DESCRIPTION                 | 4       |                        | STCONDITIONS                          | CON  | IM-07+ | 70°C | MIL. | <del>,5</del> 5% + 12 | 5°C  | UNIT |

| SYMBOL                          | PARAMETE                          |         |                        | an Maria                              | Min  | Typ'   | Mex  | Min  | Typ1                  | Max  |      |

| V <sub>IH</sub> <sup>2</sup>    | Input HIGH voltage                |         |                        | d input HIGH voltage<br>or all inputs | 2.0  |        |      | 2.0  |                       |      | ٧    |

| V <sub>IL2</sub>                | Input LOW voltage                 |         | 1                      | d input LOW voltage<br>or all inputs  |      |        | 0.8  |      |                       | 0.8  | ٧    |

| V <sub>IK</sub>                 | Input clamp diode v               | oltage  | V <sub>CC</sub> = Min, | I <sub>IN</sub> = -18mA               |      | 65     | -1.2 |      | 65                    | -1.2 | V    |

| V <sub>OH</sub>                 | Output HIGH voltag                | e .     | $V_{CC} = Min,$        | $I_{OH} = -1mA$                       | 2.7  | 3.4    |      | 2.4  | 3.4                   |      | ٧    |

| V <sub>OL</sub>                 | Output LOW voltage                | e       | V <sub>CC</sub> = Min  | I <sub>OL</sub> = 4mA                 |      |        | 0.4  |      |                       | 0.4  | ٧    |

|                                 |                                   |         |                        | I <sub>OL</sub> = 20mA                |      |        | 0.5  |      |                       | 0.5  | V    |

| l <sub>OZH</sub>                | Output "off" current (3-state)    | HIGH    | V <sub>CC</sub> = Max  | $v_{OUT} = 2.4V$                      | -145 |        | 145  | -145 |                       | 145  | μΑ   |

| l <sub>ozL</sub>                | Output "off" current<br>(3-state) | LOW     | V <sub>CC</sub> = Max  | $v, V_{OUT} = 0.4V$                   | -145 |        | 145  | -145 |                       | 145  | μΑ   |

| I <sub>IH</sub>                 | Input HIGH current                |         | V <sub>CC</sub> = Max  | $V_{IN} = 2.7V$                       |      |        | 50   |      |                       | 50   | μΑ   |

| l <sub>i</sub>                  | Input HIGH current input voltage  | at Max  | V <sub>CC</sub> = Max  | $x, V_{IN} = 5.5V$                    |      |        | 1.0  |      |                       | 1.0  | mA   |

| I <sub>IL</sub>                 | Input LOW current                 |         | V <sub>CC</sub> = Max  | $x, V_{IN} = 0.5V$                    |      |        | -0.4 |      |                       | -0.4 | mA   |

| los                             | Output short circuit              | current | V <sub>CC</sub> = Max  | $V_{OUT} = 0.5V$                      | -30  |        | -100 | -30  |                       | -100 | mA   |

|                                 |                                   | Q700    |                        |                                       |      | 350    |      |      | 350                   |      | mA   |

| l <sub>CC</sub> <sup>3</sup>    | Supply current                    | Q710    | V <sub>CC</sub> = Max  | x, 85% utilization                    |      | 220    |      |      | 220                   |      | mA   |

|                                 |                                   | Q720    |                        |                                       |      | 150    |      |      | 150                   |      | mA   |

## NOTES:

1. Typical limits are at 25°C,  $V_{CC} = 5.0V$

2a. These input levels provide zero noise immunity and should only be tested in a static, noise-free environment.

PAGE 6

<sup>2</sup>b. Use extreme care in defining input levels for AC tests. Many inputs may be changed at once, so there will be significant noise at the device pins and they may not actually reach V<sub>IL</sub> or V<sub>IH</sub> until the noise has settled. AMCC recommends using V<sub>IL</sub> ≤ 0.4V and V<sub>IH</sub> ≥ 2.4V for AC tests.

3. Maximum power supply currents vary with each circuit design implemented and can only be determined after macro level circuit designs are complete.

## **Q700 SERIES TTL MODE OPERATING CONDITIONS**

#### **AC ELECTRICAL CHARACTERISTICS**

| SYMBOL            | PARAMETER                                    | And the second                                         | COMM 0*/+75°C |     |     | MIL 55*/+ 125*C |     |     |      |

|-------------------|----------------------------------------------|--------------------------------------------------------|---------------|-----|-----|-----------------|-----|-----|------|

|                   |                                              | TEST CONDITIONS                                        | Min           | Тур | Max | Min             | Тур | Max | UNIT |

| <sup>t</sup> IPD  | Input propagation delay through input buffer |                                                        |               | 3.3 |     |                 | 3.3 |     | nS   |

| <sup>t</sup> OPD  | Output propagation delay (I/O cell)          | $R_L = 280\Omega$ , $C_L = 15 pF$<br>Load <sup>2</sup> |               | 6.6 |     |                 | 6.6 |     | nS   |

| t <sub>FPD'</sub> | Internal equivalent gate delay               |                                                        |               | .9  |     |                 | .9  |     | nS   |

| FMAXT             | Max internal flip/flop<br>toggle frequency   |                                                        |               | 250 |     |                 | 250 |     | MHz  |

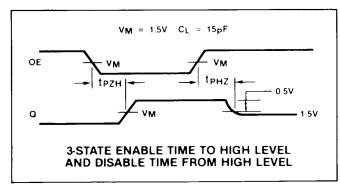

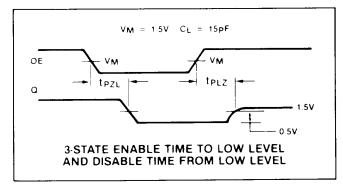

| t <sub>PZH</sub>  | Enable time to high level                    | Figure 8 3-state output                                |               | 6.0 |     |                 | 6.0 |     | nS   |

| t <sub>PZL</sub>  | Enable time to low level                     | Figure 9 3-state output                                |               | 9.0 |     |                 | 9.0 |     | nS   |

| t <sub>PHZ</sub>  | Disable time from high level                 | Figure 8 3-state output                                |               | 6.0 |     |                 | 6.0 |     | nS   |

| <sup>t</sup> PLZ  | Disable time from low level                  | Figure 9 3-state output                                |               | 9.0 |     |                 | 9.0 |     | nS   |

FIGURE 8

FIGURE 9

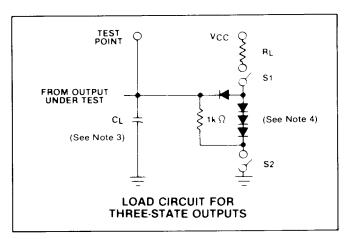

FIGURE 10

## **TEST CIRCUIT SWITCH TABLE**

| TEST FUNCTIONS   | <b>31</b> | 82     |

|------------------|-----------|--------|

| <sup>tp</sup> ZH | Open      | Closed |

| tpZL             | Closed    | Open   |

| tpHZ             | Closed    | Closed |

| tpLZ             | Closed    | Closed |

#### NOTES:

- 1. Logic cell delays are for each gate level of a more complex logic function (i.e. D flip/flop, 4 to 1 mux, etc.)

2. Standard TTL load circuit used, see Figure 10 (S1 and S2 closed)

- 3. C<sub>L</sub> includes probe and jig capacitance.

- 4. All diodes are 1N916 or 1N3064.

PAGE 7

|        |      |  |      | <br> | • |

|--------|------|--|------|------|---|

| NOTES: |      |  |      | <br> |   |

|        | <br> |  | <br> | <br> |   |

5502 OBERLIN DRIVE, SAN DIEGO, CA 92121 • (619) 450-9333

AMCC reserves the right to change specifications for this product in any manner without notice.

AMCC is a registered frademark of Applied Micro Circuits Corporation MacroMatrix is a trademark of Applied Micro Circuits Corporation.

Copyright<sup>1</sup> 1986 Applied Micro Circuits Corporation. PRINTED IN U.S.A. D 0115-0186